SBVS248A - NOVEMBER 2015-REVISED NOVEMBER 2015

**TPS7A88**

# TPS7A88 Dual, 1-A, Low-Noise (3.8-µV<sub>RMS</sub>), LDO Voltage Regulator

#### **Features**

- Two Independent LDO Channels

- Low Output Noise:  $< 3.8 \mu V_{RMS}$  (10 Hz–100 kHz)

- Low Dropout: 200 mV (Max) at 1 A

- Wide Input Voltage Range: 1.4 V to 6.5 V

- Wide Output Voltage Range: 0.8 V to 5.0 V

- High Power-Supply Ripple Rejection:

- 75 dB at DC

- 40 dB at 100 kHz

- 40 dB at 1 MHz

- 1.0% Accuracy Over Line, Load, and Temperature

- **Excellent Load Transient Response**

- Adjustable Start-Up In-Rush Control

- Selectable Soft-Start Charging Current

- Independent Open-Drain Power-Good (PG) Outputs

- Stable with a 10-µF or Larger Ceramic Output

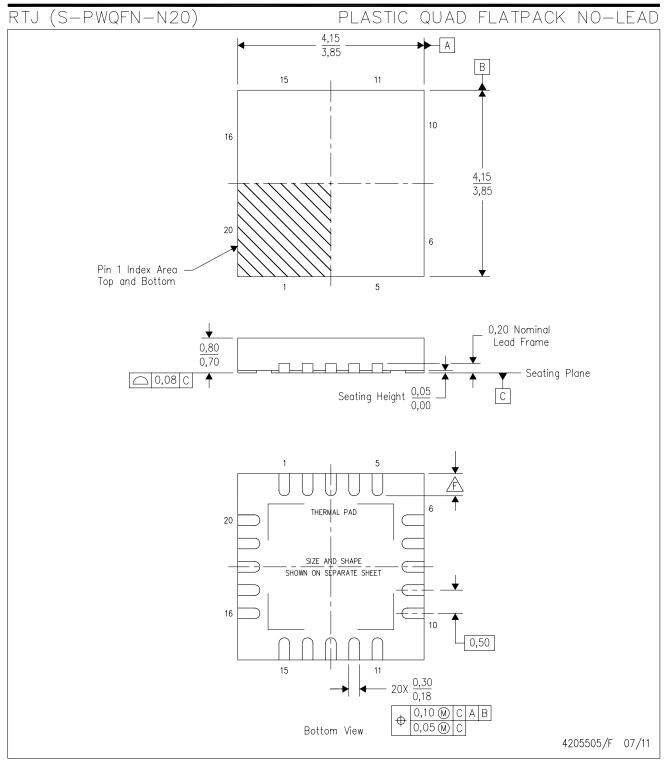

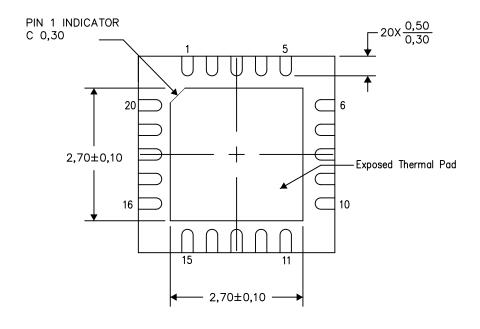

- 4-mm x 4-mm, 20-Pin WQFN Package

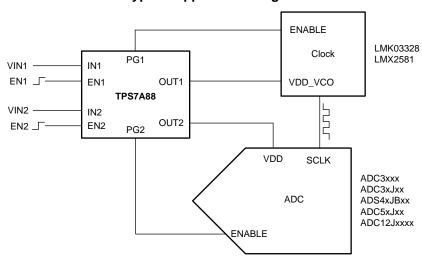

## Applications

- **High-Speed Analog Circuits:**

- VCO, ADC, DAC, LVDS

- Imaging: CMOS Sensors, Video ASICs

- **Test and Measurement**

- Instrumentation, Medical, and Audio

- Digital Loads: SerDes, FPGA, DSP™

## 3 Description

The TPS7A88 is a dual, low-noise (3.8 µV<sub>RMS</sub>), lowdropout (LDO) voltage regulator capable of sourcing 1 A per channel with only 200 mV of maximum dropout.

The TPS7A88 provides the flexibility of two independent LDOs and approximately 50% smaller solution size than two single-channel LDOs. Each output is adjustable with external resistors from 0.8 V to 5.0 V. The TPS7A88 wide input-voltage range supports operation as low as 1.4 V and up to 6.5 V.

With 1% output voltage accuracy (over line, load, and temperature) and soft-start capabilities to reduce inrush current, the TPS7A88 is ideal for powering sensitive analog low-voltage devices [such as voltage-controlled oscillators (VCOs), analog-to-digital converters (ADCs), digital-to-analog converters (DACs), high-end processors. and programmable gate arrays (FPGAs)].

The TPS7A88 is designed to power up noisesensitive components such as those found in highspeed communication, video, medical, or test and measurement applications. The very low 4-μV<sub>RMS</sub> output noise and wideband PSRR (40 dB at 1 MHz) minimizes phase noise and clock jitter. These features maximize performance of clocking devices, ADCs, and DACs.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS7A88     | WQFN (20) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

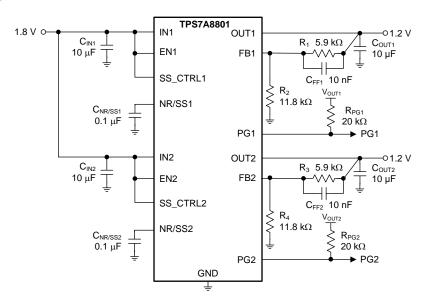

## **Typical Application Diagram**

## **Table of Contents**

| 1<br>2 | Features 1 Applications 1            | 8 Application and Implementation                    |                |

|--------|--------------------------------------|-----------------------------------------------------|----------------|

| 3      | Description 1                        | 8.2 Typical Application                             |                |

| 4      | Revision History2                    | 8.3 Do's and Don'ts                                 | 23             |

| 5      | Pin Configuration and Functions3     | 9 Power Supply Recommendations                      | 24             |

| 6      | Specifications4                      | 10 Layout                                           | 24             |

| •      | 6.1 Absolute Maximum Ratings 4       | 10.1 Layout Guidelines                              | 24             |

|        | 6.2 ESD Ratings                      | 10.2 Layout Example                                 | 2              |

|        | 6.3 Recommended Operating Conditions | 11 Device and Documentation Support                 | 26             |

|        | 6.4 Thermal Information              | 11.1 Device Support                                 | 20             |

|        | 6.5 Electrical Characteristics5      | 11.2 Documentation Support                          | 20             |

|        | 6.6 Typical Characteristics          | 11.3 Community Resources                            | 20             |

| 7      | Detailed Description                 | 11.4 Trademarks                                     | 2 <sup>-</sup> |

| -      | 7.1 Overview                         | 11.5 Electrostatic Discharge Caution                | 2 <sup>-</sup> |

|        | 7.2 Functional Block Diagram         | 11.6 Glossary                                       | 27             |

|        | 7.3 Feature Description14            | 12 Mechanical, Packaging, and Orderable Information |                |

|        | 7.4 Device Functional Modes          | Internation                                         | 21             |

## 4 Revision History

| Changes from Original (November 2015) to Revision A |                        |  |  |

|-----------------------------------------------------|------------------------|--|--|

| •                                                   | Released to production |  |  |

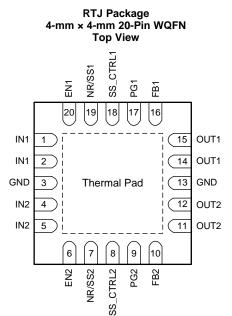

## 5 Pin Configuration and Functions

**Pin Functions**

| PIN         |        |     |                                                                                                                                                          |  |

|-------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.    | I/O | DESCRIPTION                                                                                                                                              |  |

| EN1         | 20     |     | Enable pin for each channel. These pins turn the regulator on and off. If $V_{ENx}^{(1)} \ge V_{IH(ENx)}$ , the regulator is enabled.                    |  |

| EN2         | 6      | '   | If $V_{ENx} \le V_{IL(ENx)}$ , the regulator is disabled. The ENx pin must be connected to INx if the énable function is not used.                       |  |

| FB1         | 16     |     | Feedback pin for each channel. These pins are the inputs to the control loop error amplifier and are used to set                                         |  |

| FB2         | 10     |     | the output voltage of the device.                                                                                                                        |  |

| GND         | 3, 13  | _   | Device GND. Connect both pins to the device thermal pad.                                                                                                 |  |

| IN1         | 1, 2   |     | Input pin for LDO1. A 10 μF or greater input capacitor is required to assure robust operation.                                                           |  |

| IN2         | 4, 5   | ] ' | Input pin for LDO2. A 10 μF or greater input capacitor is required to assure robust operation.                                                           |  |

| NR/SS1      | 19     |     | Noise reduction pin for each channel. Connect these pins to an external capacitor to bypass the noise generated                                          |  |

| NR/SS2      | 7      | _   | by the internal band-gap reference. The capacitor reduces the output RMS noise to very low levels and sets the output ramp rate to limit inrush current. |  |

| OUT1        | 14, 15 | 0   | Regulated output 1. A 10 µF or greater capacitor must be connected from this pin to GND to assure stability.                                             |  |

| OUT2        | 11, 12 |     | Regulated output 2. A 10 µF or greater capacitor must be connected from this pin to GND to assure stability.                                             |  |

| PG1         | 17     | 0   | Open-drain power-good indicator pins for the LDO1 and LDO2 output voltages. A 10-kΩ to 100-kΩ external pullup                                            |  |

| PG2         | 9      |     | resistor is required. These pins can be left floating or connected to GND if not used.                                                                   |  |

| SS_CTRL1    | 18     |     | Soft-start control pin for each channel. Connect these pins either to GND or INx to allow normal or fast charging of                                     |  |

| SS_CTRL2    | 8      |     | the NR/SSx capacitor. If a C <sub>NR/SSx</sub> capacitor is not used, SS_CTRLx must be connected to GND to avoid output overshoot.                       |  |

| Thermal pad |        | _   | Connect the thermal pad to the printed circuit board (PCB) ground plane.                                                                                 |  |

(1) Lowercase x indicates that the specification under consideration applies to both channel 1 and channel 2, one channel at a time.

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating junction temperature range and all voltages with respect to GND (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                        | MIN         | MAX                   | UNIT |

|---------------------------------------|--------------------------------------------------------|-------------|-----------------------|------|

|                                       | INx, PGx, ENx <sup>(2)</sup>                           | -0.3        | 7.0                   |      |

|                                       | INx, PGx, ENx (5% duty cycle, pulse duration = 200 μs) | -0.3        | 7.5                   |      |

| Voltage                               | OUTx                                                   | -0.3        | $V_{INx} + 0.3^{(3)}$ | V    |

|                                       | SS_CTRLx                                               | -0.3        | $V_{INx} + 0.3^{(3)}$ |      |

|                                       | NR/SSx, FBx <sup>(2)</sup>                             | -0.3        | 3.6                   |      |

| Comment                               | OUTx <sup>(2)</sup>                                    | Interna     | ally limited          | Α    |

| Current                               | PGx (sink current into device) (2)                     |             | 5                     | mA   |

| Operating junction temperature, T     | <br>I                                                  | -55         | 150                   | °C   |

| Storage temperature, T <sub>stg</sub> |                                                        | <b>-</b> 55 | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                          |                                                                                | VALUE | UNIT |

|--------------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| .,                 | Clastrostatia dia sharas | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                     |                              | MIN | MAX | UNIT |

|---------------------|------------------------------|-----|-----|------|

| $V_{INx}$           | Input supply voltage range   | 1.4 | 6.5 | V    |

| $V_{OUTx}$          | Output voltage range         | 0.8 | 5.0 | V    |

| $I_{OUTx}$          | Output current               | 0   | 1   | Α    |

| C <sub>INx</sub>    | Input capacitor, each input  | 10  |     | μF   |

| C <sub>OUTx</sub>   | Output capacitor             | 10  |     | μF   |

| C <sub>NR/SSx</sub> | Noise-reduction capacitor    |     | 1   | μF   |

| $R_{PG}$            | Power-good pullup resistance | 10  | 100 | kΩ   |

| T <sub>J</sub>      | Junction temperature range   | -40 | 125 | °C   |

#### 6.4 Thermal Information

|                      |                                              | TPS7A88    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTJ (WQFN) | UNIT |

|                      |                                              | 20 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 26.8       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.0        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 8.0        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.4        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Lowercase x indicates that the specification under consideration applies to both channel 1 and channel 2, one channel at a time.

<sup>(3)</sup> The absolute maximum rating is  $V_{INx} + 0.3 \text{ V}$  or 7.0 V, whichever is smaller.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics

over operating temperature range ( $T_J = -40^{\circ}C$  to +125°C),  $V_{INx} = 1.4$  V,  $V_{OUTx(TARGET)} = 0.8$  V,  $I_{OUTx} = 50$  mA,  $V_{ENx} = 1.4$  V,  $C_{OUTx} = 10$   $\mu$ F,  $C_{NR/SSx} = 0$  nF,  $C_{FFx} = 0$  nF, SS\_CTRLx = GND, PGx pin pulled up to  $V_{INx}$  with 100 k $\Omega$ , and for each channel (unless otherwise noted); typical values are at  $T_J = 25^{\circ}C$

|                                 | PARAMETER                                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                    | MIN        | TYP   | MAX        | UNIT              |  |

|---------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------------|-------------------|--|

| $V_{INx}^{(1)}$                 | Input supply voltage range                        |                                                                                                                                                                                                                                                                                                    | 1.4        |       | 6.5        | V                 |  |

| V <sub>REF</sub>                | Reference voltage                                 |                                                                                                                                                                                                                                                                                                    |            | 0.8   |            | V                 |  |

| V <sub>UVLO</sub>               | Input supply UVLO                                 | V <sub>INx</sub> rising                                                                                                                                                                                                                                                                            |            | 1.31  | 1.39       | V                 |  |

| V <sub>HYS</sub>                | $V_{UVLO}$                                        |                                                                                                                                                                                                                                                                                                    |            | 290   |            | mV                |  |

| V                               | Output voltage range                              |                                                                                                                                                                                                                                                                                                    | 0.8 – 1.0% |       | 5.0 + 1.0% | V                 |  |

| $V_{OUTx}$                      | Output voltage accuracy (2)(3)                    | $0.8 \text{ V} \le \text{V}_{\text{OUTx}} \le 5 \text{ V}, 5 \text{ mA} \le \text{I}_{\text{OUTx}} \le 1 \text{ A}$                                                                                                                                                                                | -1.0%      |       | 1.0%       |                   |  |

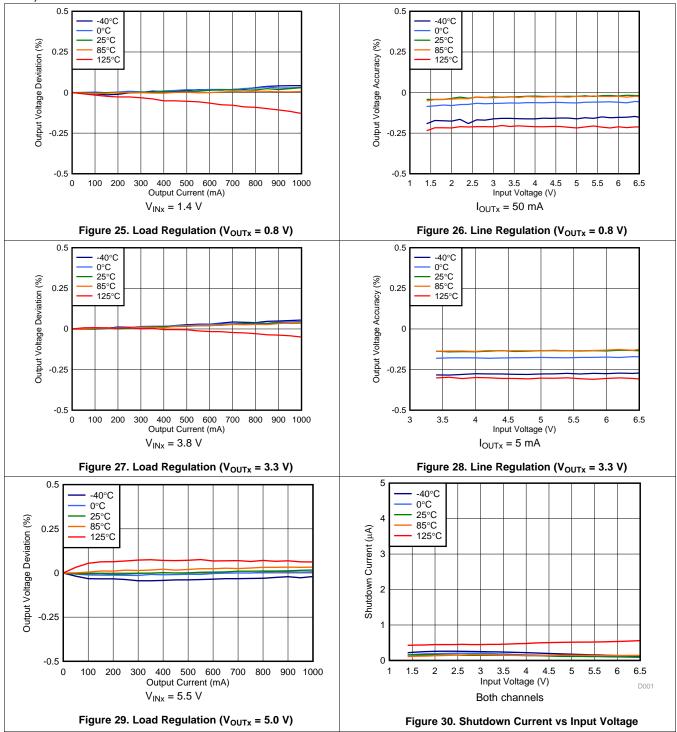

| $\Delta V_{OUTx(\Delta VINx)}$  | Line regulation                                   | $I_{OUTx} = 5 \text{ mA}, 1.4 \text{ V} \le V_{INx} \le 6.5 \text{ V}$                                                                                                                                                                                                                             |            | 0.003 |            | %/V               |  |

| $\Delta V_{OUTx(\Delta IOUTx)}$ | Load regulation                                   | 5 mA ≤ I <sub>OUTx</sub> ≤ 1 A                                                                                                                                                                                                                                                                     |            | 0.03  |            | %/A               |  |

| $V_{DO}$                        | Dropout voltage                                   | $V_{INx} \ge 1.4 \text{ V}, 0.8 \text{ V} \le V_{OUTx} \le 5.0 \text{ V},$<br>$I_{OUTx} = 1 \text{ A}, V_{FBx} = 0.8 \text{ V} - 3\%$                                                                                                                                                              |            |       | 200        | mV                |  |

| I <sub>LIM</sub>                | Output current limit                              | V <sub>OUTx</sub> forced at 0.9 × V <sub>OUTx(TARGET)</sub> ,<br>V <sub>INx</sub> = V <sub>OUTx(TARGET)</sub> + 300 mV                                                                                                                                                                             | 1.5        | 1.7   | 1.9        | Α                 |  |

|                                 | OND six surrent                                   | Both channels enabled, per channel, V <sub>INx</sub> = 6.5 V, I <sub>OUTx</sub> = 5 mA                                                                                                                                                                                                             |            | 2.1   | 3.5        | A                 |  |

| I <sub>GND</sub>                | GND pin current                                   | Both channels enabled, per channel, V <sub>INx</sub> = 1.4 V, I <sub>OUTx</sub> = 1 A                                                                                                                                                                                                              |            |       | 4          | mA                |  |

| I <sub>SDN</sub>                | Shutdown GND pin current                          | Both channels shutdown, per channel, PGx = (open), $V_{\text{INx}} = 6.5 \text{ V}, V_{\text{ENx}} = 0.5 \text{ V}$                                                                                                                                                                                |            | 0.1   | 15         | μΑ                |  |

| I <sub>ENx</sub>                | ENx pin current                                   | V <sub>INx</sub> = 6.5 V, 0 V ≤ V <sub>ENx</sub> ≤ 6.5 V                                                                                                                                                                                                                                           | -0.2       |       | 0.2        | μA                |  |

| V <sub>IL(ENx)</sub>            | ENx pin low-level input voltage (device disabled) |                                                                                                                                                                                                                                                                                                    | 0          |       | 0.4        | V                 |  |

| V <sub>IH(ENx)</sub>            | ENx pin high-level input voltage (device enabled) |                                                                                                                                                                                                                                                                                                    | 1.1        |       | 6.5        | V                 |  |

| I <sub>SS_CTRLx</sub>           | SS_CTRLx pin current                              | $V_{INx} = 6.5 \text{ V}, 0 \text{ V} \le V_{SS\_CTRLx} \le 6.5 \text{ V}$                                                                                                                                                                                                                         | -0.2       |       | 0.2        | μΑ                |  |

| V <sub>IT(PGx)</sub>            | PGx pin threshold                                 | For PGx transitioning low with falling V <sub>OUTx</sub> , expressed as a percentage of V <sub>OUTx(TARGET)</sub>                                                                                                                                                                                  | 82%        | 88.9% | 93%        |                   |  |

| V <sub>hys(PGx)</sub>           | PGx pin hysteresis                                | For PGx transitioning high with rising V <sub>OUTx</sub> , expressed as a percentage of V <sub>OUTx(TARGET)</sub>                                                                                                                                                                                  |            | 1%    |            |                   |  |

| $V_{OL(PGx)}$                   | PGx pin low-level output voltage                  | $V_{OUTx} < V_{IT(PGx)}$ , $I_{PGx} = -1$ mA (current into device)                                                                                                                                                                                                                                 |            |       | 0.4        | V                 |  |

| I <sub>lkg(PGx)</sub>           | PGx pin leakage current                           | $V_{OUTx} > V_{IT(PGx)}, V_{PGx} = 6.5 \text{ V}$                                                                                                                                                                                                                                                  |            |       | 1          | μΑ                |  |

| I <sub>NR/SSx</sub>             | NR/SSx pin charging current                       | $V_{NR/SSx} = GND, 1.4 V \le V_{INx} \le 6.5 V,$<br>$V_{SS\_CTRLx} = GND$                                                                                                                                                                                                                          | 4.0        | 6.2   | 9.0        | μA                |  |

|                                 |                                                   | $V_{NR/SSx} = GND$ , 1.4 $V \le V_{INx} \le 6.5 V$ , $V_{SS\_CTRLx} = V_{INx}$                                                                                                                                                                                                                     | 65         | 100   | 150        |                   |  |

| I <sub>FBx</sub>                | FBx pin leakage current                           | $V_{INx} = 6.5 \text{ V}, V_{FBx} = 0.8 \text{ V}$                                                                                                                                                                                                                                                 | -100       |       | 100        | nA                |  |

| PSRR                            | Power-supply ripple rejection                     |                                                                                                                                                                                                                                                                                                    |            | 40    |            | dB                |  |

| V <sub>n</sub>                  | Output noise voltage                              | $\begin{aligned} & \text{BW} = 10 \text{ Hz to } 100 \text{ kHz}, \text{ V}_{\text{INx}} = 1.8 \text{ V}, \text{ V}_{\text{OUTx}} = 0.8 \text{ V}, \\ & \text{I}_{\text{OUTx}} = 1.0 \text{ A}, \text{ C}_{\text{NR/SSx}} = 1  \mu\text{F}, \text{ C}_{\text{FFx}} = 100 \text{ nF} \end{aligned}$ |            | 3.8   |            | μV <sub>RMS</sub> |  |

|                                 | Noise spectral density                            | f = 10 kHz, V <sub>INx</sub> = 1.8 V, V <sub>OUTx</sub> = 0.8 V,<br>I <sub>OUTx</sub> = 1.0 A, C <sub>NR/SSx</sub> = 10 nF, C <sub>FFx</sub> = 10 nF                                                                                                                                               |            | 11    |            | nV/√Hz            |  |

| R <sub>diss</sub>               | Output active discharge resistance                | V <sub>ENx</sub> = GND                                                                                                                                                                                                                                                                             |            | 250   | _          | Ω                 |  |

| т                               | Thormal abutdown tomporatives                     | Shutdown, temperature increasing                                                                                                                                                                                                                                                                   |            | 160   |            | - °C              |  |

| T <sub>sd</sub>                 | Thermal shutdown temperature                      | Reset, temperature decreasing                                                                                                                                                                                                                                                                      |            | 140   |            |                   |  |

<sup>1)</sup> Lowercase x indicates that the specification under consideration applies to both channel 1 and channel 2, one channel at a time.

<sup>(2)</sup> When the device is connected to external feedback resistors at the FBx pin, external resistor tolerances are not included.

The device is not tested under conditions where V<sub>INx</sub> > V<sub>OUTx</sub> + 2.5 V and I<sub>OUTx</sub> = 1 A because the power dissipation is higher than the maximum rating of the package. Also, this accuracy specification does not apply on any application condition that exceeds the power dissipation limit of the package under test.

# TEXAS INSTRUMENTS

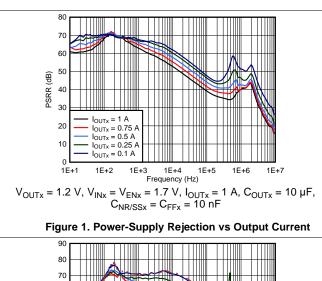

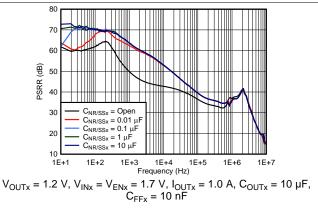

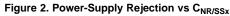

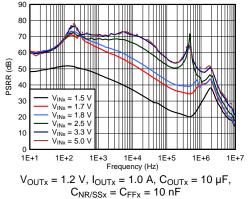

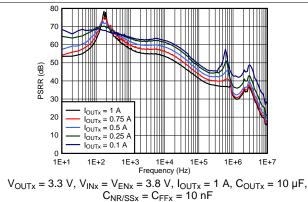

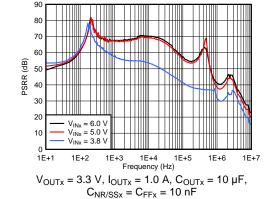

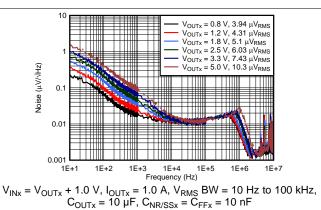

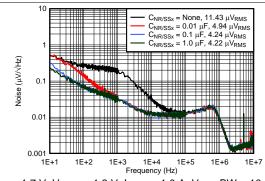

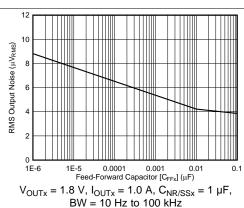

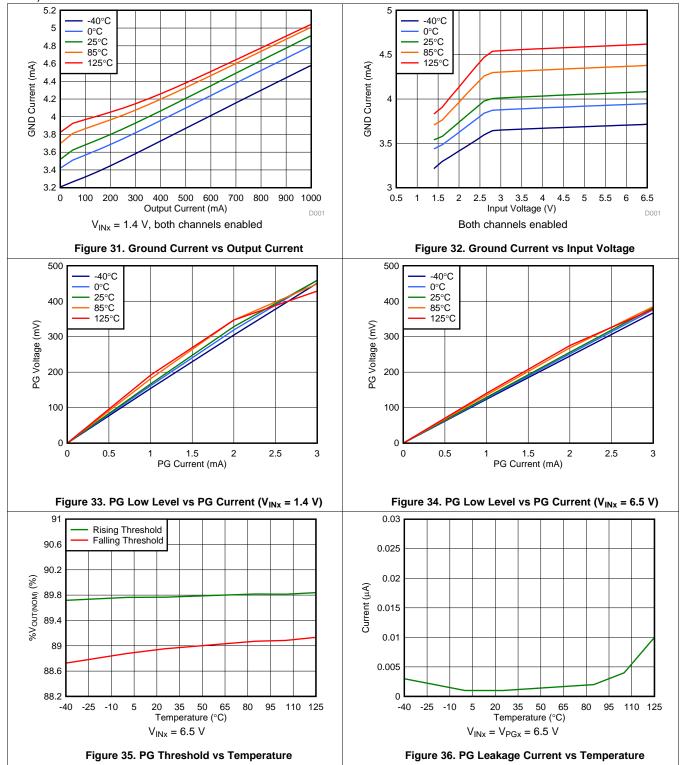

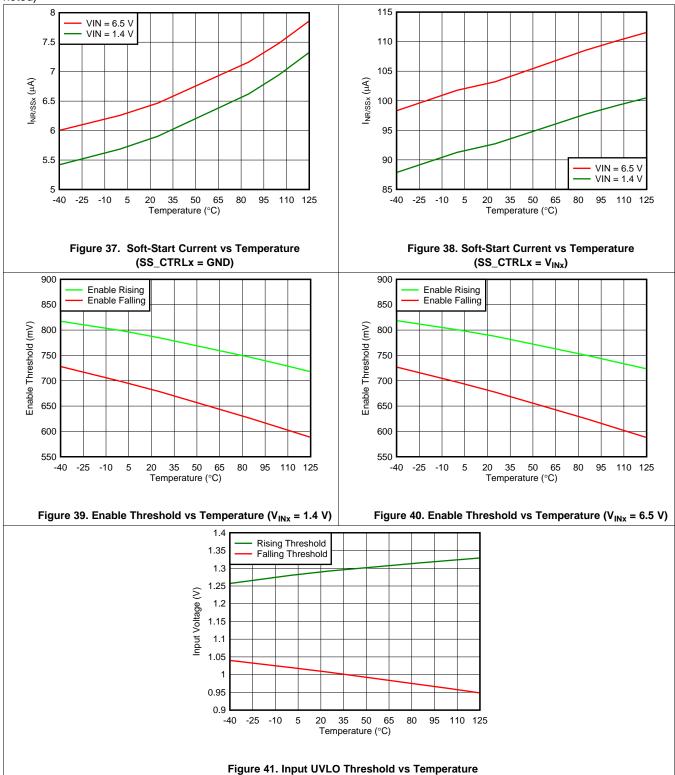

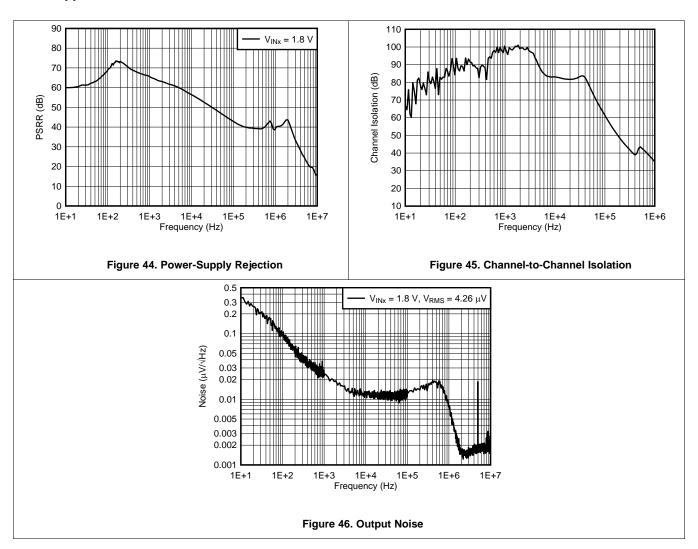

## 6.6 Typical Characteristics

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

Product Folder Links: TPS7A88

Figure 3. Power-Supply Rejection vs Input Voltage

Figure 4. Power-Supply Rejection vs Output Current

$C_{OUTx} = ceramic, C_{FFx} = 10 \text{ nF}$

Figure 6. Power-Supply Rejection vs Input Voltage

Figure 5. Power-Supply Rejection vs Output Capacitance

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

Figure 8. Spectral Noise Density vs Output Voltage

$V_{INx}$  = 1.7 V,  $V_{OUTx}$  = 1.2 V,  $I_{OUTx}$  = 1.0 A,  $V_{RMS}$  BW = 10 Hz to 100 kHz,  $C_{OUTx}$  = 10  $\mu F,\ C_{FFx}$  = 10 nF

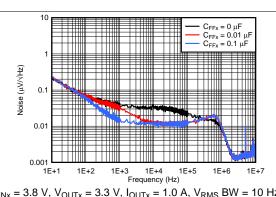

$V_{INx}=3.8$  V,  $V_{OUTx}=3.3$  V,  $I_{OUTx}=1.0$  A,  $V_{RMS}$  BW = 10 Hz to 100 kHz,  $C_{OUTx}=10~\mu F,~C_{NR/SSx}=10~nF$

Figure 10. Spectral Noise Density vs CFFx

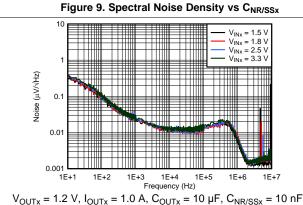

Figure 11. Spectral Noise Density vs V<sub>INx</sub>

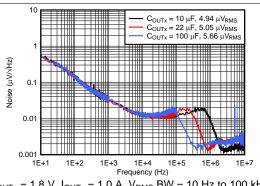

$V_{OUTx}$  = 1.8 V,  $I_{OUTx}$  = 1.0 A,  $V_{RMS}$  BW = 10 Hz to 100 kHz,  $C_{FFx} = 0.01 \mu F$

Figure 12. Spectral Noise Density vs C<sub>OUTx</sub>

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

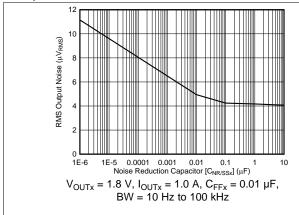

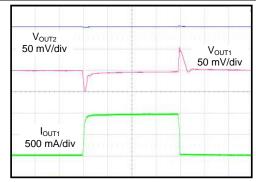

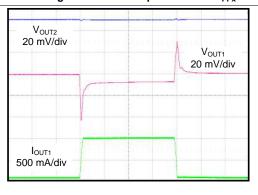

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

Figure 13. RMS Output Noise vs  $C_{NR/SSx}$

Figure 14. RMS Output Noise vs CFFx

$\label{eq:Vinx} Time~(10~\mu s/div)$   $V_{INx} = 1.5~V,~I_{OUTx} = 100~mA~to~1~A~to~100~mA~at~1~A/\mu s,$   $C_{OUTx} = 10~\mu F$

Figure 15. Load Transient Response (V<sub>OUTx</sub> = 1.2 V)

$\label{eq:VINX} Time~(10~\mu s/div)$   $V_{INX}$  = 5.5 V,  $I_{OUTx}$  = 100 mA to 1 A to 100 mA at 1 A/µs,  $C_{OUTx}$  = 10 µF

Figure 16. Load Transient Response (V<sub>OUTx</sub> = 5.0 V)

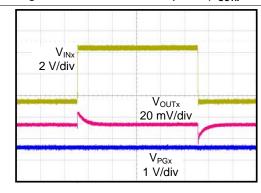

$\begin{aligned} & \text{Time (200 } \mu\text{s/div)} \\ V_{INx} = 1.4 \text{ V to 6.5 V to 1.4 V at 2 V/} \mu\text{s, V}_{OUTx} = 0.8 \text{ V,} \\ I_{OUTx} = 1 \text{ A, C}_{NR/SSx} = C_{FFx} = 10 \text{ nF} \end{aligned}$

Figure 17. Line Transient

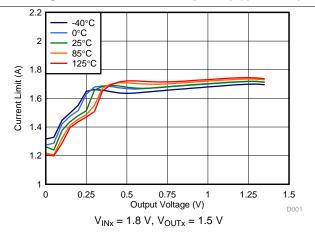

Figure 18. Current Limit Foldback

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

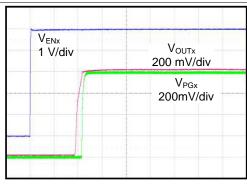

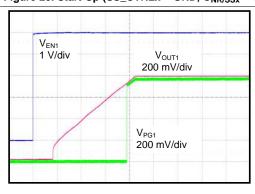

Time (50  $\mu$ s/div) V<sub>INx</sub> = 1.4 V

Figure 19. Start-Up (SS\_CTRLx = GND,  $C_{NR/SSx} = 0$  nF)

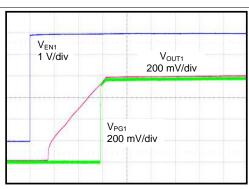

Time (500  $\mu$ s/div) V<sub>INx</sub> = 1.4 V

Figure 20. Start-Up (SS\_CTRLx = GND, C<sub>NR/SSx</sub> = 10 nF)

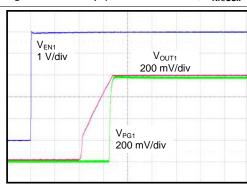

Time (50  $\mu$ s/div) V<sub>INx</sub> = 1.4 V

Figure 21. Start-Up (SS\_CTRLx =  $V_{INx}$ ,  $C_{NR/SSx}$  = 10 nF)

Time (2 ms/div)  $V_{INx} = 1.4 \text{ V}$

Figure 22. Start-Up (SS\_CTRLx =  $V_{INx}$ ,  $C_{NR/SSx}$  = 1  $\mu$ F)

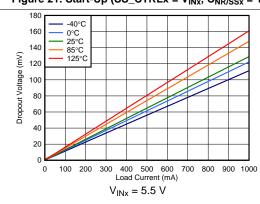

Figure 23. Dropout Voltage vs Output Current

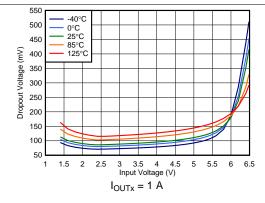

Figure 24. Dropout Voltage vs Input Voltage

Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

at T<sub>J</sub> = 25°C, 1.4 V  $\leq$  V<sub>INx</sub> < 6.5 V, V<sub>INx</sub>  $\geq$  V<sub>OUTx(TARGET)</sub> + 0.3 V, V<sub>OUTx</sub> = 0.8 V, SS\_CTRLx = GND, I<sub>OUTx</sub> = 5 mA, V<sub>ENx</sub> = 1.1 V, C<sub>OUTx</sub> = 10  $\mu$ F, C<sub>NR/SSx</sub> = 0 nF, C<sub>FFx</sub> = 0 nF, PGx pin pulled up to V<sub>OUTx</sub> with 100 k $\Omega$ , and SS\_CTRLx = GND (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

## 7 Detailed Description

#### 7.1 Overview

The TPS7A88 is a dual-channel, low-noise, high PSRR, low dropout (LDO) regulator capable of sourcing a 1-A load with only 200 mV of maximum dropout. The TPS7A88 can operate down to a 1.4-V input voltage and a 0.8-V output voltage. This combination of low-noise, high PSRR, and low dropout voltage makes the device an ideal LDO to power a multitude of loads from noise-sensitive communication components in high-speed communications applications to high-end microprocessors or field-programmable gate arrays (FPGAs).

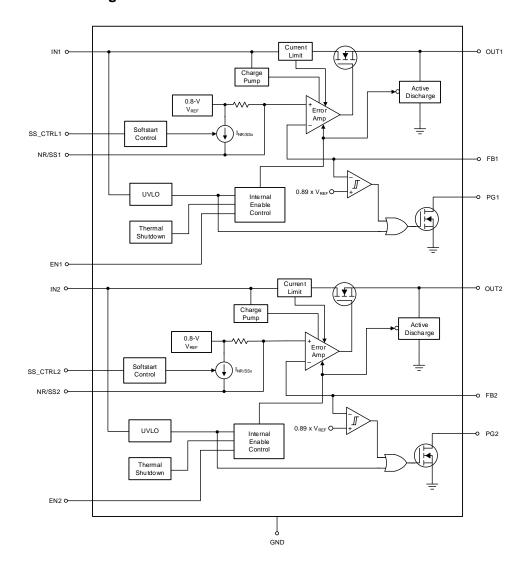

As shown in the *Functional Block Diagram* section, each linear regulator features a low-noise, 0.8-V internal reference that can be filtered externally to obtain even lower output noise. The internal protection circuitry (such as the undervoltage lockout) prevents the device from turning on before the input is high enough to ensure accurate regulation. Foldback current limiting is also included that allows each output to source the rated output current when the output voltage is in regulation but reduce the allowable output current during short-circuit conditions. The internal power-good detection circuit allows users to sequence down-stream supplies and be alerted if the output voltage is below a regulation threshold.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Independent Dual-Channel LDO

The TPS7A88 consists of two completely independent linear regulators that can be used to replace two standalone LDOs, or to provide channel isolation for the same voltage input and outputs. Regardless of the implementation, the TPS7A88 provides excellent regulation to 1% accuracy, excellent dropout voltage, and high output current. If desired, the LDOs can be cascaded to achieve even higher PSRR by connecting the output of one channel to the input of the other channel.

Both channels of the TPS7A88 have an on-board charge pump that is always running to power the error amplifier to drive the gate of the n-channel pass-FET higher than the input voltage. The integrated charge pump allows the low dropout characteristics of the device to be maintained over the entire input voltage range of 1.4 V to 6.5 V.

#### 7.3.2 Output Enable

The enable pins for the TPS7A88 are both active high. The output voltage for each channel is enabled when the corresponding enable pin voltage is greater than  $V_{IH(ENx)}$  and disabled with the enable pin voltage is less than  $V_{IL(ENx)}$ . If control of the output voltage with the enable pin is not needed, then connect the enable pin to the corresponding input.

The TPS7A88 has an internal pulldown MOSFET that connects a 250- $\Omega$  resistor to ground when the device is disabled to actively discharge the output voltage.

#### 7.3.3 Dropout Voltage (V<sub>DO</sub>)

Dropout voltage ( $V_{DO}$ ) is defined as the  $V_{INx} - V_{OUTx}$  voltage at the rated current ( $I_{RATED}$ ), where the main current pass-FET is fully on and in the ohmic region of operation.  $V_{DO}$  indirectly specifies a minimum input voltage above the nominal programmed output voltage at which the output voltage is expected to remain in regulation. If the input falls below the nominal output regulation, then the output follows the input.

Dropout voltage is determined by the  $R_{DS(ON)}$  of the main pass-FET. Therefore, if the LDO operates below the rated current, then the  $V_{DO}$  for that current scales accordingly. The  $R_{DS(ON)}$  for the TPS7A88 can be calculated using Equation 1:

$$R_{DS(ON)} = \frac{V_{DO}}{I_{RATED}}$$

(1)

## 7.3.4 Output Voltage Accuracy

Output voltage accuracy specifies minimum and maximum output voltage error, relative to the expected nominal output voltage stated as a percent. The TPS7A88 features an output voltage accuracy of 1% that includes the errors introduced by the internal reference, load regulation, and line regulation variance across the full range of rated load and line operating conditions over temperature, as specified by the *Electrical Characteristics* table. Output voltage accuracy also accounts for all variations between manufacturing lots.

#### 7.3.5 Low Output Noise

Each channel of the TPS7A88 includes a low-noise reference ensuring minimal output noise in normal operation. Adding a capacitor to the NR/SSx pins provides additional filtering to the internal reference, thus reducing the total output noise. The maximum value recommended for the NR/SSx capacitor is 1  $\mu$ F. Further output noise reduction can be achieved by adding an external  $C_{FF}$  between the SNS pin and the FBx pin.

#### 7.3.6 Internal Protection Circuitry

#### 7.3.6.1 Undervoltage Lockout (UVLO)

Each input of the TPS7A88 has an independent undervoltage lockout (UVLO) circuit that monitors the input voltage, allowing a controlled and consistent turn on and off of the output voltage. To prevent the device from turning off if the input droops during turn on, the UVLO has approximately 285 mV of hysteresis.

## **Feature Description (continued)**

#### 7.3.6.2 Internal Current Limit ( $I_{Cl}$ )

The internal current limit circuit is used to protect the LDO against transient high-load current faults or shorting events. The LDO is not designed to operate in current limit under steady-state conditions. During an overcurrent event where the output voltage is pulled 10% below the regulated output voltage, the LDO sources a constant current as specified in the *Electrical Characteristics* table. When the output voltage falls, the amount of output current is reduced to better protect the device. During a hard short-circuit event, the current is reduced to approximately 1.25 A. See Figure 18 in the *Typical Characteristics* section for more information about the current limit foldback behavior. Note also that when a current-limit event occurs, the LDO begins to heat up because of the increase in power dissipation. The increase in heat can trigger the integrated thermal shutdown protection circuit.

#### 7.3.6.3 Thermal Protection

Each LDO channel of the TPS7A88 contains a thermal shutdown protection circuit to turn off the output current when excessive heat is dissipated in the LDO. Thermal shutdown occurs when the thermal junction temperature  $(T_J)$  of the main pass-FET exceeds 160°C (typical). Thermal shutdown hysteresis assures that the LDO again resets (turns on) when the temperature falls to 140°C (typical). The thermal time-constant of the semiconductor die is fairly short, and thus the output turns on and off at a high rate when thermal shutdown is reached until power dissipation is reduced. Because there are two independent thermal shutdown circuits, one channel can be in thermal shutdown when the other channel is not.

The internal protection circuitry of the TPS7A88 is designed to protect against thermal overload conditions. The circuitry is not intended to replace proper heat sinking. Continuously running the TPS7A88 into thermal shutdown degrades device reliability.

For reliable operation, limit junction temperature to a maximum of 125°C. To estimate the thermal margin in a given layout, increase the ambient temperature until the thermal protection shutdown is triggered using worst-case load and highest input voltage conditions. For good reliability, thermal shutdown must occur at least 40°C above the maximum expected ambient temperature condition for the application. This configuration produces a worst-case junction temperature of 125°C at the highest expected ambient temperature and worst-case load.

## 7.3.7 Output Soft-Start Control

Soft-start refers to the ramp-up characteristic of the output voltage during LDO turn-on after the ENx and UVLO thresholds are exceeded. The noise-reduction capacitor ( $C_{NR/SSx}$ ) serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turn-on. Larger values for the noise-reduction capacitors decrease the noise but also result in a slower output turn-on ramp rate.

The TPS7A88 features an SS\_CTRLx pin for each output. When this pin connected to INx the charging current for the NR/SSx pin is increased to 100  $\mu$ A (typ). The higher current allows use of a much larger noise-reduction capacitor and still maintains a faster soft-start time. When the SS\_CTRLx pin is connected to GND the charging current is reduced to 6.2  $\mu$ A (typ), allowing a slower startup ramp rate. If a noise-reduction capacitor is not used on the NR/SSx pin, tying the SS\_CTRLx pin to VIN can result in output voltage overshoot of approximately 10%. Any overshoot is minimized by connecting the SS\_CTRLx pin to GND or using a capacitor on the NR/SSx pin. To achieve the lowest possible output noise, values for the noise-reduction capacitor can be as high as 10  $\mu$ F. In this case, if a faster soft-start time is needed, connect the SS\_CTRLx pin to VDD.

#### 7.3.8 Power-Good Function

The power-good circuit monitors the voltage at the feedback pin to indicate the status of the output voltage. When the feedback pin voltage falls below the PG threshold voltage ( $V_{IT(PG)}$ ), the PGx pin open-drain output engages and pulls the PGx pin close to GND. When the feedback voltage exceeds the  $V_{IT(PG)}$  threshold by an amount greater than  $V_{HYS(PG)}$ , the PGx pin becomes high impedance. By connecting a pullup resistor to an external supply, any downstream device can receive power good as a logic signal that can be used for sequencing. Make sure that the external pullup supply voltage results in a valid logic signal for the receiving device or devices. Using a pullup resistor from 10 k $\Omega$  to 100 k $\Omega$  is recommended. Using an external reset device such as the TPS3780 is also recommended in applications where high accuracy is needed or in applications where microprocessor resets are needed.

#### Feature Description (continued)

When employing the feed-forward capacitor (CFF), the turn-on time constant for the LDO is increased whereas the power-good output time constant stays the same, resulting in an invalid status of the LDO. To avoid this issue and to receive a valid PG output, ensure that the time constant of both the LDO and the power-good output are matching by adding a capacitor in parallel with the power-good pullup resistor. The state of PG is only valid when the device is operating above the minimum input voltage of the device and power good is asserted regardless of the output voltage state when the input voltage falls below the UVLO threshold minus the UVLO hysteresis. When the input voltage falls below approximately 0.8 V, there is not enough gate drive voltage to keep the open-drain, power-good device turned on and the power-good output is falsely pulled high. Connecting the power-good pullup resistor to the output voltage can help minimize this effect.

#### 7.4 Device Functional Modes

Table 1 provides a quick comparison between the normal, dropout, and disabled modes of operation.

**Table 1. Device Functional Modes Comparison**

| OPERATING MODE          | PARAMETER                          |                         |                                     |                |  |

|-------------------------|------------------------------------|-------------------------|-------------------------------------|----------------|--|

| OPERATING MODE          | V <sub>INx</sub>                   | ENx                     | I <sub>OUTx</sub>                   | T <sub>J</sub> |  |

| Normal <sup>(1)</sup>   | $V_{INx} > V_{OUTx(nom)} + V_{DO}$ | $V_{ENx} > V_{IH(ENx)}$ | I <sub>OUTx</sub> < I <sub>CL</sub> | $T_J < T_{sd}$ |  |

| Dropout <sup>(1)</sup>  | $V_{INx} < V_{OUTx(nom)} + V_{DO}$ | $V_{ENx} > V_{IH(ENx)}$ | I <sub>OUTx</sub> < I <sub>CL</sub> | $T_J < T_{sd}$ |  |

| Disabled <sup>(2)</sup> | UVLO                               | $V_{ENx} < V_{IL(ENx)}$ | _                                   | $T_J > T_{sd}$ |  |

<sup>(1)</sup> All table conditions must be met.

#### 7.4.1 Normal Operation

The device regulates to the nominal output voltage when all of the following conditions are met.

- The input voltage is greater than the nominal output voltage plus the dropout voltage (V<sub>OUTx(nom)</sub> + V<sub>DO</sub>)

- The enable voltage has previously exceeded the enable rising threshold voltage and has not yet decreased below the enable falling threshold

- The output current is less than the current limit ( $I_{OUTx} < I_{CL}$ )

- The device junction temperature is less than the thermal shutdown temperature  $(T_J < T_{sd})$

#### 7.4.2 Dropout Operation

If the input voltage is lower than the nominal output voltage plus the specified dropout voltage, but all other conditions are met for normal operation, the device operates in dropout. In this mode, the output voltage tracks the input voltage. During this mode, the transient performance of the device becomes significantly degraded because the pass device is in a triode state and no longer controls the current through the LDO. Line or load transients in dropout can result in large output-voltage deviations.

When the device is in a steady dropout state (defined as when the device is in dropout,  $V_{INx} < V_{OUTx(NOM)} + V_{DO}$ , right after being in a normal regulation state, but not during startup), the pass-FET is driven as hard as possible when the control loop is out of balance. During the normal time required for the device to regain regulation, V<sub>INx</sub> ≥  $V_{OUTx(NOM)} + V_{DO}$ ,  $V_{OUTx}$  overshoots if the input voltage slew rate is 0.1 V/µs or faster.

#### 7.4.3 Disabled

The outputs of the TPS7A88 can be shutdown by forcing the enable pins below 0.4 V. When disabled, the pass device is turned off, internal circuits are shutdown, and the output voltage is actively discharged to ground by an internal switch from the output to ground.

The device is disabled when any condition is met.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The TPS7A88 is a linear voltage regulator operating from 1.4 V to 6.5 V on the input and regulates voltages between 0.8 V to 5.0 V within 1% accuracy and a 1-A maximum output current. Efficiency is defined by the ratio of output voltage to input voltage because the TPS7A88 is a linear voltage regulator. To achieve high efficiency, the dropout voltage  $(V_{INx} - V_{OUTx})$  must be as small as possible, thus requiring a very low dropout LDO. Successfully implementing an LDO in an application depends on the application requirements. This section discusses key device features and how to best implement them to achieve a reliable design.

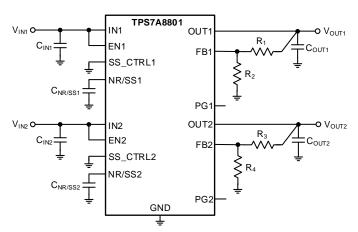

#### 8.1.1 Adjustable Outputs

The output voltages of the TPS7A8801 can be adjusted from 0.8 V to 5.0 V by using resistor divider networks as shown in Figure 42.

Figure 42. Adjustable Operation

$R_1$ ,  $R_3$  and  $R_2$ ,  $R_4$  can be calculated for any output voltage range using Equation 2. This resistive network must provide a current equal to or greater than 5  $\mu$ A for optimum noise performance.

$$R_1, R_3 = R_2, R_4 \left( \frac{V_{OUTx}}{V_{REF}} - 1 \right), \text{ where } \frac{\left| V_{REF(max)} \right|}{R_2, R_4} > 5 \,\mu\text{A}$$

(2)

If greater voltage accuracy is required, take into account the output voltage offset contributions resulting from the feedback pin current ( $I_{FB}$ ) and use 0.1% tolerance resistors.

#### **Application Information (continued)**

Table 2 shows the resistor combination required to achieve a few of the most common rails using commercially-available, 0.1%-tolerance resistors to maximize nominal voltage accuracy and also abiding to the formula given in Equation 2.

Table 2. Recommended Feedback-Resistor Values

| V <sub>OUT×(TARGET)</sub>     | FEEDBACK RESISTOR VALUES <sup>(1)</sup> |                                      |  |  |

|-------------------------------|-----------------------------------------|--------------------------------------|--|--|

| V <sub>OUTx(TARGET)</sub> (V) | R <sub>1</sub> , R <sub>3</sub> (kΩ)    | R <sub>2</sub> , R <sub>4</sub> (kΩ) |  |  |

| 0.8                           | Short                                   | Open                                 |  |  |

| 1.00                          | 2.55                                    | 10.2                                 |  |  |

| 1.20                          | 5.9                                     | 11.8                                 |  |  |

| 1.50                          | 9.31                                    | 10.7                                 |  |  |

| 1.80                          | 1.87                                    | 1.5                                  |  |  |

| 1.90                          | 15.8                                    | 11.5                                 |  |  |

| 2.50                          | 2.43                                    | 1.15                                 |  |  |

| 3.00                          | 3.16                                    | 1.15                                 |  |  |

| 3.30                          | 3.57                                    | 1.15                                 |  |  |

| 5.00                          | 10.5                                    | 2                                    |  |  |

<sup>(1)</sup> R<sub>1</sub>, R<sub>3</sub> are connected from OUTx to FBx; R<sub>2</sub>, R<sub>4</sub> are connected from FBx to GND; see Figure 42.

#### 8.1.2 Start-Up

#### 8.1.2.1 Enable (ENx) and Undervoltage Lockout (UVLO)

The TPS7A88 only turns on when ENx and UVLO are above their respective voltage thresholds. Each input to the TPS7A88 has an independent UVLO circuit that monitors the input voltage to allow a controlled and consistent turn on and off. To prevent the device from turning off if the input droops during turn on, the UVLO has approximately 285 mV of hysteresis. The ENx signal for each output allows independent logic-level turn-on and shutdown of the LDO when the input voltage is present. It is recommended to connect ENx directly to INx if independent turn-on is not needed.

#### 8.1.2.2 Noise-Reduction and Soft-Start Capacitor (C<sub>NR/SSx</sub>)

Each output of the TPS7A88 features a programmable, monotonic, voltage-controlled soft-start that is set with an external capacitor ( $C_{NR/SSx}$ ). This soft-start eliminates power-up initialization problems when powering FPGAs, digital signal processors (DSPs), or other processors. The controlled voltage ramp of the output also reduces peak inrush current during start-up, thus minimizing start-up transients to the input power bus.

To achieve a linear and monotonic start-up, the TPS7A88 error amplifier tracks the voltage ramp of the external soft-start capacitor until the voltage exceeds the internal reference. The soft-start ramp time depends on the soft-start charging current  $(I_{NR/SSx})$ , the soft-start capacitance  $(C_{NR/SSx})$ , and the internal reference  $(V_{REF})$ . The approximate soft-start ramp time  $(t_{SSx})$  can be calculated with Equation 3:

$$t_{SSx} = (V_{REF} \times C_{NR/SSx}) / I_{NR/SSx}$$

(3)

Note that the value for  $I_{NR/SSx}$  is determined by the state of the SS\_CTRLx pin. When the SS\_CTRLx pin is connected to GND, the typical value for the  $I_{NR/SSx}$  current is 6.2  $\mu$ A. Connecting the SS\_CTRLx pin to INx increases the typical soft-start charging current to 100  $\mu$ A. The larger charging current for  $I_{NR/SSx}$  is useful if smaller start-up ramp times are needed or when using larger noise reduction capacitors. Values for the soft-start charging currents are provided in the *Electrical Characteristics* table.

For low-noise applications, the noise-reduction capacitor (connected to the NR/SSx pin of the LDO) forms an RC filter for filtering out noise that is ordinarily amplified by the control loop and appears on the output voltage. For low-noise applications, a 10-nF to 1- $\mu$ F C<sub>NR/SSx</sub> is recommended. Larger values for C<sub>NR/SSx</sub> can be used; however, above 1- $\mu$ F there is little benefit in lowering the output voltage noise.

(4)

#### 8.1.2.3 Soft-Start and Inrush Current

Soft-start refers to the gradual ramp-up characteristic of the output voltage after the ENx and UVLO thresholds are exceeded. The noise-reduction capacitor serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turn-on.

Inrush current is defined as the current into the LDO at the INx pin during start-up. Inrush current then consists primarily of the sum of load and current used to charge the output capacitor. This current is difficult to measure because the input capacitor must be removed, which is not recommended. However, the inrush current can be estimated by Equation 4:

$$I_{OUTx}(t) = \left(\frac{C_{OUTx} \times dV_{OUTx}(t)}{dt}\right) + \left(\frac{V_{OUTx}(t)}{R_{LOADx}}\right)$$

where:

- V<sub>OUTx</sub>(t) is the instantaneous output voltage of the turn-on ramp

- dV<sub>OUTx</sub>(t) / dt is the slope of the V<sub>OUTx</sub> ramp and

- R<sub>LOAD</sub> is the resistive load impedance

#### 8.1.3 Capacitor Recommendation

The TPS7A88 is designed to be stable using low equivalent series resistance (ESR) ceramic capacitors at the inputs, outputs, and noise-reduction pins. Multilayer ceramic capacitors have become the industry standard for these types of applications and are recommended, but must be used with good understanding of their limitations. Ceramic capacitors that employ X7R-, X5R-, and COG-rated dielectric materials provide relatively good capacitive stability across temperature, whereas the use of Y5V-rated capacitors is discouraged precisely because the capacitance varies so widely. In all cases, ceramic capacitors vary a great deal with operating voltage and temperature and the design engineer must be aware of these characteristics. As a rule of thumb, ceramic capacitors are recommended to be derated by 50%. To compensate for this derating, increase the capacitor value by 100%. The input and output capacitors recommended herein account for a capacitance derating of 50%.

Attention must be given to the input capacitance to minimize transient input droop during load current steps. An input capacitor of 10  $\mu$ F or greater provides the desired effect and does not affect stability. Note that simply using large ceramic input capacitances can also cause unwanted ringing at the output if the input capacitor (in combination with the wire-lead inductance) creates a high-Q peaking effect during transients. For example, a 5-nH lead inductance and a 10- $\mu$ F input capacitor form an LC filter with a resonance frequency of 712 kHz that is near the edge of the open-loop bandwidth. Short, well-designed interconnect traces to the upstream supply minimize this effect without adding damping. Damping of unwanted ringing can be accomplished by using a tantalum capacitor, with a few hundred milliohms of ESR, in parallel with the ceramic input capacitor.

## 8.1.3.1 Input and Output Capacitor Requirements ( $C_{INX}$ and $C_{OUTX}$ )

The TPS7A88 is designed and characterized for operation with ceramic capacitors of 10  $\mu$ F or greater at the input and output. Locate the input and output capacitors as near as practical to the respective input and output pins to minimize the trace inductance from the capacitor to the device.

#### 8.1.3.2 Feed-Forward Capacitor (C<sub>FFx</sub>)

Although a feed-forward capacitor ( $C_{FFx}$ ), from the FBx pin to the OUTx pin is not required to achieve stability, a 10-nF, feed-forward capacitor optimizes the noise and PSRR performance. A higher capacitance  $C_{FF}$  can be used; however, the startup time is longer and the power-good signal can incorrectly indicate that the output voltage has settled. For a detailed description, see application report *Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator*, SBVA042.

#### 8.1.4 AC Performance

LDO ac performance for a dual-channel device includes power-supply rejection ratio, channel-to-channel output isolation, load step transient response, and output noise. These metrics are primarily a function of open-loop gain and bandwidth, phase margin, and reference noise.

#### 8.1.4.1 Power-Supply Ripple Rejection (PSRR)

PSRR is a measure of how well the LDO control loop rejects ripple noise from the input source to make the dc output voltage as noise-free as possible across the frequency spectrum (usually 10 Hz to 10 MHz). Even though PSRR is a loss in noise signal amplitude, the PSRR curves in the *Electrical Characteristics* table are shown as positive values in decibels (dB) for convenience. Equation 5 gives the PSRR calculation as a function of frequency where input noise voltage  $[V_{S(INx)}(f)]$  and output noise voltage  $[V_{S(OUTx)}(f)]$  are understood to be purely sinusoidal signals.

$$PSRR (dB) = 20 Log_{10} \left( \frac{V_{INx}(f)}{V_{OUTx}(f)} \right)$$

(5)

Noise that couples from the input to the internal reference voltage for the control loop is also a primary contributor to reduced PSRR magnitude and bandwidth. This reference noise is greatly filtered by the noise-reduction capacitor at the NR/SSx pin of the LDO in combination with an internal filter resistor for improved PSRR at lower frequencies.

The LDO is often employed not only as a dc-dc regulator, but also to provide exceptionally clean power-supply voltages that exhibit ultra-low noise and ripple to power-sensitive system components. This usage is especially true for the TPS7A88.

The TPS7A88 features an innovative circuit to boost the PSRR between 200 kHz and 1 MKz; see Figure 4. To achieve the maximum benefit of this PSRR boost circuit, using a capacitor with a minimum impedance in the 100-kHz to 1-MHz band is recommended.

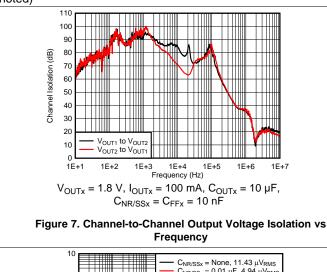

#### 8.1.4.2 Channel-to-Channel Output Isolation and Crosstalk

Output isolation is a measure of how well the device prevents voltage disturbances on one output from affecting the other output. This attenuation appears in load transient tests on the other output; however, to numerically quantify the rejection, the output channel isolation is expressed in decibels (dB). In order to characterize the output channel isolation both ac disturbances in output voltages are understood to be purely sinusoidal signals.

Output isolation performance is a strong function of the PCB layout. See the *Layout* section on how to best optimize the isolation performance.

#### 8.1.4.3 Load-Step Transient Response

The load-step transient response is the output voltage response by the LDO to a step change in load current, whereby output voltage regulation is maintained. The depth of charge depletion immediately after the load step is directly proportional to the amount of output capacitance. However, larger output capacitances function to decrease any voltage dip or peak occurring during a load step but also decrease the control-loop bandwidth, thereby slowing response.

The LDO cannot sink charge, therefore the control loop must turn off the main pass-FET to wait for the charge to deplete when the output load is removed.

#### 8.1.4.4 Noise

The TPS7A88 is designed for system applications where minimizing noise on the power-supply rail is critical to system performance. This scenario is the case for phase-locked loop (PLL)-based clocking circuits where minimum phase noise is all important, or in test and measurement systems where even small power-supply noise fluctuations can distort instantaneous measurement accuracy.

LDO noise is defined as the internally-generated intrinsic noise created by the semiconductor circuits alone. This noise is the sum of various types of noise (such as shot noise associated with current-through-pin junctions, thermal noise caused by thermal agitation of charge carriers, flicker noise, or 1/f noise and dominates at lower frequencies as a function of 1/f).

See the marketing white paper, How to Measure LDO Noise, SLYY076 for further details.

Noise is affected by the choice of noise reduction capacitor  $C_{NR/SSx}$  and feedforward capacitor  $C_{FFx}$ . See the *Noise-Reduction and Soft-Start Capacitor* ( $C_{NR/SSx}$ ) and *Feed-Forward Capacitor* ( $C_{FFx}$ ) sections for additional design information.

#### 8.1.5 Power Dissipation (P<sub>D</sub>)

Circuit reliability demands that proper consideration be given to device power dissipation, location of the circuit on the printed circuit board (PCB), and correct sizing of the thermal plane. The PCB area around the regulator must be as free as possible of other heat-generating devices that cause added thermal stresses.

To first-order approximation, power dissipation in the regulator depends on the input-to-output voltage difference and load conditions. P<sub>D</sub> can be calculated using Equation 6:

$$P_{D} = (V_{OUTx} - V_{INx}) \times I_{OUTx}$$

(6)

An important note is that power dissipation can be minimized, and thus greater efficiency achieved, by proper selection of the system voltage rails. Proper selection allows the minimum input voltage necessary for output regulation to be obtained.

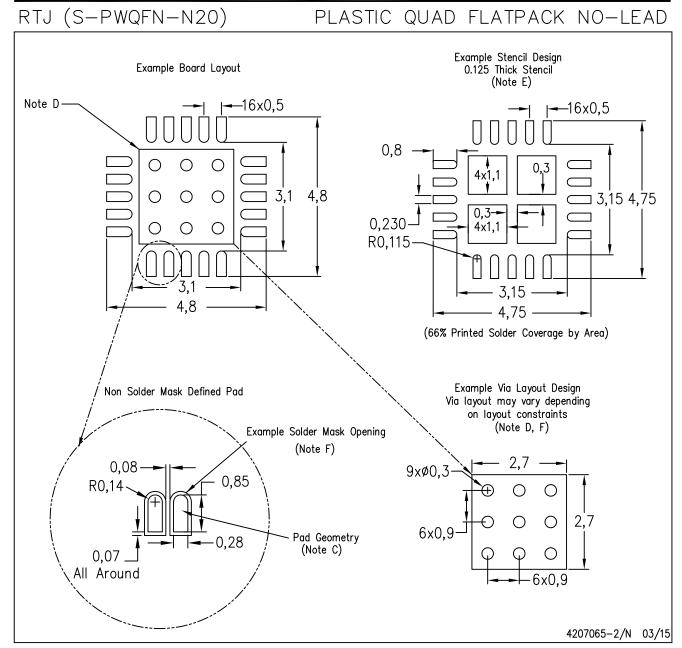

The primary heat conduction path for the RTJ package is through the thermal pad to the PCB. Solder the thermal pad to a copper pad area under the device. This pad area contains an array of plated vias that conduct heat to any inner plane areas or to a bottom-side copper plane.

The maximum power dissipation determines the maximum allowable ambient temperature  $(T_A)$  for the device. Power dissipation and junction temperature are most often related by the junction-to-ambient thermal resistance  $(\theta_{JA})$  of the combined PCB and device package and the temperature of the ambient air  $(T_A)$ , according to Equation 7.

$$T_{J} = T_{A} + (\theta_{JA} \times P_{D}) \tag{7}$$

Unfortunately, the thermal resistance  $(\theta_{JA})$  is highly dependent on the heat-spreading capability built into the particular PCB design, and therefore varies according to the total copper area, copper weight, and location of the planes. The  $\theta_{JA}$  recorded in the *Thermal Information* table is determined by the JEDEC standard, PCB, and copper-spreading area and is only used as a relative measure of package thermal performance.

## 8.1.6 Estimating Junction Temperature

The JEDEC standard now recommends the use of psi  $(\Psi)$  thermal metrics to estimate the junction temperatures of the LDO when in-circuit on a typical PCB board application. These metrics are not strictly speaking thermal resistances, but rather offer practical and relative means of estimating junction temperatures. These psi metrics are determined to be significantly independent of the copper-spreading area. The key thermal metrics  $(\Psi_{JT}$  and  $\Psi_{JB})$  are given in the *Thermal Information* table and are used in accordance with Equation 8.

$$\Psi_{JT}$$

:  $T_J = T_T + \Psi_{JT} \times P_D$

$\Psi_{JB}$ :  $T_J = T_B + \Psi_{JB} \times P_D$

where:

- P<sub>D</sub> is the power dissipated as explained in Equation 6

- T<sub>T</sub> is the temperature at the center-top of the device package and

- T<sub>B</sub> is the PCB surface temperature measured 1 mm from the device package and centered on the package edge

(8)

#### 8.2 Typical Application

This section discusses the implementation of the TPS7A88 to regulate from a common input voltage to two output voltages of the same value. This is a common application where two noise-sensitive loads must have the same supply voltage but have high channel-to-channel isolation. The schematic for this application circuit is provided in Figure 43.

Figure 43. Application Example

#### 8.2.1 Design Requirements

For the design example shown in Figure 43, use the parameters listed in Table 3 as the input parameters.

**PARAMETER DESIGN REQUIREMENT** Input voltages (V<sub>IN1</sub> and V<sub>IN2</sub>) 1.8 V, ±3%, provided by the dc-dc converter switching at 750 kHz Maximum ambient operating temperature 55°C Output voltages (V<sub>OUT1</sub> and VOUT2) 1.2 V, ±1%, output voltages are isolated Output currents ( $I_{OUT2}$  and  $I_{OUT2}$ ) 1.0 A (maximum), 10 mA (minimum) Channel-to-channel isolation Isolation greater than 50 dB at 100 kHz  $< 5 \mu V_{RMS}$ , bandwidth = 10 Hz to 100 kHz RMS noise PSRR at 750 kHz >40 dBStartup time < 5 ms

**Table 3. Design Parameters**

#### 8.2.2 Detailed Design Procedure

The output voltages can be set to 1.2 V by selecting the correct values for R<sub>1</sub>, R<sub>3</sub> and R<sub>2</sub>, R<sub>4</sub>; see Equation 2.

Input and output capacitors are selected in accordance with the *Capacitor Recommendation* section. Ceramic capacitances of 10  $\mu$ F for both inputs and outputs are selected.

To satisfy the required startup time ( $t_{SSx}$ ) and still maintain low-noise performance, a 0.1- $\mu$ F  $C_{NR/SSx}$  is selected for both channels with SS\_CTRL1 and SS\_CTRL2 connected to  $V_{IN1}$  and  $V_{IN2}$ , respectively. This value is calculated with Equation 9.

$$t_{SSx} = (V_{REF} \times C_{NR/SSx}) / I_{NR/SSx}$$

(9)

With a 1.0-A maximum load, the internal power dissipation is 600 mW per channel or 1.2 W total, which corresponds to a 40°C junction temperature rise. With an 55°C maximum ambient temperature, the junction temperature is at 95°C. To minimize noise, a feed-forward capacitance (C<sub>FF</sub>) of 10 nF is selected.

Channel-to-channel isolation depends greatly on the layout of the design. To minimize crosstalk between the outputs, keep the output capacitor grounds on separate sides of the design. See the *Layout* section for an example of how to layout the TPS7A88 to achieve best PSRR, channel-to-channel isolation, and noise.

#### 8.2.3 Application Curves

#### 8.3 Do's and Don'ts

Table 4 lists the recommended guidelines for the TPS7A88.

Table 4. Recommended Guidelines for Designing with the TPS7A88

| DO'S                                                                                                        | DON'TS                                                                        |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Do place at least one 10-µF ceramic capacitor as close as possible to each output of the device.            | Do not place either output capacitor more than 10 mm away from the regulator. |

| Do connect a 10-µF or larger low equivalent series resistance (ESR) capacitor across each input pin to GND. | Do not exceed the absolute maximum ratings.                                   |

| Do follow the recommended layout in Figure 47                                                               | Do not leave the enable pins floating.                                        |

## 9 Power Supply Recommendations

Both inputs of the TPS7A88 are designed to operate from an input voltage range between 1.4 V and 6.5 V. The input voltage range must provide adequate headroom in order for the device to have a regulated output. This input supply must be well regulated. If the input supply is noisy, additional input capacitors with low ESR can help improve the output noise performance.

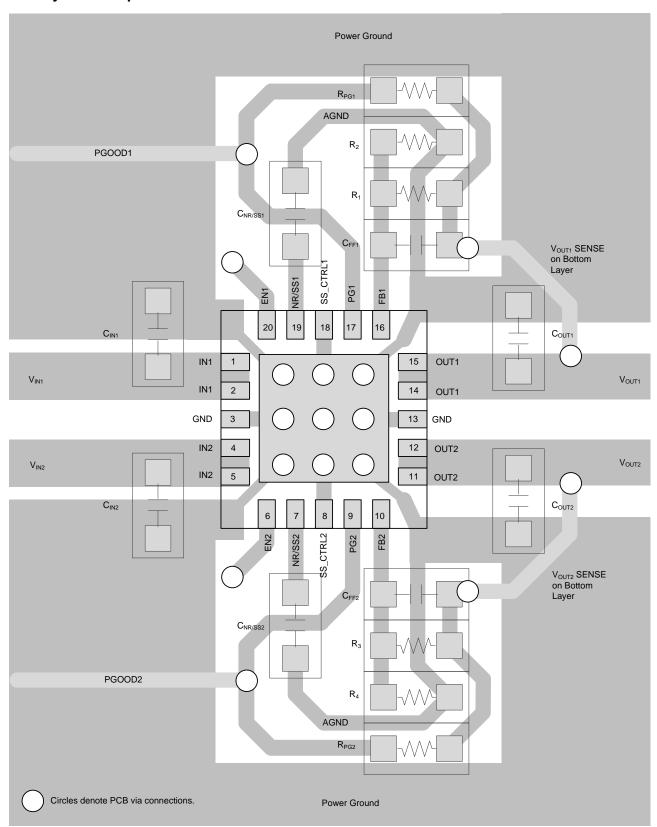

## 10 Layout

## 10.1 Layout Guidelines

General guidelines for linear regulator designs are to place all circuit components on the same side of the circuit board and as near as practical to the respective LDO pin connections. Place ground return connections to the input and output capacitor, and to the LDO ground pin as close to each other as possible, connected by a wide, component-side, copper surface. The use of vias and long traces to create LDO circuit connections is strongly discouraged and negatively affects system performance.

#### 10.1.1 Board Layout

To maximize the ac performance of the TPS7A88, following the layout example illustrated in Figure 47 is recommended. This layout isolates the analog ground (AGND) from the noisy power ground. Components that must be connected to the quiet analog ground are the noise reduction capacitors ( $C_{NR/SSx}$ ) and the lower feedback resistors ( $R_2$ ,  $R_4$ ). These components must have a separate connection back to the power pad of the device. To minimize crosstalk between the two outputs, the output capacitor grounds are positioned on opposite sides of the layout and only connect back to the device at opposite sides of the thermal pad. TI recommends connecting the GND pins directly to the thermal pad and not to any external plane.

To maximize the output voltage accuracy, the connection from each output voltage back to top output divider resistors ( $R_1$  and  $R_3$ ) must be made as close as possible to the load. This method of connecting the feedback trace eliminates the voltage drop from the device output to the load.

To improve thermal performance, a  $3 \times 3$  thermal via array must connect the thermal pad to internal ground planes. A larger area for the internal ground planes improves the thermal performance and lowers the operating temperature of the device.

## 10.2 Layout Example

Figure 47. TPS7A88 Example Layout

## 11 Device and Documentation Support

#### 11.1 Device Support

#### 11.1.1 Development Support

#### 11.1.1.1 Evaluation Modules

An evaluation module (EVM) is available to assist in the initial circuit performance evaluation using the TPS7A88. The summary information for this fixture is shown in Table 4.

Table 5. Design Kits & Evaluation Modules<sup>(1)</sup>

| Name                                                    | Part #         |  |  |  |

|---------------------------------------------------------|----------------|--|--|--|

| TPS7A88 Low-Dropout Voltage Regulator Evaluation Module | TPS7A88EVM-776 |  |  |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the device product folder at www.ti.com.

The EVM can be requested at the Texas Instruments web site (www.ti.com) through the TPS7A88 product folder.

#### 11.1.1.2 Spice Models

Computer simulation of circuit performance using spice is often useful when analyzing the performance of analog circuits and systems. A spice model for the TPS7A88 is available through the TPS7A88 product folder under simulation models.

#### 11.1.2 Device Nomenclature

Table 6. Ordering Information<sup>(1)</sup>

| PRODUCT               | DESCRIPTION                                                                                                                        |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TPS7A88xx <b>YYYZ</b> | YYY is the package designator.  XX represents the output voltage. 01 is the adjustable output version.  Z is the package quantity. |  |  |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the device product folder at www.ti.com.

#### 11.2 Documentation Support

#### 11.2.1 Related Documentation

TPS3780 Data Sheet, SBVS250

TPS7A88EVM User's Guide, SBVU027

Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator, SBVA042

How to Measure LDO Noise, SLYY076

#### 11.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Trademarks

DSP, E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

6-Dec-2015

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TPS7A8801RTJR    | ACTIVE | QFN          | RTJ     | 20   | 3000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | TPS7A88        | Samples |

| TPS7A8801RTJT    | ACTIVE | QFN          | RTJ     | 20   | 250  | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | TPS7A88        | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.