# Multi-Rail Power Supply for Microcontrollers in Safety-Critical Applications

Check for Samples: TPS65381-Q1

## FEATURES

- Multi-Rail Power Supply Supporting Among Others:

- Texas Instruments TMS570LS Series 16/32-Bit RISC Flash Microcontroller

- Supply Rails:

- Input voltage range:

- 5.8 V to 36 V (CAN, I/O, MCU Core, and Sensor Supply Regulators Functional)

- 4.5 V to 5.8 V (3.3-V I/O and MCU Core Voltage Functional)

- 6-V Asynchronous Switch-Mode Pre-Regulator With Internal FET, 1.5-A Current Limit, and Temperature Protection

- 5-V (CAN) Supply Voltage, Linear Regulator With Internal FET, and Temperature Protection

- 3.3-V or 5-V MCU I/O Voltage, Linear Regulator With Internal FET, and Temperature Protection

- 0.8-V to 3.3-V Adjustable MCU Core Voltage, Linear Regulator Controller With External FET

- Sensor Supply: Linear Tracking Regulator With Tracking Input, 300-mA Current Limit, Temperature Protection, and Protection Against Short to Battery and Short to Ground

- Reverse Battery Protection With External FET Allowing for Low-Voltage Operation Down To 4.5 V

- Charge Pump: Typ. 12 V Above Battery Voltage

- Power Supply / System Monitoring:

- Under- and Overvoltage Monitoring on All Regulator Outputs, Battery Voltage, and Internal Supplies

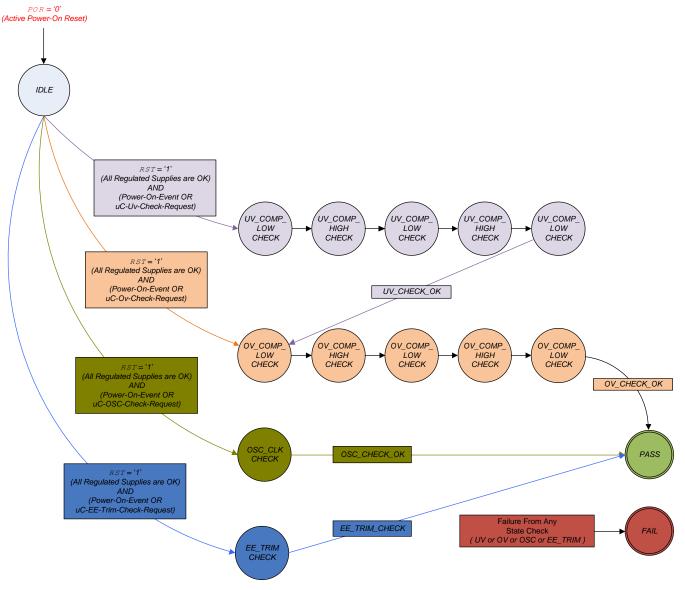

- Self-Check on All Voltage Monitoring (During Power Up and After Power Up Initiated by External MCU)

- Independent Voltage References for Regulator References and Voltage Monitoring. Voltage-Monitoring Circuitry With Separate Battery Voltage Input

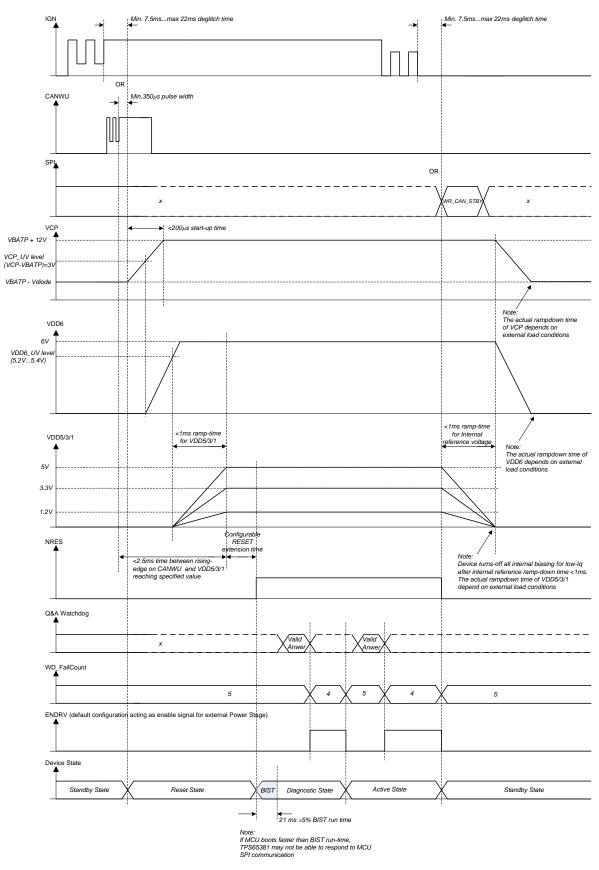

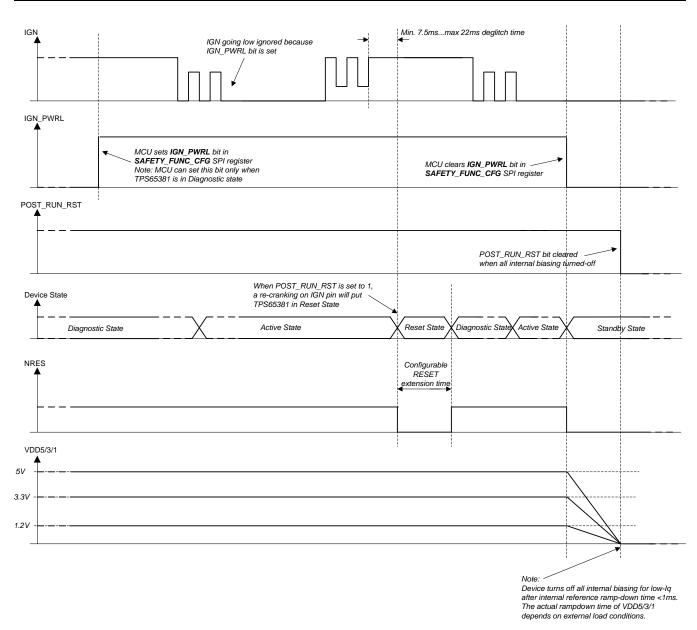

- Wake-Up Through Deglitched Ignition Signal

- Wake-Up Through CAN WAKEUP Pin

- Enable Circuit for Peripheral Device Wake-Up Circuitry or Power Stages

- Junction Temperature Sensing With Shutdown Thresholds

- Microcontroller Interface

- Open/Close Window or Question-Answer Watchdog Function

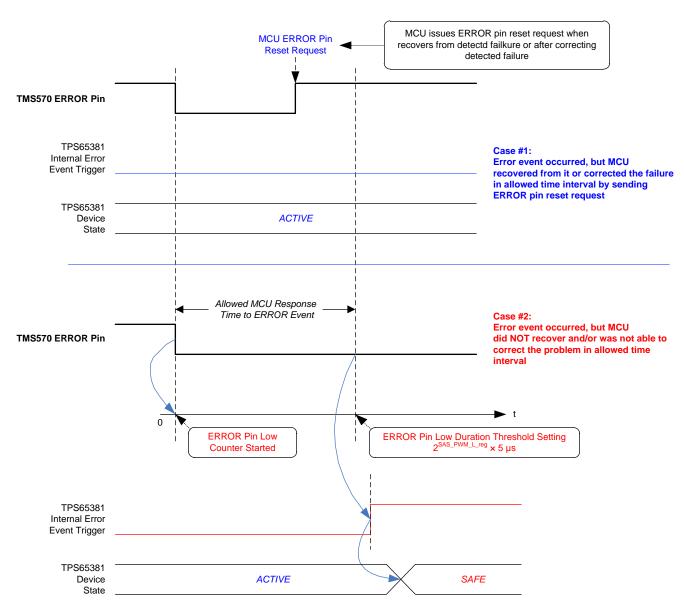

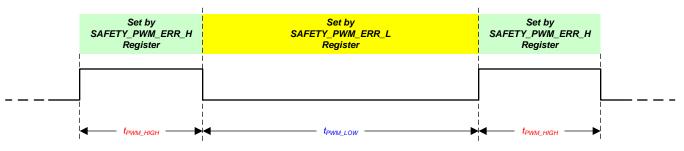

- MCU Error-Signal Monitor (Supports TI TMS570 MCU Mode or Other MCUs with PWM-Like Signaling)

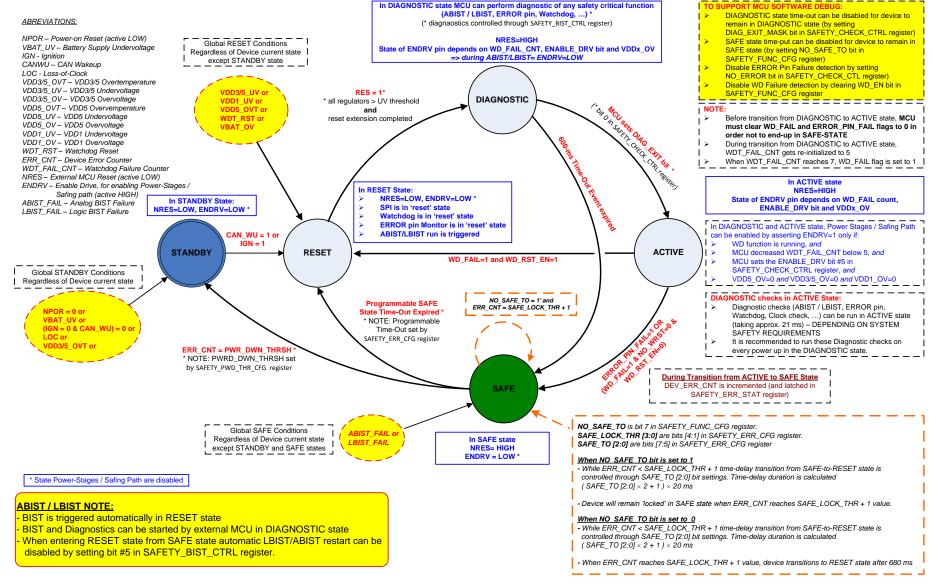

- DIAGNOSTIC State for Performing Device Self-Tests, Diagnostics, and External Interconnect Checks.

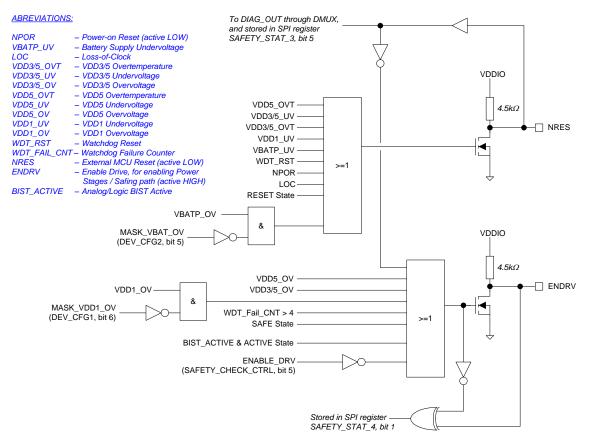

- Safe-State for Device and System

Protection on Error Event Detection

- Clock Monitor for Internal Oscillators

- Self-Tests for Analog and Digital Critical Circuits Executed With Every Device Power Up or Activated by External MCU in DIAGNOSTIC State

- CRC on Non-Volatile Memory and Device/System Configuration Registers

- Reset circuit for MCU

- SPI Interface

- Configuring IC Registers

- Watchdog Question-Answering

- Diagnostic Readout

- Compliant With 3.3-V and 5-V Logic Levels

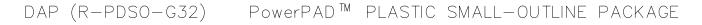

- Package: 32-Pin HTSSOP PowerPAD™ Package

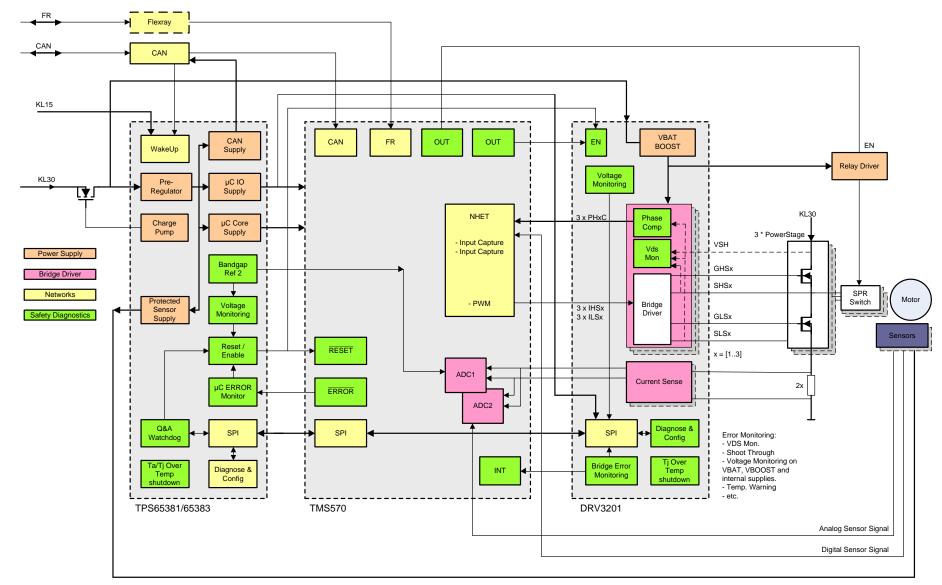

# APPLICATIONS

- Safety Critical Automotive Applications

- Electrical Power Steering (EPS, EHPS)

- Braking

- Suspension

- Airbag

- Industrial Safety Applications

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments. SLVSBC4 - MAY 2012

## DESCRIPTION

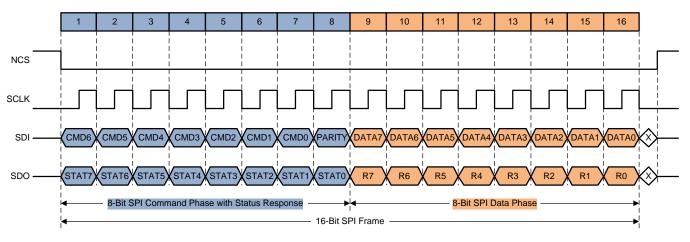

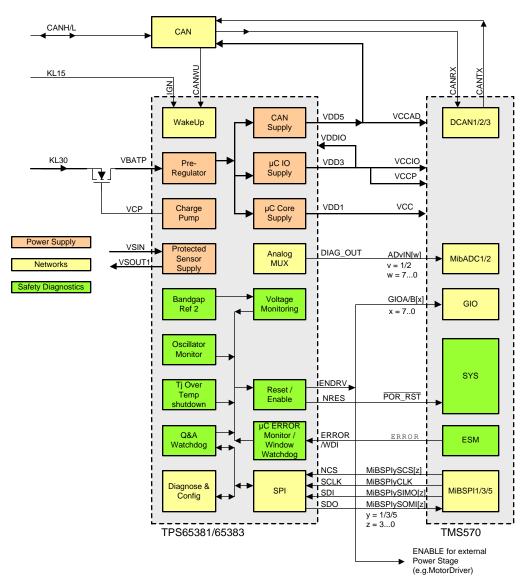

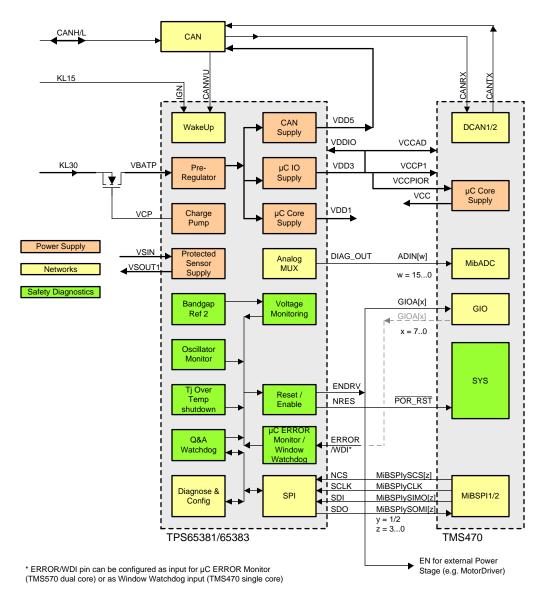

The TPS65381-Q1 is a multi-rail power supply designed to supply microcontrollers in safety-critical applications, such as those found in automotive. The devices supports Texas Instruments' TMS570LS series 16/32-bit RISC flash MCU and other microcontrollers with dual-core lockstep (LS) or loosely coupled architectures (LC).

The TPS65381-Q1 integrates multiple supply rails to power the MCU, CAN or FlexRay, and an external sensor. An asynchronous buck switch-mode power-supply converter with internal FET converts the input battery voltage to a 6-V pre-regulator output. This 6 V is used to supply the other regulators.

A fixed 5-V linear regulator with an internal FET is integrated to be used as, for example, a CAN supply. A second linear regulator, also with an internal FET, regulates the 6 V to a selectable 5-V or 3.3-V MCU I/O voltage.

The TPS65381-Q1 comprises a linear regulator controller with external FET and resistor divider, regulating the 6 V to an externally adjustable core voltage of between 0.8 V and 2.6 V.

The device comprises a sensor supply with short-to-ground and short-to-battery protection. This supply can thus be used to power a sensor outside the electronic control unit (ECU).

The device has an integrated charge pump to provide overdrive voltage for the internal regulators. Reversebattery protection can be obtained by using the charge pump output to control an external NMOS transistor. This solution allows for a lower minimum-battery-voltage operation compared to a traditional reverse-battery blocking diode.

The device monitors under- and overvoltage on all regulator outputs, battery voltage, and internal supply rails. A second band-gap reference, independent from the main band-gap reference, is used for the under- and overvoltage monitoring, to avoid any drifts in the main band-gap reference from being undetected. In addition, regulator current limits and temperature protections are implemented.

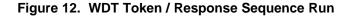

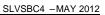

The TPS65381-Q1 functional safety architecture features a question-answer watchdog, MCU error-signal monitor, clock monitoring on internal oscillators, self-check on clock monitor, CRC on non-volatile memory, and a reset circuit for the MCU. A built-in self-test (BIST) allows for monitoring the device functionality at start-up. A dedicated DIAGNOSTIC state allows the MCU to check TPS65381-Q1 safety functions.

The TPS65381-Q1 is offered in an HTSSOP-32 PowerPAD package.

SLVSBC4 -MAY 2012

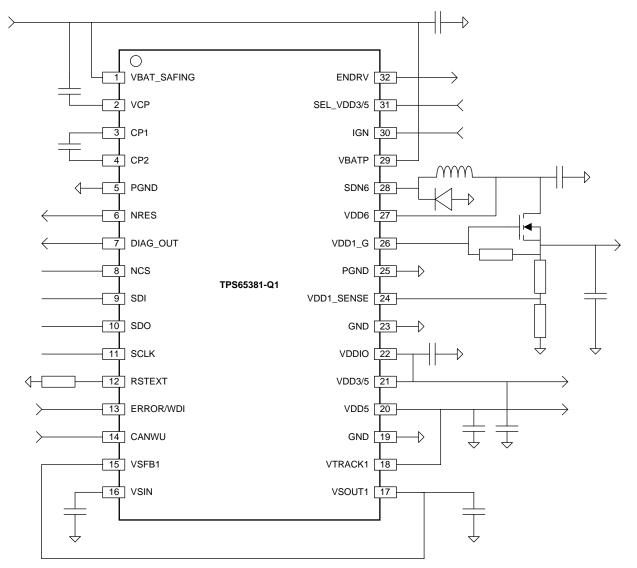

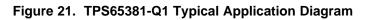

Figure 1. Typical Application Diagram

SLVSBC4 -MAY 2012

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

| POS   |                                              |                                                                               | VALUE      | UNIT |

|-------|----------------------------------------------|-------------------------------------------------------------------------------|------------|------|

| M1.1  | Protected battery voltage                    | VBATP, VBAT_SAFING, VSIN                                                      | -0.3 to 40 | V    |

| M1.2  | Charge-pump voltages                         | VCP, CP1                                                                      | -0.3 to 50 | V    |

| M1.3  | Charge-pump pumping capacitor voltage        | CP2                                                                           | -0.3 to 40 | V    |

| M1.4  | VDD6 switching-node voltage                  | SDN6                                                                          | -0.3 to 40 | V    |

| M1.5  | VDD6 output voltage                          | VDD6                                                                          | -0.3 to 40 | V    |

| M1.6  | VDD5 output voltage                          | VDD5                                                                          | -0.3 to 7  | V    |

| M1.7  | VDD3/5 output voltage                        | VDD3/5                                                                        | -0.3 to 7  | V    |

| M1.8  | VDD1_G voltage                               | VDD1_G                                                                        | -0.3 to 15 | V    |

| M1.10 | VDD1_SENSE voltage                           | VDD1_SENSE                                                                    | -0.3 to 7  | V    |

| M1.11 | Sensor supply tracking voltage               | VTRACK1                                                                       | -0.3 to 40 | V    |

| M1.12 | Sensor supply feedback voltage               | VSFB1                                                                         | -2 to 40   | V    |

| M1.13 | Sensor supply output voltage                 | VSOUT1                                                                        | -2 to 40   | V    |

| M1.14 | Analog/digital ref. output voltage           | DIAG_OUT                                                                      | -0.3 to 7  | V    |

| M1.15 | Logic I/O voltage                            | VDDIO, ERROR/WDI, ENDRV, NRES, NCS, SDI, SDO, SCLK, DMUXO, SEL_VDD3/5, RSTEXT | -0.3 to 7  | V    |

| M1.16 | IGN wake-up                                  | IGN                                                                           | -7 to 40   | V    |

| M1.17 | CAN wake-up                                  | CANWU                                                                         | -0.3 to 40 | V    |

| M1.18 | Operating virtual junction temperature range | TJ                                                                            | -40 to 150 | °C   |

| M1.19 |                                              | HBM on sensor supply pins VSOUT1 and VSFB1                                    | ±4         |      |

| M1.20 | - ESD                                        | HBM on all other pins                                                         | ±2         | kV   |

| M1.21 |                                              | CDM on corner pins                                                            | ±750       |      |

| M1.22 |                                              | CDM on all other pins                                                         | ±500       | V    |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted.

## THERMAL INFORMATION

|                    |                                                             | TPS65381   |                |

|--------------------|-------------------------------------------------------------|------------|----------------|

|                    | THERMAL METRIC <sup>(1)</sup>                               | HTSSOP-DAP | UNITS          |

|                    |                                                             | 32 PINS    |                |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 31.4       |                |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 14.3       |                |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance <sup>(4)</sup>         | 15.3       | 8 <b>0</b> 444 |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.3        | °C/W           |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter <sup>(6)</sup> | 15.2       |                |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.6        |                |

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953. (1)

The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as (2) specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5)The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted

(6) from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific (7)JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## **RECOMMENDED OPERATING CONDITIONS**

over operating temperature range (unless otherwise noted)

| Pos   |                                                                                                                                                                                                                         | MIN | TYP | MAX | UNIT |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R1.1  | Input supply-voltage range on VBATP pins for initial power up                                                                                                                                                           | 5.8 |     |     | V    |

| R1.2  | Input supply voltage range on VBATP<br>– VDD5, VDD3/5, VDD1 outputs functional (no undervoltage)                                                                                                                        | 5.8 | 12  | 36  | V    |

| R1.3  | Input supply-voltage range on VBATP<br>– VDD6, VDD5 regulators in low dropout, VDD3 and VDD1 regulator outputs functional (no<br>undervoltage). VSOUT1 either functional or in low dropout, depending on configuration. | 4.5 |     |     | V    |

| R1.3a | Input supply voltage for VBAT_SAFING (when below minimum, device does not start up and NRES, ENDRV is pulled low.) 4.2                                                                                                  |     |     | 40  | V    |

| R1.4  | VDDIO supply-voltage range (Note: VDDIO has internal pullup diode to VDD3/5.)                                                                                                                                           | 3.3 |     | 5   | V    |

| R1.5  | Current consumption in standby mode (all regulator outputs disabled)                                                                                                                                                    |     |     | 75  | μA   |

## **ELECTRICAL CHARACTERISTICS**

Over operating ambient temperature T<sub>J</sub> = -40°C to 150°C and operating VBATP range 6 V to 36 V (unless otherwise noted)

| POS   |                             | PARAMETER TEST CONDITIONS                                                       |                                                                                                          |      |    | MAX | UNIT |  |

|-------|-----------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|----|-----|------|--|

| VDD6- | DD6-BUCK With Internal FET  |                                                                                 |                                                                                                          |      |    |     |      |  |

| AN    | C <sub>VDD6</sub>           | Value of output ceramic capacitor                                               | ESR range 100 m $\Omega$ to 300 m $\Omega$                                                               | 22   |    | 47  | μF   |  |

| AN    | L <sub>VDD6</sub>           | Value of inductor                                                               |                                                                                                          | 22   | 33 |     | μH   |  |

| A1.1  | VDD6                        | VDD6 output voltage                                                             | Average dc value excl. ripple and load transients, VBAT > 7 V, $0 < I_{VDD6} < 1.3 A$ , inclding dc line | -10% | 6  | 10% | V    |  |

|       |                             |                                                                                 | and load regulation, temperature<br>drift, and long-term drift                                           |      |    |     |      |  |

| A1.2  | I <sub>VDD6</sub>           | I <sub>VDD5</sub> + I <sub>VDD3</sub> + I <sub>VDD1</sub> + I <sub>VSOUT1</sub> | Load currents from VDD5,<br>VDD3_5, VDD1 and VSOUT1;<br>VDD6 not recommended to be<br>loaded directly    |      |    | 1.3 | A    |  |

| A1.3  | Vdropout6                   | VDD6 output dropout voltage Vdropout6 = (VBATP – SDN6)                          | I <sub>VDD6</sub> = 1.3 A                                                                                |      |    | 0.6 | V    |  |

| A1.4  | I <sub>VDD6_limit</sub>     | Current limit                                                                   |                                                                                                          | 1.5  |    | 2.5 | А    |  |

| VDD6- | VDD6-BUCK With Internal FET |                                                                                 |                                                                                                          |      |    |     |      |  |

PRODUCT PREVIEW

SLVSBC4 -MAY 2012

# **ELECTRICAL CHARACTERISTICS (continued)**

| POS   |                         | PARAMETER                                                                              | TEST CONDITIONS                                                                                                                                                                                                                        | MIN          | TYP        | MAX          | UNIT |

|-------|-------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|------|

| A1.5  | F <sub>sw_VDD6</sub>    | Switching frequency                                                                    | In continuous mode and steady state                                                                                                                                                                                                    | -10%         | 440        | 10%          | kHz  |

| A1.6  | DC <sub>VDD6</sub>      | Ton/Tperiod                                                                            | VBATP > 7 V                                                                                                                                                                                                                            | 7%           |            | 100%         |      |

| A1.7  | Tprot <sub>VDD6</sub>   | Temperature protection threshold                                                       | Global shutdown                                                                                                                                                                                                                        | 175          |            | 210          | °C   |

| VDD5  | - LDO With Intern       | al FET                                                                                 | •                                                                                                                                                                                                                                      |              |            |              |      |

| AN    | C <sub>VDD5</sub>       | Value of output ceramic capacitor                                                      | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                                                                                                                               | 1            |            | 5            | μF   |

| 2.1   | VDD5                    | VDD5 output voltage                                                                    | $0 < I_{VDD}5 < 300$ mA, including line<br>and load regulation, temperature<br>drift, and long-term drift                                                                                                                              | -2%          | 5          | 2%           | V    |

| 2.2   | I <sub>VDD5</sub>       | VDD5 output current                                                                    | Min. load with internal resistor of typ. 660 $\Omega$                                                                                                                                                                                  |              |            | 300          | mA   |

| 2.3   | VDD5 <sub>dyn</sub>     | VDD5 output voltage dynamic                                                            | Load step 10% to 90% in 1 $\mu s,$ with 5- $\mu F$ $C_{VDD5}$                                                                                                                                                                          | 4.85         | 5          | 5.15         | V    |

| 2.4   | VDD5 <sub>max</sub>     | Maximum VDD5 output voltage during VBATP step from 5.5 V to 13.5 V within 10 $\mu s$   | $C_{VDD5}$ = 5 µF, $I_{VDD5}$ < 300 mA                                                                                                                                                                                                 |              |            | 5.5          | V    |

| 2.5   | Vdropout5               | VDD5 output dropout voltage Vdropout5 = (VDD6-<br>VDD5)                                | I <sub>VDD5</sub> < 300 mA                                                                                                                                                                                                             |              |            | 0.30         | V    |

| 2.6   | PSRR <sub>VDD5</sub>    | Power supply rejection ratio                                                           | 50 < f < 20 kHz,VBATP = 10 V, U<br>= 4 Vpp                                                                                                                                                                                             | 40           |            |              | dB   |

| 2.7   | LnReg <sub>VDD5</sub>   | Line regulation (I <sub>VDD5</sub> constant)                                           | $C_{VDD5} = 5 \ \mu\text{F}, \ 0 < I_{VDD5} < 300 \ \text{mA}$<br>$0 < I_{VDD5} < 300 \ \text{mA}, \ 8 \ \text{V} < \text{VBATP}$<br>$< 19 \ \text{V}$                                                                                 | -25          |            | 25           | mV   |

| 2.8   | LdReg <sub>VDD5</sub>   | Load regulation (VDD6 constant)                                                        | 0 < I <sub>VDD5</sub> < 300 mA, 8 V < VBATP<br>< 19 V                                                                                                                                                                                  | -25          |            | 25           | mV   |

| 2.9   | TmpCo <sub>VDD5</sub>   | Temperature drift                                                                      | Normalized to 25°C value                                                                                                                                                                                                               | -0.5         |            | 0.5          | %    |

|       | 1 4003                  |                                                                                        | Empty                                                                                                                                                                                                                                  |              |            |              |      |

| 2.11  | dVDD5/dt                | dV/dt at VDD5 at startup                                                               |                                                                                                                                                                                                                                        | 5            |            | 50           | V/ms |

| 2.12  | t <sub>delayVDD5</sub>  | VDD5 voltage stabilization delay                                                       | Maximum delay between rising<br>edge on CANWU pin till VDD5<br>reaching end-value within 2%                                                                                                                                            |              |            | 2.5          | ms   |

| 2.13  | Tprot <sub>VDD5</sub>   | Temperature protection threshold                                                       | VDD5 switch-off                                                                                                                                                                                                                        | 175          |            | 210          | °C   |

| 2.14  | I <sub>VDD5 limit</sub> | Current limit                                                                          |                                                                                                                                                                                                                                        | 350          |            | 650          | mA   |

| VDD3/ | 5 – LDO With Inte       | rnal FET                                                                               | <u> </u>                                                                                                                                                                                                                               |              |            |              |      |

| AN    | C <sub>VDD3/5</sub>     | Value of output ceramic capacitor                                                      | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                                                                                                                               | 1            |            | 5            | μF   |

| 3.1   | VDD3/5                  | VDD3/5 output voltage                                                                  | $\begin{array}{l} \text{SEL_VDD3/5 pin open: 3.3 V} \\ \text{SEL_V_{DD3/5} to ground: 5 V} \\ \text{O} < I_{\text{VDD3/5}} < 300 \text{ mA, inclusive of} \\ \text{line and load regulation,} \\ \text{temperature drift} \end{array}$ | -2%          | 3.35       | +2%          | V    |

| 3.2   | I <sub>VDD3/5</sub>     | VDD3/5 output current                                                                  | Min. load with internal resistor: 440 $\Omega$ for 3.3-V setting 660 $\Omega$ for 5-V setting                                                                                                                                          |              |            | 300          | mA   |

| 3.3   | VDD3/5 <sub>dyn</sub>   | VDD3/5 output voltage dynamic                                                          | Depending on 3.3 V/5 V setting Load step 10% to 90% in 1 $\mu$ s, with 5 $\mu$ F CVDD3/5                                                                                                                                               | 3.17<br>4.85 | 3.3<br>5.0 | 3.43<br>5.15 | †    |

| 3.4   | VDD3/5 <sub>max</sub>   | Maximum VDD3/5 output voltage during VBATP step from 5.5 V to 13.5 V within 10 $\mu s$ | Depending on 3.3 V/5 V setting $C_{\text{VDD3/5}}$ = 5 $\mu\text{F},~\text{I}_{\text{VDD3/5}}$ < 300 mA                                                                                                                                |              |            | 3.6<br>5.5   | V    |

| 3.5   | Vdropout3/5             | VDD3/5 output dropout voltage Vdropout3/5= (VDD6-<br>VDD3/5)                           | I <sub>VDD3/5</sub> < 300 mA                                                                                                                                                                                                           |              |            | 0.3          | ۷    |

| 3.6   | PSRR <sub>VDD3/5</sub>  | Power-supply rejection ratio                                                           | $\begin{array}{l} 50 < f < 20 \ \text{kHz}, \ \text{VBATP} = 10 \ \text{V}, \\ U = 4 \ \text{Vpp} \\ C_{\text{VDD3/5}} = 5 \ \mu\text{F}, \ 0 < I_{\text{VDD3/5}} < 300 \\ \text{mA} \end{array}$                                      | 40           |            |              | dB   |

| 3.7   | LnReg <sub>VDD3/5</sub> | Line regulation (I <sub>VDD3</sub> constant)                                           | 0 < I <sub>VDD3/5</sub> < 300 mA,<br>8 V < VBATP < 19 V                                                                                                                                                                                | -25          |            | 25           | mV   |

| 3.8   | LdReg <sub>VDD3/5</sub> | Load regulation (VDD5 constant)                                                        | 0 < I <sub>VDD3/5</sub> < 300 mA<br>8 V < VBATP < 19 V                                                                                                                                                                                 | -25          |            | 25           | mV   |

| 3.9   | TmpCo <sub>VDD3/5</sub> | Temperature drift                                                                      | Normalized to 25°C value                                                                                                                                                                                                               | -0.5%        |            | 0.5%         |      |

|       |                         |                                                                                        | Empty                                                                                                                                                                                                                                  |              |            |              |      |

|       |                         |                                                                                        |                                                                                                                                                                                                                                        |              |            |              |      |

SLVSBC4 -MAY 2012

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

## Over operating ambient temperature $T_J = -40^{\circ}$ C to 150°C and operating VBATP range 6 V to 36 V (unless otherwise noted)

| POS    |                           | PARAMETER                                                                            | TEST CONDITIONS                                                                                                                                                                                                  | MIN    | ΤΥΡ | MAX      | UNIT |

|--------|---------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------|------|

| 3.11   | dVDD35/dt                 | dV/dt at VDD3/5 at start-up                                                          | Depending on 3.3 V/5 V setting                                                                                                                                                                                   | 3<br>5 |     | 30<br>50 | V/ms |

| 3.12   | t <sub>VDD3/5</sub>       | VDD3/5 voltage stabilization delay                                                   | Maximum delay after CAN wake-<br>up for VDD3/5 output to settle                                                                                                                                                  |        |     | 2.5      | ms   |

| 3.13   | Tprot <sub>VDD3/5</sub>   | Temperature protection threshold                                                     | Global shutdown                                                                                                                                                                                                  | 175    |     | 210      | °C   |

| 3.14   | I <sub>VDD3_5_limit</sub> | Current limit                                                                        |                                                                                                                                                                                                                  | 350    |     | 650      | mA   |

| 3.15   | Ipu_SEL_VDD3/5            | Pullup current on SEL_VDD3/5 pin                                                     |                                                                                                                                                                                                                  |        |     | 20       | μA   |

| VDD1 · | - LDO With Externa        | IFET                                                                                 |                                                                                                                                                                                                                  |        |     |          |      |

| AN     | Vgs(th)                   | Gate threshold voltage, external FET                                                 | ID = 1 mA                                                                                                                                                                                                        | 0.3    |     | 3        | V    |

| AN     | Ciss                      | Gate capacitance, external FET                                                       | VGS = 0 V                                                                                                                                                                                                        |        |     | 3200     | pF   |

| AN     | Qgate                     | Gate Charge ext. FET                                                                 | VGS = 0 V to 10 V                                                                                                                                                                                                |        |     | 70       | nC   |

| AN     | gfs                       | Forward transconductance, external FET                                               | ID = 50 mA                                                                                                                                                                                                       | 0.4    |     |          | S    |

| AN     | C <sub>VDD1</sub>         | Value of output ceramic capacitor                                                    | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                                                                                                         | 5      |     | 40       | μF   |

| A4.1   | VDD1                      | VDD1 output voltage                                                                  | Depends on external resistive divider                                                                                                                                                                            | 0.8    |     | 3.3      | V    |

| A4.2   | VDD1 <sub>SENSE</sub>     | VDD1 reference voltage                                                               | 10 mA < $I_{VDD1}$ < 600 mA,<br>including line and load regulation,<br>temperature drift and long-term<br>drift                                                                                                  | -2%    | 0.8 | 2%       | V    |

| A4.3   | I <sub>VDD1</sub>         | VDD1 output current                                                                  | Minimum current realized with external resistive divider                                                                                                                                                         | 10     |     | 600      | mA   |

| A4.4   | VDD1 <sub>G</sub>         | VDD1_G output voltage                                                                | Referred to GND                                                                                                                                                                                                  |        |     | 15       | V    |

| A4.5   | VDD1 <sub>G_off</sub>     | VDD1_G voltage in OFF condition                                                      | Test condition: 20 µA into VDD1_G pin                                                                                                                                                                            |        |     | 0.3      | V    |

| A4.6   | I VDD1 <sub>G</sub>       | VDD1 G DC load current                                                               |                                                                                                                                                                                                                  |        |     | 200      | μA   |

| A4.7   | VDD1 <sub>dyn</sub>       | VDD1 output voltage dynamic                                                          | Load step 10% to 90% in 1 $\mu$ s, with 40 $\mu$ F C <sub>VDD1</sub>                                                                                                                                             | -4%    |     | 4%       | V    |

| A4.8   | VDD1 <sub>max</sub>       | Maximum VDD1 output voltage during VBATP step from 5.5 V to 13.5 V within 10 $\mu s$ | C <sub>VDD1</sub> > 6 μF, I <sub>VDD1</sub> < 600 mA                                                                                                                                                             |        |     | 10%      | V    |

| A4.9   | PSRR <sub>VDD1</sub>      | Power-supply rejection ratio                                                         | $\begin{array}{l} 50 < f < 20 \text{ kHz}, \text{VBATP} = 10 \text{ V}, \\ U = 4 \text{ Vpp}, \\ C_{\text{VDD1}} = 10 \ \mu\text{F}, \ 10 \ \text{mA} < \text{I}_{\text{VDD1}} < \\ 600 \ \text{mA} \end{array}$ | 40     |     |          | dB   |

| A4.10  | LnReg <sub>VDD1</sub>     | Line regulation on VDD1_SENSE (I <sub>VDD1</sub> constant)                           | 10 mA < <sub>IVDD1</sub> < 600 mA, 8 V < VBATP < 19 V                                                                                                                                                            | -7     |     | 7        | mV   |

| A4.11  | LdReg <sub>VDD1</sub>     | Load regulation on VDD1_SENSE (VBATP constant)                                       | 10 mA < I <sub>VDD</sub> 1 < 600 mA, 8 V <<br>VBATP < 19 V                                                                                                                                                       | -7     |     | 7        | mV   |

| A4.12  | TmpCo <sub>VDD1</sub>     | Temperature drift                                                                    | Normalized to 25°C value                                                                                                                                                                                         | -0.5%  |     | 0.5%     |      |

|        |                           |                                                                                      | Empty                                                                                                                                                                                                            |        |     |          |      |

| A4.14  | dVDD1/dt                  | dV/dt at VDD1_SENSE at start-up                                                      |                                                                                                                                                                                                                  | 0.8    |     | 8        | V/ms |

| A4.15  | t <sub>delayVDD1</sub>    | VDD1 voltage stabilization delay                                                     | Maximum delay after CAN wake-<br>up for VDD1 output to settle                                                                                                                                                    |        |     | 2.5      | ms   |

| vsou   | Г1 – LDO With Prote       | ected Internal FET                                                                   |                                                                                                                                                                                                                  |        |     |          |      |

| AN     | C <sub>VSOUT1</sub>       | Value of output ceramic capacitor                                                    | ESR range 0 m $\Omega$ to 100 m $\Omega$                                                                                                                                                                         | 0.5    |     | 10       | μF   |

| 5.1    | VSOUT1                    | VSOUT1 output voltage                                                                | Depends on extal resistive divider.                                                                                                                                                                              | 3.3    |     | 9.5      | V    |

| 5.2    | MVVSOUT1                  | For tracking mode:<br>Matching output errorMV <sub>VSOUT1</sub> = (VTRACK1 – VSFB1)  | 0 < I <sub>VSOUT1</sub> < 100 mA<br>For specified IV <sub>SOUT</sub> range,<br>referenced to VTRACK1 input,<br>including long-term and<br>temperature drift.                                                     | -15    |     | 15       | mV   |

| 5.3    | VSFB1                     | For non-tracking mode: VSOUT1 reference voltage                                      | 10 mA < IV <sub>SOUT</sub> < 100 mA,<br>including line and load regulation,<br>temperature drift and long-term<br>drift                                                                                          | -2%    | 2.5 | 2%       | V    |

| 5.3a   | VTRACK1 <sub>th</sub>     | Threshold for tracking/non-tracking                                                  | VTRACK1 > 1.2 V; VSOUT1 in<br>tracking mode<br>VTRACK1 < 1.2 V; VSOUT1 in<br>non-tracking mode                                                                                                                   |        | 1.2 |          | V    |

SLVSBC4 -MAY 2012

# **ELECTRICAL CHARACTERISTICS (continued)**

Over operating ambient temperature  $T_J = -40^{\circ}$ C to 150°C and operating VBATP range 6 V to 36 V (unless otherwise noted)

| POS   |                           | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                                                            | MIN         | TYP MAX     | UNIT       |

|-------|---------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|

| 5.3b  | VTRACK1 <sub>pd</sub>     | Internal pulldown resistance on VTRACK1 pin                                                |                                                                                                                                                            |             | 100         | kΩ         |

| 5.4   | IVSOUT1                   | VSOUT1 output current                                                                      | internal resistor to dissipate min current                                                                                                                 |             | 100         | mA         |

| 5.5   | VdrS1                     | VSOUT1 dropout voltage VdrS1 = (VSIN-VSOUT1)                                               | $T_J = -40^{\circ}$ C to 165°C<br>0 < I <sub>VSOUT1</sub> < 100 mA                                                                                         |             | 0.75        | V          |

| 5.6   | PSRR <sub>VSOUT1</sub>    | Power-supply rejection ratio                                                               | With stable VTRACK1 input<br>voltage<br>50 < f < 20  kHz, VBATP = 10 V,<br>U = 4 Vpp<br>$C_{VSOUT1} = 1 \ \mu\text{F}$ , 0 < $I_{VSOUT1} < 100 \text{ mA}$ | 40          |             | dB         |

| 5.7   | LnReg <sub>VSOUT1</sub>   | Line regulation I <sub>VSOUT1</sub> constant)                                              | 0 < IVSOUT1 < 100 mA, 8 V <<br>VBATP < 19 V                                                                                                                | -25         | 25          | mV         |

| 5.8   | LdReg <sub>VSOUT1</sub>   | Load regulation (VSIN constant)                                                            | 0 < IVSOUT1 < 100 mA, 8 V <<br>VBATP < 19 V                                                                                                                | -25         | 25          | mV         |

| 5.9   | TmpCo <sub>VSOUT1</sub>   | Temperature drift                                                                          | Normalized to 25°C value<br>Empty                                                                                                                          | -0.5%       | 0.5%        |            |

| 5.11  | VSOUT1 <sub>SH</sub>      | Output short circuit voltage range                                                         |                                                                                                                                                            | -2          | 40          | V          |

| 5.12  | -I <sub>VSIN</sub>        | Output reverse current                                                                     | VSOUT1 = 14 V and VBATP = 0<br>V, regulator switched off                                                                                                   |             | 20          | mA         |

| 5.13  | TprotVSOUT1               | Temperature protection threshold                                                           | VSOUT1 switch-off                                                                                                                                          | 175         | 210         | °C         |

| 5.14  | I <sub>VSOUT1_limit</sub> | Current limit                                                                              |                                                                                                                                                            | 100         | 500         | mA         |

| VOLTA |                           |                                                                                            |                                                                                                                                                            |             |             | 1          |

| 6.1   | VBATP_UVoff               | VBATP level for switching off VDDx                                                         |                                                                                                                                                            | 4.2         | 4.5         | V          |

| 6.2   | VBATP_UVon                | VBATP level for switching on VDDx                                                          |                                                                                                                                                            | 5.4         | 5.8         | V          |

| 6.3   | VBATP_UVhys               | Undervoltage hysteresis                                                                    |                                                                                                                                                            | 1.1         | 1.4         | V          |

| 6.4   | VBATP_OVrise              | VBATP level for setting VBAT_OV flag                                                       |                                                                                                                                                            | 29.5        | 32.5        | V          |

| 6.5   | <br>VBATP_OVfall          | VBATP level for clearing VBAT_OV flag                                                      |                                                                                                                                                            | 29          | 32          | V          |

| 6.6   | VBATP_OVhys               | Overvoltage hysteresis                                                                     |                                                                                                                                                            | 0.2         | 0.9         | V          |

| 6.7   | VBATP_deglitch            | VBATP under/overvoltage monitor deglitch time                                              |                                                                                                                                                            |             | 200         | μs         |

| 6.8   | VDD5_UV                   | VDD5 undervoltage level                                                                    |                                                                                                                                                            | 4.5         | 4.85        | V          |

| 6.9   | VDD5_UVhead               | VDD5 undervoltage headroom (VDD5act –<br>VDD5_UVact)                                       |                                                                                                                                                            | 200         |             | mV         |

| 6.10  | VDD5_OV                   | VDD5 overvoltage level                                                                     |                                                                                                                                                            | 5.2         | 5.5         | V          |

| 6.11  | VDD5_OVhead               | VDD5 overvoltage headroom (VDD5_OVact – VDD5act)                                           |                                                                                                                                                            | 200         |             | mV         |

| 6.12  | VDD3/5_UV                 | VDD3/5 undervoltage level<br>3.3-V setting<br>5-V setting                                  |                                                                                                                                                            | 2.97<br>4.5 | 3.17<br>4.8 | V          |

| 6.13  | VDD3/5_UVhead             | VDD3/5 undervoltage headroom<br>(VDD3/5act – VDD3/5_UVact)<br>3.3-V setting<br>5-V setting |                                                                                                                                                            | 170<br>200  |             | mV         |

| 6.14  | VDD5_3_OV                 | VDD5_3 overvoltage level<br>3.3-V setting<br>5-V setting                                   |                                                                                                                                                            | 3.43<br>5.2 | 3.63<br>5.5 | V          |

| 6.15  | VDD3/5_UVhead             | VDD3/5 undervoltage headroom<br>(VDD3/5_OVact – VDD3/5act)<br>3.3-V setting<br>5-V setting |                                                                                                                                                            | 170<br>200  |             | mV         |

| 6.16  | VDD1_UV                   | VDD1 undervoltage level                                                                    | Sensed on VDD1_SENSE pin                                                                                                                                   | 0.94        | 0.97        | VDD1       |

| 6.17  | VDD1_OV                   | VDD1 overvoltage level                                                                     | Sensed on VDD1_SENSE pin                                                                                                                                   | 1.03        | 1.06        | VDD1       |

| 6.18  | VDDx_deglitch             | VDDx under/overvoltage monitor deglitch time                                               |                                                                                                                                                            | 10          | 40          | μs         |

| 6.19  | VSOUT1_UV                 | VSOUT1 undervoltage level                                                                  | Sensed on VSFB1 pin                                                                                                                                        | 0.88        | 0.94        | VSOUT<br>1 |

| 6.20  | VSOUT1_OV                 | VSOUT1 overvoltage level                                                                   | Sensed on VSFB1 pin                                                                                                                                        | 1.06        | 1.12        | VSOUT<br>1 |

| 6.21  | VSOUT1_deglitch           | VSOUT1 under/overvoltage monitor deglitch time                                             |                                                                                                                                                            | 10          | 40          | μs         |

#### SLVSBC4 -MAY 2012

## ELECTRICAL CHARACTERISTICS (continued)

Over operating ambient temperature  $T_J = -40^{\circ}$ C to 150°C and operating VBATP range 6 V to 36 V (unless otherwise noted)

| POS     |                                 | PARAMETER                                                                | TEST CONDITIONS                                       | MIN            | TYP | MAX   | UNIT |

|---------|---------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------|----------------|-----|-------|------|

| 6.22    | VDD6_UV                         | VDD6 undervoltage level                                                  |                                                       | 5.2            |     | 5.4   | V    |

| 6.23    | VDD6_OV                         | VDD6 overvoltage level                                                   |                                                       | 7.8            |     | 8.2   | V    |

| IGNITI  | ON and CAN WAKE                 | -UP                                                                      |                                                       | 1              |     | 1     |      |

| 7.1     | IGN_WUP                         | IGN wake-up threshold                                                    |                                                       | 2              |     | 3     | V    |

| 7.2     | CAN_WUP                         | CAN wake-up threshold                                                    |                                                       | 2              |     | 3     | V    |

| 7.3     | WUP_hyst                        | Wake-up hysteresis                                                       |                                                       | 50             |     | 200   | mV   |

| 7.4     | I_IGN                           | IGN forward leakage current                                              |                                                       |                |     | 50    | μA   |

| 7.5     | I_IGN_rev                       | IGN current at -7 V                                                      |                                                       |                |     | -1    | mA   |

| 7.6     | IGN_deg                         | IGN deglitch filter time                                                 |                                                       | 7.5            |     | 22    | ms   |

| 7.7     | I_CAN                           | CAN forward leakage current                                              |                                                       |                |     | 50    | μA   |

| 7.8     | I_CAN_rev                       | CAN current at -0.3 V                                                    |                                                       |                |     | 1     | mA   |

| 7.9     | CAN_deg                         | CAN deglitch filter time                                                 |                                                       | 100            |     | 350   | μs   |

| Charg   | e Pump                          |                                                                          |                                                       |                |     |       |      |

| AN      | C <sub>pump</sub>               | Pumping capacitor                                                        |                                                       |                | 10  |       | nF   |

| AN      | C <sub>store</sub>              | Storage capacitor                                                        |                                                       |                | 100 |       | nF   |

| 8.1     | VCPon                           | VCP output voltage in on-state                                           | VBATP > 5.8 V                                         | VBATP          |     | VBATP | V    |

|         |                                 |                                                                          | VUATE 20.0 V                                          | + 4            |     | + 15  |      |

| 8.2     | I <sub>CP</sub>                 | External load                                                            |                                                       |                |     | 100   | μA   |

| 8.3     | f <sub>CP</sub>                 | Charge-pump switching frequency                                          |                                                       |                | 250 |       | kHz  |

| Reset   | and Enable Outputs              |                                                                          |                                                       | 1              |     |       |      |

| 9.1     | V <sub>NRES_ENDRV_L</sub>       | NRES / ENDRV low output level                                            | With external 5-mA open-drain<br>current              |                |     | 0.2   | V    |

| 9.2     | R <sub>NRES_ENDRV_PULLU</sub>   | NRES / ENDRV internal pullup resistance                                  |                                                       | 3              |     | 6     | kΩ   |

| 9.2a    | R <sub>dson_ENDRV_NRES</sub>    | rds(on) NRES/ENDRV pulldown transistor                                   |                                                       | 11             |     | 86    | Ω    |

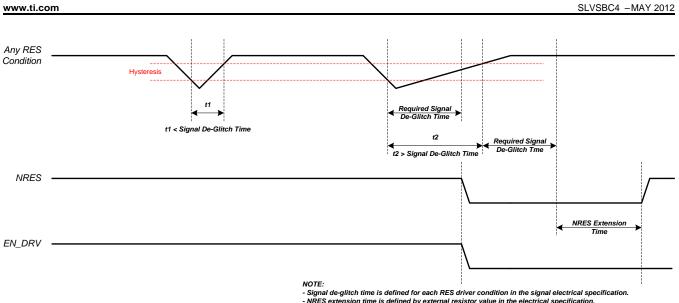

| 9.3     | R <sub>RSTEXT</sub>             | Value of external reset extension resistor <sup>(1)</sup>                | In case of open-connect, device stays in RESET state. | 0              | 22  |       | kΩ   |

| 9.4     | $t_{RSTEXT(22k\Omega)}$         | Reset extension delay                                                    |                                                       | 4.05           | 4.5 | 4.95  | ms   |

| 9.4a    | t <sub>RSTEXT(0kΩ)</sub>        | Reset extension delay                                                    |                                                       |                | 1.4 |       | ms   |

| 9.5     | V <sub>ENDRV_NRES_TH</sub>      | ENDRV and NRES readback threshold                                        | Read-back muxed to DIAG_OUT pin                       | 300            | 400 | 500   | mV   |

| Digital | Input / Output                  |                                                                          |                                                       |                |     |       |      |

| 10.1    | V <sub>DIGIN_HIGH</sub>         | Digital input, high level                                                |                                                       | 2              |     |       | V    |

| 10.2    | V <sub>DIGIN_LOW</sub>          | Digital input, low level                                                 |                                                       |                |     | 0.8   | V    |

| 10.3    | V <sub>DIGIN_HYST</sub>         |                                                                          |                                                       | 0.1            |     |       | V    |

| 10.4    |                                 |                                                                          | Empty                                                 |                |     |       |      |

| 10.5    | V <sub>DIGOUT_HIGH</sub>        | Digital output, high level                                               | lout = -2 mA (out of pin)                             | VDDIO<br>- 0.2 |     |       | V    |

| 10.6    | V <sub>DIGOUT_LOW</sub>         | Digital output, low level                                                | lout = 2 mA (into pin)                                |                |     | 0.2   | V    |

| Interna | al System Clock                 |                                                                          |                                                       |                |     |       |      |

| 11.1    | f <sub>Syscik</sub>             | System clock frequency                                                   |                                                       | 3.8            | 4   | 4.2   | MHz  |

| Windo   | w Watchdog                      |                                                                          |                                                       |                |     |       |      |

| 12.1    | t <sub>ERROR_WDI_deglitch</sub> | Deglitch time on ERROR/WDI pin                                           |                                                       | 14.25          | 15  | 15.75 | μs   |

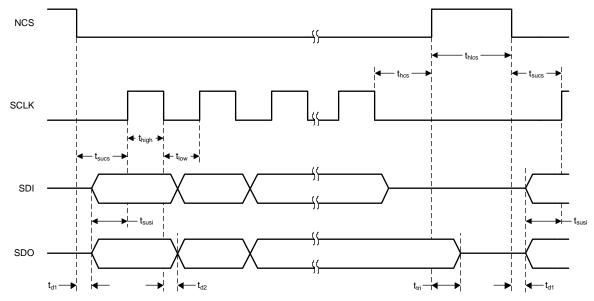

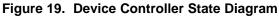

| Serial  | Peripheral Interface            | Timing                                                                   | 1                                                     | 1              |     | 1     |      |

| 13.1    | f <sub>SPI</sub>                | SPI clock (SCLK) frequency                                               |                                                       |                |     | 8(2)  | MHz  |

| 13.2    | t <sub>SPI</sub>                | SPI clock period                                                         |                                                       | 125            |     |       | ns   |

| 13.3    | t <sub>high</sub>               | High time: SCLK logic high duration                                      |                                                       | 45             |     |       | ns   |

| 13.4    | t <sub>low</sub>                | Low time: SCLK logic low duration                                        |                                                       | 45             |     |       | ns   |

| 13.5    | t <sub>sucs</sub>               | Setup time NCS: time between falling edge of NCS and rising edge of SCLK |                                                       | 45             |     |       | ns   |

(1) In case of open-connect, device stays in RESET state.

(2) MAX SPI Clock tolerance is ±10%

TEXAS INSTRUMENTS

SLVSBC4 -MAY 2012

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Over operating ambient temperature  $T_J = -40^{\circ}$ C to 150°C and operating VBATP range 6 V to 36 V (unless otherwise noted)

| POS   | PARAMETER              |                                                                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------|------------------------|------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 13.6  | t <sub>d1</sub>        | Delay time: time delay from falling edge of NCS to data valid at SDO         |                 |     |     | 30  | ns   |

| 13.7  | t <sub>susi</sub>      | Setup time at SDI: setup time of SDI before the rising edge of SCLK          |                 |     |     | 15  | ns   |

| 13.8  | t <sub>d2</sub>        | Delay time: time delay from falling edge of SCLK to data valid at SDO        |                 | 0   |     | 30  | ns   |

| 13.9  | t <sub>hcs</sub>       | Hold time: time between the falling edge of SCLK and rising edge of NCS      |                 | 45  |     |     | ns   |

| 13.10 | t <sub>hlcs</sub>      | SPI transfer inactive time (time between two transfers)                      |                 | 250 |     |     | ns   |

| 13.11 | t <sub>tri</sub>       | Hi-Z state delay time: time between rising edge of NCS and SDO in Hi-Z state |                 |     |     | 15  | ns   |

| 13.12 | R <sub>PULL_UP</sub>   | Internal pullup resistor on NCS input pin                                    |                 | 40  | 70  | 100 | kΩ   |

| 13.13 | R <sub>PULL_DOWN</sub> | Internal pulldown resistor on SDI and SCLK input pins                        |                 | 40  | 70  | 100 | kΩ   |

Figure 2. SPI Timing Parameters

## **PIN ASSIGNMENT**

|                    | AP Package<br>(Top View) |

|--------------------|--------------------------|

| O<br>1 VBAT_SAFING | ENDRV [32]               |

| 2 VCP              | SEL_VDD3/5 31            |

| 3 CP1              | IGN 30                   |

| 4 CP2              | VBATP 29                 |

| 5 PGND             | SDN6 28                  |

| 6 NRES             | VDD6 [27]                |

| 7 DIAG_OUT         | VDD1_G                   |

|                    | PGND 25<br>PS65381-Q1    |

| 9 SDI              | VDD1_SENSE 24            |

| 10 SDO             | GND 23                   |

| 11 SCLK            | VDDIO 22                 |

| 12 RSTEXT          | VDD3/5 [21]              |

| 13 ERROR/WDI       | VDD5 [20]                |

| 14 CANWU           | GND [19]                 |

| 15 VSFB1           | VTRACK1 18               |

| 16 VSIN            | VSOUT1 17                |

### **PIN FUNCTIONS**

| PIN         |        | I/O/    | DESCRIPTION                                                          |  |

|-------------|--------|---------|----------------------------------------------------------------------|--|

| NAME        | NO.    | PWR/GND | DESCRIPTION                                                          |  |

| CANWU       | 14     | I       | Wake-up input signal from CAN tranceiver                             |  |

| CP1         | 3      | PWR     | Charge-pump external capacitor, high-voltage side                    |  |

| CP2         | 4      | PWR     | Charge-pump extenal capacitor, low-voltage side                      |  |

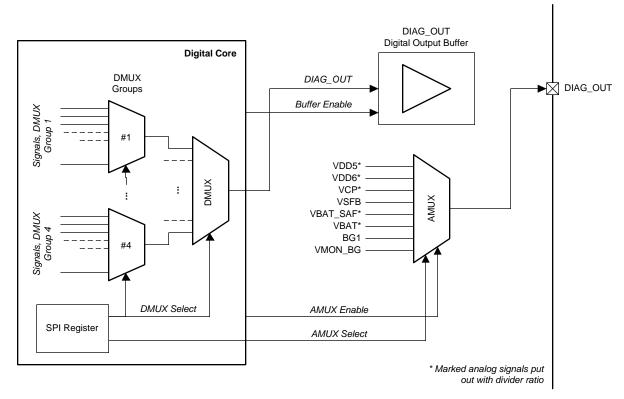

| DIAG_OUT    | 7      | 0       | Analog MUX output for MCU ADC                                        |  |

| ENDRV       | 32     | 0       | Enable output signal for peripherals (for example, motor-driver IC). |  |

| ERROR/WDI   | 13     | I       | Error input signal from MCU / window watchdog input trigger          |  |

| GND         | 19, 23 | GND     | Ground (analog)                                                      |  |

| IGN         | 30     | I       | Wake-up signal from ignition key                                     |  |

| NCS         | 8      | I       | SPI chip select (active-low)                                         |  |

| NRES        | 6      | 0       | Cold-reset (NPOR_RST) output signal for µC                           |  |

| PGND        | 5, 25  | I       | Ground (power)                                                       |  |

| RSTEXT      | 12     | I       | Configuration pin for reset extension                                |  |

| SCLK        | 11     | I       | SPI clock                                                            |  |

| SDI         | 9      | I       | SPI serial data IN                                                   |  |

| SEL_VDD3/5  | 31     | I       | Select input for VDD3/5 regulator                                    |  |

| SDN6        | 28     | PWR     | Switching node for VDD6 switch-mode regulator                        |  |

| SDO         | 10     | 0       | SPI serial data OUT                                                  |  |

| VBATP       | 29     | PWR     | Battery voltage (reverse protected)                                  |  |

| VBAT_SAFING | 1      | PWR     | Battery voltage (reverse protected) for safety functions             |  |

Copyright © 2012, Texas Instruments Incorporated

## TEXAS INSTRUMENTS

www.ti.com

SLVSBC4 -MAY 2012

## PIN FUNCTIONS (continued)

| PIN         |     | I/O/    | DECODIDITION                                                                                    |  |

|-------------|-----|---------|-------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | PWR/GND | DESCRIPTION                                                                                     |  |

| VCP         | 2   | PWR     | Charge-pump output voltage                                                                      |  |

| VDD1_G      | 26  | 0       | Gate of external FET for VDD1 regulator                                                         |  |

| VDD1_SENSE  | 24  | I       | Input reference for VDD1 regulator                                                              |  |

| VDD3/5      | 21  | I       | VDD3/5 regulator output voltage                                                                 |  |

| VDD5        | 20  | PWR     | VDD5 regulator output voltage                                                                   |  |

| VDD6        | 27  | PWR     | VDD6 switch-mode regulator output voltage                                                       |  |

| VDDIO       | 22  | PWR     | I/O-level for pins from/to MCU                                                                  |  |

| VSFB1       | 15  | I       | Feedback input reference for sensor supply regulator                                            |  |

| VSIN        | 16  | PWR     | Sensor supply regulator input supply voltage                                                    |  |

| VSOUT1      | 17  | PWR     | Sensor supply regulator output voltage                                                          |  |

| VTRACK1     | 18  | I       | Tracking input reference for sensor supply regulator                                            |  |

| Thermal pad | -   |         | Connected to GNDIO. Place thermal vias to large ground plane and connect to AGND and GNDIO pin. |  |

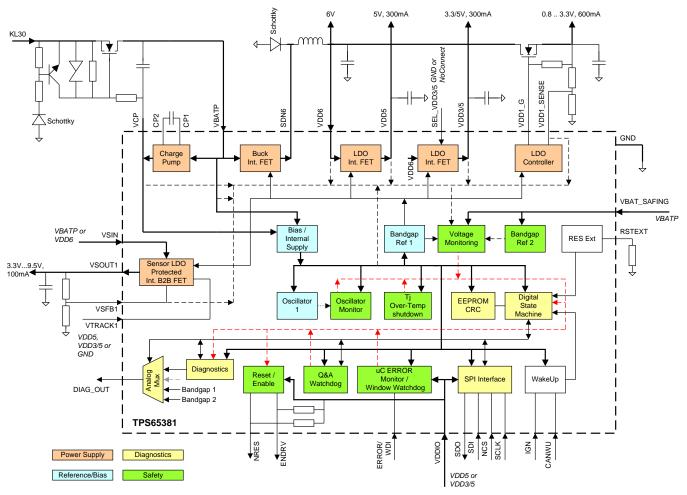

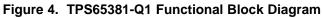

## FUNCTIONAL BLOCK DIAGRAM

12 Submit Documentation Feedback

## DETAILED DESCRIPTION

#### VDD6 Buck Switch-Mode Power Supply

The purpose of the VDD6 buck switch-mode power supply is to reduce the power dissipation inside the IC. It converts the ingoing power for VDD5, VDD3/5, VDD1 and VSOUT1 from the battery-voltage domain to the 6-V voltage domain. Hence, VDD6 is intended to be used as pre-regulator only; its output voltage is less accurate compared to VDD5, VDD3/5, VDD1, and VSOUT1. The VDD6 output-current capability is dimensioned to supply VDD5, VDD3/5, VDD1, and VSOUT1 at their respective maximum output currents.

This switch-mode power supply (SMPS) operates with fixed-frequency adaptive on-time control pulse-width modulation (PWM). Its control loop is based on a hysteretic comparator. The internal N-channel MOSFET is turned on at the beginning of each cycle. This MOSFET is turned off when the hysteretic PWM comparator resets the latch. Once this internal MOSFET is turned OFF, the external Schottky diode recirculates the energy stored in the inductor for the remainder of the switching period. In order to preserve sufficient headroom for the VDD5 regulator at low battery voltage, the VDD6 regulator is put in dropout mode for battery voltage below 7 V.

The internal MOSFET is protected from excess power dissipation with a current-limit circuit, and junction overtemperature protection shared with VDD3/5. In case of an overtemperature condition in VDD6 detected by the VDD3/5 overtemperature protection, the TPS65381-Q1 goes to the STANDBY state (all regulators switched off).

#### VDD5 Linear Regulator

This is a regulated supply of 5 V  $\pm$ 2% over temperature and battery supply range. A low-ESR ceramic capacitor is required for loop stabilization; this capacitor must be placed close to the pin of the IC. This output is protected against shorts to ground by a current limit, and limits output voltage overshoot during power up, or during line or load transients.

On an initial IGN or CANWU power cycle, the soft-start circuit on this regulator is initiated. This is typically in the 1-ms to 2-ms range. This output may require a larger output capacitor to ensure that during load transients the output does NOT drop below the required regulation specifications.

The internal MOSFET is protected from excess power dissipation with junction overtemperature protection. In case of an overtemperature condition in VDD5, only the VDD5 regulator is be switched off by clearing bit 4 in the SENS\_CTRL register. In order to re-enable VDD5, first bit 1 in SAFETY\_STAT 1 must be cleared on readout, and after that bit 4 in the SENS\_CTRL register must be set again.

### VDD3/5 Linear Regulator

This is a regulated supply of 3.3 V or 5 V  $\pm$ 2% over temperature and battery supply range. The output voltage level can be selected with the SEL\_VDD5/3 pin (open pin selects 3.3 V, grounded pin selects 5 V). The state of this selection pin is sampled and latched directly at the first initial IGN or CANWU power cycle. Once latched, any change in the state of this selection pin after the first initial IGN or CANWU power cycle does not change the initially selected state of the VDD3/5 regulator.

A low-ESR ceramic capacitor is required for loop stabilization; this capacitor must be placed close to the pin of the IC. This output is protected against shorts to ground by a current limit, and limits output-voltage overshoot during power up or during line or load transients.

On an initial IGN or CANWU power cycle, the soft-start circuit on this regulator is initiated. This is typically in the 1-ms to 2-ms range. This output may require a larger output capacitor to ensure that during load transients the output does NOT drop below the required regulation specifications.

The internal MOSFET is protected from excess power dissipation with a current-limit circuit and junction overtemperature protection. In case of an over-temperature in VDD3/5, the TPS65381-Q1 goes to STANDBY state (all regulators switched-off)

### VDD1 Linear Regulator