TMDS171, TMDS1711

SLLSEN7A - OCTOBER 2015-REVISED DECEMBER 2015

# TMDS171/I 3.4 Gbps TMDS RETIMER

#### **Features**

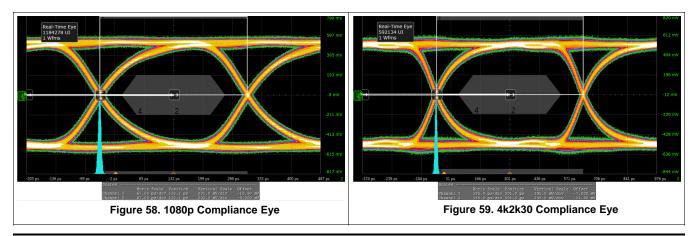

- HDMI Input Port to Output Port with CDR Supporting up to 3.4 Gbps Data Rates

- Compatible with HDMI1.4b Electrical Parameters.

- Support for 4k2k30p and up to WUXGA 12-bit Color Depth or 1080p with Higher Refresh Rates™

- Retimes Input Stream to Compensate for Random

- Adaptive Receiver Equalizer or Programmable Fixed Equalizer

- I<sup>2</sup>C and Pin Strap Programmable

- Inter-Pair Skew Compensation of 5+ Bits

- Link Debug Tools Including Eye Diagram After RX Equalizer

- Single Ended Mode ARC Support

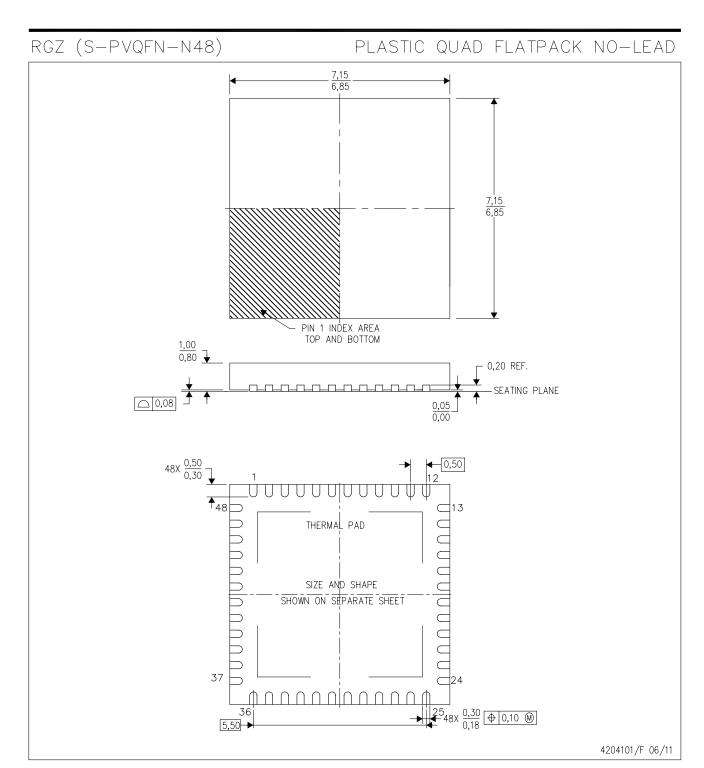

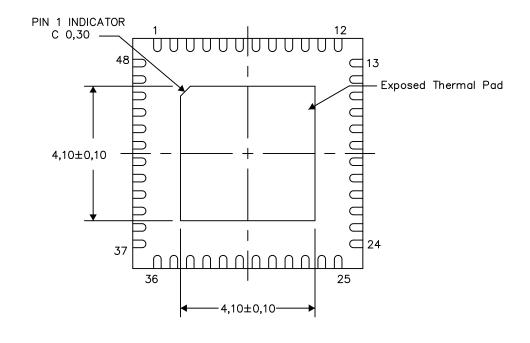

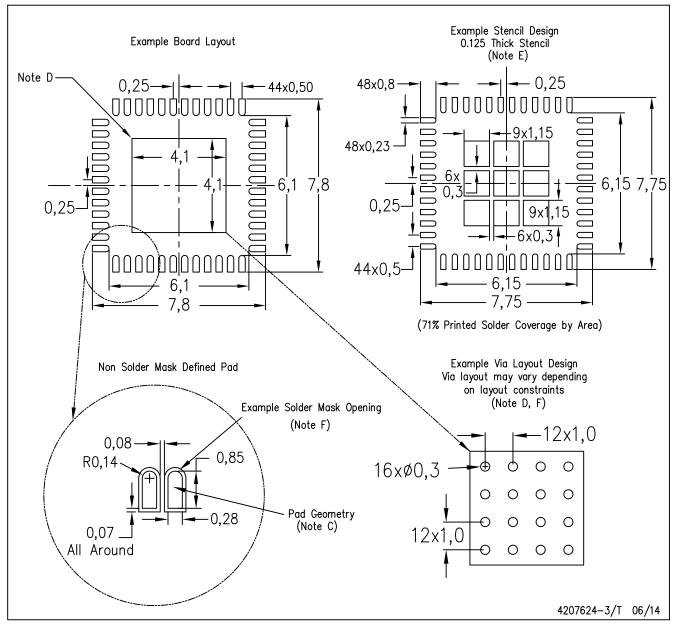

- 48-pin 7mm x 7mm 0.5 mm Pitch VQFN Package

- **Extended Commercial Temperature Support** 0°C - 85°C (TMDS171)

- Industrial Temperature Support -40°C 85°C (TMDS1711)

### 2 Applications

- Digital TV

- Digital Projector

- Audio/Video Equipment

- Blu-Ray DVD

- Monitors

- Desktops/ All-in-Ones

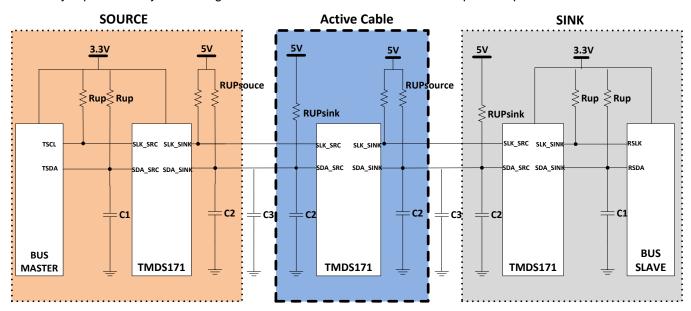

- **Active Cables**

## 3 Description

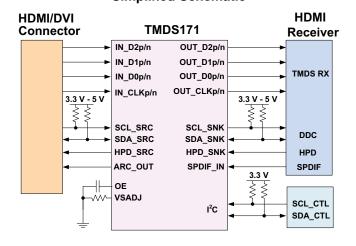

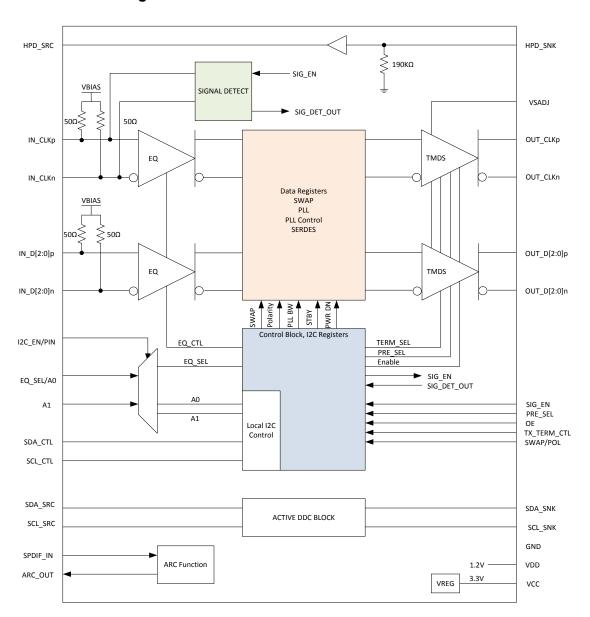

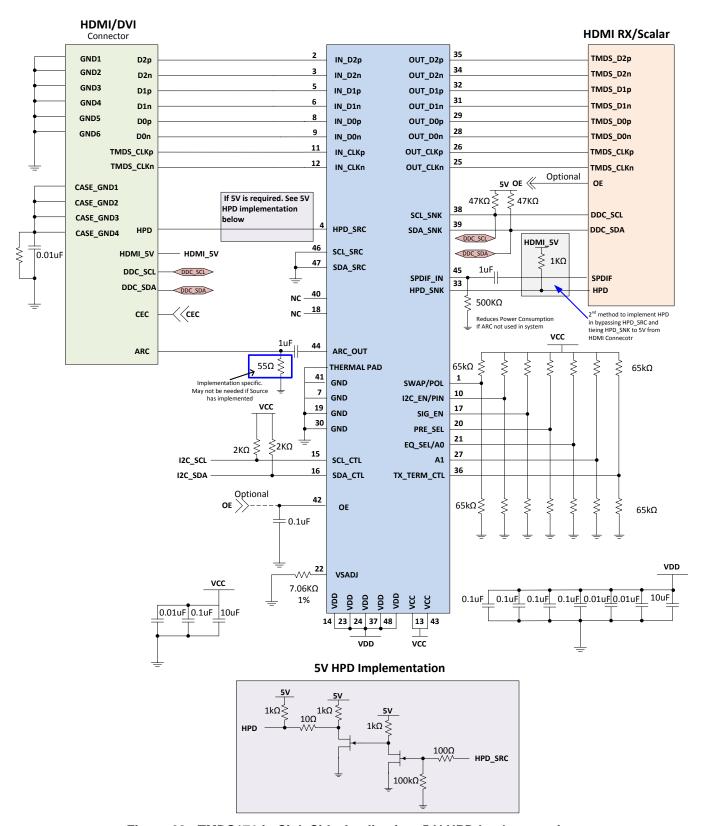

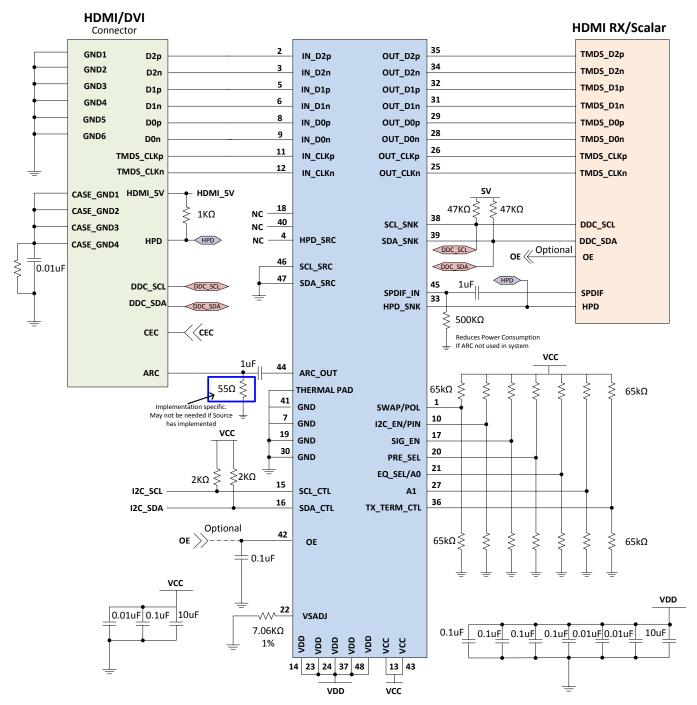

The TMDS171 is a digital video interface (DVI) or high-definition multimedia interface (HDMI) retimer. The TMDS171 supports four TMDS channels, Audio Return Channel (SPDIF\_IN/ARC\_OUT), Hot Plug Detect (HPD) and Digital Display Control (DDC) interfaces. The TMDS171 supports signaling rates up to 3.4 Gbps to allow for the highest resolutions of 4k2k30p 24 bits per pixel and up to WUXGA 12-bit color depth or 1080p with higher refresh rates. The TMDS171 automatically configures itself as a redriver at low data rate (< 1 Gbps) or as a re-timer above this data rate.

The TMDS171 supports dual power supply rails of 1.2 V on VDD and 3.3 V on VCC for active power reduction. Several methods of power management implemented to reduce overall consumption. TMDS171 supports fixed EQ gain or adaptive EQ control by I<sup>2</sup>C or pin strap to compensate for different lengths input cable or board traces.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE                               | BODY SIZE (NOM)   |  |  |

|-------------|---------------------------------------|-------------------|--|--|

| TMDS171     | (\( \( \subseteq \text{EN} \) 40 Dino | 7.00 mm v 7.00 mm |  |  |

| TMDS171I    | (VQFN) 48 Pins                        | 7.00 mm x 7.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

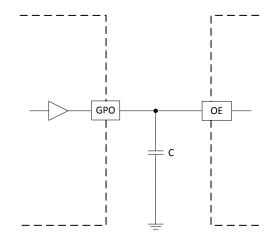

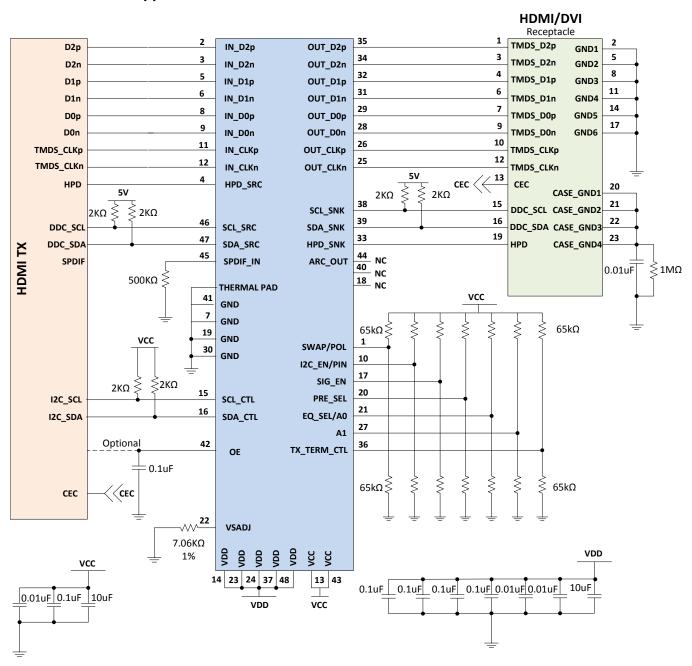

# Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                                          |    | 8.3 Feature Description                          | 20 |

|---|---------------------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                                      |    | 8.4 Device Functional Modes                      | 2  |

| 3 | Description 1                                                       |    | 8.5 Register Maps                                | 29 |

| 4 | Revision History2                                                   | 9  | Application and Implementation                   | 42 |

| 5 | Pin Configuration and Functions                                     |    | 9.1 Application Information                      | 42 |

| 6 | Specifications5                                                     |    | 9.2 Source Side Application                      | 4  |

| U | 6.1 Absolute Maximum Ratings 5                                      |    | 9.3 System Examples                              | 49 |

|   | 6.2 ESD Ratings                                                     | 10 | Power Supply Recommendations                     | 50 |

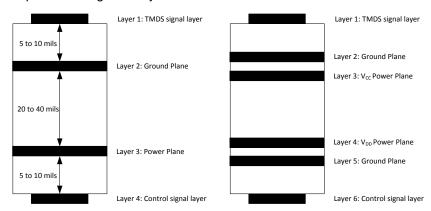

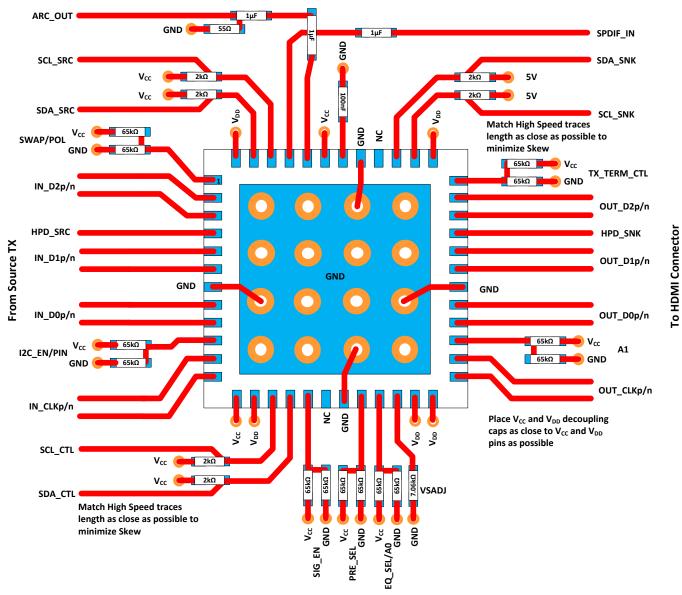

|   | 6.3 Recommended Operating Conditions                                | 11 | Layout                                           | 52 |

|   | 6.4 Thermal Information                                             |    | 11.1 Layout Guidelines                           | 5  |

|   | 6.5 Electrical Characteristics                                      |    | 11.2 Layout Example                              |    |

|   | 6.6 Switching Characteristics 9                                     |    | 11.1 Documentation Support                       | 5  |

|   | 6.7 Typical Characteristics                                         |    | 11.2 Community Resources                         | 54 |

| 7 | Parameter Measurement Information                                   |    | 11.3 Trademarks                                  | 54 |

| _ |                                                                     |    | 11.4 Electrostatic Discharge Caution             | 5  |

| 8 | Detailed Description                                                |    | 11.5 Glossary                                    |    |

|   | 8.1 Overview       19         8.2 Functional Block Diagram       20 | 12 | Mechanical, Packaging, and Orderable Information |    |

# 4 Revision History

| Changes from Original (October 2015) to Revision A |

|----------------------------------------------------|

|                                                    |

Page

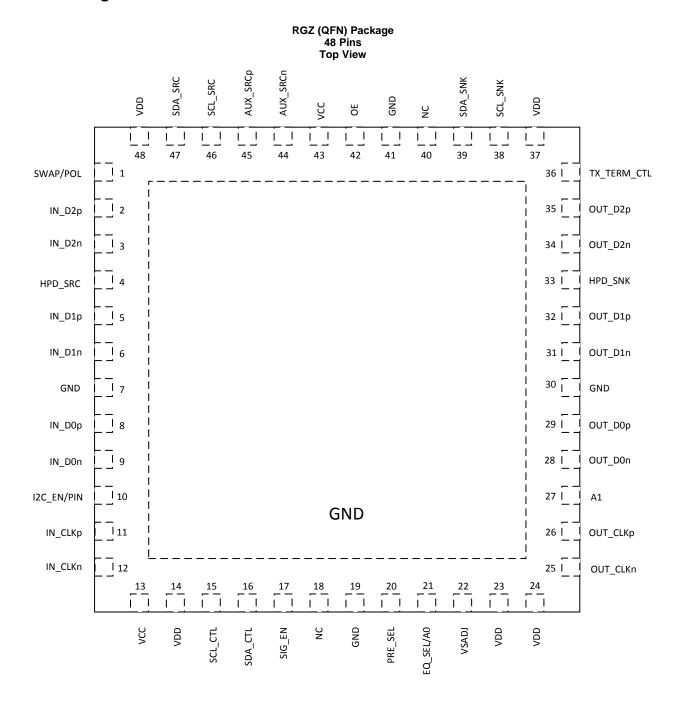

# 5 Pin Configuration and Functions

#### Pin Functions

|                 | Pin Functions       |                    |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-----------------|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 | PIN                 | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| NAME            | NO.                 |                    |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| VCC             | 13, 43              | Р                  | 3.3 V Power Supply                                                                                                                                                                                                                                                           |  |  |  |  |  |

| VDD             | 14, 23, 24, 37, 48  | Р                  | 1.2 V Power Supply                                                                                                                                                                                                                                                           |  |  |  |  |  |

| GND             | 7, 19, 27, 41, 30   | G                  | Ground                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Thermal Pad     |                     | G                  | Ground                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| MAIN LINK INPUT | PINS (FAILAFE)      |                    |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| IN_D2p/n        | 2, 3                | I                  | Channel 2 Differential Input                                                                                                                                                                                                                                                 |  |  |  |  |  |

| IN_D1p/n        | 5, 6                | 1                  | Channel 1 Differential Input                                                                                                                                                                                                                                                 |  |  |  |  |  |

| IN_D0p/n        | 8, 9                | 1                  | Channel 0 Differential Input                                                                                                                                                                                                                                                 |  |  |  |  |  |

| IN_CLKp/n       | 11, 12              | I                  | Clock Differential Input                                                                                                                                                                                                                                                     |  |  |  |  |  |

| MAIN LINK OUTPU | T PINS (FAILAFE)    |                    |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| OUT_D2n/p       | 34, 35              | 0                  | TMDS Data 2 Differential Output                                                                                                                                                                                                                                              |  |  |  |  |  |

| OUT_D1n/p       | 31, 32              | 0                  | TMDS Data 1 Differential Output                                                                                                                                                                                                                                              |  |  |  |  |  |

| OUT_D0n/p       | 28, 29              | 0                  | TMDS Data 0 Differential Output                                                                                                                                                                                                                                              |  |  |  |  |  |

| OUT_CLKn/p      | 25, 26              | 0                  | TMDS Clock Differential Output                                                                                                                                                                                                                                               |  |  |  |  |  |

| HOT PLUG DETEC  | T PINS              | L                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                        |  |  |  |  |  |

| HPD_SRC         | 4                   | 0                  | Hot Plug Detect Output to source side                                                                                                                                                                                                                                        |  |  |  |  |  |

| HPD SNK         | 33                  | ı                  | Hot Plug Detect Input from sink side                                                                                                                                                                                                                                         |  |  |  |  |  |

|                 | HANNEL and DDC PINS | <u> </u>           |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| SPDIF_IN        | 45                  | ı                  | SPDIF signal input                                                                                                                                                                                                                                                           |  |  |  |  |  |

| ARC_OUT         | 44                  | 0                  | Audio return channel output                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SDA_SRC         | 47                  | 1/0                | Source Side TMDS Port Bidirectional DDC Data line                                                                                                                                                                                                                            |  |  |  |  |  |

| SCL_SRC         | 46                  | 1/0                | Source Side TMDS Port Bidirectional DDC Clock line                                                                                                                                                                                                                           |  |  |  |  |  |

| SDA_SNK,        | 39                  | 1/0                | Sink Side TMDS Port Bidirectional DDC Data Line                                                                                                                                                                                                                              |  |  |  |  |  |

| SCL_SNK         | 38                  | 1/0                | Sink Side TMDS Port Bidirectional DDC Clock Line                                                                                                                                                                                                                             |  |  |  |  |  |

| CONTROL PINS(2) | 30                  | 1/0                | Silik Side Tivids Fort Bidirectional DDC Clock Line                                                                                                                                                                                                                          |  |  |  |  |  |

| CONTROL FINS    |                     |                    | Operation Enable/Reset Pin                                                                                                                                                                                                                                                   |  |  |  |  |  |

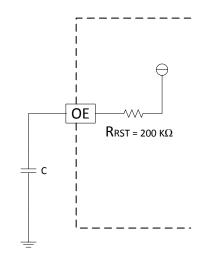

| OE              | 42                  | I                  | OE = L: Power Down Mode OE = H: Normal Operation Internal weak pull up: Resets device when transitions from H to L                                                                                                                                                           |  |  |  |  |  |

| SIG_EN          | 17                  | I                  | Signal detector circuit enable SIG_EN = L: Signal Detect Circuit Disabled: Term resistors always connected (Default) SIG_EN = H: Signal Detect Circuit Enabled: When no valid clock device enters Standby Mode. Internal weak pull down                                      |  |  |  |  |  |

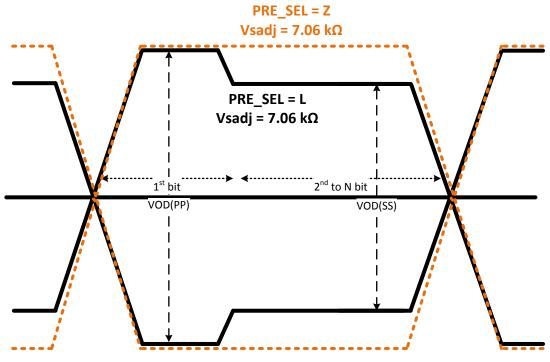

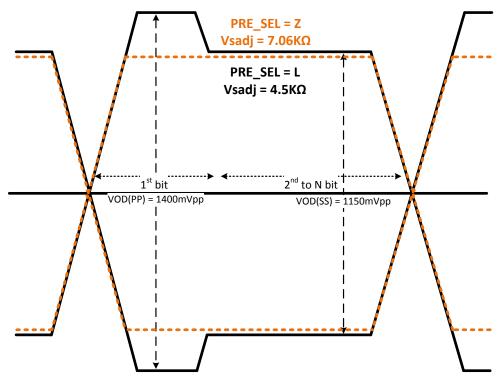

| PRE_SEL         | 20                  | I<br>3-Level       | De-emphasis Control when I2C_EN/PIN = Low. PRE_SEL = L: -2 dB PRE_SEL = No Connect: 0 dB PRE_SEL = H: Reserved When I2C_EN/PIN = High; De-emphasis is controlled through I <sup>2</sup> C                                                                                    |  |  |  |  |  |

| EQ_SEL/A0       | 21                  | I                  | Input Receive Equalization pin strap when I2C_EN/PIN = Low EQ_SEL = L: Fixed EQ at 7.5 dB EQ_SEL = No Connect: Adaptive EQ EQ_SEL = H: Fixed at 14 dB When I2C_EN/PIN = High Address Bit 1 Note: 3 level for pin strap programming but 2 level when I <sup>2</sup> C address |  |  |  |  |  |

| I2C_EN/PIN      | 10                  | I                  | I2C_EN/PIN = High; Puts Device into I2C Control Mode I2C_EN/PIN = Low; Puts Device into Pin Strap Mode                                                                                                                                                                       |  |  |  |  |  |

| SCL_CTL         | 15                  | I/O                | $I^2C$ Clock Signal when $I^2C$ _EN/PIN = High.<br>Note: When I2C_EN = Low; Pin strapping takes priority and those functions cannot be changed by $I^2C$                                                                                                                     |  |  |  |  |  |

| SDA_CTL         | 16                  | I/O                | I <sup>2</sup> C Data Signal when I <sup>2</sup> C_EN/PIN = High Note: When I2C_EN = Low; Pin strapping takes priority and those functions cannot be changed by I <sup>2</sup> C                                                                                             |  |  |  |  |  |

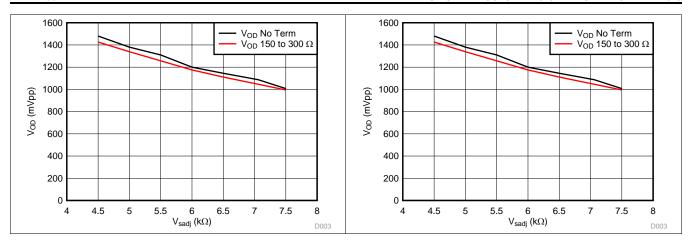

| VSadj           | 22                  | I                  | TMDS Output Voltage Swing Control; Nominal 7.06 kΩ Resistor to GND                                                                                                                                                                                                           |  |  |  |  |  |

<sup>(1) (1)</sup> G = Ground, I = Input, O = Output, P = Power (2) (H) Logic High (Pin strapped to VCC through 65 k $\Omega$  resistor); (L) Logic Low (Pin strapped to GND through 65 k $\Omega$  resistor); (Mid-Level = No connect)

#### Pin Functions (continued)

| P           | PIN    |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| A1          | 27     | I                  | High address bit 2 for I <sup>2</sup> C programming Weak internal pull down. Note: When I2C_EN/PIN = Low for Pin Strapping Mode leave this pin as No connect                                                                                                                                                                                                                                                             |  |

| TX_TERM_CTL | 36     | l<br>3-Level       | Transmit Termination Control TX_TERM_CTL = H: No transmit Termination $TX\_TERM\_CTL = L: 150 - 300 \ \Omega$ $TX\_TERM\_CTL = No \ Connect: Automatically selects the termination impedance 2 \ Gbps > DR \leq 3.4 \ Gbps - 150 - 300 \ \Omega \ differential \ near \ end \ termination DR < 2 \ Gbps - no \ termination Note: If left floating; the device will be in Automatic Select Mode. DR stands for Data Rate$ |  |

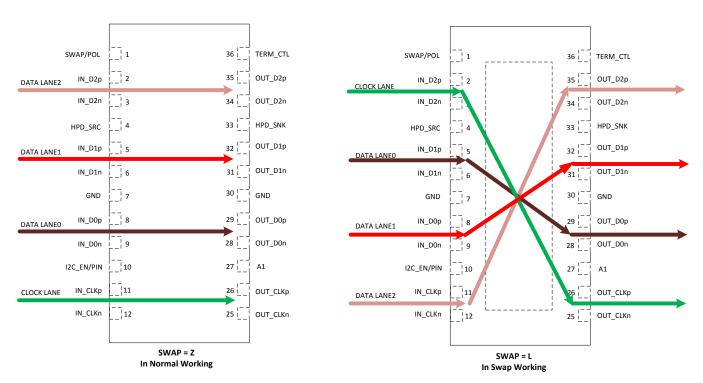

| SWAP/POL    | 1      | I<br>3-Level       | Receive Polarity Swap and Receive Lane Swap control pin SWAP/POL = H: Receive Lanes Polarity Swap (Retimer Mode Only) SWAP/POL = L: Receive Lanes (Retimer and Redriver Mode) Swap SWAP/POL = No Connect, Normal Operation                                                                                                                                                                                               |  |

| NC          | 18, 40 | -                  | No connect                                                                                                                                                                                                                                                                                                                                                                                                               |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                       |                                                                                                | MIN                      | MAX                     | UNIT |

|---------------------------------------|------------------------------------------------------------------------------------------------|--------------------------|-------------------------|------|

| Complex Valtages Dange                | VCC                                                                                            | -0.3                     | 4                       |      |

| Supply Voltage Range                  | VDD                                                                                            | -0.3                     | 1.4                     |      |

|                                       | Main Link Input Differential Voltage (IN_Dx, IN_CLKx); I <sub>IN</sub> = 15mA                  | V <sub>CC</sub> - 0.75 V | V <sub>CC</sub> + 0.3 V |      |

|                                       | TMDS Outpus ( OUT_Dx)                                                                          | -0.3                     | 4                       | V    |

| Voltage Range                         | HPD_SRC, Vsadj, SDA_CTL, SCL_CTL, OE, A1, PRE_SEL, EQ_SEL/A0, I2C_EN/PIN, SIG_EN, TX_TERM_CTL, | -0.3                     | 4                       |      |

|                                       | HDP_SNK, SDA_SNK, SCL_SNK, SDA_SRC, SCL_SRC                                                    | -0.3                     | 6                       |      |

| Input Current I <sub>IN</sub>         | Main Link Input Differential Voltage (IN_Dx, IN_CLKx);                                         |                          | 15                      | mA   |

| Continuous power dissipation          | on                                                                                             | See Therma               | I Information           |      |

| Storage temperature, T <sub>stg</sub> |                                                                                                | -65                      | 150                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values, except differential voltages, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with JEDEC Standard 22, Test Method A114-B

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                                       |                                                                                               | MIN       | NOM  | MAX                                                                                                      | UNIT |

|----------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|------|----------------------------------------------------------------------------------------------------------|------|

| V <sub>CC</sub>      | Supply Voltage Nominal Value 3.3 V                                    |                                                                                               | 3.135     | 3.3  | 3.465                                                                                                    | V    |

| $V_{DD}$             | Supply Voltage Nominial Value 1.2 V                                   |                                                                                               | 1.1       | 1.2  | 1.27                                                                                                     | V    |

| T <sub>STG</sub>     | Storage temperature                                                   |                                                                                               | -65       |      | 150                                                                                                      | °C   |

| T <sub>CASE</sub>    | Case temperature                                                      |                                                                                               |           |      | 92.7                                                                                                     | °C   |

| <del>-</del>         | Operating free-air temperature (TMD                                   | S171)                                                                                         | 0         |      | 85                                                                                                       | °C   |

| T <sub>A</sub>       | Operating free-air temperature (TMD                                   | S171I)                                                                                        | -40       |      | 85                                                                                                       | °C   |

| MAIN LINI            | K DIFFERENTIAL PINS                                                   |                                                                                               |           |      |                                                                                                          |      |

| V <sub>ID(PP)</sub>  | Peak-to-peak input differential voltage                               | •                                                                                             | 75        |      | 1560                                                                                                     | mVpp |

| V <sub>IC</sub>      | Input Common Mode Voltage                                             |                                                                                               | VCC - 0.4 |      | VCC + 0.1                                                                                                | V    |

| d <sub>R</sub>       | Data rate                                                             |                                                                                               | 0.25      |      | 3.4                                                                                                      | Gbps |

| R <sub>(VSADJ)</sub> | TMDS compliant swing voltage bias r                                   | esistor 1%                                                                                    |           | 7.06 |                                                                                                          | ΚΩ   |

| DDC, I2C,            | HPD, AND CONTROL PINS                                                 |                                                                                               |           |      |                                                                                                          |      |

| V <sub>I(DC)</sub>   | DC Input Voltage                                                      | HDP_SNK, SDA_SNK, SCL_SNK,<br>SDA_SRC, SCL_SRC                                                | -0.3      |      | 5.5                                                                                                      | V    |

| 1(50)                | . 5                                                                   | All other Local I <sup>2</sup> C, and control pins                                            | -0.3      |      | 3.6                                                                                                      | V    |

| $V_{IL}$             | Low-level input voltage HPD                                           | Low-level input voltage HPD                                                                   |           |      | 0.8                                                                                                      | V    |

|                      | Low-level input voltage at DDC/I2C                                    |                                                                                               |           |      | 0.3 x V <sub>CC</sub>                                                                                    | V    |

| V IL                 | Low-level input voltage at PRE_SEL, SWAP/POL pins only <sup>(1)</sup> | Low-level input voltage at PRE_SEL, EQ_SEL/A0, TX_TERM_CTL, SWAP/POL pins only <sup>(1)</sup> |           |      | 0.3                                                                                                      | V    |

| V <sub>IM</sub>      | Mid-Level input voltage at PRE_SEL, SWAP/POL pins only (1)            | EQ_SEL/A0, TX_TERM_CTL,                                                                       | 1         | 1.2  | 1.4                                                                                                      | V    |

|                      | High-level input voltage at HPD                                       |                                                                                               | 2         |      |                                                                                                          | V    |

|                      | High-level input voltage at I <sup>2</sup> C and SI                   | DA_SRC, SCL_SRC                                                                               | 1.8       |      | 150<br>92.7<br>85<br>85<br>1560<br>VCC + 0.1<br>3.4<br>5.5<br>3.6<br>0.8<br>0.3 × V <sub>CC</sub><br>0.3 | V    |

| $V_{IH}$             | High-level input voltage at SDA_SNK                                   | , SCL_SNK                                                                                     | 2.8       |      |                                                                                                          |      |

| V <sub>IH</sub>      | High-level input voltage at PRE_SEL, SWAP/POL pins only (1)           | EQ_SEL/A0, TX_TERM_CTL,                                                                       | 2.6       |      |                                                                                                          | V    |

| V <sub>OL</sub>      | Low-level output voltage                                              |                                                                                               |           |      | 0.4                                                                                                      | V    |

| V <sub>OH</sub>      | High-level output voltage                                             |                                                                                               | 2.4       |      |                                                                                                          | V    |

| f <sub>SCL</sub>     | SCL clock frequency fast I <sup>2</sup> C mode for                    | or local I <sup>2</sup> C control                                                             |           | 400  |                                                                                                          | kHz  |

| C <sub>bus</sub>     | Total capacitive load for each bus line                               | e (DDC and local I <sup>2</sup> C terminals)                                                  |           |      | 400                                                                                                      | pF   |

| d <sub>R(DDC)</sub>  | DDC Data rate                                                         | •                                                                                             |           | 100  | 400                                                                                                      | kbps |

| l <sub>IH</sub>      | High level input current                                              |                                                                                               | 30        |      | 30                                                                                                       | μA   |

| I <sub>IL</sub>      | Low level input current                                               |                                                                                               | -25       |      | 25                                                                                                       | μA   |

| I <sub>os</sub>      | Short circuit output current                                          |                                                                                               | -50       |      | 50                                                                                                       | mA   |

| I <sub>OZ</sub>      | High impedance output current                                         |                                                                                               |           |      | 10                                                                                                       | μΑ   |

| R <sub>(OEPU)</sub>  | Pull up resistance on OE pin                                          |                                                                                               | 150       |      | 250                                                                                                      | ΚΩ   |

<sup>(1)</sup> These values are based upon a microcontroller driving the control pins. The pull up/down/floating resistor configuration will set control pins properly which will have a different value than shown due to internal biasing.

### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | RGZ (QFN) | LINUT |

|----------------------|----------------------------------------------|-----------|-------|

|                      | I HERMAL METRIC**                            | 48 PINS   | UNIT  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 31.1      |       |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 18.2      |       |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.1       | °C/W  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.4       | °C/VV |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.1       |       |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.2       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

The Maximum rating is simulated at 3.465 V  $V_{CC}$  and 1.27 V  $V_{DD}$  and at 85°C temperature. The Typical rating is simulated at 3.3  $V_{CC}$  and 1.2 V  $V_{DD}$  and at 27°C temperature (unless otherwise noted)

|                                      | PARAMETER                                                       | TEST CONDIT                                                                                                   | IONS                                                              | MIN                        | TYP | MAX                        | UNIT |

|--------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|-----|----------------------------|------|

| Power Supply                         | ,                                                               |                                                                                                               |                                                                   |                            |     |                            |      |

| P <sub>(D1)</sub> <sup>(1) (2)</sup> | Device power Dissipation (Retimer Operation)                    | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V, V <sub>DD</sub><br>IN_Dx: VID_PP = 1200 mV, I2C_E                  |                                                                   |                            | 675 | 875                        | mW   |

| P <sub>(D2)</sub> <sup>(1) (2)</sup> | Device power Dissipation (Redriver Operation)                   | H, EQ_CTL= H, SDA_CTL/CLK_C<br>3.4 Gbps TMDS pattern, V <sub>I</sub> = 3.3 V                                  |                                                                   |                            | 400 | 600                        | mW   |

| P <sub>(SD1)</sub> <sup>(1)(2)</sup> | Device power in Standby                                         | OE = H, $V_{CC}$ = 3.3 V / 3.465 V $V_{DD}$ = 1.2 V / 1.27 V , HPD = H, No Valid input Signal                 | <sub>DD</sub> = 1.2 V / 1.27 V , HPD = H,<br>o Valid input Signal |                            | 50  | 100                        | mW   |

| P <sub>(SD2)</sub> <sup>(1)(2)</sup> | Device power in PowerDown                                       | E = L, V <sub>CC</sub> = 3.3 V / 3.465 V<br><sub>DD</sub> = 1.2 V / 1.27 V                                    |                                                                   |                            | 10  | 30                         | mW   |

| I <sub>CC1</sub> (1)(2)              | V <sub>CC</sub> Supply current (TMDS 3.4 Gpbs Retimer Mode)     | DE = H, V <sub>CC</sub> = 3.3 V / 3.465 V<br><sub>DD</sub> = 1.2 V / 1.27 V                                   |                                                                   |                            | 80  | 140                        | mA   |

| I <sub>DD1</sub> <sup>(1)</sup> (2)  | V <sub>DD</sub> Supply current (TMDS 3.4<br>Gpbs Retimer Mode)  | IN_Dx: VID_PP = 1200 mV,<br>3.4 Gbps TMDS pattern I2C_EN/PI<br>EQ_CTL = H, SDA_CTL/CLK_CTL                    |                                                                   |                            | 286 | 325                        | mA   |

| I <sub>CC2</sub> <sup>(1)(2)</sup>   | V <sub>CC</sub> Supply current (TMDS 3.4<br>Gpbs Redriver Mode) | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V<br>V <sub>DD</sub> = 1.2 V / 1.27 V                                 |                                                                   |                            | 51  |                            | mA   |

| I <sub>DD2</sub> <sup>(1)(2)</sup>   | V <sub>DD</sub> Supply current (TMDS 3.4<br>Gpbs Redriver Mode) | IN_Dx: VID_PP = 1200 mV, 3.4 Gbps TMDS pattern I2C_EN/PI EQ_CTL = H, SDA_CTL/CLK_CTL                          |                                                                   |                            | 188 |                            | mA   |

|                                      |                                                                 | OE = H, V <sub>CC</sub> = 3.3 V / 3.465 V                                                                     | 3.3V Rail <sup>(1)</sup>                                          |                            | 6   | 6 15                       |      |

| $I_{(SD1)}$                          | Standby current                                                 | V <sub>DD</sub> = 1.2 V / 1.27 V<br>HPD = H: No valid signal on<br>IN_CLK                                     | 1.2V Rail                                                         |                            | 40  | 50                         | mA   |

|                                      |                                                                 | OE = L, V <sub>CC</sub> = 3.3 V / 3.465 V 3.3V Rail <sup>(1)</sup> V <sub>DD</sub> = 1.2 V / 1.27 V 1.2V Rail |                                                                   |                            | 2   | 5                          |      |

| I <sub>(SD2)</sub>                   | PowerDown current                                               |                                                                                                               |                                                                   |                            | 3.5 | 15                         | mA   |

| TMDS Differer                        | ntial Input                                                     |                                                                                                               |                                                                   |                            |     |                            |      |

| D <sub>(R_RX_DATA)</sub>             | TMDS data lanes data rate                                       |                                                                                                               |                                                                   | 0.25                       |     | 3.4                        | Gbps |

| D <sub>(R_RX_CLK)</sub>              | TMDS clock lanes clock rate                                     |                                                                                                               |                                                                   | 25                         |     | 340                        | MHz  |

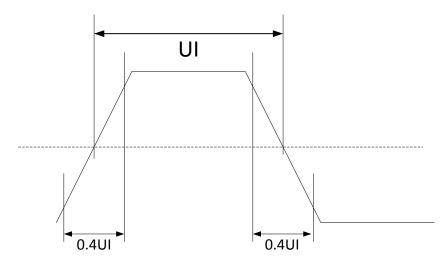

| t <sub>RX_DUTY</sub>                 | Input clock duty circle                                         |                                                                                                               |                                                                   | 40%                        | 50% | 60%                        |      |

| t <sub>CLK_JIT</sub>                 | Input clock jitter tolerance                                    |                                                                                                               |                                                                   |                            |     | 0.3                        | Tbit |

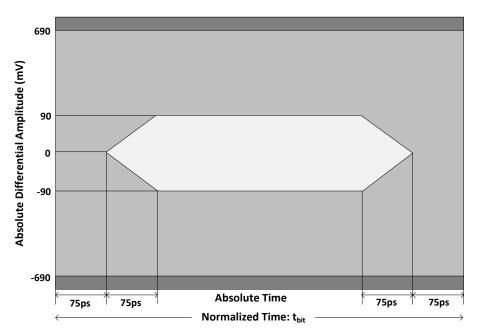

| t <sub>DATA_JIT</sub>                | Input data jitter tolerance                                     | Test the TTP2 See Figure 11                                                                                   |                                                                   |                            |     | 150                        | ps   |

| t <sub>RX_INTRA</sub>                | Input intra-pair skew tolerance                                 | Test at TTP2 when DR =1.6 Gbps                                                                                | See Figure 11                                                     | 112                        |     |                            | ps   |

| t <sub>RX_INTER</sub>                | Input inter-pair skew tolerance                                 |                                                                                                               |                                                                   |                            |     | 1.8                        | ns   |

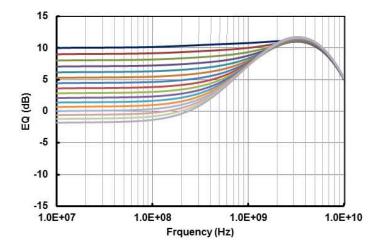

| $E_{QH(D)}$                          | Fixed EQ gain for data lane IN_D(0,1,2)n/p                      | EQ_SEL/A0=H; Fixed EQ gain, tes                                                                               | t at 3.4 Gbps                                                     |                            | 14  |                            |      |

| $E_{QL(D)}$                          | Fixed EQ gain for data lane IN_D(0,1,2)n/p                      | EQ_SEL/A0=L; Fixed EQ gain, test                                                                              | t at 3.4 Gbps                                                     |                            | 7.5 |                            | dB   |

| $E_{QZ(D)}$                          | Adaptive EQ gain for data lane IN_D(0,1,2)n/p                   | EQ_SEL/A0=NC; adaptive EQ                                                                                     |                                                                   | 2                          |     | 14                         |      |

| $E_{Q(C)}$                           | EQ gain for clock lane IN_CLKn/p                                | EQ_SEL/A0=H,LNC                                                                                               |                                                                   |                            | 0   |                            |      |

| R <sub>(INT)</sub>                   | Input differential termination impedance                        |                                                                                                               |                                                                   | 90                         | 100 | 115                        | Ω    |

| TMDS Differer                        | ntial Output                                                    |                                                                                                               |                                                                   |                            |     |                            |      |

| V                                    | Single-ended high level output                                  | PRE_SEL = NC; TX_TERM_CTL = Mbps; VSadj = $7.06 \text{ k}\Omega$                                              | H; OE = H; DR = 750                                               | V <sub>CC</sub> -<br>10mV  |     | V <sub>CC</sub> +<br>10mV  |      |

| V <sub>OH</sub>                      | voltage                                                         | PRE_SEL = NC; TX_TERM_CTL = Gbps; VSadj = 7.06 kΩ                                                             | = H; OE = NC; DR = 2.97                                           | V <sub>CC</sub> -<br>200mV |     | V <sub>CC</sub> + 10mV     |      |

| V                                    | Single-ended low level output voltage No Pre-emphasis, Load is  | PRE_SEL = NC; TX_TERM_CTL = Mbps; VSadj = 7.06 kΩ                                                             | = H; OE = H; DR = 750                                             | V <sub>CC</sub> -<br>600mV |     | V <sub>CC</sub> -<br>400mV | V    |

| V <sub>OL</sub>                      | 50 Ω pull ups to 3.135 V and 3.465 V                            | PRE_SEL = NC; TX_TERM_CTL = Gbps; VSadj = 7.06 k $\Omega$                                                     | = H; OE = NC; DR = 2.97                                           | V <sub>CC</sub> - 700mV    |     | V <sub>CC</sub> - 400mV    |      |

<sup>(1)</sup>  $I_{CC}$  is a direct result of the source design as the TMDS171 integrated receive termination resistor accounts for 85 mA to 100 mA. (2) 4.  $I_{DD}$  is impacted by ARC usage. Connecting a 500 K $\Omega$  resistor to GND at SPDIF reduces the value by more than 20 mA

# **Electrical Characteristics (continued)**

The Maximum rating is simulated at 3.465 V  $V_{CC}$  and 1.27 V  $V_{DD}$  and at 85°C temperature. The Typical rating is simulated at 3.3  $V_{CC}$  and 1.2 V  $V_{DD}$  and at 27°C temperature (unless otherwise noted)

|                                | PARAMETER                                                                                                         | TEST CONDITIONS                                                                                           | MIN                 | TYP            | MAX                        | UNIT |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|----------------|----------------------------|------|

| V <sub>(SWING_DA)</sub>        | Single-ended output voltage swing on data lane                                                                    | PRE_SEL = NC; TX_TERM_CTL = H/NC; OE = NC; DR = $\leq$ 3.4 Gbps; VSadj = 7.06 k $\Omega$                  | 400                 | 500            | 600                        |      |

| V <sub>(SWING_CLK)</sub>       | Single-ended output voltage swing on clock lane                                                                   | PRE_SEL = NC; TX_TERM_CTL = H/NC; OE = NC; DR = $\leq$ 3.4 Gbps; VSadj = 7.06 kΩ                          | 400                 | 500            | 600                        |      |

| $\Delta V_{(SWING)}$           | Change in single-end output voltage swing per 100Ω ΔVSadj                                                         |                                                                                                           |                     | 20             |                            |      |

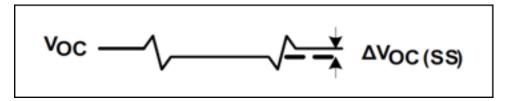

| $\Delta V_{OCM(SS)}$           | Change in steady state output<br>common mode voltage between<br>logic levels                                      |                                                                                                           | -5                  |                | 5                          | mV   |

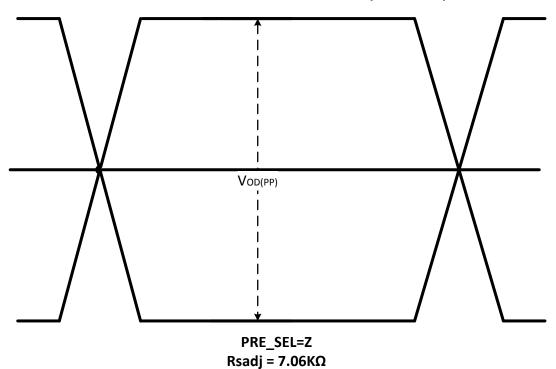

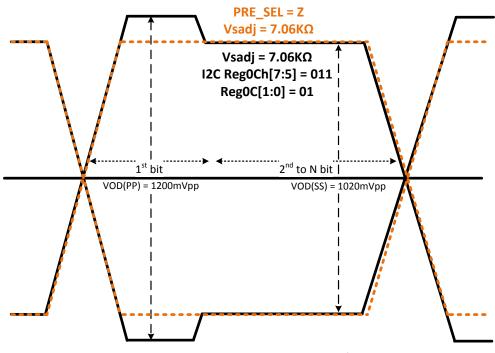

| $V_{OD(PP)}$                   | Initial output differential voltage<br>before steady state when pre-<br>emphasis or de-emphasis is<br>implemented | VSadj = 7.06 kΩ; PRE_SEL = NC, See Figure 8                                                               | 800                 |                | 1200                       |      |

| V <sub>OD(SS)</sub>            | Steady state output differential voltage                                                                          | VSadj = 7.06 kΩ; PRE_SEL = L, See Figure 9                                                                | 600                 |                | 1075                       |      |

| los                            | Short circuit current limit                                                                                       | Main link output shorted to GND                                                                           |                     |                | 50                         | mA   |

| I <sub>LEAK</sub>              | Failsafe condition leakage current                                                                                | $\rm V_{CC}$ = 0 V; $\rm V_{DD}$ = 0 V; TMDS Outputs pulled to 3.3V through 50 $\Omega$ resistor          |                     |                | 45                         | μA   |

| R <sub>(TERM)</sub>            | Source Termination resistance                                                                                     |                                                                                                           | 150                 |                | 300                        | Ω    |

| DDC and I2C                    |                                                                                                                   |                                                                                                           |                     |                |                            |      |

| V <sub>IL</sub>                | SCL/SDA_CTL, SCL/SDA_SRC low level input voltage                                                                  |                                                                                                           |                     |                | 0.3xV <sub>CC</sub>        |      |

| V <sub>IH</sub>                | SCL/SDA_CTL, SCL/SDA_SRC high level input voltage                                                                 |                                                                                                           | 0.7xV <sub>CC</sub> |                | V <sub>CC</sub> + 0.5      | V    |

| V <sub>OL</sub>                | SCL/SDA_CTL, SCL/SDA_SRC low level output voltage                                                                 | $I_O = 3$ mA and $V_{CC} > 2$ V<br>$I_O = 3$ mA and $V_{CC} < 2$ V                                        |                     |                | 0.4<br>0.2xV <sub>CC</sub> |      |

| HPD                            |                                                                                                                   | 10 - 3 THA and VCC \ 2 V                                                                                  |                     |                | U.ZXVCC                    |      |

| V <sub>IH</sub>                | High-level input voltage                                                                                          | HPD_SNK                                                                                                   | 2.1                 |                |                            |      |

| V <sub>IL</sub>                | Low-level input voltage                                                                                           | HPD_SNK                                                                                                   |                     |                | 0.8                        |      |

| V <sub>OH</sub>                | High-level output voltage                                                                                         | I <sub>OH</sub> = -500 μA; HPD_SRC                                                                        | 2.4                 |                | 3.6                        | V    |

| V <sub>OL</sub>                | Low-level output voltage                                                                                          | I <sub>OL</sub> = -500 μA; HPD_SRC                                                                        | 0                   |                | 0.1                        |      |

| I <sub>LEAK</sub>              | Failsafe condition leakage current                                                                                | V <sub>CC</sub> = 0 V; V <sub>DD</sub> = 0 V; HPD_SNK = 5 V                                               |                     |                | 40                         |      |

| LEAR                           | Tancare contained loakage carrent                                                                                 | Device powered; V <sub>IH</sub> = 5 V; I <sub>H(HPD)</sub> includes R <sub>pd(HPD)</sub> resistor current |                     |                | 40                         |      |

| I <sub>H(HPD)</sub>            | High level input current                                                                                          | Device powered; $V_{IL} = 0.8 \text{ V}$ ; $I_{H(HPD)}$ includes $R_{pd(HPD)}$ resistor current           |                     |                | 30                         | μA   |

| R <sub>pd(HPD)</sub>           | HPD input termination to GND;                                                                                     | V <sub>CC</sub> < 0 V                                                                                     | 150                 | 190            | 220                        | kΩ   |

| SPDIF and AR                   | С                                                                                                                 |                                                                                                           |                     |                | +                          |      |

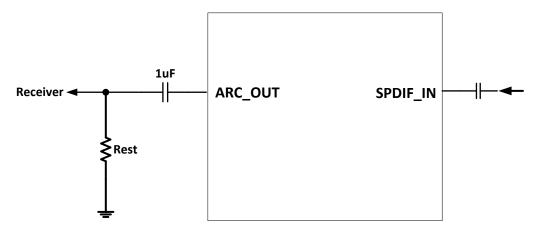

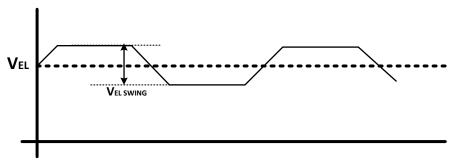

| V <sub>(EL)</sub>              | Operating DC voltage for single mode ARC output                                                                   | Test at ARC_OUT, see Figure 19                                                                            | 0                   |                | 5                          | V    |

| V <sub>IN(DC)</sub>            | Operating DC voltage for SPDIF input                                                                              |                                                                                                           |                     |                | 0.05                       | V    |

| V <sub>(SP_SW)</sub>           | Signal amplitude of SPDIF input                                                                                   |                                                                                                           | 0.2                 | 0.5            | 0.6                        | V    |

| V <sub>(EISWING)</sub>         | Signal amplitude on the ARC output                                                                                | Test at ARC_OUT, 75 $\Omega$ external termination resistor, see Figure 19                                 | 0.4                 | 0.5            | 0.6                        | V    |

| CLK <sub>(ARC)</sub>           | Signal frequency on ARC                                                                                           | Test at ARC_OUT, see Figure 19                                                                            | 3.687               | 5.645±0.<br>1% | 13.517                     | MHz  |

| Duty Cycle                     | Output Clock Duty cycle                                                                                           |                                                                                                           | 45%                 | 50%            | 55%                        | -    |

|                                | SPDIF Input DR                                                                                                    |                                                                                                           | 7.373               | 11.29          | 27.034                     | Mbps |

| Data Rate                      | •                                                                                                                 |                                                                                                           |                     |                |                            |      |

| Data Rate<br>t <sub>EDGE</sub> | The rise/fall time for ARC output                                                                                 | From 10% to 90% voltage level, see Figure 19                                                              |                     |                | 0.4                        | UI   |

|                                | The rise/fall time for ARC output The Input Termination resistance for SPDIF                                      | From 10% to 90% voltage level, see Figure 19                                                              |                     | 75             | 0.4                        | Ω    |

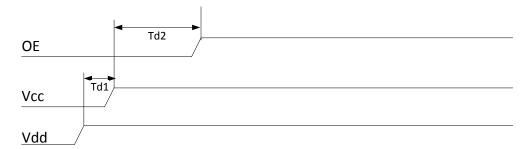

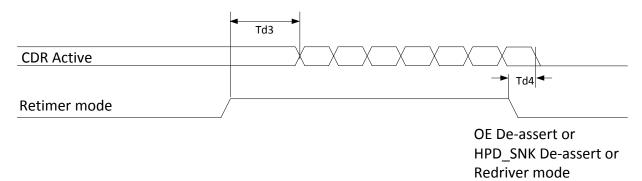

# 6.6 Switching Characteristics

The Maximum rating is simulated at 3.465 V  $V_{CC}$  and 1.27 V  $V_{DD}$  and at 85°C temperature. The Typical rating is simulated at 3.3 V  $V_{CC}$  and 1.2 V  $V_{DD}$  and at 27°C temperature (unless otherwise noted)

|                           | PARAMETER                                                                                       | TEST CONDITIONS                                                                                                           | MIN  | TYP  | MAX  | UNIT |

|---------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| TMDS Redi                 | river Mode                                                                                      | 1201 20112111211                                                                                                          |      |      |      |      |

| D <sub>R</sub>            | Data rate (Redriver mode)                                                                       |                                                                                                                           | 250  |      | 3400 | Mbps |

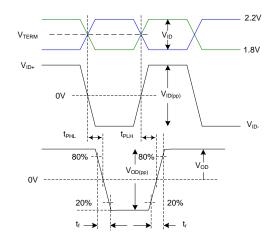

| t <sub>PLH</sub>          | Propagation delay time (low to high)                                                            |                                                                                                                           | 250  |      | 600  | Mopo |

| t <sub>PHL</sub>          | Propagation delay time (high to low)                                                            |                                                                                                                           | 250  |      | 800  |      |

| t <sub>T1</sub>           | Transition time (rise and fall time); measured at 20% and 80% levels for Data Lanes.            | TX_TERM_CTL=L; PRE_SEL=NC;<br>Data Rate 3.4 Gbps; Clock 340 MHz                                                           | 75   |      |      | ps   |

| t <sub>SK1(T)</sub>       | Intra-pair output skew                                                                          | TX_TERM_CTL=NC;<br>PRE_SEL=NC;                                                                                            |      |      | 40   | ·    |

| t <sub>SK2(T)</sub>       | Inter-pair output skew                                                                          | TX_TERM_CTL=NC;<br>PRE_SEL=NC;                                                                                            |      |      | 100  |      |

| t <sub>JITD1</sub>        | Total output data jitter                                                                        | DR = 750 Mbps, PRE_SEL = NC,                                                                                              |      |      | 0.2  |      |

| t <sub>JITC1</sub>        | Total output clock jitter                                                                       | EQ_SEL/A0 = NC. See Figure 5 at TTP3                                                                                      |      |      | 0.25 | Tbit |

| TMDS Retir                | mer Mode                                                                                        |                                                                                                                           |      |      |      |      |

| D <sub>R</sub>            | Data rate (retimer mod )                                                                        |                                                                                                                           | 1.2  |      | 3.4  | Gbps |

| d <sub>(XVR)</sub>        | Automatic redriver to Retimer Cross-<br>Over                                                    | Measured with input signal applied from 0 to 200 mV <sub>PP</sub>                                                         | 0.75 | 1.00 | 1.25 | Gbps |

| f <sub>(CROSSOVE</sub> R) | Crossover frequency hysteresis                                                                  |                                                                                                                           |      | 250  |      | MHz  |

| PLL <sub>(BW)</sub>       | Data Retimer PLL bandwidth                                                                      | Default loop bandwidth setting                                                                                            |      | 0.4  | 1    | MHz  |

| t <sub>ACQ</sub>          | Input Clock Frequency Detection and Retimer Acquisition Time                                    |                                                                                                                           |      | 180  |      | μs   |

| I <sub>JT1</sub>          | Input Clock Jitter Tolerance                                                                    | Tested when data rate > 1.0 Gbps                                                                                          |      |      | 0.3  | Tbit |

| t <sub>T1</sub>           | Transition time (rise and fall time);<br>measured at 20% and 80% levels<br>for Data Lanes. TMDS |                                                                                                                           | 75   |      |      | ps   |

| t <sub>DCD</sub>          | OUT_CLK ± duty cycle                                                                            |                                                                                                                           | 40%  | 50%  | 60%  |      |

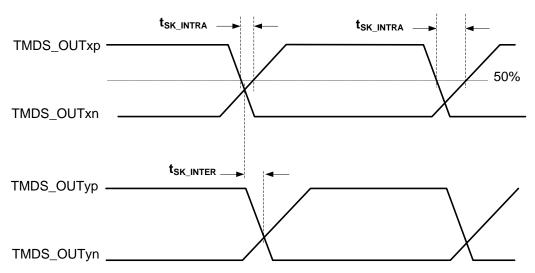

| t <sub>SK_INTER</sub>     | Inter-pair output skew                                                                          | Default setting for internal inter-pair<br>skew adjust, PRE_SEL = NC;<br>TX_TERM_CTL = NC, DR ≤ 3.4<br>Gbps; See Figure 6 |      |      | 0.2  | Tch  |

| <sup>t</sup> sk_intra     | Intra-pair output skew                                                                          | Default setting for internal intra-pair<br>skew adjust, PRE_SEL = NC;<br>TX_TERM_CTL = NC, DR ≤ 3.4<br>Gbps; See Figure 6 |      |      | 0.15 | Tbit |

| t <sub>JITC2</sub>        | Total output clock jitter                                                                       | CLK Rate ≤ 340 MHz                                                                                                        |      |      | 0.25 | Tbit |

| t <sub>JITD2</sub>        | Total output data jitter                                                                        | DR ≤ 3.4 Gbps; See Figure 11                                                                                              |      |      | 0.2  | Tbit |

| HPD                       |                                                                                                 |                                                                                                                           |      |      |      |      |

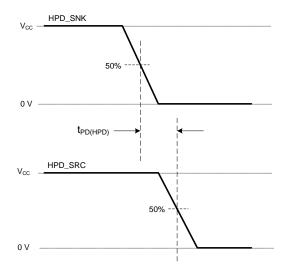

| t <sub>PD(HPD)</sub>      | Propagation delay from HPD_SNK to HPD_SRC; rising edge and falling edge <sup>(1)</sup>          | see Figure 13; not valid during switching time                                                                            |      | 40   | 120  | ns   |

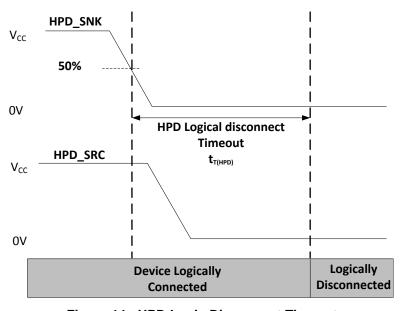

| t <sub>T(HPD)</sub>       | HPD logical disconnected timeout                                                                | see Figure 14                                                                                                             |      | 2    |      | ms   |

| DDC and I2                | ec                                                                                              |                                                                                                                           |      |      |      |      |

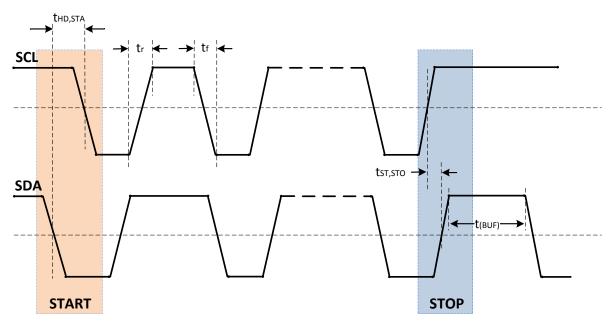

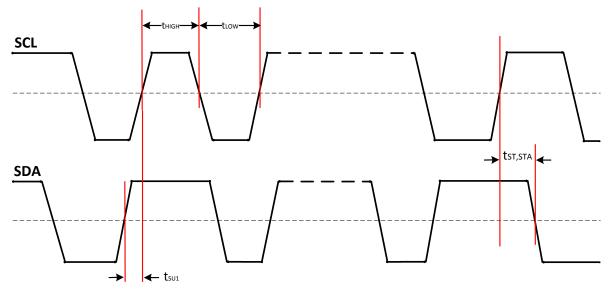

| t <sub>r</sub>            | Rise time of both SDA and SCL signals                                                           | V <sub>CC</sub> = 3.3 V                                                                                                   |      |      | 300  |      |

| t <sub>f</sub>            | Fall time of both SDA and SCL signals                                                           |                                                                                                                           |      |      | 300  | ns   |

| t <sub>HIGH</sub>         | Pulse duration, SCL high                                                                        |                                                                                                                           | 0.6  |      |      |      |

| $t_{LOW}$                 | Pulse duration, SCL low                                                                         |                                                                                                                           | 1.3  |      |      | μs   |

| t <sub>SU1</sub>          | Setup time, SDA to SCL                                                                          |                                                                                                                           | 100  |      |      | ns   |

(1) The Maximum rating is simulated at 3.465 V  $\rm V_{CC}$  and 1.27 V  $\rm V_{DD}$

## **Switching Characteristics (continued)**

The Maximum rating is simulated at 3.465 V  $V_{CC}$  and 1.27 V  $V_{DD}$  and at 85°C temperature. The Typical rating is simulated at 3.3 V  $V_{CC}$  and 1.2 V  $V_{DD}$  and at 27°C temperature (unless otherwise noted)

|                     | PARAMETER                                            | TEST CONDITIONS                                        | MIN | TYP | MAX | UNIT |

|---------------------|------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| t <sub>ST,STA</sub> | Setup time, SCL to start condition                   |                                                        | 0.6 |     |     |      |

| t <sub>HD,STA</sub> | Hold time, start condition to SCL                    |                                                        | 0.6 |     |     |      |

| t <sub>ST,STO</sub> | Setup time, SCL to stop condition                    |                                                        | 0.6 |     |     | μs   |

| t <sub>(BUF)</sub>  | Bus free time between stop and start condition       |                                                        | 1.3 |     |     |      |

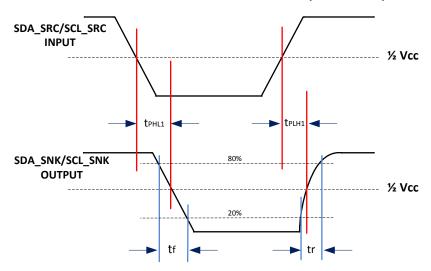

| t <sub>PLH1</sub>   | Propagation delay time, low-to-high-<br>level output | Source to Sink:100 kbps pattern;                       |     | 360 |     |      |

| t <sub>PHL1</sub>   | Propagation delay time, high-to-low-level output     | $C_{b(Sink)} = 400 \text{ pF}^{(2)}$ ; see Figure 17   |     | 230 |     | 20   |

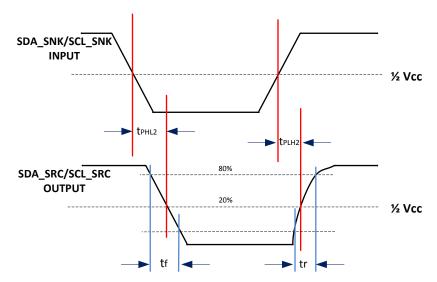

| t <sub>PLH2</sub>   | Propagation delay time, low-to-high-<br>level output | Sink to Source: 100 kbps pattern;                      |     | 250 |     | ns   |

| t <sub>PHL2</sub>   | Propagation delay time, high-to-low-level output     | $C_{b(Source)} = 100 \text{ pF}^{(2)}$ ; see Figure 18 |     | 200 |     |      |

<sup>(2)</sup> Cb = total capacitance of one bus line in pF

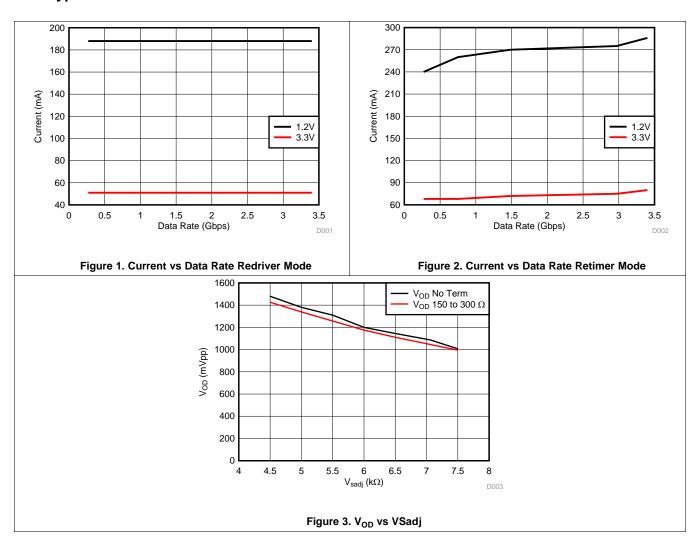

## 6.7 Typical Characteristics

### 7 Parameter Measurement Information

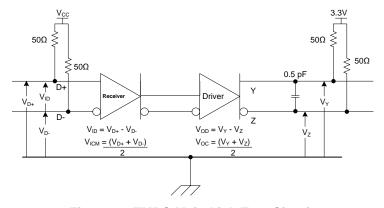

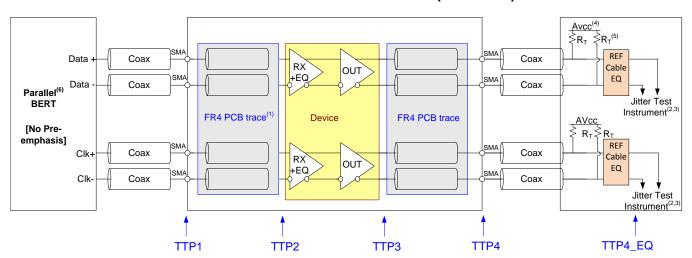

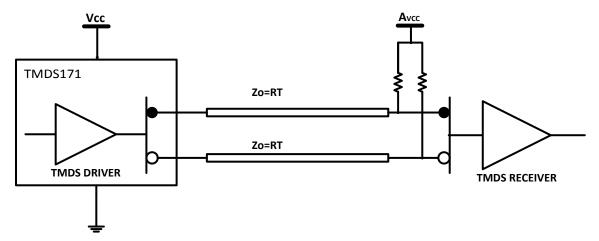

Figure 4. TMDS Main Link Test Circuit

Figure 5. Input/Output Timing Measurements

Figure 6. TMDS Output Skew Measurements

Figure 7. HDMI/DVI TMDS Output Common Mode Measurement

Figure 8. Output Differential Waveform

Figure 9. Output De-emphasis Waveform

- (1) The FR4 trace between TTP1 and TTP2 is designed to emulate 1-8" of FR4, connector and another 1-8" of FR4. Trace width -4 mils. 100  $\Omega$  differential impedance.

- (2) All Jitter is measured at a BER of 10<sup>-9</sup>

- (3) Residual jitter reflects the total jitter measured at TTP4 minus the jitter measured at TTP1

- (4) AVCC = 3.3 V

- (5)  $R_T = 50 \Omega$

- (6) The input signal from parallel Bert does not have any pre-emphasis. Refer to Recommended Operating Conditions.

Figure 10. Jitter Measurement Circuit

Figure 11. HDMI Output Jitter Measurement

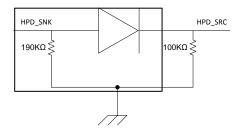

Figure 12. HPD Test Circuit

Figure 13. HPD Timing Diagram No. 1

Figure 14. HPD Logic Disconnect Timeout

Figure 15. Start and Stop Condition Timing

Figure 16. SCL and SDA Timing

Product Folder Links: TMDS171

16

Figure 17. DDC Propagation Delay - Source to Sink

Figure 18. DDC Propagation Delay - Sink to Source

Figure 19. ARC Output

Figure 20. Rise/Fall Time of ARC

# 8 Detailed Description

#### 8.1 Overview

The TMDS171 is a digital video interface (DVI) or high-definition multimedia interface (HDMI) retimer. The TMDS171 supports four TMDS channels, Audio Return Channel (SPDIF\_IN/ARC\_OUT), Hot Plug Detect, and a Digital Display Control (DDC) interfaces. The TMDS171 supports signaling rates up to 3.4 Gbps to allow for the highest resolutions of 4k2k30p 24 bits per pixel and up to WUXGA 12-bit color depth or 1080p with higher refresh rates. The TMDS171 can automatically configure itself as a re-driver at low data rate (< 1 Gbps) or as a re-timer above this data rate. For passing compliance and reducing system level design issues several features have been included such as TMDS output amplitude adjust using an external resistor on the VSADJ pin and source termination selection control. Device operation and configuration can be programmed by pin strapping or I<sup>2</sup>C. Four TMDS171s can be used on one I<sup>2</sup>C bus when I2C\_EN enable and device address set by A0/A1.

To reduce active power the TMDS171 supports dual power supply rails of 1.2 V on  $V_{DD}$  and 3.3 V on  $V_{CC}$ . The TMDS171 supports several methods of power management. It can enter power down mode using three methods; (1) HPD is low; (2) Writing an 1 to register 09h[3]; or (3) de-asserting OE. If using OE, the device must be reprogrammed via  $I^2C$  if it was originally programmed this way. The SIG\_EN pin enables the signal detect circuit that provides an automatic power-management feature during normal operation. When no valid signal is present on the inputs the device enters Stand by mode. By disabling the detect circuit the receiver block is always on which is needed for certain HDMI CTS test. DDC link supports 100 Kbps data rate default and 400 kbps adjustable by software.

TMDS171 supports both fixed EQ gain control or adaptive equalization to compensate for different lengths of input cables or board traces. The EQ gain can be software adjusted by I<sup>2</sup>C control or selection between two fixed values or adaptive equalization by pin strapping EQ\_SEL pin. Implementers can use the TX\_TERM\_CTL pin to change the transmitter termination impedance for better output performance when working in HDMI1.4b or leave it floating. When floating the TMDS171 in conjunction with the rate detect will automatically change its output termination to be compatible with HDMI1.4b requirements.

The TMDS171 supports single ended mode audio return channel. To assist in ease of implementation the TMDS171 supports receive lane swapping and receive polarity swap. When swapping the input lanes IN\_CLK and IN\_D2 swap and IN\_D1 and IN\_D0 swap with each other. Swap works in both retimer and redriver mode. Polarity swap will swap the receive pins n and p channel polarity in each lane and is only available during retimer mode. Both lane swap and polarity swap can be implemented at the same time in retimer mode using I<sup>2</sup>C control.