THS4031, THS4032

SLOS224H - JULY 1999-REVISED JUNE 2016

# THS403x 100-MHz Low-Noise High-Speed Amplifiers

#### **Features**

- Ultra-Low 1.6 nV/√Hz Voltage Noise

- High Speed:

- 100-MHz Bandwidth [G = 2 (-1), -3 dB]

- 100-V/μs Slew Rate

- Very Low Distortion

- THD = -72 dBc (f = 1 MHz,  $R_1$  = 150 Ω)

- THD = -90 dBc (f = 1 MHz,  $R_L = 1 \text{ k}\Omega$ )

- Low 0.5-mV (Typical) Input Offset Voltage

- 90-mA Output Current Drive (Typical)

- Typical Operation from ±5 V to ±15 V

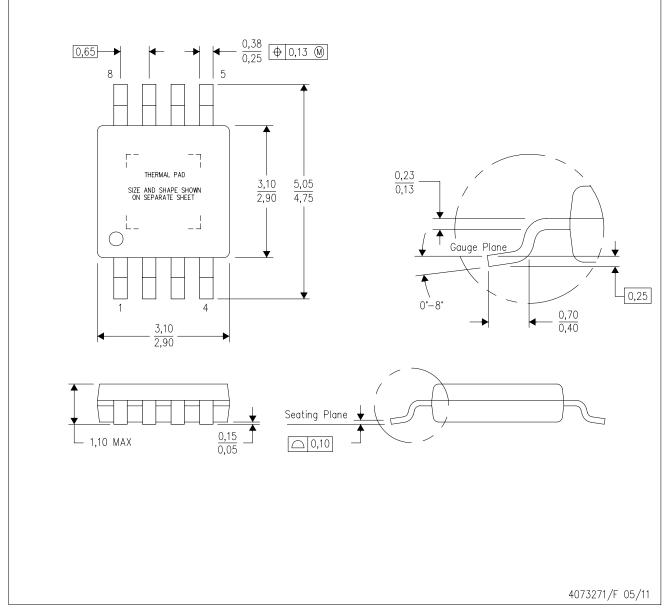

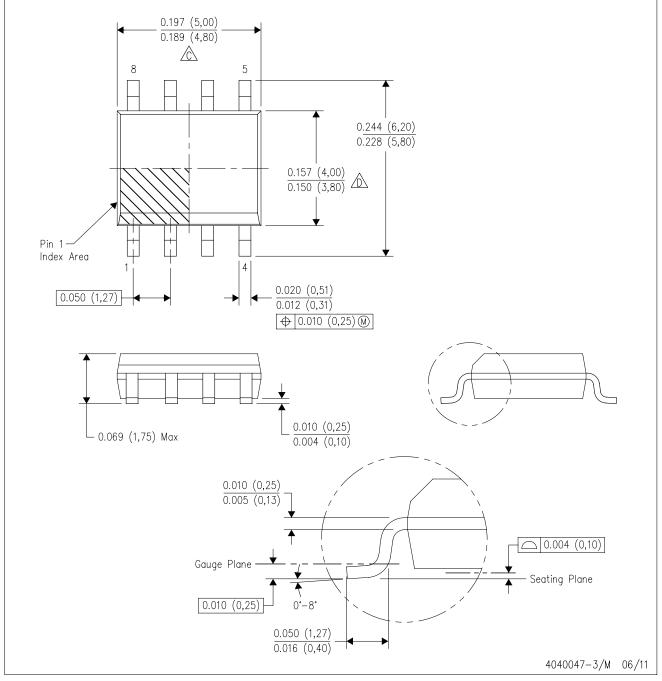

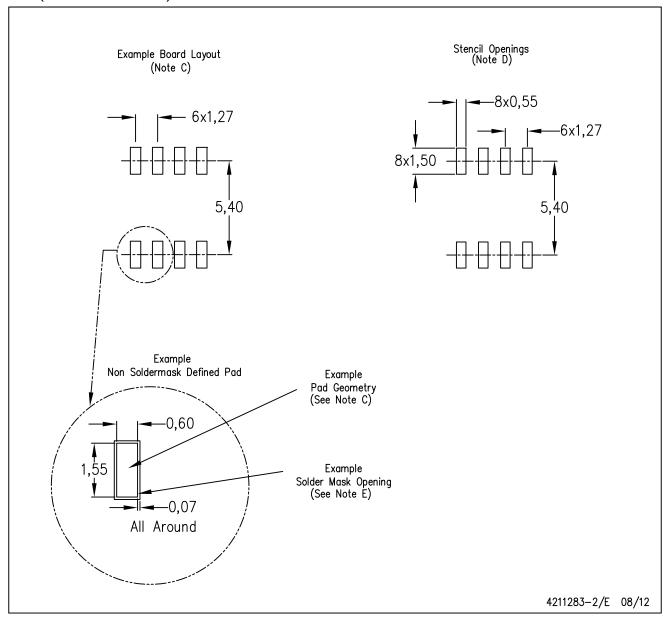

- Available in Standard SOIC and MSOP-PowerPAD™, Packages

- **Evaluation Module Available**

## Applications

- Low-Noise, Wideband Amplifier for Industrial Applications

- Voltage-Controlled Oscillators

- Active Filters

- Video Amplifiers

- Cable Drivers

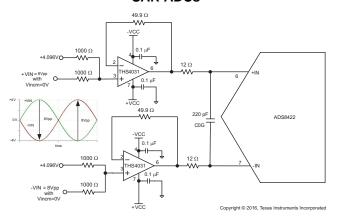

#### High-Performance, Low-Noise Driver for 16-bit **SAR ADCs**

# 3 Description

The THS4031 and THS4032 are ultra-low voltage noise, high-speed voltage feedback amplifiers that are ideal for applications requiring low voltage noise, including communications and imaging. The single amplifier THS4031 and the dual amplifier THS4032 offer very good AC performance with 100-MHz bandwidth ( $\ddot{G}$  = 2), 100-V/ $\mu$ s slew rate, and 60-ns settling time (0.1%). The THS4031 and THS4032 are unity-gain stable with 275-MHz bandwidth. These amplifiers have a high drive capability of 90 mA and draw only 8.5-mA supply current per channel. With -90 dBc of total harmonic distortion (THD) at f = 1 MHz and a very low noise of 1.6 nV/ $\sqrt{Hz}$ , the THS4031 and THS4032 are ideally suited for applications requiring low distortion and low noise such as buffering analog-to-digital converters.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE           | BODY SIZE (NOM)   |  |  |

|-------------|-------------------|-------------------|--|--|

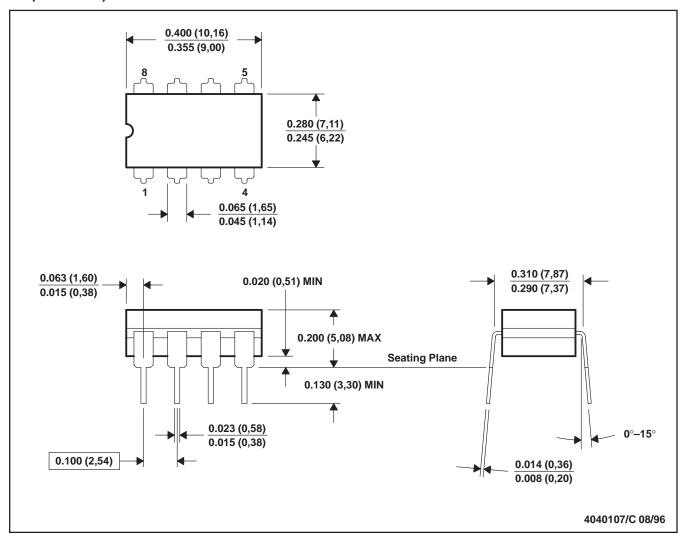

| THS403x     | SOIC (8)          | 4.90 mm × 3.91 mm |  |  |

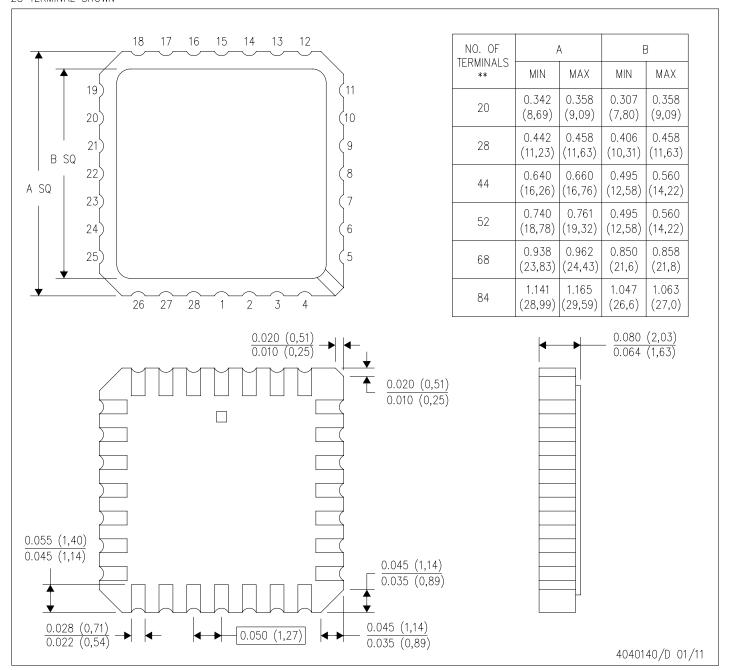

|             | MSOP-PowerPAD (8) | 3.00 mm × 3.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

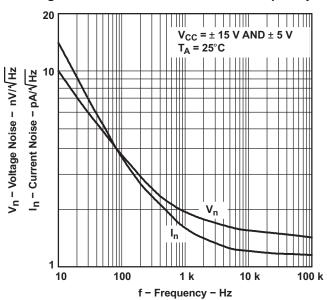

#### **Voltage Noise and Current Noise vs Frequency**

Page

**Page**

#### **Table of Contents**

| 1 | Features 1                                                 |    | 9.4 Device Functional Modes                         | 24                 |

|---|------------------------------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 | Applications 1                                             | 10 | Application and Implementation                      | 25                 |

| 3 | Description 1                                              |    | 10.1 Application Information                        | 25                 |

| 4 | Revision History2                                          |    | 10.2 Typical Application                            | 25                 |

| 5 | Device Comparison Table3                                   | 11 | Power Supply Recommendations                        | 28                 |

| 6 | Pin Configuration and Functions 4                          | 12 | Layout                                              | 28                 |

| 7 | Specifications5                                            |    | 12.1 Layout Guidelines                              | 28                 |

| • | 7.1 Absolute Maximum Ratings                               |    | 12.2 Layout Example                                 | 28                 |

|   | 7.2 ESD Ratings                                            |    | 12.3 General PowerPAD™ Design Considerations        | <b>2</b> 9         |

|   | 7.3 Recommended Operating Conditions                       | 13 | Device and Documentation Support                    | 32                 |

|   | 7.4 Thermal Information – THS4031                          |    | 13.1 Device Support                                 | 32                 |

|   | 7.5 Thermal Information – THS4032                          |    | 13.2 Documentation Support                          | 32                 |

|   | 7.6 Electrical Characteristics – $R_{L}$ = 150 $\Omega$    |    | 13.3 Related Links                                  | 32                 |

|   | 7.7 Electrical Characteristics – $R_L = 1 \text{ k}\Omega$ |    | 13.4 Receiving Notification of Documentation Update | es <mark>32</mark> |

|   | 7.8 Typical Characteristics                                |    | 13.5 Community Resources                            | 32                 |

| 8 | Parameter Measurement Information                          |    | 13.6 Trademarks                                     | 33                 |

| 9 | Detailed Description                                       |    | 13.7 Electrostatic Discharge Caution                | <mark>33</mark>    |

| 9 | 9.1 Overview                                               |    | 13.8 Glossary                                       | <mark>33</mark>    |

|   | 9.2 Functional Block Diagrams                              | 14 | Mechanical, Packaging, and Orderable Information    | 33                 |

|   |                                                            |    |                                                     |                    |

### 4 Revision History

Changes from Revision G (March 2010) to Revision H

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| •        | Changed units for input voltage noise parameter (+25°C specifications) from nA/√Hz to nV√Hz                                                                                                                                                                                         | <b>7</b> |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| CI       | hanges from Revision F (September 2008) to Revision G                                                                                                                                                                                                                               | Page     |

| <u>•</u> | Moved the information in the Related Devices table to the Development Support section                                                                                                                                                                                               | 32       |

| •        | Removed the graphs in the General PowerPAD™ Design Considerations section                                                                                                                                                                                                           | 29       |

| •        | Removed the Dissipation Ratings table                                                                                                                                                                                                                                               | 9        |

| •        | Changed Thermal Information tables                                                                                                                                                                                                                                                  | 6        |

| •        | Deleted Lead temperature row for JG package and case temperature row for FK package from <i>Absolute Maximum Ratings</i>                                                                                                                                                            | 5        |

| •        | Removed the obselete Ceramic DIP (JG) and Chip Carrier (FK) packages from the data sheet                                                                                                                                                                                            | 3        |

| •        | Removed obselete JG and FK packages                                                                                                                                                                                                                                                 | 1        |

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1        |

Deleted bullet point for Stable in Gain of 2 (-1) or greater

Editorial changes to paragraph format

Submit Documentation Feedback

Changes from Revision E (June 2007) to Revision F

Copyright © 1999–2016, Texas Instruments Incorporated

# **Device Comparison Table**

Table 1. Available Options<sup>(1)</sup>

|                |                       | ı                          |                                                  |        |                   |  |

|----------------|-----------------------|----------------------------|--------------------------------------------------|--------|-------------------|--|

| T <sub>A</sub> | NUMBER OF<br>CHANNELS | PLASTIC SMALL              | PLASTIC MSOP <sup>(2)</sup> (DGN) <sup>(3)</sup> |        | EVALUATION MODULE |  |

|                | OHAMILEO              | OUTLINE <sup>(2)</sup> (D) | DEVICE                                           | SYMBOL | MODULE            |  |

| 0°C to 70°C    | 1                     | THS4031CD                  | THS4031CDGN                                      | TIACM  | THS4031EVM        |  |

| 0 0 10 70 0    | 2                     | THS4032CD                  | THS4032CDGN                                      | TIABD  | THS4032EVM        |  |

| 40°C to 95°C   | 1                     | THS4031ID                  | THS4031IDGN                                      | TIACN  | _                 |  |

| –40°C to 85°C  | 2                     | THS4032ID                  | THS4032IDGN                                      | TIABG  | _                 |  |

| -55°C to 125°C | 1                     | _                          | _                                                | _      | _                 |  |

For the most current package and ordering information, see Mechanical, Packaging, and Orderable Information, or see the TI web site at www.ti.com.

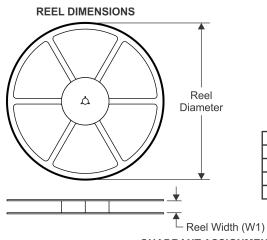

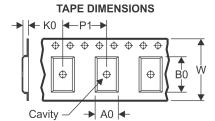

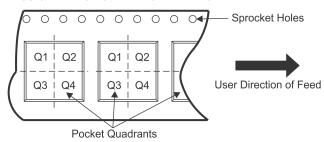

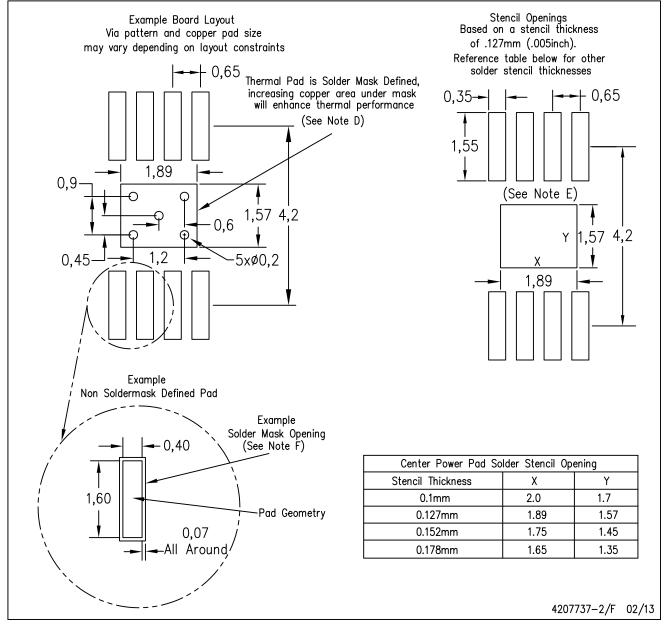

The D and DGN packages are available taped and reeled. Add an R suffix to the device type (that is, THS4031CDGNR). The PowerPAD<sup>TM</sup> on the underside of the DGN package is electrically isolated from all other pins and active circuitry. Connection to the PCB ground plane is recommended, although not required, as this copper plane is typically the largest copper plane on the PCB.

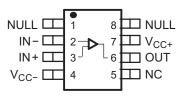

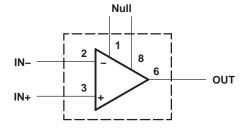

# 6 Pin Configuration and Functions

#### THS4031 D or DGN Package 8-Pin SOIC or HVSSOP Top View

NC - No internal connection

#### Pin Functions - THS4031

| PIN               |      | 1/0 | DESCRIPTION           |

|-------------------|------|-----|-----------------------|

| NAME              | NO.  | I/O | DESCRIPTION           |

| NULL              | 1, 8 | I   | Voltage offset adjust |

| IN-               | 2    | I   | Inverting input       |

| IN+               | 3    | I   | Noninverting input    |

| V <sub>CC</sub> - | 4    | POW | Negative power supply |

| NC                | 5    | _   | No connection         |

| OUT               | 6    | 0   | Output of amplifier   |

| V <sub>CC+</sub>  | 7    | POW | positive power supply |

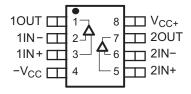

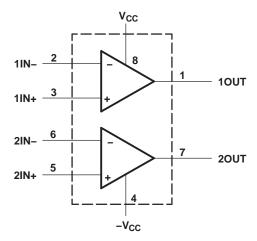

#### 7THS4032 D or DGN Package 8-Pin SOIC or HVSSOP Top View

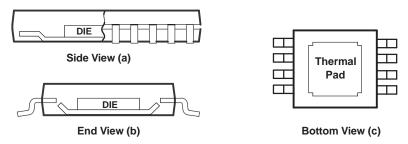

Cross-Section View Showing PowerPAD™ Option (DGN)

### Pin Functions - THS4032

| F                | PIN | 1/0 | DESCRIPTION                  |  |  |

|------------------|-----|-----|------------------------------|--|--|

| NAME             | NO. | 1/0 | DESCRIPTION                  |  |  |

| 1OUT             | 1   | 0   | Channel 1 output             |  |  |

| 1IN-             | 2   | I   | annel 1 inverting input      |  |  |

| 1IN+             | 3   | I   | annel 1 noninverting input   |  |  |

| -V <sub>CC</sub> | 4   | POW | Negative power supply        |  |  |

| 2IN+             | 5   | I   | Channel 2 noninverting input |  |  |

| 2IN-             | 6   | I   | Channel 2 inverting input    |  |  |

| 2OUT             | 7   | 0   | Channel 2 output             |  |  |

| V <sub>CC+</sub> | 8   | POW | Positive power supply        |  |  |

Product Folder Links: THS4031 THS4032

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). (1)

|                  |                                            |                                                | MIN         | MAX                         | UNIT |

|------------------|--------------------------------------------|------------------------------------------------|-------------|-----------------------------|------|

| V <sub>CC</sub>  | Supply voltage, \                          | / <sub>CC+</sub> to V <sub>CC-</sub>           |             | 33                          | V    |

| VI               | Input voltage                              |                                                |             | ±V <sub>CC</sub>            |      |

| Io               | Output current                             |                                                |             | 150                         | mA   |

| V <sub>IO</sub>  | Differential input                         | voltage                                        |             | ±4                          | V    |

|                  | Continuous total power dissipation         |                                                |             | werPAD™ Design<br>lerations |      |

|                  |                                            | C-suffix                                       | 0           | 70                          |      |

| T <sub>A</sub>   | Operating free-<br>air temperature         | I-suffix                                       | -40         | 85                          | °C   |

|                  | an temperature                             | M-suffix                                       | -55         | 125                         |      |

| TJ               | Maximum junctio                            | n temperature, (any condition)                 |             | 150                         | °C   |

|                  | Maximum junctio reliability <sup>(2)</sup> | n temperature, continuous operation, long term |             | 130                         | °C   |

|                  | Lead temperature                           | e 1,6 mm (1/16 inch) from case for 10 seconds  |             | 300                         | °C   |

| T <sub>stg</sub> | Storage tempera                            | ture                                           | <b>–</b> 65 | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|        |               |                                                                                | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------|-------|------|

| V/ECD) | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

|        | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

|                |                                |               | MIN         | NOM | MAX | UNIT |

|----------------|--------------------------------|---------------|-------------|-----|-----|------|

| \/ and \/      | Supply voltage                 | Dual supply   | ±4.5        | ±15 | ±16 | V    |

| vCC+ and vCC-  |                                | Single supply | 9           | 30  | 32  | V    |

|                | Operating free-air temperature | C-suffix      | 0           | 25  | 70  |      |

| T <sub>A</sub> |                                | I-suffix      | -40         | 25  | 85  | °C   |

|                |                                | M-suffix      | <b>–</b> 55 | 25  | 125 |      |

<sup>(2)</sup> The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device. Does not apply to the JG package or FK package.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information – THS4031

|                      |                                              | TH       | THS4031      |      |  |

|----------------------|----------------------------------------------|----------|--------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGN (HVSSOP) | UNIT |  |

|                      |                                              | 8 PINS   | 8 PINS       |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 128.9    | 61.6         | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 80.9     | 53.9         | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 69.2     | 43.2         | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 23.7     | 3.8          | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 68.8     | 42.9         | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a      | 14.5         | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

#### 7.5 Thermal Information – THS4032

|                      |                                              | TH       |              |      |

|----------------------|----------------------------------------------|----------|--------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGN (HVSSOP) | UNIT |

|                      |                                              | 8 PINS   | 8 PINS       |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 121.2    | 56.5         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 72.8     | 48.4         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 61.4     | 37.7         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 18.2     | 2.5          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 61       | 37.5         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a      | 9.9          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# 7.6 Electrical Characteristics – $R_L$ = 150 $\Omega$

At  $T_A$  = 25°C,  $V_{CC}$  = ±15 V, and  $R_L$  = 150  $\Omega$  for the THS403xC, THS403xI (unless otherwise noted).

|                | PARAMETER                           |                              | TEST CONDITIONS (1)         | '                 | MIN | TYP | MAX | UNIT    |  |

|----------------|-------------------------------------|------------------------------|-----------------------------|-------------------|-----|-----|-----|---------|--|

| DYNA           | MIC PERFORMANCE                     | •                            |                             |                   |     |     | ٠   |         |  |

|                | Small-signal bandwidth (–3          | $V_{CC} = \pm 15 \text{ V}$  |                             | Gain = -1 or 2    |     | 100 |     | N.41.1- |  |

| BW             | dB)                                 | $V_{CC} = \pm 5 \text{ V}$   |                             | Gaiii = -1 01 2   |     | 90  |     | MHz     |  |

|                | Bandwidth for 0.1-dB                | $V_{CC} = \pm 15 \text{ V}$  |                             | Gain = -1 or 2    |     | 50  |     | MHz     |  |

|                | flatness                            | $V_{CC} = \pm 5 \text{ V}$   |                             | Gaiii = -1 01 2   |     | 45  |     | IVI⊓Z   |  |

|                | Full power bandwidth <sup>(2)</sup> | $V_{O(pp)} = 20 V,$          | $V_{CC} = \pm 15 \text{ V}$ | D 4160            |     | 2.3 |     | NAL I-  |  |

|                |                                     | $V_{O(pp)} = 5 V$ ,          | $V_{CC} = \pm 5 \text{ V}$  | $R_L = 1 k\Omega$ |     | 7.2 |     | MHz     |  |

| SR             | Slew rate <sup>(3)</sup>            | $V_{CC} = \pm 15 \text{ V},$ | 20-V step                   | Gain = -1         |     | 100 |     | V/μs    |  |

| SK             | Siew rate 7                         | $V_{CC} = \pm 5 V$ ,         | 5-V step                    | Gairi = -1        |     | 80  |     |         |  |

|                | Settling time to 0.1%               | $V_{CC} = \pm 15 V$ ,        | 5-V step                    | Gain = -1         |     | 60  |     |         |  |

|                | Settling time to 0.1%               | $V_{CC} = \pm 5 V$ ,         | 2.5-V step                  | Gairr = -1        |     | 45  |     | ns      |  |

| t <sub>S</sub> | Cattling time to 0.040/             | $V_{CC} = \pm 15 \text{ V},$ | 5-V step                    | Gain = -1         |     | 90  |     |         |  |

|                | Settling time to 0.01%              | $V_{CC} = \pm 5 \text{ V},$  | 2.5-V step                  | Gain = -1         |     | 80  |     | ns      |  |

- (1) Full range = 0°C to 70°C for THS403xC and −40°C to 85°C for THS403xI suffix.

(2) Full power bandwidth = slew rate / [√2 πV<sub>OC(Peak)</sub>].

(3) Slew rate is measured from an output level range of 25% to 75%.

Submit Documentation Feedback

Copyright © 1999-2016, Texas Instruments Incorporated

# Electrical Characteristics – $R_L = 150 \Omega$ (continued)

At  $T_A$  = 25°C,  $V_{CC}$  = ±15 V, and  $R_L$  = 150  $\Omega$  for the THS403xC, THS403xI (unless otherwise noted).

|                 | PARAMETER                          |                    | TEST                                                   | CONDITIONS (1)            |                             | MIN    | TYP   | MAX | UNIT               |  |

|-----------------|------------------------------------|--------------------|--------------------------------------------------------|---------------------------|-----------------------------|--------|-------|-----|--------------------|--|

| NOISE           | DISTORTION PER                     | RFORMANC           | E                                                      |                           |                             |        |       |     |                    |  |

|                 |                                    |                    |                                                        |                           | R <sub>L</sub> = 150 Ω      |        | -81   |     |                    |  |

|                 | Total harmonic                     | THS4031            | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$       | $V_{O(pp)} = 2 V,$        | $R_L = 1 k\Omega$           |        | -96   |     |                    |  |

| THD             | distortion                         |                    | f = 1 MHz                                              | Gain = 2                  | R <sub>L</sub> = 150 Ω      |        | -72   |     | dBc                |  |

|                 |                                    | THS4032            |                                                        |                           | $R_L = 1 k\Omega$           |        | -90   |     |                    |  |

| V <sub>n</sub>  | Input voltage nois                 | se                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$       | f > 10 kHz                |                             |        | 1.6   |     | nV/√ <del>Hz</del> |  |

| I <sub>n</sub>  | Input current nois                 | е                  | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$       | f > 10 kHz                |                             |        | 1.2   |     | pA/√ <del>Hz</del> |  |

|                 | D''' '' '                          |                    |                                                        | V <sub>CC</sub> = ±15 V   |                             | 0.015% |       |     |                    |  |

|                 | Differential gain e                | error              | Gain = 2,                                              | NTSC and PAL,             | $V_{CC} = \pm 5 \text{ V}$  |        | 0.02% |     |                    |  |

|                 | D''' and a Callada and             |                    | 40 IRE modulation,                                     | ±100 IRE ramp             | V <sub>CC</sub> = ±15 V     |        | 0.025 |     | 0                  |  |

|                 | Differential phase                 | error              |                                                        |                           | $V_{CC} = \pm 5 \text{ V}$  |        | 0.03  |     | Ŭ                  |  |

|                 | Channel-to-chanr<br>(THS4032 only) | nel crosstalk      | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$       | f = 1 MHz                 |                             |        | -61   |     | dBc                |  |

| DC PE           | RFORMANCE                          |                    |                                                        |                           |                             |        |       |     |                    |  |

|                 | Onen leen gein                     |                    | $V_{CC} = \pm 15 \text{ V}, R_{L} = 1 \text{ k}\Omega$ |                           | $T_A = 25^{\circ}C$         | 93     | 98    |     |                    |  |

|                 |                                    |                    | VCC = ±13 V, KL = 1 KZ                                 | 2, V <sub>O</sub> = ±10 V | T <sub>A</sub> = full range | 92     |       |     | dB                 |  |

|                 | Open loop gain                     |                    | $V_{CC} = \pm 5 \text{ V}, R_1 = 1 \text{ k}\Omega,$   | Va = +25 V                | $T_A = 25^{\circ}C$         | 90     | 95    |     | uБ                 |  |

|                 |                                    |                    | VCC = ±3 V, IVL = 1 K22,                               | VO = ±2.5 V               | T <sub>A</sub> = full range | 89     |       |     |                    |  |

| Vos             | Input offset voltage               | 10                 | V <sub>CC</sub> = ±5 V or ±15 V                        |                           | $T_A = 25^{\circ}C$         |        | 0.5   | 2   | mV                 |  |

| vos             | input onset voitag                 | JC                 | ACC = 73 A QI 7.12 A                                   |                           | T <sub>A</sub> = full range |        |       | 3   | 111 V              |  |

| L.              | Input bias current                 |                    | V <sub>CC</sub> = ±5 V or ±15 V                        |                           | $T_A = 25^{\circ}C$         |        | 3     | 6   | μА                 |  |

| I <sub>IB</sub> | input bias current                 | •                  | ACC = 73 A OL 712 A                                    |                           | T <sub>A</sub> = full range |        |       | 8   | μΑ                 |  |

|                 | Input offset current               |                    | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$        |                           | $T_A = 25$ °C               |        | 30    | 250 | nA                 |  |

| los             | input onset curre                  | III.               | ACC = 73 A QI 712 A                                    |                           | T <sub>A</sub> = full range |        |       | 400 | IIA                |  |

|                 | Offset voltage dri                 | ft                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$        |                           | T <sub>A</sub> = full range |        | 2     |     | μV/°C              |  |

|                 | Input offset curre                 | nt drift           | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$        |                           | T <sub>A</sub> = full range |        | 0.2   |     | nA/°C              |  |

| INPUT           | CHARACTERISTI                      | CS                 |                                                        |                           |                             |        |       |     |                    |  |

| $V_{ICR}$       | Common-mode in                     | nput voltage       | $V_{CC} = \pm 15 \text{ V}$                            |                           | ±13.5                       | ±14    |       | V   |                    |  |

| VICR            | range                              |                    | $V_{CC} = \pm 5 \text{ V}$                             |                           |                             | ±3.8   | ±4    |     | V                  |  |

|                 |                                    |                    | $V_{CC} = \pm 15 \text{ V}, V_{ICR} = \pm 1$           | 2 \/                      | $T_A = 25^{\circ}C$         | 85     | 95    |     |                    |  |

| CMRR            | Common-mode re                     | ejection           | VCC - ±15 V, VICR - ±1                                 | Z V                       | T <sub>A</sub> = full range | 80     |       |     | dB                 |  |

| Civilata        | ratio                              |                    | $V_{CC} = \pm 5 \text{ V}, V_{ICR} = \pm 2.5$          | 5 \/                      | $T_A = 25^{\circ}C$         | 90     | 100   |     |                    |  |

|                 |                                    |                    | VCC = ±5 V, VICR = ±2.0                                |                           | T <sub>A</sub> = full range | 85     |       |     |                    |  |

| r <sub>i</sub>  | Input resistance                   |                    |                                                        |                           |                             |        | 2     |     | ΜΩ                 |  |

| Ci              | Input capacitance                  | )                  |                                                        |                           |                             |        | 1.5   |     | pF                 |  |

| OUTPL           | JT CHARACTERIS                     | STICS              |                                                        |                           |                             |        |       |     |                    |  |

|                 |                                    |                    | V <sub>CC</sub> = ±15 V                                |                           | $R_L = 1 k\Omega$           | ±13    | ±13.6 |     |                    |  |

| Vo              | Output voltage sv                  | vina               | $V_{CC} = \pm 5 \text{ V}$                             |                           | 1.7 - 1.7.22                | ±3.4   | ±3.8  |     | V                  |  |

| ٧O              | Output voltage SV                  | viily              | V <sub>CC</sub> = ±15 V                                |                           | $R_L = 150 \Omega$          | ±12    | ±12.9 |     |                    |  |

|                 |                                    |                    | $V_{CC} = \pm 5 \text{ V}$                             |                           | $R_L = 250 \Omega$          | ±3     | ±3.5  |     |                    |  |

| -<br> -         | Output current <sup>(4)</sup>      |                    | V <sub>CC</sub> = ±15 V                                |                           | R <sub>L</sub> = 20 Ω       | 60     | 90    |     | mA                 |  |

| lo              | Output current\                    |                    | $V_{CC} = \pm 5 \text{ V}$                             |                           | 11 = 20 12                  | 50     | 50 70 |     | ША                 |  |

| I <sub>SC</sub> | Short-circuit curre                | ent <sup>(4)</sup> | V <sub>CC</sub> = ±15 V                                |                           | 150                         |        | mA    |     |                    |  |

| Ro              | Output resistance                  | )                  | Open loop                                              |                           |                             |        | 13    | J   | Ω                  |  |

<sup>(4)</sup> Observe power dissipation ratings to keep the junction temperature below the absolute maximum rating when the output is heavily loaded or shorted. See the *Absolute Maximum Ratings* in this data sheet for more information.

# Electrical Characteristics – $R_L$ = 150 $\Omega$ (continued)

At  $T_A$  = 25°C,  $V_{CC}$  = ±15 V, and  $R_L$  = 150  $\Omega$  for the THS403xC, THS403xI (unless otherwise noted).

|                 | PARAMETER                    | ITIONS <sup>(1)</sup>                           | MIN                         | TYP | MAX   | UNIT |    |

|-----------------|------------------------------|-------------------------------------------------|-----------------------------|-----|-------|------|----|

| POWE            | R SUPPLY                     |                                                 |                             |     |       |      |    |

| V <sub>CC</sub> | Supply voltage operating     | Dual supply                                     | ±4.5                        |     | ±16.5 | V    |    |

|                 | range                        | Single supply                                   | 9                           |     | 33    |      |    |

|                 |                              | \/ .45\/                                        | T <sub>A</sub> = 25°C       |     | 8.5   | 10   |    |

|                 | Supply current (each         | $V_{CC} = \pm 15 \text{ V}$                     | T <sub>A</sub> = full range |     |       | 11   | A  |

| ICC             | amplifier)                   | V .5.V                                          | T <sub>A</sub> = 25°C       |     | 7.5   | 9    | mA |

|                 |                              | $V_{CC} = \pm 5 \text{ V}$                      | T <sub>A</sub> = full range |     |       | 10.5 |    |

| PSRR            | Dower aupply rejection ratio | //F. // or .15 //                               | T <sub>A</sub> = 25°C       | 85  | 95    |      | dB |

|                 | Power-supply rejection ratio | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ | T <sub>A</sub> = full range | 80  |       |      | ub |

# 7.7 Electrical Characteristics – $R_L = 1 k\Omega$

At  $T_A$  = full range,  $V_{CC}$  = ±15 V, and  $R_L$  = 1 k $\Omega$  for the THS403xC, THS403xI (unless otherwise noted).

|                | PARAMETER                           | TEST CONDITION                                                                                   | MIN                         | TYP                | MAX    | UNIT |                    |  |  |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------|--------------------|--------|------|--------------------|--|--|

| DYNA           | MIC PERFORMANCE                     |                                                                                                  |                             |                    |        | *    |                    |  |  |

|                | Unity gain bandwidth                | V <sub>CC</sub> = ±15 V, closed loop                                                             | $R_L = 1 k\Omega$           | 100 <sup>(2)</sup> | 120    |      | MHz                |  |  |

|                | Small-signal bandwidth              | V <sub>CC</sub> = ±15 V                                                                          | Caia 4 au 0                 |                    | 100    |      | N 41 1-            |  |  |

|                | (-3 dB)                             | $V_{CC} = \pm 5 \text{ V}$                                                                       | Gain = -1 or 2              |                    | 90     | MHz  |                    |  |  |

|                | Bandwidth for 0.1-dB flatness       | V <sub>CC</sub> = ±15 V                                                                          | Gain = -1 or 2              |                    | 50     | MHz  |                    |  |  |

| BW             | Dandwidth for 0.1-db flattless      | $V_{CC} = \pm 5 \text{ V}$                                                                       | Gairi = -1 or 2             |                    | 45     |      |                    |  |  |

|                | Full power bandwidth <sup>(3)</sup> | $V_{O(pp)} = 20 \text{ V},$<br>$V_{CC} = \pm 15 \text{ V}$                                       | D 110                       |                    | 2.3    |      | MHz                |  |  |

|                | Full power bandwidth                | $V_{O(pp)} = 5 \text{ V},$<br>$V_{CC} = \pm 5 \text{ V}$                                         | $R_L = 1 k\Omega$           |                    | 7.1    |      | IVI⊓∠              |  |  |

| SR             | Slew rate                           | V <sub>CC</sub> = ±15 V                                                                          | $R_L = 1 k\Omega$           | 80 <sup>(2)</sup>  | 100    |      | V/μs               |  |  |

| t <sub>S</sub> | Sottling time to 0.40/              | $V_{CC} = \pm 15 \text{ V},$<br>5-V step                                                         | Gain = −1                   |                    | 60     |      |                    |  |  |

|                | Settling time to 0.1%               | $V_{CC} = \pm 5 \text{ V},$<br>2.5-V step                                                        | Gain = -1                   |                    | 45     |      | ns                 |  |  |

|                | 0.411.                              | V <sub>CC</sub> = ±15 V,<br>5-V step                                                             | 0-1-                        |                    | 90     |      |                    |  |  |

|                | Settling time to 0.01%              | $V_{CC} = \pm 5 \text{ V},$<br>2.5-V step                                                        | Gain = -1                   |                    | 80     |      | ns                 |  |  |

| NOISE          | DISTORTION PERFORMANCE              |                                                                                                  |                             |                    |        |      |                    |  |  |

|                |                                     | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$                                                 | $R_L = 150 \Omega$          |                    | -81    |      |                    |  |  |

| THD            | Total harmonic distortion           | $f = 1 \text{ MHz}, \text{ Gain} = 2, \\ V_{O(pp)} = 2 \text{ V}, \\ T_A = 25^{\circ}\text{C}$   | $R_L = 1 k\Omega$           |                    | -96    |      | dBc                |  |  |

| V <sub>n</sub> | Input voltage noise                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$ $T_A = 25^{\circ}\text{C}$ $f > 10 \text{ kHz}$ | R <sub>L</sub> = 150 Ω      |                    | 1.6    |      | nV/√ <del>Hz</del> |  |  |

| In             | Input current noise                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V},$ $T_A = 25^{\circ}\text{C}$ $f > 10 \text{ kHz}$ | R <sub>L</sub> = 150 Ω      |                    | 1.2    |      | pA/√ <del>Hz</del> |  |  |

|                | Differential gain error             | Gain = 2, $V_{CC} = \pm 15$                                                                      |                             |                    | 0.015% |      |                    |  |  |

|                | Differential gain error             | 40 IRE modulation,  T <sub>A</sub> = 25°C                                                        | $V_{CC} = \pm 5 \text{ V}$  |                    | 0.02%  |      |                    |  |  |

|                |                                     | NTSC and PAL,                                                                                    | $V_{CC} = \pm 15 \text{ V}$ |                    | 0.025  |      |                    |  |  |

|                | Differential phase error            | $\pm 100$ IRE ramp,<br>R <sub>1</sub> = 150 Ω                                                    | $V_{CC} = \pm 5 \text{ V}$  |                    | 0.03   |      | 0                  |  |  |

Product Folder Links: THS4031 THS4032

<sup>(1)</sup> Full range = 0°C to 70°C for THS403xC and -40°C to 85°C for THS403xI suffix.

This parameter is not tested.

Full power bandwidth = slew rate /  $[\sqrt{2} \pi V_{OC(Peak)}]$ . (3)

# Electrical Characteristics – $R_L = 1 k\Omega$ (continued)

At  $T_A$  = full range,  $V_{CC}$  = ±15 V, and  $R_L$  = 1 k $\Omega$  for the THS403xC, THS403xI (unless otherwise noted).

|                                                  | PARAMETER                            | TEST CONDITIONS <sup>(1)</sup>                                               | MIN                         | TYP   | MAX   | UNIT  |       |  |

|--------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|--|

| DC PE                                            | RFORMANCE                            |                                                                              |                             |       |       |       |       |  |

|                                                  |                                      | V 45 V B 410 V 40 V                                                          | T <sub>A</sub> = 25°C       | 93    | 98    |       |       |  |

|                                                  |                                      | $V_{CC} = \pm 15 \text{ V}, R_L = 1 \text{ k}\Omega, V_O = \pm 10 \text{ V}$ | T <sub>A</sub> = full range | 92    |       |       |       |  |

|                                                  | Open loop gain                       |                                                                              | T <sub>A</sub> = 25°C       | 92    | 95    |       | dB    |  |

|                                                  |                                      | $V_{CC} = \pm 5 \text{ V}, R_L = 1 \text{ k}\Omega, V_O = \pm 2.5 \text{ V}$ | T <sub>A</sub> = full range | 91    |       |       |       |  |

|                                                  |                                      | .,                                                                           | T <sub>A</sub> = 25°C       |       | 0.5   | 2     | .,    |  |

| Vos                                              | Input offset voltage                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                              | T <sub>A</sub> = full range |       |       | 3     | mV    |  |

|                                                  |                                      |                                                                              | T <sub>A</sub> = 25°C       |       | 3     | 6     |       |  |

| I <sub>IB</sub>                                  | Input bias current                   | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                              | T <sub>A</sub> = full range |       |       | 8     | μΑ    |  |

|                                                  |                                      | .,                                                                           | T <sub>A</sub> = 25°C       |       | 30    | 250   |       |  |

| los                                              | Input offset current                 | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                              | T <sub>A</sub> = full range |       |       | 400   | nA    |  |

|                                                  | Offset voltage drift                 | V <sub>CC</sub> = ±5 V or ±15 V                                              | T <sub>A</sub> = full range |       | 2     |       | μV/°C |  |

|                                                  | Input offset current drift           | V <sub>CC</sub> = ±5 V or ±15 V                                              | T <sub>A</sub> = full range |       | 0.2   |       | nA/°C |  |

| INPUT                                            | CHARACTERISTICS                      |                                                                              | -                           |       |       |       |       |  |

| V <sub>ICR</sub> Common-mode input voltage range |                                      | V <sub>CC</sub> = ±15 V                                                      |                             | ±13.5 | ±14.3 |       |       |  |

|                                                  |                                      | V <sub>CC</sub> = ±5 V                                                       |                             | ±3.8  | ±4.3  |       | V     |  |

|                                                  |                                      |                                                                              | T <sub>A</sub> = 25°C       | 85    | 95    |       |       |  |

|                                                  |                                      | $V_{CC} = \pm 15 \text{ V}, V_{ICR} = \pm 12 \text{ V}$                      | T <sub>A</sub> = full range | 80    |       |       |       |  |

| CMRR                                             | Common-mode rejection ratio          |                                                                              | T <sub>A</sub> = 25°C       | 90    | 100   |       | dB    |  |

|                                                  |                                      | $V_{CC} = \pm 5 \text{ V}, V_{ICR} = \pm 2.5 \text{ V}$                      | T <sub>A</sub> = full range | 85    |       |       |       |  |

| r <sub>i</sub>                                   | Input resistance                     |                                                                              |                             |       | 2     |       | МΩ    |  |

| C <sub>i</sub>                                   | Input capacitance                    |                                                                              |                             |       | 1.5   |       | pF    |  |

| OUTPL                                            | JT CHARACTERISTICS                   |                                                                              |                             |       |       |       |       |  |

|                                                  |                                      | V <sub>CC</sub> = ±15 V                                                      |                             | ±13   | ±13.6 |       |       |  |

|                                                  |                                      | V <sub>CC</sub> = ±5 V                                                       | $R_L = 1 k\Omega$           | ±3.4  | ±3.8  |       |       |  |

| Vo                                               | Output voltage swing                 | V <sub>CC</sub> = ±15 V                                                      | R <sub>L</sub> = 150 Ω      | ±12   | ±12.9 |       | V     |  |

|                                                  |                                      | V <sub>CC</sub> = ±5 V                                                       | R <sub>L</sub> = 250 Ω      | ±3    | ±3.5  |       |       |  |

|                                                  | - (4)                                | V <sub>CC</sub> = ±15 V                                                      |                             | 60    | 90    |       |       |  |

| lo                                               | Output current <sup>(4)</sup>        | V <sub>CC</sub> = ±5 V                                                       | $R_L = 20 \Omega$           | 50    | 70    |       | mA    |  |

| I <sub>SC</sub>                                  | Short-circuit current <sup>(4)</sup> | V <sub>CC</sub> = ±15 V                                                      |                             |       | 150   |       | mA    |  |

| R <sub>O</sub>                                   | Output resistance                    | Open loop                                                                    |                             |       | 13    |       | Ω     |  |

|                                                  | R SUPPLY                             |                                                                              |                             |       |       |       |       |  |

|                                                  |                                      | Dual supply                                                                  |                             | ±4.5  |       | ±16.5 |       |  |

| $V_{CC}$                                         | Supply voltage operating range       | Single supply                                                                |                             | 9     |       | 33    | V     |  |

|                                                  |                                      |                                                                              | T <sub>A</sub> = 25°C       |       | 8.5   | 10    |       |  |

|                                                  |                                      | $V_{CC} = \pm 15 \text{ V}$                                                  | T <sub>A</sub> = full range |       |       | 11    |       |  |

| I <sub>CC</sub>                                  | Supply current (each amplifier)      |                                                                              | T <sub>A</sub> = 25°C       |       | 7.5   | 9     | mA    |  |

|                                                  |                                      | $V_{CC} = \pm 5 \text{ V}$                                                   | T <sub>A</sub> = full range |       |       | 10    |       |  |

|                                                  |                                      |                                                                              | T <sub>A</sub> = 25°C       | 85    | 95    | -     |       |  |

| PSRR                                             | Power-supply rejection ratio         | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                              | T <sub>A</sub> = full range | 80    |       |       | dB    |  |

|                                                  |                                      |                                                                              | r <sub>A</sub> = ruii range | 80    |       |       |       |  |

<sup>(4)</sup> Observe power dissipation ratings to keep the junction temperature below the absolute maximum rating when the output is heavily loaded or shorted. See the *Absolute Maximum Ratings* in this data sheet for more information.

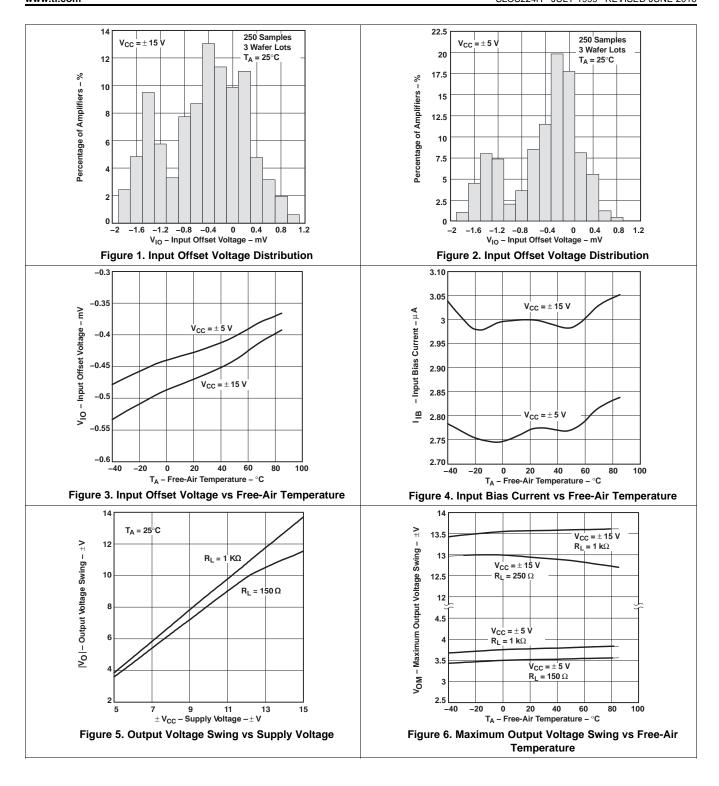

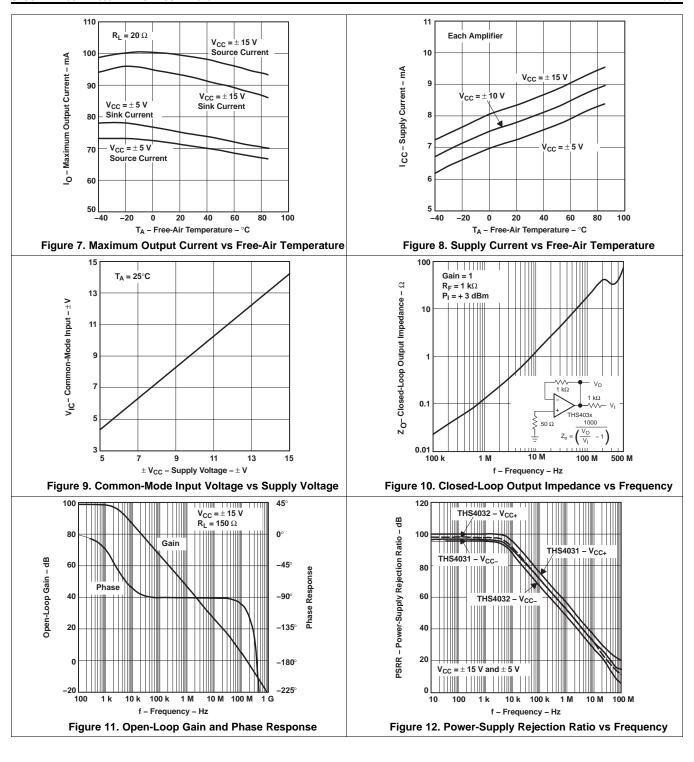

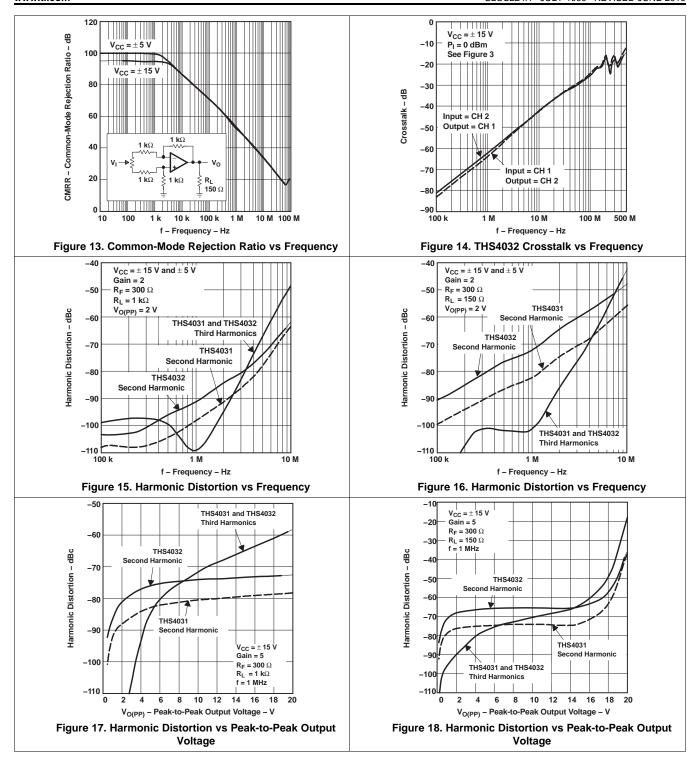

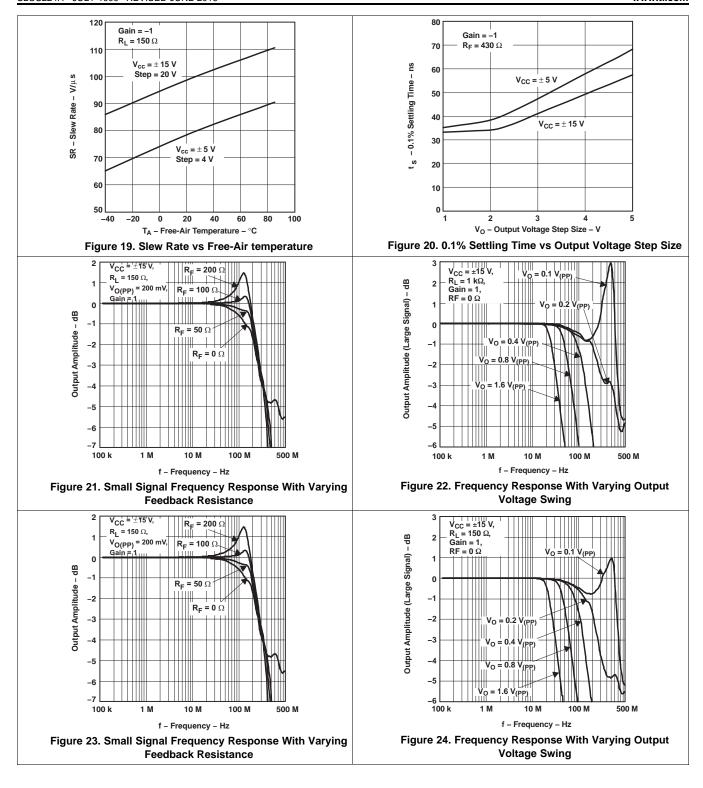

# 7.8 Typical Characteristics

# Table 2. Table of Graphs

|                                                                  |                                                                         | FIGURE                  |

|------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------|

| Input offset voltage distribution                                |                                                                         | Figure 1,<br>Figure 2   |

| Input offset voltage                                             | vs Free-air temperature                                                 | Figure 3                |

| Input bias current                                               | vs Free-air temperature                                                 | Figure 4                |

| Output voltage swing                                             | vs Supply voltage                                                       | Figure 5                |

| Maximum output voltage swing                                     | vs Free-air temperature                                                 | Figure 6                |

| Maximum output current                                           | vs Free-air temperature                                                 | Figure 7                |

| Supply current                                                   | vs Free-air temperature                                                 | Figure 8                |

| Common-mode input voltage                                        | vs Supply voltage                                                       | Figure 9                |

| Closed-loop output impedance                                     | vs Frequency                                                            | Figure 10               |

| Open-loop gain and phase response                                | vs Frequency                                                            | Figure 11               |

| Power-supply rejection ratio                                     | vs Frequency                                                            | Figure 12               |

| Common-mode rejection ratio                                      | vs Frequency                                                            | Figure 13               |

| Crosstalk                                                        | vs Frequency                                                            | Figure 14               |

| Harmonic distortion                                              | vs Frequency                                                            | Figure 15,<br>Figure 16 |

| Harmonic distortion                                              | vs Peak-to-peak output voltage                                          | Figure 17,<br>Figure 18 |

| Slew rate                                                        | vs Free-air temperature                                                 | Figure 19               |

| 0.1% settling time                                               | vs Output voltage step size                                             | Figure 20               |

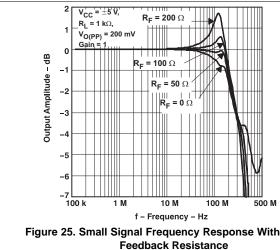

| Small signal frequency response with varying feedback resistance | Gain = 1, $V_{CC}$ = ±15 V, $R_L$ = 1 k $\Omega$                        | Figure 21               |

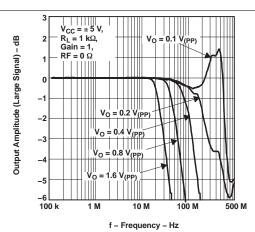

| Frequency response with varying output voltage swing             | Gain = 1, $V_{CC}$ = ±15 $V$ , $R_L$ = 1 $k\Omega$                      | Figure 22               |

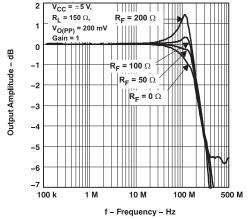

| Small signal frequency response with varying feedback resistance | Gain = 1, $V_{CC}$ = ±15 V, $R_L$ = 150 k $\Omega$                      | Figure 23               |

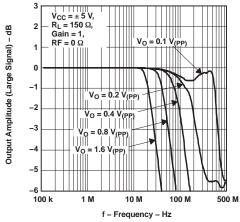

| Frequency response with varying output voltage swing             | Gain = 1, $V_{CC}$ = ±15 V, $R_L$ = 150 $k\Omega$                       | Figure 24               |

| Small signal frequency response with varying feedback resistance | Gain = 1, $V_{CC}$ = ±5 V, $R_L$ = 1 $k\Omega$                          | Figure 25               |

| Frequency response with varying output voltage swing             | Gain = 1, $V_{CC}$ = ±5 V, $R_L$ = 1 k $\Omega$                         | Figure 26               |

| Small signal frequency response with varying feedback resistance | Gain = 1, $V_{CC}$ = ±5 V, $R_L$ = 150 $k\Omega$                        | Figure 27               |

| Frequency response with varying output voltage swing             | Gain = 1, $V_{CC}$ = ±5 V, $R_L$ = 150 $k\Omega$                        | Figure 28               |

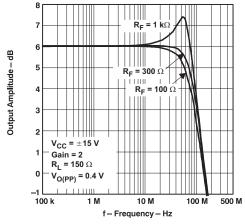

| Small signal frequency response with varying feedback resistance | Gain = 2, $V_{CC}$ = ±5 V, $R_L$ = 150 $k\Omega$                        | Figure 29               |

| Small signal frequency response with varying feedback resistance | Gain = 2, $V_{CC} = \pm 5 \text{ V}$ , $R_L = 150 \text{ k}\Omega$      | Figure 30               |

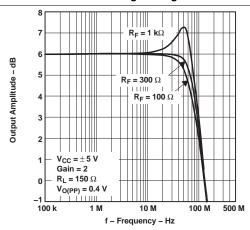

| Small signal frequency response with varying feedback resistance | Gain = $-1$ , $V_{CC} = \pm 15 \text{ V}$ , $R_L = 150 \text{ k}\Omega$ | Figure 31               |

| Frequency response with varying output voltage swing             | Gain = -1, $V_{CC}$ = ±5 V, $R_L$ = 150 kΩ                              | Figure 32               |

| Small signal frequency response                                  | Gain = 5, V <sub>CC</sub> = ±15 V, ±5 V                                 | Figure 33               |

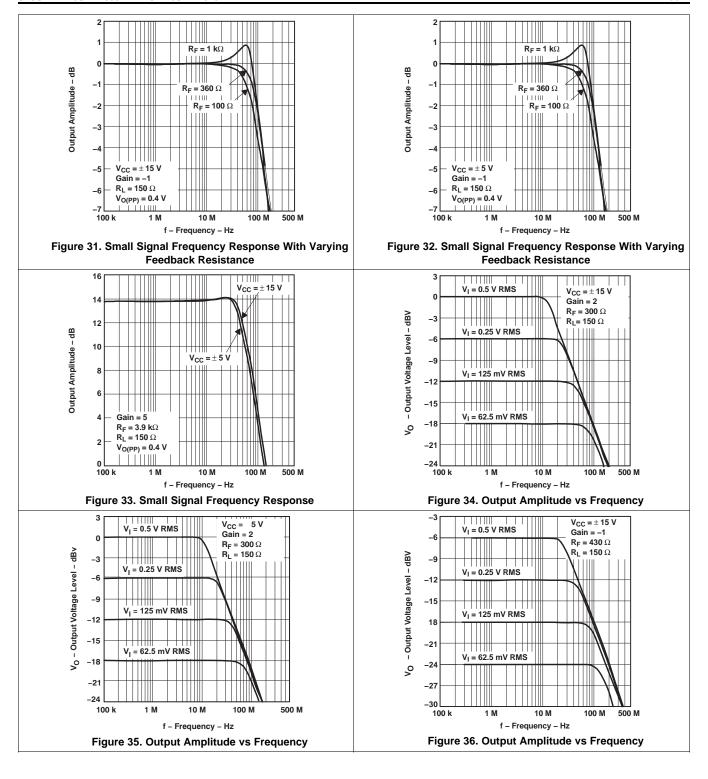

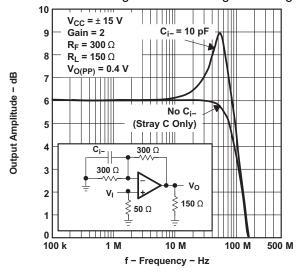

| Output amplitude                                                 | vs Frequency, Gain = 2, V <sub>S</sub> = ±15 V                          | Figure 34               |

| Output amplitude                                                 | vs Frequency, Gain = 2, V <sub>S</sub> = ±5 V                           | Figure 35               |

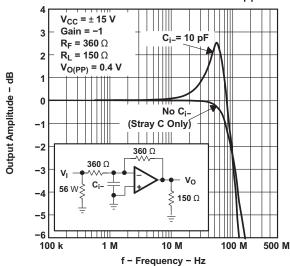

| Output amplitude                                                 | vs Frequency, Gain = $-1$ , $V_S = \pm 15 \text{ V}$                    | Figure 36               |

| Output amplitude                                                 | vs Frequency, Gain = $-1$ , $V_S = \pm 5$ V                             | Figure 37               |

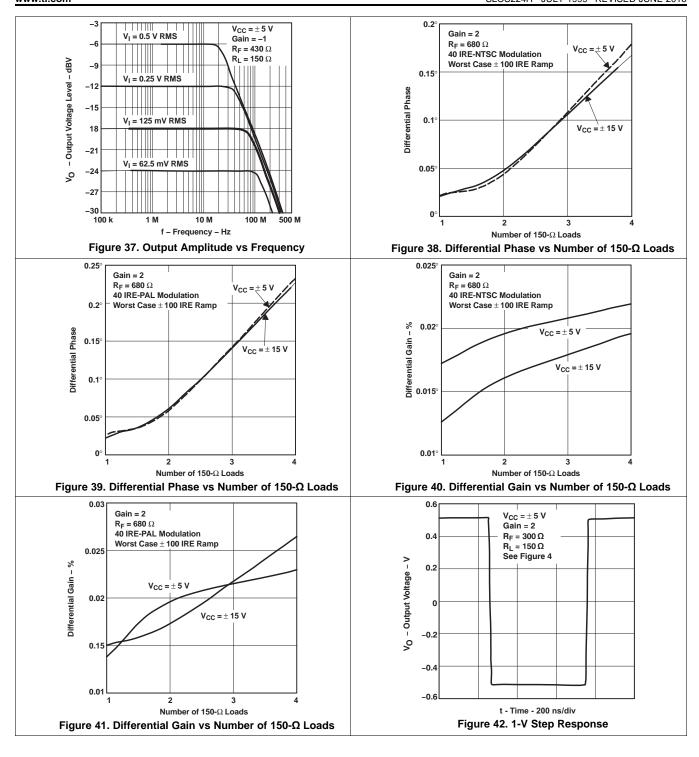

| Differential phase                                               | vs Number of 150-Ω loads                                                | Figure 38,<br>Figure 39 |

| Differential gain                                                | vs Number of 150-Ω loads                                                | Figure 40,<br>Figure 41 |

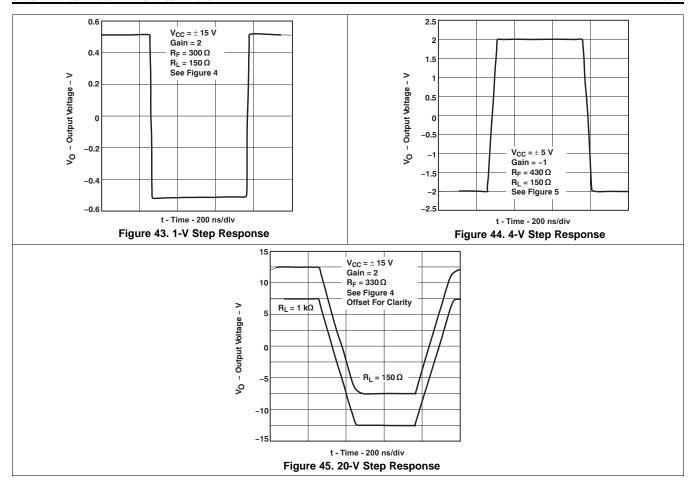

| 1-V step response                                                | vs Time                                                                 | Figure 42,<br>Figure 43 |

| 4-V step response                                                | vs Time                                                                 | Figure 44               |

| 20-V step response                                               | vs Time                                                                 | Figure 45               |

Submit Documentation Feedback

Copyright © 1999–2016, Texas Instruments Incorporated

Figure 25. Small Signal Frequency Response With Varying

Figure 26. Frequency Response With Varying Output **Voltage Swing**

Figure 27. Small Signal Frequency Response With Varying **Feedback Resistance**

Figure 28. Frequency Response With Varying Output **Voltage Swing**

Figure 29. Small Signal Frequency Response With Varying Feedback Resistance

Figure 30. Small Signal Frequency Response With Varying Feedback Resistance

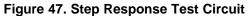

# 8 Parameter Measurement Information

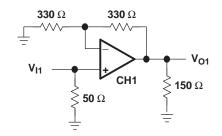

Figure 46. THS4032 Crosstalk Test Circuit

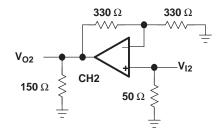

Figure 48. Step Response Test Circuit

### **Detailed Description**

#### 9.1 Overview

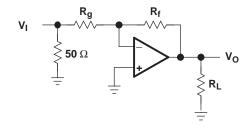

The THS403x is a high-speed operational amplifier configured in a voltage feedback architecture. It is built using a 30-V, dielectrically isolated, complementary bipolar process with NPN and PNP transistors possessing frs of several GHz. This results in an exceptionally high-performance amplifier that has wide bandwidth, high slew rate, fast settling time, and low distortion. Figure 49 shows a simplified schematic.

Figure 49. THS4031 Simplified Schematic

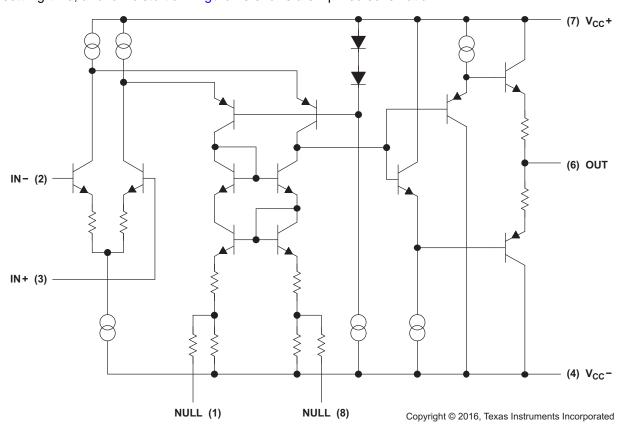

### 9.2 Functional Block Diagrams

Figure 50. THS4031 - Single Channel

## **Functional Block Diagrams (continued)**

Figure 51. THS4032 - Dual Channel

## 9.3 Feature Description

#### 9.3.1 Noise Calculations and Noise Figure

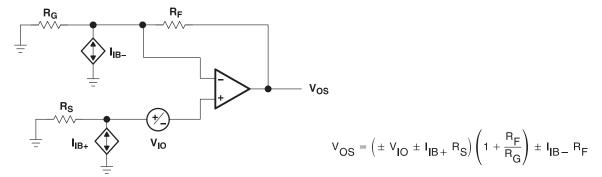

Noise can cause errors on very small signals. This is especially true when amplifying small signals. The noise model for the THS403x, shown in Figure 52, includes all of the noise sources as follows:

- $e_n = Amplifier internal voltage noise (nV/<math>\sqrt{Hz}$ )

- IN+ = Noninverting current noise (pA/ $\sqrt{\text{Hz}}$ )

- IN- = Inverting current noise (pA/√Hz)

- e<sub>Rx</sub> = Thermal voltage noise associated with each resistor (e<sub>Rx</sub> = 4 kTR<sub>x</sub>)

Figure 52. Noise Model

The total equivalent input noise density (e<sub>ni</sub>) is calculated by using Equation 1:

$$e_{ni} = \sqrt{(e_n)^2 = (IN + \times R_S)^2 = (IN - \times (R_F \parallel R_G))^2 + 4kTR_S + 4kT(R_F \parallel R_G)}$$

where

- $k = Boltzmann's constant = 1.380658 \times 10^{-23}$

- T = Temperature in degrees Kelvin (273+°C)

- $R_F \parallel R_G = Parallel resistance of R_F and R_G$  (1)

To get the equivalent output noise of the amplifier, just multiply the equivalent input noise density ( $e_{ni}$ ) by the overall amplifier gain ( $A_V$ ) in Equation 2.

Copyright © 1999–2016, Texas Instruments Incorporated

#### Feature Description (continued)

$$e_{no} = e_{ni}A_V = e_{ni}\left(1 + \frac{R_F}{R_G}\right)$$

(Noninverting Case)

As the previous equations show, to keep noise at a minimum, small-value resistors should be used. As the closed-loop gain is increased (by reducing R<sub>G</sub>), the input noise is reduced considerably because of the parallel resistance term. This leads to the general conclusion that the most dominant noise sources are the source resistor (R<sub>s</sub>) and the internal amplifier noise voltage (e<sub>n</sub>). Because noise is summed in a root-mean-squares method, noise sources smaller than 25% of the largest noise source can be effectively ignored. This advantage can greatly simplify the formula and make noise calculations much easier to calculate.

For more information on noise analysis, see the application note, *Noise Analysis for High-Speed Op Amps*.

## 9.3.2 Optimizing Frequency Response

Internal frequency compensation of the THS403x was selected to provide very wide bandwidth performance and still maintain a very low noise floor. To meet these performance requirements, the THS403x must have a minimum gain of 2 (-1). Because everything is referred to the noninverting terminal of an operational amplifier, the noise gain in a G = -1 configuration is the same as a G = 2 configuration.

One of the keys to maintaining a smooth frequency response, and hence, a stable pulse response, is to pay particular attention to the inverting terminal. Any stray capacitance at this node causes peaking in the frequency response (see Figure 53 and Figure 54). Two things can be done to help minimize this effect. The first is to simply remove any ground planes under the inverting terminal of the amplifier, including the trace that connects to this terminal. Additionally, the length of this trace should be minimized. The capacitance at this node causes a lag in the voltage being fed back due to the charging and discharging of the stray capacitance. If this lag becomes too long, the amplifier will not be able to correctly keep the noninverting terminal voltage at the same potential as the inverting terminal's voltage. Peaking and possible oscillations will then occur if this happens.

Figure 53. Output Amplitude vs Frequency

Figure 54. Output Amplitude vs Frequency

The second precaution to help maintain a smooth frequency response is to keep the feedback resistor (R<sub>f</sub>) and the gain resistor (R<sub>o</sub>) values fairly low. These two resistors are effectively in parallel when looking at the AC small-signal response. But, as can be seen in Figure 21 through Figure 32, a value too low starts to reduce the bandwidth of the amplifier. Table 3 shows some recommended feedback resistors to be used with the THS403x.

| Table 3. Recommended | Feedback Resistors |

|----------------------|--------------------|

|----------------------|--------------------|

| GAIN | $R_f$ for $V_{CC} = \pm 15 \text{ V}$ and $\pm 5 \text{ V}$ |

|------|-------------------------------------------------------------|

| 1    | 50 Ω                                                        |

| 2    | 300 Ω                                                       |

| -1   | 360 Ω                                                       |

| 5    | 3.3 kΩ (low stray-c PCB only)                               |

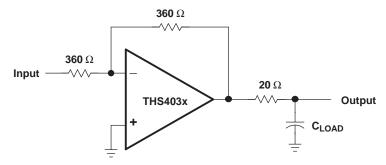

#### 9.3.3 Driving a Capacitive Load

Driving capacitive loads with high-performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS403x has been internally compensated to maximize its bandwidth and slew-rate performance. When the amplifier is compensated in this manner, capacitive loading directly on the output will decrease the phase margin of the device leading to high-frequency ringing or oscillations. Therefore, for capacitive loads of greater than 10 pF, TI recommends placing a resistor in series with the output of the amplifier, as shown in Figure 55. A minimum value of 20  $\Omega$  should work well for most applications. For example, in 75- $\Omega$  transmission systems, setting the series resistor value to 75  $\Omega$  both isolates any capacitance loading and provides the proper line impedance matching at the source end.

Figure 55. Driving a Capacitive Load

#### 9.3.4 Offset Voltage

The output offset voltage  $(V_{OO})$  is the sum of the input offset voltage  $(V_{IO})$  and both input bias currents  $(I_{IB})$  times the corresponding gains. The following schematic and formula shown in Figure 56 can be used to calculate the output offset voltage:

Figure 56. Output Offset Voltage Model

#### 9.3.5 General Configurations

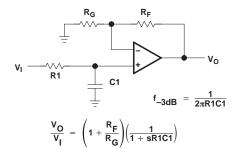

When receiving low-level signals, limiting the bandwidth of the incoming signals into the system is often required. The simplest way to accomplish this is to place an RC filter at the noninverting terminal of the amplifier (see Figure 57).

Figure 57. Single-Pole Low-Pass Filter

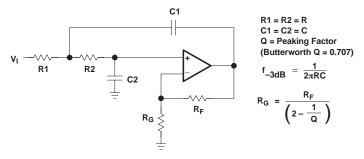

If even more attenuation is needed, a multiple-pole filter is required. The Sallen-Key filter can be used for this task. For best results, the amplifier should have a bandwidth that is 8 to 10 times the filter frequency bandwidth. Otherwise, phase shift of the amplifier can occur.

Figure 58. Two-Pole Low-Pass Sallen-Key Filter

#### 9.4 Device Functional Modes

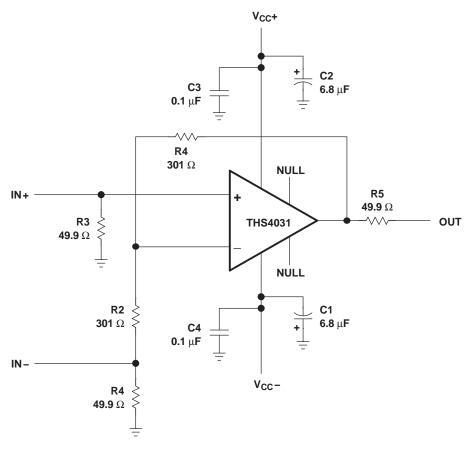

#### 9.4.1 Offset Nulling

The THS403x has very low input offset voltage for a high speed amplifier. However, if additional correction is required, the designer can make use of an offset nulling function provided on the THS4031. By placing a potentiometer between terminals 1 and 8 of the device and tying the wiper to the negative supply, the input offset can be adjusted. This is shown in Figure 59.

Figure 59. Offset Nulling Schematic

Submit Documentation Feedback

Copyright © 1999–2016, Texas Instruments Incorporated

# 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 10.1 Application Information

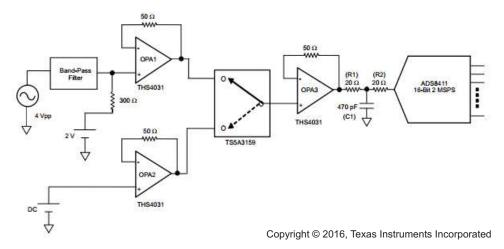

This application report is intended as a guide for using an analog multiplexer to multiplex several input signals to a high-performance driver amplifier which subsequently drives a single high-resolution, high-speed SAR analog-to-digital converter (ADC). The ADC and the multiplexer used were the ADS8411 and the TS5A3159 or TS5A3359, respectively. The operational amplifier used in this application was the THS4031.

### 10.2 Typical Application

As shown in Figure 60, the evaluation system consists of the ADC (ADS8411), a driving operational amplifier (THS4031), the multiplexer (TS5A3159), an AC source, a DC source, and two driving operational amplifiers (two THS4031s or a single THS4032) for the sources to make them a low-impedance source, a passive band-pass filter after the AC source to filter the source noise and distortion.

Figure 60. Evaluation Set-Up

#### 10.2.1 Design Requirements

Design a multiplexed digitizer system with the dynamic performance shown in Table 4:

**DEVICE SPEED INPUT FREQUENCY (kHz)** SNR (dB) THD (dB) CROSSTALK (dB) (MSPS) 20 > 84 2 < -90 < -110 2 100 > 84 < -90 < -96

**Table 4. Design Specifications**

### 10.2.2 Detailed Design Procedure

The ADS8411 is a 16-bit, 2-MSPS analog-to-digital converter (ADC) with a 4-V reference. The device includes a 16-bit capacitor-based SAR ADC with inherent sample and hold. It has a unipolar single-ended input. The device offers a 16-bit parallel interface.

The TS5A3159 is a single-pole, double-throw (SPDT) analog switch that is designed to operate from 1.65 V to 5.5 V. The device offers a low ON state resistance and an excellent ON resistance matching with the break-before-make feature to prevent signal distortion during the transfer of a signal from one channel to another. The device has an excellent total harmonic distortion (THD) performance and consumes low power. The TS5A3359 is a single-pole, triple-throw (SP3T) version of the same switch

#### 10.2.2.1 Selection of Multiplexer

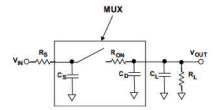

Figure 61 shows an equivalent circuit diagram of one of the channels of a multiplexer.  $C_S$  is the input capacitance of the channel,  $R_{ON}$  is the resistance of the channel when the channel is ON.  $C_L$  and  $R_L$  are the load capacitance and resistance, respectively.  $V_{IN}$  is the input voltage of the source;  $R_S$  is the source resistance of the source.  $V_{OUT}$  is the output voltage of the multiplexer.

Figure 61. Multiplexer Equivalent Circuit

To improve settling time, the values of  $R_S$ ,  $R_{ON}$ ,  $C_S$ ,  $C_D$ , and  $C_L$  need to be smaller, and the value of  $R_L$  should be large.

#### For TS5A3159:

- R<sub>S</sub> = 1 Ω

- $C_S = C_D = 84 pF$

#### Considerina

- R<sub>S</sub> = 50 Ω

- $C_1 = 5 pF$

- R<sub>L</sub> = 10 kΩ

- T<sub>RC</sub> (time constant) = 8.65 ns

For a 16-bit system, at least 18-bit settling is required. For 18-bit settling, the time required is  $(18 \times In2) \times T_{RC} = 108$  ns, which is better than 2 MSPS (500 ns). If the settling time is more than the conversion time of the ADC, the output of the multiplexer does not settle to the required accuracy which results in harmonic distortion.

One more important parameter of a multiplexer is the ON-state resistance variation with voltage. This also affects distortion because  $R_{ON}$  and  $R_{L}$  act like a resistor divider circuit and any variation of  $R_{ON}$  with voltage affects the output voltage.

#### 10.2.2.2 Signal Source

The input signal source should be a low-noise, low-distortion source with low source resistance. As discussed in the earlier section, RS should be low to improve settling time. If the source is not a low-noise and low-distortion source, a passive band-pass filter can be added to improve the signal quality as shown in Figure 60.

## 10.2.2.3 Driving Amplifier

The driving operational amplifier (OPA3 in Figure 60) in this application needs to have good slew rate and bandwidth along with low noise and distortion. The input of the operational amplifier may see a maximum step of 4 V because of MUX switching. So, even if the signal bandwidth is low, the driving amplifier needs to settle from 0 V to 4 V (or 4 V to 0 V) within one ADC sampling frame. When selecting the operational amplifier, one must ensure that it can settle from 0 V to 4 V (or from 4 V to 0 V) within the ADC sampling time (in this case 500 ns). The amplifier used for driving the ADC is the THS4031. The operational amplifiers (OPA1, OPA2 in Figure 60) used before the MUX is for signal conditioning. These operational amplifiers need to have low noise and distortion.

#### 10.2.2.4 Driving Amplifier Bandwidth Restriction

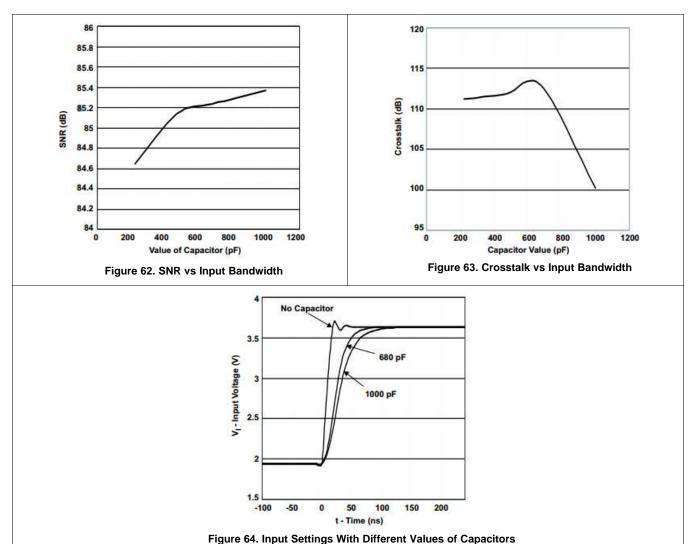

The restriction of bandwidth by an RC filter (after OPA3 in Figure 60) may result in better SNR and THD, but it makes the operational amplifier difficult to settle within the required accuracy. If the output does not settle properly, some residual charge of the previous channel remains in the next sampling. It appears as a crosstalk. If the throughput of the ADC is reduced, allowing the output of the operational amplifier to settle properly, the problem becomes smaller. Therefore, using a larger capacitor makes the operational-amplifier output settling slower. So, within the ADC sampling frame, the operational-amplifier output does not settle to its final level. The diagrams of Figure 62 and Figure 63 show SNR and crosstalk as a function of the filter capacitor.

The input settling behavior is shown in Figure 64 with three different bandwidths. The value of the capacitor is changed to change the bandwidth. As the bandwidth increases, the settling time improves (see Equation 3).

Bandwidth

$$\cong \frac{1}{2\pi R_1 C_1}$$

(3)

#### 10.2.3 Application Curves

iguio o il iliput dottiligo tritili billoront tuludo di dupuditor

# 11 Power Supply Recommendations

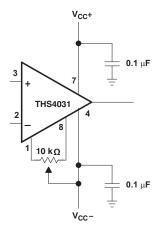

The THS4031 can operate off a single supply or with dual supplies as long as the input CM voltage range (CMIR) has the required headroom to either supply rail. Operating from a single supply can have numerous advantages. With the negative supply at ground, the DC errors due to the –PSRR term can be minimized. Supplies should be decoupled with low inductance, often ceramic, capacitors to ground less than 0.5 inches from the device pins. TI recommends using a ground plane. In most high speed devices, it is advisable to remove the ground plane close to device sensitive pins such as the inputs. An optional supply decoupling capacitor across the two power supplies (for split supply operation) improves second harmonic distortion performance.

## 12 Layout

#### 12.1 Layout Guidelines

In order to achieve the levels of high-frequency performance of the THS403x, it is essential that proper printed-circuit board (PCB) high-frequency design techniques be followed. A general set of guidelines is given below. In addition, a THS403x evaluation board is available to use as a guide for layout or for evaluating the device performance.

- Ground planes: TI highly recommends using a ground plane on the board to provide all components with a low inductive ground connection. However, in the areas of the amplifier inputs and output, the ground plane can be removed to minimize the stray capacitance.

- Proper power-supply decoupling: Use a 6.8-μF tantalum capacitor in parallel with a 0.1-μF ceramic capacitor on each supply terminal. It may be possible to share the tantalum among several amplifiers depending on the application, but a 0.1-μF ceramic capacitor should always be used on the supply terminal of every amplifier. In addition, the 0.1-μF capacitor should be placed as close as possible to the supply terminal. As this distance increases, the inductance in the connecting trace makes the capacitor less effective. The designer should strive for distances of less than 0.1 inch between the device power terminals and the ceramic capacitors.

- Sockets: TI does not recommend sockets for high-speed operational amplifiers. The additional lead inductance in the socket pins will often lead to stability problems. Surface-mount packages soldered directly to the printed-circuit board is the best implementation.

- Short trace runs/compact part placements: Optimum high-frequency performance is achieved when stray series inductance has been minimized. To realize this, the circuit layout should be made as compact as possible, thereby minimizing the length of all trace runs. Particular attention should be paid to the inverting input of the amplifier. Its length should be kept as short as possible. This will help to minimize stray capacitance at the input of the amplifier.