# **PCA2131**

# Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Rev. 1.0 — 26 July 2021

**Product data sheet**

# 1 General description

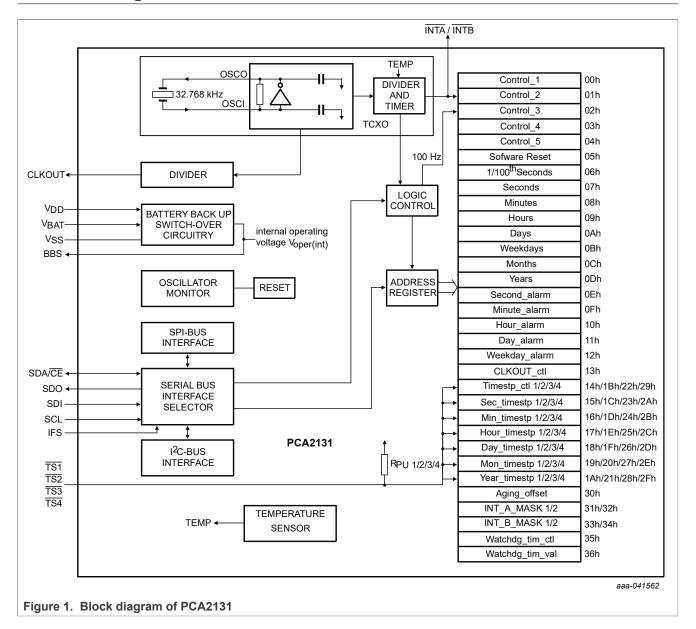

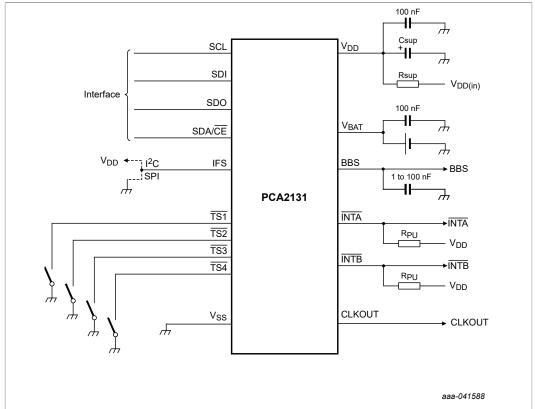

The PCA2131 is a CMOS Real Time Clock (RTC) and calendar with an integrated Temperature Compensated Crystal (Xtal) Oscillator (TCXO) and a 32.768 kHz quartz crystal optimized for very high accuracy and ultra low power consumption. The PCA2131 has a selectable I<sup>2</sup>C-bus or SPI-bus, a backup battery switch-over circuit, a programmable watchdog function, four timestamps function, and many other features.

For a selection of NXP Real-Time Clocks, see <u>Section 15.1</u>.

### 2 Features and benefits

- AEC-Q100 compliant version: PCA2131TF/Q900 for automotive applications

- Operating temperature range from -40 °C to +105 °C

- Temperature Compensated Crystal Oscillator (TCXO) with trimmed integrated capacitors

- Clock operational up to 125 °C

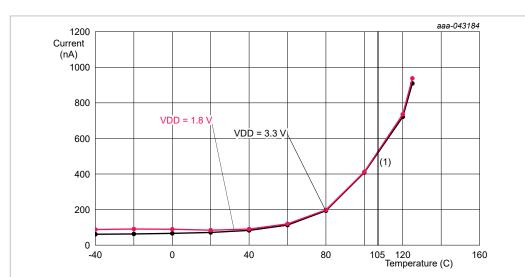

- Ultra low supply current: typical 106 nA at V<sub>DD</sub> = 3.3 V

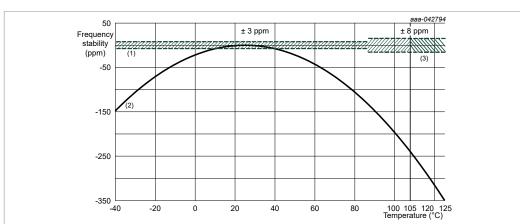

- Temperature compensated RTC, typical accuracy ±3 ppm from -40 °C to +85 °C;

±8 ppm from +85 °C to +105 °C

- Integration of a 32.768 kHz quartz crystal and oscillator in the same package

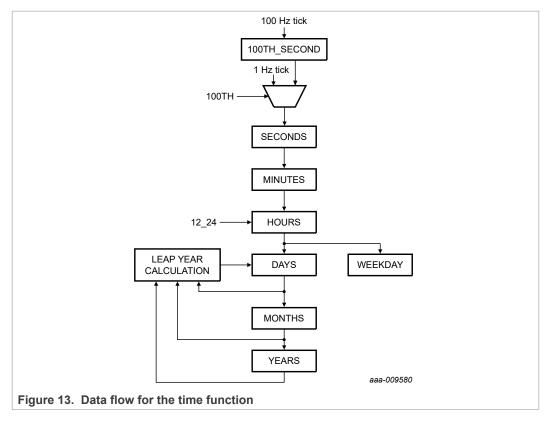

- Provides year, month, day, weekday, hours, minutes, seconds and 1/100 seconds

- · Provides leap year correction

- · Timestamp function

- with interrupt capability

- detection of four different events on four input pins (for example, for tamper detection)

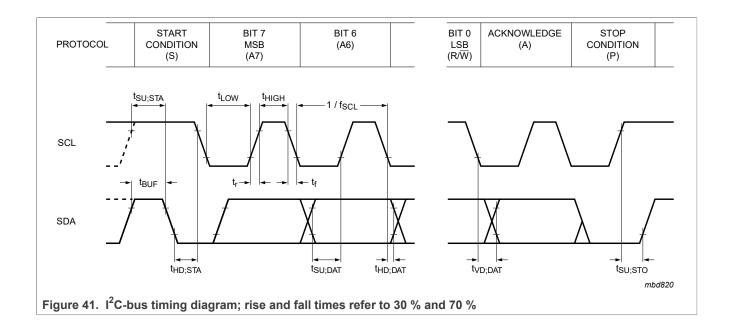

- 2-line bidirectional 400 kHz Fast-mode I<sup>2</sup>C-bus interface

- 4-line SPI-bus with separate data input and output (maximum speed 6.5 Mbit/s)

- · Battery backup input pin and switch-over circuitry

- Battery backed output voltage

- · Battery low detection function

- Power-On Reset (POR)

- Power-On Reset Override (PORO) function

- · Software reset function

- Two interrupt outputs (open-drain)

- Programmable 1 second or 1 minute interrupt

- Programmable watchdog timer with interrupt

- · Programmable alarm function with interrupt capability

- Programmable square output

- Clock operating voltage: 1.2 V to 5.5 V

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

# 3 Applications

- · Electronic metering for electricity, water, and gas

- · Precision timekeeping

- · Access to accurate time of the day

- GPS equipment to reduce time to first fix

- Applications that require an accurate process timing

- Products with long automated unattended operation time

# 4 Ordering information

Table 1. Ordering information

| Type number    | Topside<br>marking | Package |                                                                                                                                               |           |  |  |  |  |

|----------------|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

|                |                    | Name    | Description                                                                                                                                   | Version   |  |  |  |  |

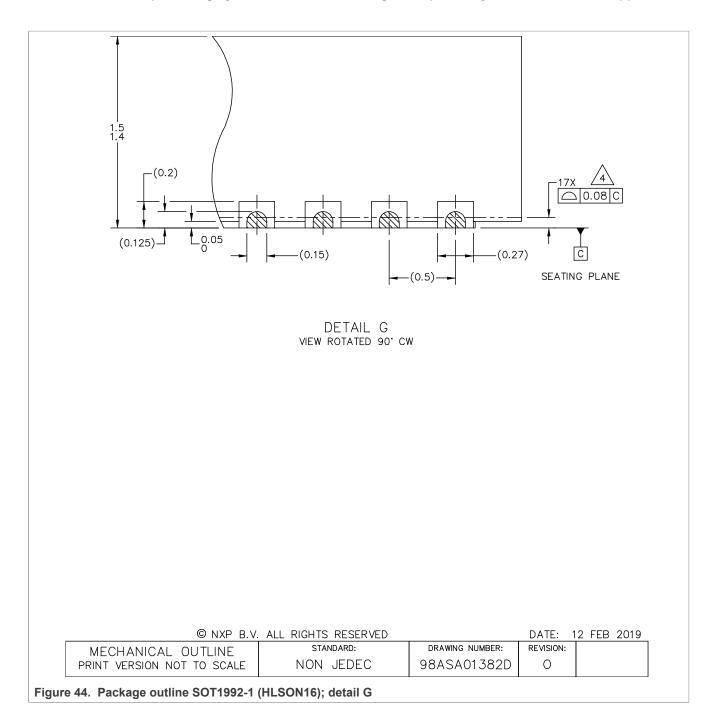

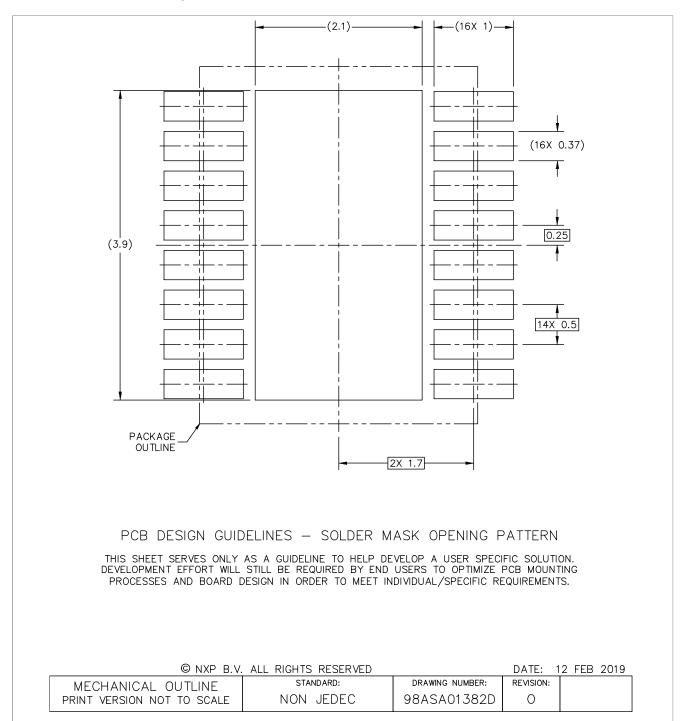

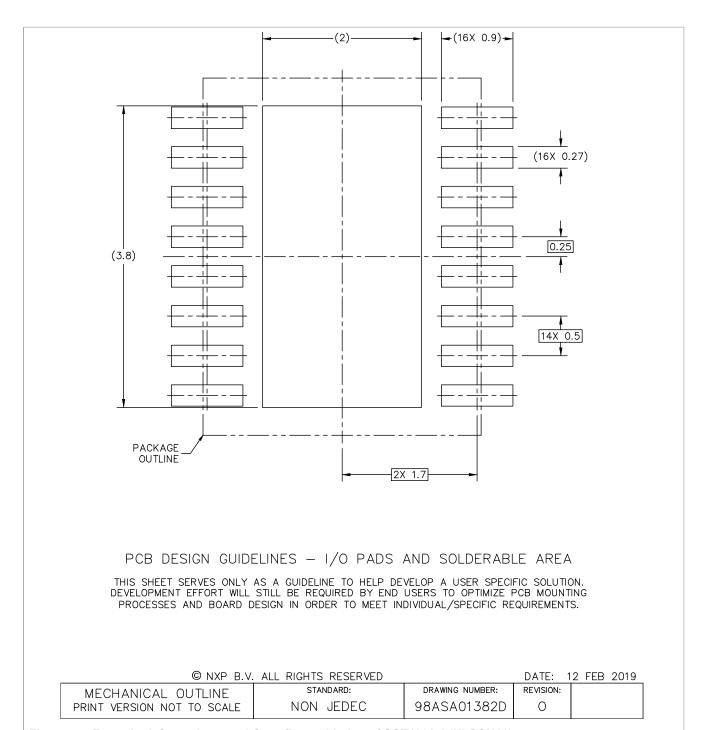

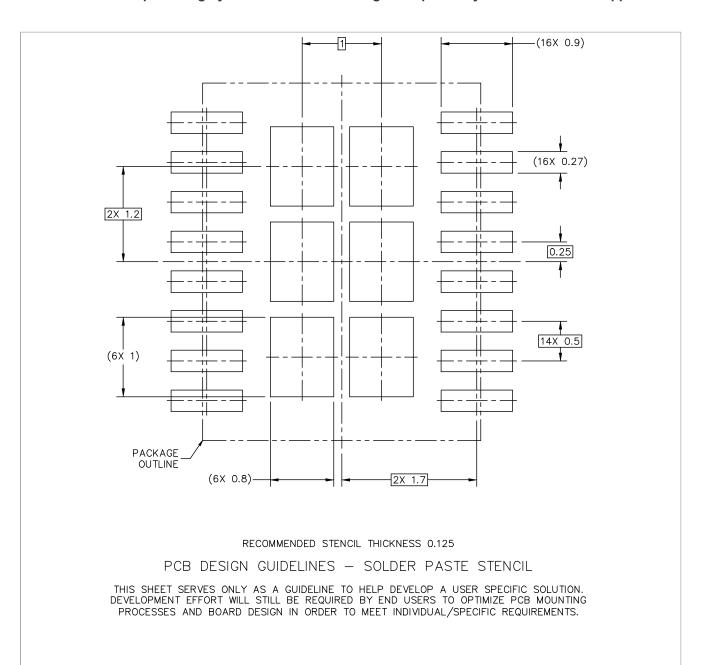

| PCA2131TF/Q900 | A31                | HLSON16 | thermal enhanced low profile small outline; no leads, 16 terminals, 0.125 dimple wettable flank, 0.5 mm pitch, 4.5 mm x 3.5 mm x 1.45 mm body | SOT1992-1 |  |  |  |  |

### 4.1 Ordering options

Table 2. Ordering options

| Product type number | Orderable part<br>number | Package | Packing method | Minimum<br>Order<br>Quantity | Temperature                          |

|---------------------|--------------------------|---------|----------------|------------------------------|--------------------------------------|

| PCA2131TF/Q900      | PCA2131TF/Q900Y          | HLSON16 | REEL 13" Q1 DP | 4000                         | T <sub>amb</sub> = -40 °C to +105 °C |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

# 5 Block diagram

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

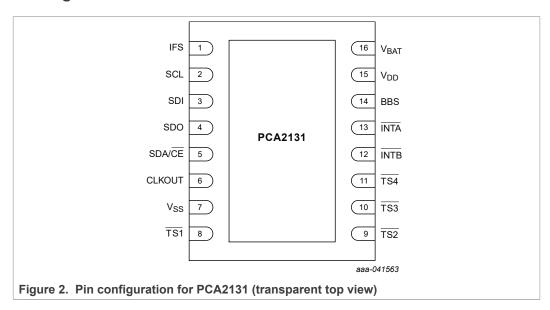

# 6 Pinning information

# 6.1 Pinning

### 6.2 Pin description

Table 3. Pin description

Input or input/output pins must always be at a defined level ( $V_{SS}$  or  $V_{DD}$ ) unless otherwise specified.

| Symbol           | Pin       | Description                                                                                                                |

|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| SCL              | 2         | combined serial clock input for both I <sup>2</sup> C-bus and SPI-bus                                                      |

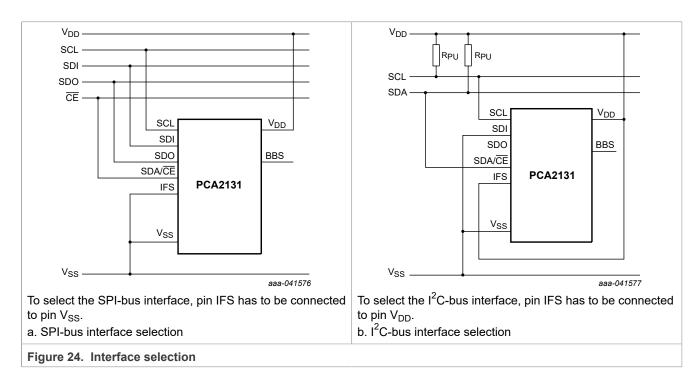

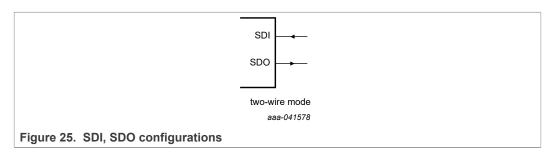

| SDI              | 3         | serial data input for SPI-bus connect to pin V <sub>SS</sub> if I <sup>2</sup> C-bus is selected                           |

| SDO              | 4         | serial data output for SPI-bus, push-pull leave open or connect to pin V <sub>SS</sub> if I <sup>2</sup> C-bus is selected |

| SDA/CE           | 5         | combined serial data input and output for the I <sup>2</sup> C-bus and chip enable input (active LOW) for the SPI-bus      |

| IFS              | 1         | interface selector input connect to pin $V_{SS}$ to select the SPI-bus connect to pin $V_{DD}$ to select the $I^2$ C-bus   |

| TS1,TS2,TS3,TS4, | 8,9,10,11 | timestamp input (active LOW) with 500 k $\Omega$ internal pull-up resistor (R $_{PU}$ )                                    |

| CLKOUT           | 6         | clock output (push-pull)                                                                                                   |

| V <sub>SS</sub>  | 7         | ground supply voltage                                                                                                      |

| INTB             | 12        | interrupt B output (open-drain; active LOW)                                                                                |

| INTA             | 13        | interrupt A output (open-drain; active LOW)                                                                                |

| BBS              | 14        | output voltage (battery backed)                                                                                            |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 3. Pin description...continued

Input or input/output pins must always be at a defined level (V<sub>SS</sub> or V<sub>DD</sub>) unless otherwise specified.

| Symbol      | Pin | Description                                                                                   |

|-------------|-----|-----------------------------------------------------------------------------------------------|

| $V_{BAT}$   | 16  | battery supply voltage (backup) connect to V <sub>SS</sub> if battery switch-over is not used |

| $V_{DD}$    | 15  | supply voltage                                                                                |

| Exposed Pad |     | Tie to V <sub>SS</sub> (preferred) <sup>[1]</sup> or leave floating                           |

<sup>[1]</sup> This protects against signal feedback to the oscillator if routed close to the part.

# 7 Functional description

The PCA2131 is a Real Time Clock (RTC) and calendar with an on-chip Temperature Compensated Crystal (Xtal) Oscillator (TCXO) and a 32.768 kHz quartz crystal integrated into the same package.

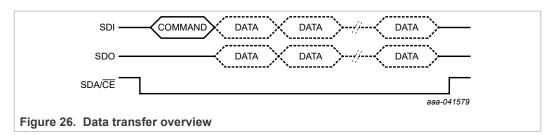

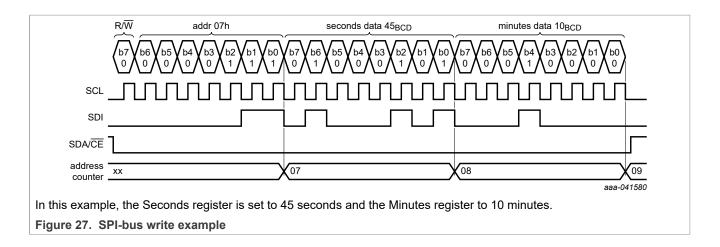

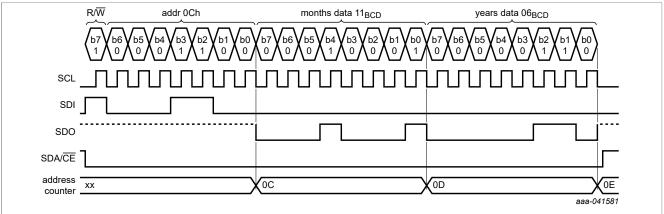

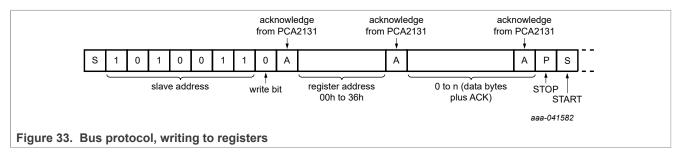

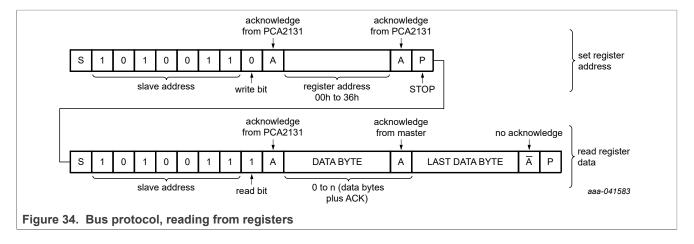

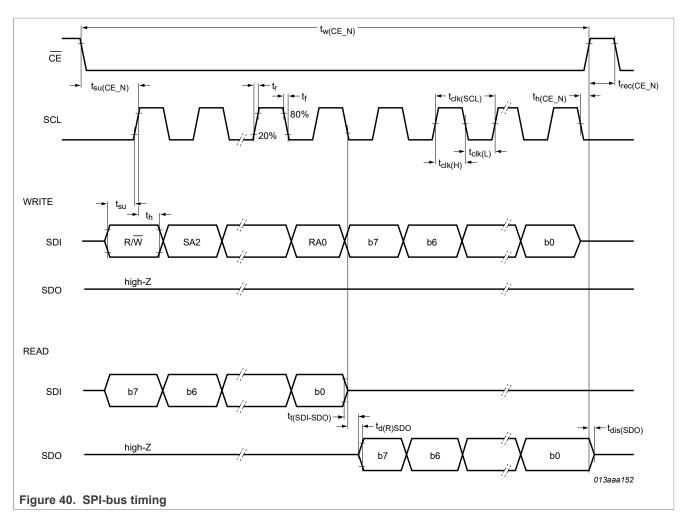

Address and data are transferred by a selectable 400 kHz Fast-mode I<sup>2</sup>C-bus or a 4-line SPI-bus with separate data input and output (see Section 7.16). The maximum speed of the SPI-bus is 6.5 Mbit/s.

The PCA2131 has a backup battery input pin and backup battery switch-over circuit which monitors the main power supply. The backup battery switch-over circuit automatically switches to the backup battery when a power failure condition is detected (see Section 7.5.1). Accurate timekeeping is maintained even when the main power supply is interrupted.

A battery low detection circuit monitors the status of the battery (see Section 7.5.2). When the battery voltage drops below a certain threshold value, a flag is set to indicate that the battery must be replaced soon. This ensures the integrity of the data during periods of battery backup.

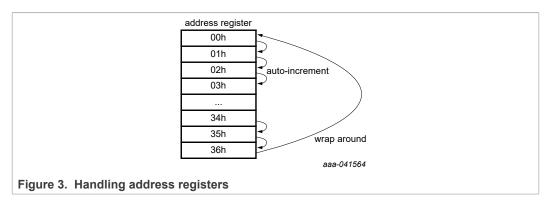

### 7.1 Register overview

The PCA2131 contains an auto-incrementing address register: the built-in address register will increment automatically after each read or write of a data byte up to the register 36h. After register 36h, the auto-incrementing will wrap around to address 00h (see Figure 3).

• The first five registers (memory address 00h, 01h, 02h, 03h and 04h) are used as control registers (see Section 7.2).

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

- The register at address 05h is for software reset.

- The memory addresses 06h through to 0Dh are used as counters for the clock function (1/100 seconds up to years). The date is automatically adjusted for months with fewer than 31 days, including corrections for leap years. The clock can operate in 12-hour mode with an AM/PM indication or in 24-hour mode (see Section 7.9).

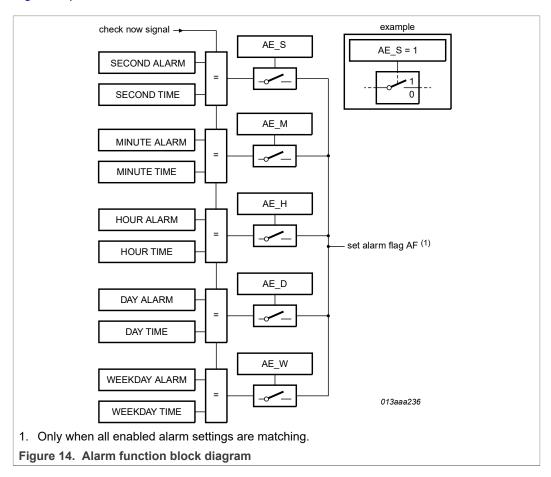

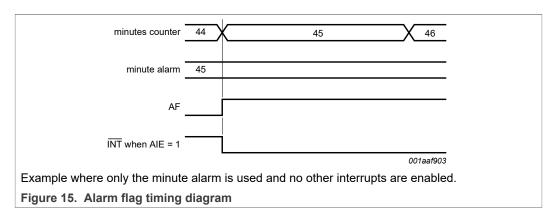

- The registers at addresses 0Eh through 12h define the alarm function. It can be selected that an interrupt is generated when an alarm event occurs (see <u>Section 7.10</u>).

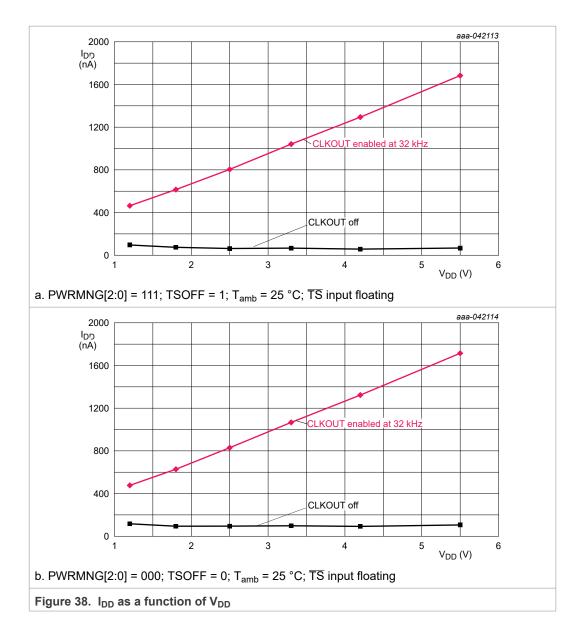

- The register at address 13h defines the temperature measurement period and the clock out mode. The temperature measurement can be selected from every 32 minutes (default) down to every 4minutes (see <u>Table 17</u>). CLKOUT frequencies of 32.768 kHz (default) down to 1 Hz for use as system clock, microcontroller clock, and so on, can be chosen (see <u>Table 18</u>).

- The registers at addresses 14h to 2Fh are used for the timestamp function. When

the trigger event happens, the actual time is saved in the timestamp registers (see

Section 7.12).

- The register at address 30h is used for the correction of the crystal aging effect (see Section 7.4.1).

- The registers at addresses 31h to 34h are used for interrupt configration.

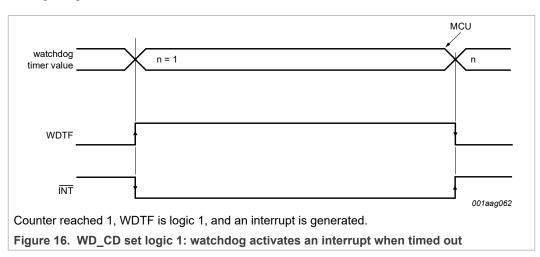

- The registers at addresses 35h and 36h are used for the watchdog timer functions. The

watchdog timer has four selectable source clocks allowing for timer periods from less

than 20 ms to greater than 4 hours (see <u>Table 59</u>). An interrupt is generated when the

watchdog times out.

- The registers 100th Seconds, Seconds, Minutes, Hours, Days, Months, and Years are all coded in Binary Coded Decimal (BCD) format to simplify application use. Other registers are either bit-wise or standard binary.

When one of the RTC registers is written or read, the content of all counters is temporarily frozen, all registers hold their state during SPI or I2C transactions. The time stamp registers would update as soon as the bus transaction completes. This prevents a faulty writing or reading of the clock and calendar during a carry condition (see Section 7.9.9).

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 4. Register overview

Bit positions labeled as T are unused and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Address     | Register name  | Bit          | Bit       |                                                     |                 |                                  |                 |             |       |           | Reference |

|-------------|----------------|--------------|-----------|-----------------------------------------------------|-----------------|----------------------------------|-----------------|-------------|-------|-----------|-----------|

|             |                | 7            | 6         | 5                                                   | 4               | 3                                | 2               | 1           | 0     |           |           |

| Control reg | gisters        |              |           |                                                     |                 | - 1                              |                 |             |       |           |           |

| 00h         | Control_1      | EXT_<br>TEST | TC_DIS    | STOP                                                | 100TH_<br>S_DIS | POR_<br>OVRD                     | 12_24           | MI          | SI    | 0000 1000 | Table 5   |

| 01h         | Control_2      | MSF          | WDTF      | Т                                                   | AF              | Т                                | Т               | AIE         | Т     | 0000 0000 | Table 7   |

| )2h         | Control_3      |              | PWRMNG[2: | 0]                                                  | BTSE            | BF                               | BLF             | BIE         | BLIE  | 1110 0000 | Table 9   |

| 03h         | Control_4      | TSF1         | TSF2      | TSF3                                                | TSF4            | Т                                | Т               | Т           | Т     | 0000 0000 | Table 11  |

| 04h         | Control_5      | TSIE1        | TSIE2     | TSIE3                                               | TSIE4           | Т                                | Т               | Т           | Т     | 0000 0000 | Table 13  |

| Software R  | eset           | '            |           |                                                     |                 |                                  |                 |             |       | 1         | ,         |

| 05h         | SR_Reset       | CPR          | Т         | Т                                                   | Т               | SR                               | Т               | Т           | CTS   | 0010 0100 | Table 24  |

| Time and d  | late registers | '            |           |                                                     |                 |                                  |                 |             |       | 1         | ,         |

| 06h         | 100th_Seconds  |              |           |                                                     | 0000 0000       | Table 25                         |                 |             |       |           |           |

| 07h         | Seconds        | OSF          |           |                                                     | SI              | ECONDS (0 t                      | o 59)           |             |       | 1000 0000 | Table 28  |

| 08h         | Minutes        | -            |           |                                                     | M               | IINUTES (0 to                    | 59)             |             |       | 0000 0000 | Table 31  |

| 09h         | Hours          | -            | -         | AMPM                                                |                 | HOURS                            | (1 to 12) in 12 | ?-hour mode |       | 0000 0000 | Table 33  |

|             |                |              |           |                                                     | Н               | OURS (0 to 2                     | 3) in 24-hour r | node        |       | 0000 0000 |           |

| 0Ah         | Days           | -            | -         |                                                     |                 | DAYS                             | (1 to 31)       |             |       | 0000 0001 | Table 35  |

| 0Bh         | Weekdays       | -            | -         | -                                                   | -               | -                                | W               | /EEKDAYS (0 | to 6) | 0000 0001 | Table 37  |

| 0Ch         | Months         | -            | -         | -                                                   |                 |                                  | MONTHS (1 to    | 12)         |       | 0000 0001 | Table 40  |

| 0Dh         | Years          |              |           |                                                     | YEARS           | 6 (0 to 99)                      |                 |             |       | 0000 0001 | Table 43  |

| Alarm regis | sters          |              |           |                                                     |                 |                                  |                 |             |       |           |           |

| 0Eh         | Second_alarm   | AE_S         |           |                                                     | SECO            | ND_ALARM                         | (0 to 59)       |             |       | 1000 0000 | Table 45  |

| 0Fh         | Minute_alarm   | AE_M         |           |                                                     | MINU            | JTE_ALARM                        | (0 to 59)       |             |       | 1000 0000 | Table 47  |

| 10h         | Hour_alarm     | AE_H         | -         | AMPM HOUR_ALARM (1 to 12) in 12-hour mode 1000 0000 |                 |                                  |                 |             |       | Table 49  |           |

|             |                |              |           |                                                     | HOUF            | R_ALARM (0                       | to 23) in 24-ho | our mode    |       | 1000 0000 |           |

| 11h         | Day_alarm      | AE_D         | -         |                                                     |                 | DAY_ALA                          | RM (1 to 31)    |             |       | 1000 0000 | Table 51  |

| 12h         | Weekday_alarm  | AE_W         | -         | -                                                   | -               | WEEKDAY_ALARM (0 to 6) 1000 0000 |                 |             |       |           |           |

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 4. Register overview...continued

Bit positions labeled as T are unused and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Address   | Register name | Bit |          |                          |                                        |               |                |                  |           | Reset value | Reference |

|-----------|---------------|-----|----------|--------------------------|----------------------------------------|---------------|----------------|------------------|-----------|-------------|-----------|

|           |               | 7   | 6        | 5                        | 4                                      | 3             | 2              | 1                | 0         |             |           |

| 13h       | CLKOUT_ctl    | TC  | R[1:0]   | OTPR                     | -                                      | -             |                | COF[2            | :0]       | 00X0 0000   | Table 15  |

| Timestamp | 1 registers   | -   |          |                          |                                        | '             |                |                  |           | '           | ,         |

| 14h       | Timestp_ctl1  | TSM | TSOFF    | -                        |                                        |               | SUBSEC_TI      | MESTP[4:0]       |           | 0000 0000   | Table 64  |

| 15h       | Sec_timestp1  | -   |          |                          | SE                                     | COND_TIME     | STP (0 to 59   | )                |           | 0000 0000   | Table 66  |

| 16h       | Min_timestp1  | -   |          |                          | М                                      | INUTE_TIMES   | STP (0 to 59   | )                |           | 0000 0000   | Table 68  |

| 17h       | Hour_timestp1 | -   | -        | AMPM                     |                                        | HOUR_T        | MESTP (1 to    | o 12) in 12-hour | mode      | 0000 0000   | Table 70  |

|           |               |     |          |                          | HOUR_TIMESTP (0 to 23) in 24-hour mode |               |                |                  |           | 0000 0000   |           |

| 18h       | Day_timestp1  | -   | -        |                          |                                        | DAY_T         | IMESTP (1 t    | o 31)            |           | 0000 0000   | Table 72  |

| 19h       | Mon_timestp1  | -   | -        | -                        |                                        | М             | ONTH_TIME      | STP (1 to 12)    |           | 0000 0000   | Table 74  |

| 1Ah       | Year_timestp1 |     | <u>'</u> | YEAR_TIMESTP (0 to 99)   |                                        |               |                |                  |           | 0000 0000   | Table 76  |

| Timestamp | o2 registers  |     |          |                          |                                        |               |                |                  |           |             | ,         |

| 1Bh       | Timestp_ctl2  | TSM | TSOFF    | -                        | - SUBSEC_TIMESTP[4:0]                  |               |                |                  | 0000 0000 | Table 64    |           |

| 1Ch       | Sec_timestp2  | -   |          | SECOND_TIMESTP (0 to 59) |                                        |               |                |                  | 0000 0000 | Table 66    |           |

| 1Dh       | Min_timestp2  | -   |          |                          | М                                      | INUTE_TIMES   | STP (0 to 59   | )                |           | 0000 0000   | Table 68  |

| 1Eh       | Hour_timestp2 | -   | -        | AMPM                     |                                        | HOUR_T        | MESTP (1 to    | o 12) in 12-hour | mode      | 0000 0000   | Table 70  |

|           |               |     |          |                          | НС                                     | DUR_TIMEST    | P (0 to 23) in | 24-hour mode     |           | 0000 0000   |           |

| 1Fh       | Day_timestp2  | -   | -        |                          |                                        | DAY_T         | IMESTP (11     | o 31)            |           | 0000 0000   | Table 72  |

| 20h       | Mon_timestp2  | -   | -        | -                        |                                        | М             | ONTH_TIME      | STP (1 to 12)    |           | 0000 0000   | Table 74  |

| 21h       | Year_timestp2 |     |          |                          | YEAR_                                  | TIMESTP (0 to | 99)            |                  |           | 0000 0000   | Table 76  |

| Timestamp | o3 registers  |     |          |                          |                                        |               |                |                  |           |             | ,         |

| 22h       | Timestp_ctl3  | TSM | TSOFF    | -                        |                                        |               | SUBSEC_TI      | MESTP[4:0]       |           | 0000 0000   | Table 64  |

| 23h       | Sec_timestp3  | -   |          |                          | SE                                     | COND_TIME     | STP (0 to 59   | )                |           | 0000 0000   | Table 66  |

| 24h       | Min_timestp3  | -   |          | MINUTE_TIMESTP (0 to 59) |                                        |               |                | 0000 0000        | Table 68  |             |           |

| 25h       | Hour_timestp3 | -   | -        | AMPM                     |                                        | HOUR_T        | MESTP (1 to    | o 12) in 12-hour | mode      | 0000 0000   | Table 70  |

|           |               |     |          |                          | НС                                     | DUR_TIMEST    | P (0 to 23) in | 24-hour mode     |           | 0000 0000   |           |

| 26h       | Day_timestp3  | -   | -        |                          |                                        | DAY_T         | IMESTP (1 t    | o 31)            |           | 0000 0000   | Table 72  |

| 27h       | Mon_timestp3  | -   | -        | -                        |                                        | М             | ONTH_TIME      | STP (1 to 12)    |           | 0000 0000   | Table 74  |

PCA213

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 4. Register overview...continued

Bit positions labeled as T are unused and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Address      | Register name   | Bit   |       |       |                                             |                    |               |         |           | Reset value | Reference |

|--------------|-----------------|-------|-------|-------|---------------------------------------------|--------------------|---------------|---------|-----------|-------------|-----------|

|              |                 | 7     | 6     | 5     | 4                                           | 3                  | 2             | 1       | 0         |             |           |

| 28h          | Year_timestp3   |       |       |       | YEAR_TIM                                    | 1ESTP (0 to 99)    |               |         |           | 0000 0000   | Table 76  |

| Timestamp    | 4 registers     | '     |       |       |                                             |                    |               |         |           |             | ,         |

| 29h          | Timestp_ctl4    | TSM   | TSOFF | -     |                                             | SUBS               | SEC_TIMEST    | ΓP[4:0] |           | 0000 0000   | Table 64  |

| 2Ah          | Sec_timestp4    | -     |       |       | SECC                                        | OND_TIMESTP        | (0 to 59)     |         | 0000 0000 | Table 66    |           |

| 2Bh          | Min_timestp4    | -     |       |       | MINUTE_TIMESTP (0 to 59)                    |                    |               |         |           | 0000 0000   | Table 68  |

| 2Ch          | Hour_timestp4   | -     | -     | AMPM  | AMPM HOUR_TIMESTP (1 to 12) in 12-hour mode |                    |               |         |           | 0000 0000   | Table 70  |

|              |                 |       |       |       | HOUR_TIMESTP (0 to 23) in 24-hour mode      |                    |               |         |           |             |           |

| 2Dh          | Day_timestp4    | -     | -     |       |                                             | DAY_TIMES          | STP (1 to 31) |         |           | 0000 0000   | Table 72  |

| 2Eh          | Mon_timestp4    | -     | -     | -     | - MONTH_TIMESTP (1 to 12)                   |                    |               |         |           |             | Table 74  |

| 2Fh          | Year_timestp4   |       |       |       | YEAR_TIM                                    | 1ESTP (0 to 99)    |               |         |           | 0000 0000   | Table 76  |

| Aging offse  | et register     | '     |       |       |                                             |                    |               |         |           |             | ,         |

| 30h          | Aging_offset    | -     | -     | -     | -                                           |                    | AC            | 0[3:0]  |           | 0000 1000   | Table 19  |

| Interrupt ma | ask registers   | ,     |       |       | '                                           |                    |               |         |           |             | ,         |

| 31h          | INT_A_MASK1     | -     | -     | MIA   | SIA                                         | WD_CDA             | AIEA          | BIEA    | BLIEA     | 0011 1111   | Table 80  |

| 3 <u>2</u> h | INT_A_MASK2     | -     | -     | -     | -                                           | TSIE1A             | TSIE2A        | TSIE3A  | TSIE4A    | 0000 1111   | Table 80  |

| 33h          | INT_B_MASK1     | -     | -     | MIB   | SIB                                         | WD_CDB             | AIEB          | BIEB    | BLIEB     | 0011 1111   | Table 82  |

| 34h          | INT_B_MASK2     | -     | -     | -     | -                                           | TSIE1B             | TSIE2B        | TSIE3B  | TSIE4B    | 0000 1111   | Table 82  |

| Watchdog     | registers       | 1     |       | 1     |                                             |                    | 1             |         | -         | 1           | 1         |

| 35h          | Watchdg_tim_ctl | WD_CD | Т     | TI_TP | -                                           | -                  | -             | TF      | [1:0]     | 0000 0011   | Table 55  |

| 36h          | Watchdg_tim_val |       |       | 1     | WATCHDG                                     | <br>G_TIM_VAL[7:0] | 1             | 1       |           | 0000 0000   | Table 57  |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

### 7.2 Control registers

The first five registers of the PCA2131, with the addresses 00h, 01h, 02h, 03h and 04h, are used as control registers.

### 7.2.1 Register Control\_1

Table 5. Control\_1 - control and status register 1 (address 00h) bit allocation Bits labeled as T are unused and return 0 when read.

| Bit         | 7            | 6      | 5    | 4               | 3            | 2     | 1  | 0  |

|-------------|--------------|--------|------|-----------------|--------------|-------|----|----|

| Symbol      | EXT_<br>TEST | TC_DIS | STOP | 100TH_<br>S_DIS | POR_<br>OVRD | 12_24 | MI | SI |

| Reset value | 0            | 0      | 0    | 0               | 1            | 0     | 0  | 0  |

Table 6. Control\_1 - control and status register 1 (address 00h) bit description Bits labeled as T are unused and return 0 when read.

| Bit | Symbol      | Value | Description                                                                                                                      | Reference             |

|-----|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 7   | EXT_TEST    | 0     | normal mode                                                                                                                      | Section 7.14          |

|     |             | 1     | external clock test mode                                                                                                         | -                     |

| 6   | TC_DIS      | 0     | Temperature compensation enabled                                                                                                 | Section 7.3.1         |

|     |             | 1     | Temperature compensation disabled                                                                                                |                       |

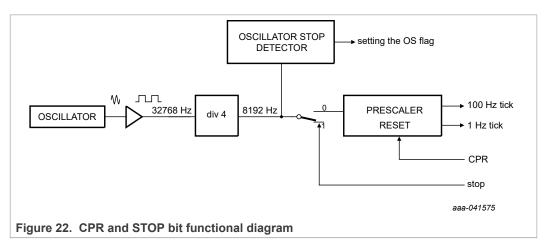

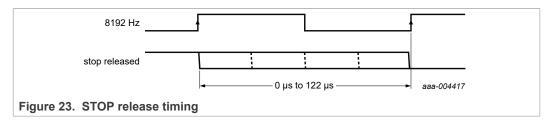

| 5   | STOP        | 0     | RTC source clock runs                                                                                                            | Section 7.15          |

|     |             | 1     | RTC clock is stopped; RTC divider chain flip-flops are asynchronously set logic 0; CLKOUT output frequencies are still available |                       |

| 4   | 100TH_S_DIS | 0     | -                                                                                                                                |                       |

|     |             | 1     | 100th seconds counter Disabled, register 06h reset to 00h.                                                                       | -                     |

| 3   | POR_OVRD    | 0     | Power-On Reset Override (PORO) facility disabled; set logic 0 for normal operation                                               | Section 7.7.2         |

|     |             | 1     | Power-On Reset Override (PORO) sequence reception enabled                                                                        |                       |

| 2   | 12_24       | 0     | 24-hour mode selected                                                                                                            | Table 34,             |

|     |             | 1     | 12-hour mode selected                                                                                                            | Table 50,<br>Table 71 |

| 1   | MI          | 0     | minute interrupt disabled                                                                                                        | <u>Section 7.13.1</u> |

|     |             | 1     | minute interrupt enabled                                                                                                         |                       |

| 0   | SI          | 0     | second interrupt disabled                                                                                                        |                       |

|     |             | 1     | second interrupt enabled                                                                                                         |                       |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

### 7.2.2 Register Control\_2

Table 7. Control\_2 - control and status register 2 (address 01h) bit allocation Bits labeled as T are unused and return 0 when read.

| Bit         | 7   | 6    | 5 | 4  | 3 | 2 | 1   | 0 |

|-------------|-----|------|---|----|---|---|-----|---|

| Symbol      | MSF | WDTF | Т | AF | Т | T | AIE | Т |

| Reset value | 0   | 0    | 0 | 0  | 0 | 0 | 0   | 0 |

Table 8. Control\_2 - control and status register 2 (address 01h) bit description Bits labeled as T are unused and return 0 when read.

| Bit | Symbol | Value | Description                                                                                       | Reference             |  |

|-----|--------|-------|---------------------------------------------------------------------------------------------------|-----------------------|--|

| 7   | MSF    | 0     | no minute or second interrupt generated                                                           | Section 7.13          |  |

|     |        | 1     | flag set when minute or second interrupt<br>generated;<br>flag must be cleared to clear interrupt |                       |  |

| 6   | WDTF   | 0     | no watchdog timer interrupt generated                                                             | <u>Section 7.13.3</u> |  |

|     | 1      |       | flag set when watchdog timer interrupt generated; flag cannot be cleared by command (read-only)   |                       |  |

| 5   | Т      | 0     | unused                                                                                            | -                     |  |

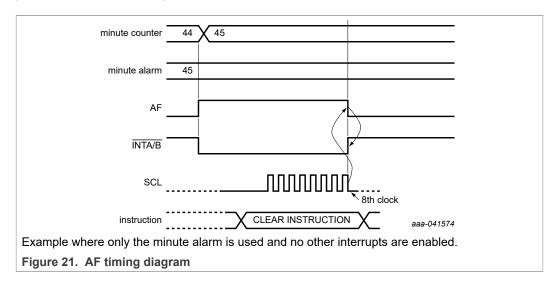

| 4   | AF     | 0     | no alarm interrupt triggered                                                                      | Section 7.10.6        |  |

|     |        | 1     | flag set when alarm triggered; flag must be cleared to clear interrupt                            |                       |  |

| 3:2 | Т      | 0     | unused                                                                                            | -                     |  |

| 1   | AIE    | 0     | no interrupt generated from the alarm flag                                                        | <u>Section 7.13.4</u> |  |

|     |        | 1     | interrupt generated when alarm flag set                                                           |                       |  |

| 0   | Т      | 0     | unused                                                                                            | -                     |  |

# 7.2.3 Register Control\_3

Table 9. Control\_3 - control and status register 3 (address 02h) bit allocation

| Bit         | 7 | 6          | 5 | 4    | 3  | 2   | 1   | 0    |

|-------------|---|------------|---|------|----|-----|-----|------|

| Symbol      | ı | PWRMNG[2:0 | ] | BTSE | BF | BLF | BIE | BLIE |

| Reset value | 1 | 1          | 1 | 0    | 0  | 0   | 0   | 0    |

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 10. Control\_3 - control and status register 3 (address 02h) bit description

| Bit    | Symbol      | Value           | Description                                                                                                    | Reference             |

|--------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------|-----------------------|

| 7 to 5 | PWRMNG[2:0] | see<br>Table 22 | control of the battery switch-over, battery low detection, and extra power fail detection functions            | Section 7.5           |

| 4      | BTSE        | 0               | no timestamp when battery switch-over occurs                                                                   | Section 7.12.4        |

|        |             | 1               | time-stamped when battery switch-over occurs                                                                   |                       |

| 3      | BF          | 0               | no battery switch-over interrupt occurred                                                                      | Section 7.5.1         |

|        |             | 1               | flag set when battery switch-over occurs; flag must be cleared to clear interrupt                              | Section 7.12.4        |

| 2      | BLF         | 0               | battery status ok;<br>no battery low interrupt generated                                                       | Section 7.5.2         |

|        |             | 1               | battery status low; flag cannot be cleared by command, flag is automatically cleared when battery is replaced. |                       |

| 1      | 1 BIE       |                 | no interrupt generated from the battery flag (BF)                                                              | Section 7.13.6        |

|        |             |                 | interrupt generated when BF is set                                                                             |                       |

| 0      | ) BLIE      |                 | no interrupt generated from battery low flag (BLF)                                                             | <u>Section 7.13.7</u> |

|        |             |                 | interrupt generated when BLF is set                                                                            |                       |

# 7.2.4 Register Control\_4

Table 11. Control\_4 - control and status register 4 (address 03h) bit allocation

| Bit         | 7    | 6    | 5    | 4    | 3 | 2 | 1 | 0 |

|-------------|------|------|------|------|---|---|---|---|

| Symbol      | TSF1 | TSF2 | TSF3 | TSF4 | Т | T | Т | Т |

| Reset value | 0    | 0    | 0    | 0    | 0 | 0 | 0 | 0 |

Table 12. Control\_4 - control and status register 4 (address 03h) bit description

| Bit | Symbol | Value                                                                                  | Description                                                                          | Reference      |

|-----|--------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|

| 7   | TSF1   | 0                                                                                      | no timestamp interrupt generated for pin TS1                                         | Section 7.12.1 |

|     |        | 1                                                                                      | flag set when TS1 input is driven to ground; flag must be cleared to clear interrupt |                |

| 6   | TSF2   | 0                                                                                      | no timestamp interrupt generated when pin TS2                                        | Section 7.12.1 |

|     |        | 1 flag set when TS2 input is driven to ground; flag must be cleared to clear interrupt |                                                                                      |                |

| 5   | TSF3   | 0                                                                                      | no timestamp interrupt generated for pin TS3                                         | Section 7.12.1 |

|     |        | 1                                                                                      | flag set when TS3 input is driven to ground; flag must be cleared to clear interrupt |                |

| 4   | TSF4   | 0                                                                                      | no timestamp interrupt generated when pin TS4                                        | Section 7.12.1 |

|     |        | 1                                                                                      | flag set when TS4 input is driven to ground; flag must be cleared to clear interrupt |                |

| 3   | Т      | 0                                                                                      | Unused                                                                               |                |

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 12. Control\_4 - control and status register 4 (address 03h) bit description...continued

| Bit | Symbol | Value | Description | Reference |

|-----|--------|-------|-------------|-----------|

| 2   | Т      | 0     | Unused      |           |

| 1   | Т      | 0     | Unused      |           |

| 0   | Т      | 0     | Unused      |           |

### 7.2.5 Register Control\_5

Table 13. Control\_5 - control and status register 5 (address 04h) bit allocation

| Bit         | 7     | 6     | 5     | 4     | 3 | 2 | 1 | 0 |

|-------------|-------|-------|-------|-------|---|---|---|---|

| Symbol      | TSIE1 | TSIE2 | TSIE3 | TSIE4 | Т | T | Т | Т |

| Reset value | 0     | 0     | 0     | 0     | 0 | 0 | 0 | 0 |

Table 14. Control 5 - control and status register 5 (address 04h) bit description

| Bit    | Symbol | Value | /alue Description                                                      |                |

|--------|--------|-------|------------------------------------------------------------------------|----------------|

| 7      | TSIE1  | 0     | no interrupt generated from timestamp flag of TS1                      | Section 7.13.5 |

|        |        | 1     | interrupt generated when timestamp flag set of TS1                     |                |

| 6      | TSIE2  | 0     | no interrupt generated from timestamp flag of TS2                      | Section 7.13.5 |

|        |        | 1     | interrupt generated when timestamp flag set of TS2                     | -              |

| 5      | TSIE3  | 0     | no interrupt generated from timestamp flag of TS3                      | Section 7.13.5 |

|        |        | 1     | interrupt generated when timestamp flag set of TS3                     | -              |

| 4      | TSIE4  | 0     | no interrupt generated from timestamp flag of $\overline{\text{TS4}}$  | Section 7.13.5 |

|        |        | 1     | interrupt generated when timestamp flag set of $\overline{\text{TS4}}$ | -              |

| 3 to 0 | Т      | 0     | unused                                                                 | -              |

# 7.3 Register CLKOUT\_ctl

Table 15. CLKOUT\_ctl - CLKOUT control register (address 13h) bit allocation

Bits labeled as T are unused and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Bit         | 7   | 6     | 5    | 4 | 3 | 2 | 1        | 0 |

|-------------|-----|-------|------|---|---|---|----------|---|

| Symbol      | TCR | [1:0] | OTPR | Т | Т |   | COF[2:0] |   |

| Reset value | 0   | 0     | X    | 0 | 0 | 0 | 0        | 0 |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 16. CLKOUT\_ctl - CLKOUT control register (address 13h) bit description Bits labeled as T are unused and return 0 when read.

| Bit    | Symbol   | Value               | Description                    | Reference     |

|--------|----------|---------------------|--------------------------------|---------------|

| 7 to 6 | TCR[1:0] | see <u>Table 17</u> | temperature measurement period |               |

| 5      | OTPR     | 0                   | no OTP refresh                 | Section 7.3.2 |

|        |          | 1                   | OTP refresh performed          |               |

| 4      | Т        | 0                   | unused <sup>[1]</sup>          |               |

| 3      | Т        | 0                   | unused                         |               |

| 2 to 0 | COF[2:0] | see <u>Table 18</u> | CLKOUT frequency selection     | Section 7.3.3 |

<sup>[1]</sup> programming this bit to 1 may lead to a decrease of timing accuracy.

#### 7.3.1 Temperature compensated Real Time Clock

The frequency of tuning fork quartz crystal oscillators is temperature-dependent. In the PCA2131, the frequency deviation caused by temperature variation is corrected by adjusting the RTC frequency divider with digital method.

The load capacitance is trimmed to the required value at 25 °C in order to compensate the frequency deviation over process variation.

The frequency accuracy at 25 °C can be evaluated by measuring the frequency of the square wave signal available at the output pin CLKOUT. However, the selection of  $f_{CLKOUT}$  = 32.768 kHz (default value) can lead to inaccurate measurements. Accurate frequency measurement occurs when  $f_{CLKOUT}$  = 16.384 kHz or lower is selected (see Table 18).

The temperature compensated frequency input for the Real Time Clock cannot be observed at the CLKOUT pin but can be evaluated by following these steps.

- Set Second Interrupt, bit SI in register Control\_1 to 1

- Set bit TI\_TP in register Watchdg\_tim\_ctl to 1 for a pulsed interrupt signal

- Set bit SIA in register INTA\_MASK\_1 to 0 to direct the Second Interrupt to pin INTA for a 1 Hz pulse output.

The RTC temperature compensation works by adding or deleting pulses at the 32.768 kHz level. These correction pulses are spaced evenly over a sufficiently long period of time to reach the required resolution and accuracy. Every second corrections with a resolution of about 30.5 ppm (1/32768) can be generated by the temperature compensation engine. If for instance a 10 ppm correction is called for, the correction pulses will be generated approximately once every 3 seconds, for a 50 ppm correction every 0.6 s and so on.

The 1 Hz interrupt output signal can be measured with a counter and by selecting an appropriate gating time the measurement resolution can be set to the desired level. A gating time of 100 s for instance will determine the averaged 1 second period with a resolution of 0.3 ppm.

The feature of temperature compensation can be turned off for ultra low power consumption by first performing a software reset (SR) followed by setting TC\_DIS to '1' within 5 seconds.

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

#### 7.3.1.1 Temperature measurement

The PCA2131 has a temperature sensor circuit used to perform temperature compensation of the clock input to the RTC. The temperature is measured immediately after power-on and then periodically with a period set by the temperature conversion rate TCR[1:0] in the register CLKOUT\_ctl. During the first approximately 60 s after start-up the compensation will be inactive, after this period the temperature compensation is active.

Table 17. Temperature measurement period

| TCR[1:0] |     | Temperature measurement period |

|----------|-----|--------------------------------|

| 00       | [1] | 32 min                         |

| 01       |     | 16 min                         |

| 10       |     | 8 min                          |

| 11       |     | 4 min                          |

<sup>[1]</sup> Default value.

#### 7.3.2 OTP refresh

Each IC is calibrated during production and testing of the device. The calibration parameters are stored on EPROM cells called One Time Programmable (OTP) cells. It is recommended to process an OTP refresh once after the power is up and the oscillator is operating stable. The OTP refresh takes less than 100 ms to complete.

To perform an OTP refresh, bit OTPR has to be cleared (set to logic 0) and then set to logic 1 again.

When read OTPR bit, its state is:

"0" until the OTP read state machine completes copying of the eFuse data into the shadow registers. This could be due to a POR event or to writing a 0 > 1 to the OTPR register bit.

"1" when the OTP read state machine completes copying to the shadow registers from the eFuse instances. During normal operation OTPR must be kept at 1 to prevent higher power usage.

The OTP logic is not reset nor affected by the Software Reset. The OTPR functionality is only reset by the initial digital POR.

During OTP refresh,  $V_{DD}$  has to be above 1.8 V, the rising speed to 1.8 V needs to be faster than 2 V/100 ms. After OTP refresh has finished, PCA2131 can operate with  $V_{DD}$  as low as 1.2 V.

#### 7.3.3 Clock output

A programmable square wave is available at pin CLKOUT. Operation is controlled by the COF[2:0] control bits in register CLKOUT\_ctl. Frequencies of 32.768 kHz (default) down to 1 Hz can be generated for use as system clock, microcontroller clock, charge pump input, or for calibrating the oscillator at 25 °C to determine aging offset. The CLKOUT output is not temperature compensated to prevent jitter due to digital compensation method.

CLKOUT is a push-pull output and is enabled at power-on. When disabled, the output is high-impedance.

PCA2131

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 18. CLKOUT frequency selection

| COF[2:0] |     | CLKOUT frequency (Hz) | Typical duty cycle [1] |

|----------|-----|-----------------------|------------------------|

| 000      | [2] | 32 768                | 60 : 40 to 40 : 60     |

| 001      |     | 16 384                | 50 : 50                |

| 010      |     | 8 192                 | 50 : 50                |

| 011      |     | 4 096                 | 50 : 50                |

| 100      |     | 2 048                 | 50 : 50                |

| 101      |     | 1 024                 | 50 : 50                |

| 110      |     | 1                     | 50 : 50                |

| 111      |     | CLKOUT = high-Z       | -                      |

<sup>[1]</sup> Duty cycle definition: % HIGH-level time: % LOW-level time.

The duty cycle of the selected clock is not controlled, however, due to the nature of the clock generation all but the 32.768 kHz frequencies are 50 : 50.

### 7.4 Register Aging\_offset

Table 19. Aging\_offset - crystal aging offset register (address 30h) bit allocation Bits labeled as T are unused and return 0 when read.

| Bit         | 7 | 6 | 5 | 4 | 3 | 2   | 1    | 0 |

|-------------|---|---|---|---|---|-----|------|---|

| Symbol      | T | Т | T | Т |   | AO[ | 3:0] |   |

| Reset value | 0 | 0 | 0 | 0 | 1 | 0   | 0    | 0 |

Table 20. Aging\_offset - crystal aging offset register (address 30h) bit description Bits labeled as T are unused and return 0 when read.

| Bit    | Symbol  | Value               | Description        |

|--------|---------|---------------------|--------------------|

| 7 to 4 | Т       | 0000                | unused             |

| 3 to 0 | AO[3:0] | see <u>Table 21</u> | aging offset value |

#### 7.4.1 Crystal aging correction

The PCA2131 has an offset register Aging\_offset to correct the crystal aging effects <sup>1</sup>.

The accuracy of the frequency of a quartz crystal depends on its aging. The aging offset adds an adjustment, positive or negative, in the temperature compensation circuit which allows correcting the aging effect.

The aging offset bits allow a frequency correction of typically 2 ppm per AO[3:0] value, from -14 ppm to +16 ppm.

<sup>[2]</sup> Default value.

<sup>1</sup> For further information, refer to the application note [1].

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 21. Frequency correction at 25 °C, typical

| AO[3:0] |        |     | ppm |

|---------|--------|-----|-----|

| Decimal | Binary |     |     |

| 0       | 0000   |     | +16 |

| 1       | 0001   |     | +14 |

| 2       | 0010   |     | +12 |

| 3       | 0011   |     | +10 |

| 4       | 0100   |     | +8  |

| 5       | 0101   |     | +6  |

| 6       | 0110   |     | +4  |

| 7       | 0111   |     | +2  |

| 8       | 1000   | [1] | 0   |

| 9       | 1001   |     | -2  |

| 10      | 1010   |     | -4  |

| 11      | 1011   |     | -6  |

| 12      | 1100   |     | -8  |

| 13      | 1101   |     | -10 |

| 14      | 1110   |     | -12 |

| 15      | 1111   |     | -14 |

<sup>[1]</sup> Default value.

### 7.5 Power management functions

The PCA2131 has two power supplies:

V<sub>DD</sub> - the main power supply

V<sub>BAT</sub> - the battery backup supply

Internally, PCA2131 operates with the internal operating voltage  $V_{oper(int)}$  which is also available as  $V_{BBS}$  on the battery backed output voltage pin, BBS. Depending on the condition of the main power supply and the selected power management function,  $V_{oper(int)}$  is either on the potential of  $V_{DD}$  or  $V_{BAT}$ .

Two power management functions are implemented:

**Battery switch-over function** - monitors the main power supply  $V_{DD}$  and switching to  $V_{BAT}$  in case a power fail condition is detected (see Section 7.5.1).

**Battery low detection function** - monitors the status of the battery,  $V_{BAT}$  (see Section 7.5.2).

The power management functions are controlled by the control bits PWRMNG[2:0] (see <u>Table 22</u>) in register Control\_3 (see <u>Table 10</u>):

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

| Table 22. Power management control bit description | Table 22. | Power management | control b | oit description |

|----------------------------------------------------|-----------|------------------|-----------|-----------------|

|----------------------------------------------------|-----------|------------------|-----------|-----------------|

| PWRMNG[2:0] |         | Function                                                                                                                |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------------|

| 000         |         | battery switch-over function is enabled in standard mode; battery low detection function is enabled                     |

| 001,010     |         | battery switch-over function is enabled in standard mode; battery low detection function is disabled                    |

| 011         |         | battery switch-over function is enabled in direct switching mode; battery low detection function is enabled             |

| 100,101     |         | battery switch-over function is enabled in direct switching mode; battery low detection function is disabled            |

| 110,111     | [1] [2] | battery switch-over function is disabled, only one power supply $(V_{DD})$ ; battery low detection function is disabled |

<sup>[1]</sup> Default value.

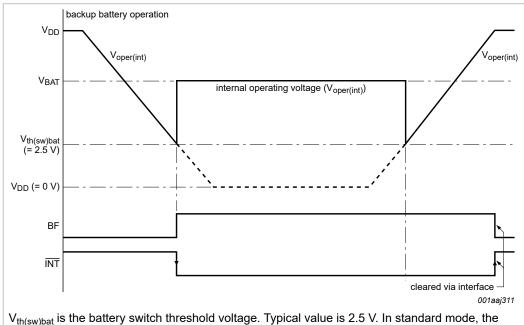

#### 7.5.1 Battery switch-over function

PCA2131 has a backup battery switch-over circuit which monitors the main power supply  $V_{DD}$ . When a power failure condition is detected, it automatically switches to the backup battery.

One of two operation modes can be selected:

Standard mode - the power failure condition happens when:

$$V_{DD} < V_{BAT}$$

AND  $V_{DD} < V_{th(sw)bat}$

$V_{th(sw)bat}$  is the battery switch threshold voltage. Typical value is 2.5 V. The battery switch-over in standard mode works only for  $V_{DD} > 2.5$  V. Applying back-up battery voltage to  $V_{BAT}$  without applying  $V_{DD}$  supply will not power on the device; only when  $V_{DD}$  main power is supplied the device will start operating.

**Direct switching mode** - the power failure condition happens when  $V_{DD} < V_{BAT}$ . Direct switching from  $V_{DD}$  to  $V_{BAT}$  without requiring  $V_{DD}$  to drop below  $V_{th(sw)bat}$

When a power failure condition occurs and the power supply switches to the battery, the following sequence occurs:

- 1. The battery switch flag BF (register Control 3) is set to logic 1.

- 2. An interrupt is generated if the control bit BIE (register Control\_3) is enabled (see Section 7.13.6).

- 3. If the control bit BTSE (register Control\_3) is logic 1, the timestamp 4 registers store the time and date when the battery switch occurred (see Section 7.12.4).

- 4. The battery switch flag BF is cleared by command; it must be cleared to clear the interrupt.

The interface and CLKOUT output are disabled in battery backup operation:

- Interface inputs are not recognized, preventing extraneous data being written to the device

- · Interface outputs are high-impedance

<sup>[2]</sup> When the battery switch-over function is disabled, the device works only with the power supply V<sub>DD</sub>. V<sub>BAT</sub> must be put to ground and the battery low detection function is disabled.

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

For further information about I<sup>2</sup>C-bus communication and battery backup operation, see Section 7.16.3.

#### 7.5.1.1 Standard mode

If  $V_{DD} > V_{BAT}$  OR  $V_{DD} > V_{th(sw)bat}$ :  $V_{oper(int)}$  is at  $V_{DD}$  potential.

If  $V_{DD} < V_{BAT}$  AND  $V_{DD} < V_{th(sw)bat}$ :  $V_{oper(int)}$  is at  $V_{BAT}$  potential.

$V_{th(sw)bat}$  is the battery switch threshold voltage. Typical value is 2.5 V. In standard mode, the battery switch-over works only for  $V_{DD} > 2.5$  V.

$V_{DD}$  may be lower than  $V_{BAT}$  (for example  $V_{DD}$  = 3 V,  $V_{BAT}$  = 4.1 V).

Figure 4. Battery switch-over behavior in standard mode with bit BIE set logic 1 (enabled)

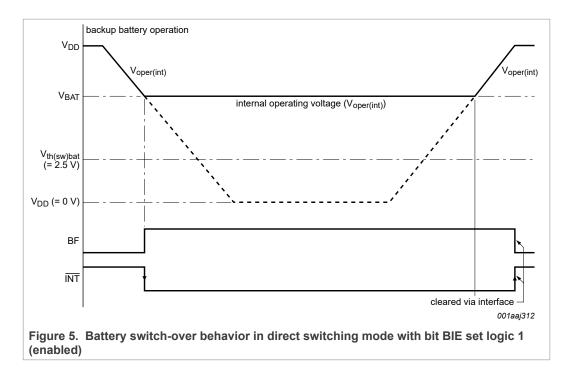

#### 7.5.1.2 Direct switching mode

If  $V_{DD} > V_{BAT}$ :  $V_{oper(int)}$  is at  $V_{DD}$  potential.

If  $V_{DD} < V_{BAT}$ :  $V_{oper(int)}$  is at  $V_{BAT}$  potential.

The direct switching mode is useful in systems where  $V_{DD}$  is always higher than  $V_{BAT}$ . This mode is not recommended if the  $V_{DD}$  and  $V_{BAT}$  values are similar (for example,  $V_{DD}$  = 3.3 V,  $V_{BAT}$   $\geq$  3.0 V). In direct switching mode, the power consumption is reduced compared to the standard mode because the monitoring of  $V_{DD}$  and  $V_{th(sw)bat}$  is not performed.

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

### 7.5.1.3 Battery switch-over disabled: only one power supply (V<sub>DD</sub>)

When the battery switch-over function is disabled:

- The power supply is applied on the V<sub>DD</sub> pin

- The V<sub>BAT</sub> pin must be connected to ground

- V<sub>oper(int)</sub> is at V<sub>DD</sub> potential

- The battery flag (BF) is always logic 0

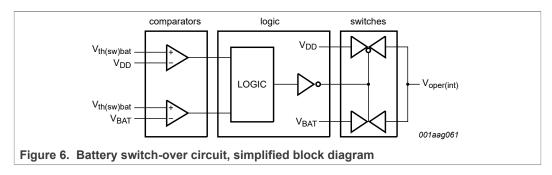

#### 7.5.1.4 Battery switch-over architecture

The architecture of the battery switch-over circuit is shown in Figure 6.

$V_{oper(int)}$  is at  $V_{DD}$  or  $V_{BAT}$  potential.

**Remark:** It has to be assured that there are decoupling capacitors on the pins  $V_{DD}$ ,  $V_{BAT}$ , and BBS.

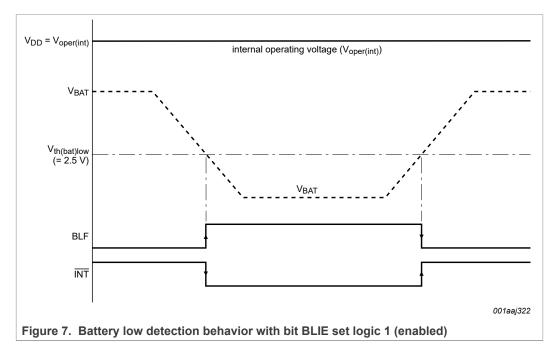

### 7.5.2 Battery low detection function

The PCA2131 has a battery low detection circuit which monitors the status of the battery  $V_{\text{BAT}}$ .

PCA2131

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

When  $V_{BAT}$  drops below the threshold value  $V_{th(bat)low}$  (typical 2.5 V), the BLF flag (register Control\_3) is set to indicate that the battery is low and that it must be replaced. Monitoring of the battery voltage also occurs during battery operation.

An unreliable battery cannot prevent the supply voltage from dropping below  $V_{low}$  (typical 1.2 V) and with that the data integrity gets lost. (For further information about  $V_{low}$  see Section 7.6.)

When  $V_{BAT}$  drops below the threshold value  $V_{th(bat)low}$ , the following sequence occurs (see <u>Figure 7</u>):

- 1. The battery low flag BLF is set logic 1.

- 2. An interrupt is generated if the control bit BLIE (register Control\_3) is enabled (see Section 7.13.7).

- 3. The flag BLF remains logic 1 until the battery is replaced. BLF cannot be cleared by command. It is automatically cleared by the battery low detection circuit when the battery is replaced or when the voltage rises again above the threshold value. This could happen if a super capacitor is used as a backup source and the main power is applied again.

### 7.5.3 Battery backup supply

The  $V_{BBS}$  voltage on the output pin BBS is at the same potential as the internal operating voltage  $V_{oper(int)}$ , depending on the selected battery switch-over function mode:

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 23. Output pin BBS

| Battery switch-over function mode | Conditions                                                                      | Potential of V <sub>oper(int)</sub> and V <sub>BBS</sub> |

|-----------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|

| standard                          | $V_{DD} > V_{BAT} OR V_{DD} > V_{th(sw)bat}$                                    | $V_{DD}$                                                 |

|                                   | V <sub>DD</sub> < V <sub>BAT</sub> AND V <sub>DD</sub> < V <sub>th(sw)bat</sub> | V <sub>BAT</sub>                                         |

| direct switching                  | $V_{DD} > V_{BAT}$                                                              | $V_{DD}$                                                 |

|                                   | $V_{DD} < V_{BAT}$                                                              | $V_{BAT}$                                                |

| disabled                          | only V <sub>DD</sub> available,<br>V <sub>BAT</sub> must be put to ground       | $V_{DD}$                                                 |

The output pin BBS can be used as a supply for external devices with battery backup needs, such as SRAM (see [1]).

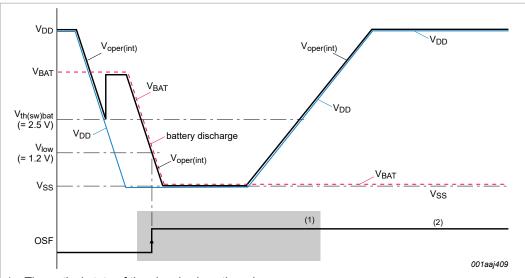

### 7.6 Oscillator stop detection function

The PCA2131 has an on-chip oscillator detection circuit which indicates the status of the oscillation by monitoring the supply of oscillator: whenever the supply is out of the expected range, a reset occurs and the oscillator stop flag OSF (in register Seconds) is set logic 1.

#### • Power-on:

- 1. The oscillator is not running, the chip is in reset (OSF is logic 1).

- 2. When the oscillator starts running and supply is OK after power-on, the chip exits from reset.

- 3. The flag OSF is still logic 1 and can be cleared (OSF set logic 0) by command.

#### • Power supply failure:

- 1. When the power supply of the chip drops below a certain value (V<sub>low</sub>), typically 1.2 V, the oscillator supply also fails and a reset occurs.

- 2. When the power supply returns to normal operation, the oscillator supply is OK again, the chip exits from reset.

- 3. The flag OSF is still logic 1 and can be cleared (OSF set logic 0) by command.

- 4. When OSF flag is cleared an OTP refresh should be performed (see Section 7.3.2).

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

- 1. Theoretical state of the signals since there is no power.

- 2. The oscillator stop flag (OSF), set logic 1, indicates that the oscillation has stopped and a reset has occurred since the flag was last cleared (OSF set logic 0). In this case, the integrity of the clock information is not guaranteed. The OSF flag is cleared by command.

Figure 8. Power failure event due to battery discharge: reset occurs

#### 7.7 Power-On Reset function

The PCA2131 has a Power-On Reset (POR) and a Power-On Reset Override (PORO) function implemented.

### 7.7.1 Power-On Reset (POR)

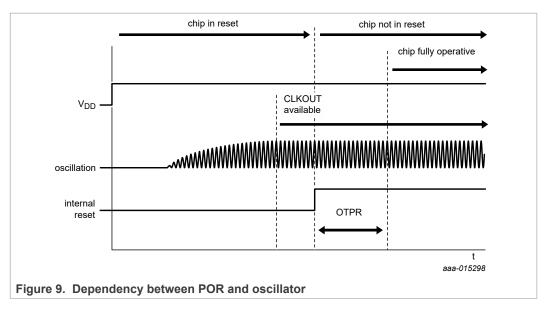

The POR is active whenever the oscillator is stopped. The oscillator is considered to be stopped during the time between power-on and stable crystal resonance (see <u>Figure 9</u>). This time may be in the range of 200 ms to 2 s depending on temperature and supply voltage. Whenever an internal reset occurs, the oscillator stop flag is set (OSF set logic 1).

The OTP refresh (see <u>Section 7.3.2</u>) should ideally be executed as the first instruction after start-up and also after a reset due to an oscillator stop.

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

After POR, the following mode is entered:

- 32.768 kHz CLKOUT active

- Power-On Reset Override (PORO) available to be set

- 24-hour mode is selected

- Battery switch-over function disabled, only one power supply (V<sub>DD</sub>)

- · Temperature compensation enabled

- · 100th second enabled

- Time 00:00:00.00

- Date 2001.01.01

- · Weekday Monday

The register values after power-on are shown in <u>Table 4</u>.

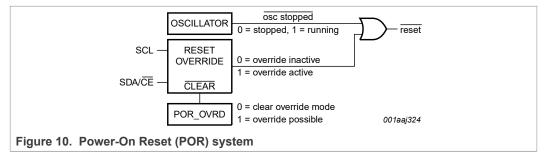

### 7.7.2 Power-On Reset Override (PORO)

The POR duration is directly related to the crystal oscillator start-up time. Due to the long start-up times experienced by these types of circuits, a mechanism has been built in to disable the POR and therefore speed up the on-board test of the device.

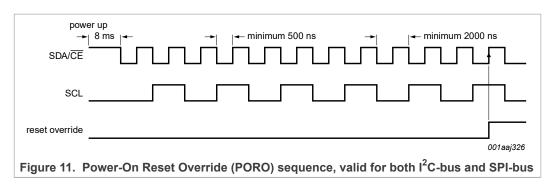

The setting of the PORO mode requires that POR\_OVRD in register Control\_1 is set logic 1 and that the signals at the interface pins SDA/CE and SCL are toggled as illustrated in Figure 11. All timings shown are required minimum.

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Once the override mode is entered, the device is immediately released from the reset state and the set-up operation can commence.

The PORO mode is cleared by writing logic 0 to POR\_OVRD. POR\_OVRD must be logic 1 before a re-entry into the override mode is possible. Setting POR\_OVRD logic 0 during normal operation has no effect except to prevent accidental entry into the PORO mode.

### 7.8 Software Reset register

Table 24. Reset - software reset control (address 05h) bit description

| Bit     | 7             | 6 | 5 | 4 | 3             | 2 | 1 | 0             |

|---------|---------------|---|---|---|---------------|---|---|---------------|

| Symbol  | CPR           | 0 | 1 | 0 | SR            | 1 | 0 | CTS           |

| Section | Section 7.8.2 |   |   |   | Section 7.8.1 |   |   | Section 7.8.3 |

То

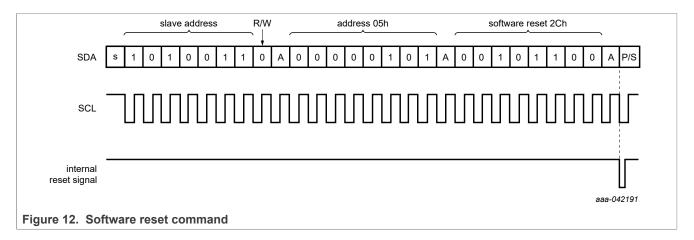

- trigger a software reset (SR), 0010 1100 (2Ch) must be sent to register Reset (address 05h). A software reset also triggers CPR and CTS

- clear prescaler (CPR), 1010 0100 (A4h) must be sent to register Reset (address 05h)

- clear timestamp (CTS), 0010 0101 (25h) must be sent to register Reset (address 05h)

It is possible to combine CPR and CTS by sending 1010 0101 (A5h).

Read of the SR RESET register will return a fixed pattern of 00100100;

Remark: Any other value sent to this register is ignored.

#### 7.8.1 SR - Software reset

A reset is automatically generated at power-on as Power-On Reset as described in Section 7.7. A reset can also be initiated with the software reset command.

After software reset, the following mode is entered:

- 32.768 kHz CLKOUT active

- Power-On Reset Override (PORO) unchanged

- OTP not reloaded, OTPR unchanged.

- 24-hour mode is selected

- Battery switch-over function disabled, only one power supply (V<sub>DD</sub>)

- Temperature compensation enabled

- · 100th second enabled

- Time 00:00:00.00

- Date 2001.01.01

PCA2131

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

### · Weekday Monday

### 7.8.2 CPR: clear prescaler

To set the time for RTC mode, the clear prescaler instruction is needed.

Before sending this instruction, it is mandatory to first set *stop* by the STOP bit.

See STOP definition for an explanation on using this instruction.

### 7.8.3 CTS: clear timestamp

The timestamp registers (address 14h to 2Fh) can be set to all 0 with this instruction.

#### 7.9 Time and date function

Most of these registers are coded in the Binary Coded Decimal (BCD) format.

### 7.9.1 Register 100th Seconds

Table 25. 100th Seconds - 100th seconds (address 06h) bit allocation

| Bit         | 7 | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------|---|-------------------------|---|---|---|---|---|---|--|

| Symbol      |   | 100TH SECONDS (0 to 99) |   |   |   |   |   |   |  |

| Reset value | 0 | 0                       | 0 | 0 | 0 | 0 | 0 | 0 |  |

Table 26. 100th Seconds - 100th seconds register (address 06h) bit description

| Bit    | Symbol        | Value  | Place value | Description                        |

|--------|---------------|--------|-------------|------------------------------------|

| 7 to 4 | 100TH SECONDS | 0 to 9 | ten's place | actual seconds coded in BCD format |

| 3 to 0 |               | 0 to 9 | unit place  |                                    |

Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 27. 100th Seconds coded in BCD format

| Seconds             | Upper-dig | jit (ten's pl | ace)  |       | Digit (unit place) |       |       |       |

|---------------------|-----------|---------------|-------|-------|--------------------|-------|-------|-------|

| value in<br>decimal | Bit 6     | Bit 6         | Bit 5 | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

| 00                  | 0         | 0             | 0     | 0     | 0                  | 0     | 0     | 0     |

| 01                  | 0         | 0             | 0     | 0     | 0                  | 0     | 0     | 1     |

| 02                  | 0         | 0             | 0     | 0     | 0                  | 0     | 1     | 0     |

| :                   | :         | :             | :     | :     | :                  | :     | :     | :     |

| 09                  | 0         | 0             | 0     | 0     | 1                  | 0     | 0     | 1     |

| 10                  | 0         | 0             | 0     | 1     | 0                  | 0     | 0     | 0     |

| :                   | :         | :             | :     | :     | :                  | :     | :     | :     |

| 98                  | 1         | 0             | 0     | 1     | 1                  | 0     | 0     | 0     |

| 99                  | 1         | 0             | 0     | 1     | 1                  | 0     | 0     | 1     |

### 7.9.2 Register Seconds

Table 28. Seconds - seconds and clock integrity register (address 07h) bit allocation

| Bit         | 7   | 6 | 5 | 4  | 3           | 2   | 1 | 0 |

|-------------|-----|---|---|----|-------------|-----|---|---|

| Symbol      | OSF |   |   | SE | CONDS (0 to | 59) |   |   |

| Reset value | 1   | 0 | 0 | 0  | 0           | 0   | 0 | 0 |

Table 29. Seconds - seconds and clock integrity register (address 07h) bit description

| Bit    | Symbol  | Value  | Place value | Description                                                                                                       |

|--------|---------|--------|-------------|-------------------------------------------------------------------------------------------------------------------|

| 7      | OSF     | 0      | -           | clock integrity is guaranteed                                                                                     |

|        |         | 1      | -           | clock integrity is not guaranteed: oscillator has stopped and chip reset has occurred since flag was last cleared |

| 6 to 4 | SECONDS | 0 to 5 | ten's place | actual seconds coded in BCD format                                                                                |

| 3 to 0 |         | 0 to 9 | unit place  |                                                                                                                   |

Table 30. Seconds coded in BCD format

| Seconds             | Upper-dig | Upper-digit (ten's place) |       |       | Digit (unit place) |       |       |  |  |

|---------------------|-----------|---------------------------|-------|-------|--------------------|-------|-------|--|--|

| value in<br>decimal | Bit 6     | Bit 5                     | Bit 4 | Bit 3 | Bit 2              | Bit 1 | Bit 0 |  |  |

| 00                  | 0         | 0                         | 0     | 0     | 0                  | 0     | 0     |  |  |

| 01                  | 0         | 0                         | 0     | 0     | 0                  | 0     | 1     |  |  |

| 02                  | 0         | 0                         | 0     | 0     | 0                  | 1     | 0     |  |  |

| :                   | :         | :                         | :     | :     | :                  | :     | :     |  |  |

| 09                  | 0         | 0                         | 0     | 1     | 0                  | 0     | 1     |  |  |

| 10                  | 0         | 0                         | 1     | 0     | 0                  | 0     | 0     |  |  |

PCA2131

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

### Nano-power highly accurate RTC with integrated quartz crystal for automotive applications

Table 30. Seconds coded in BCD format...continued

| Seconds             | Upper-digi | t (ten's plac | e)    | Digit (unit place) |       |       |       |

|---------------------|------------|---------------|-------|--------------------|-------|-------|-------|

| value in<br>decimal | Bit 6      | Bit 5         | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

| :                   | :          | :             |       | :                  | :     | :     | :     |

| 58                  | 1          | 0             | 1     | 1                  | 0     | 0     | 0     |

| 59                  | 1          | 0             | 1     | 1                  | 0     | 0     | 1     |

### 7.9.3 Register Minutes

Table 31. Minutes - minutes register (address 08h) bit allocation Bits labeled as T are unused and return 0 when read

| Bit         | 7 | 6 | 5                 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|-------------------|---|---|---|---|---|

| Symbol      | Т |   | MINUTES (0 to 59) |   |   |   |   |   |

| Reset value | 0 | 0 | 0                 | 0 | 0 | 0 | 0 | 0 |

Table 32. Minutes - minutes register (address 08h) bit description Bits labeled as T are unused and return 0 when read

| Bit    | Symbol  | Value  | Place value | Description                        |

|--------|---------|--------|-------------|------------------------------------|

| 7      | Т       | 0      | -           | unused                             |

| 6 to 4 | MINUTES | 0 to 5 | ten's place | actual minutes coded in BCD format |

| 3 to 0 |         | 0 to 9 | unit place  |                                    |

### 7.9.4 Register Hours

Table 33. Hours - hours register (address 09h) bit allocation Bits labeled as T are unused and return 0 when read

| Bit         | 7 | 6 | 5                                    | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|--------------------------------------|---|---|---|---|---|

| Symbol      | Т | T | AMPM HOURS (1 to 12) in 12-hour mode |   |   |   |   |   |

|             |   |   | HOURS (0 0to 23) in 24-hour mode     |   |   |   |   |   |

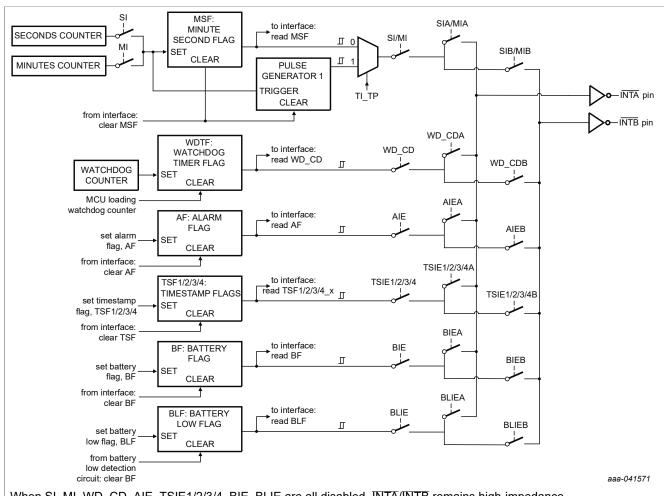

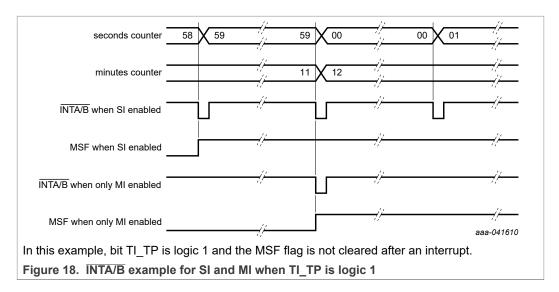

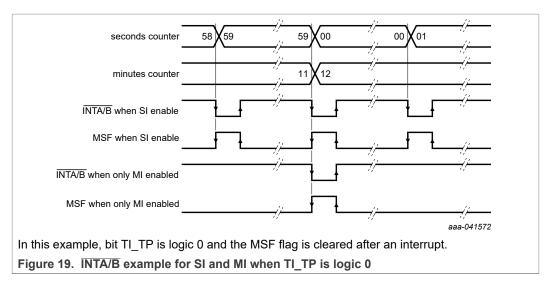

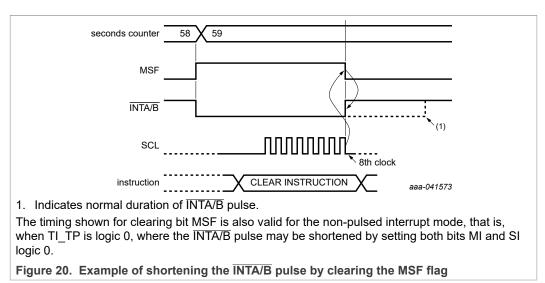

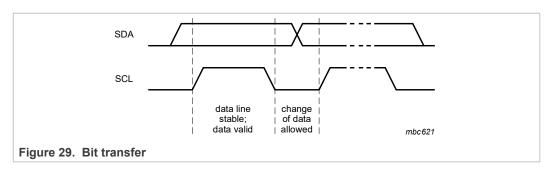

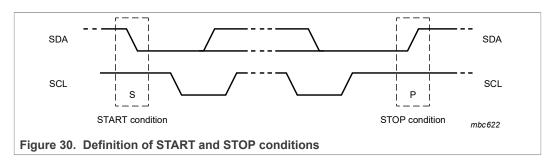

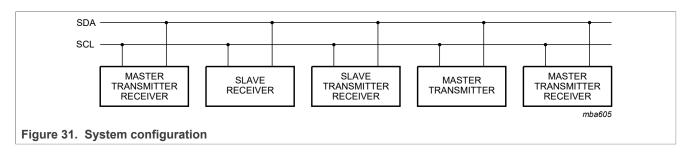

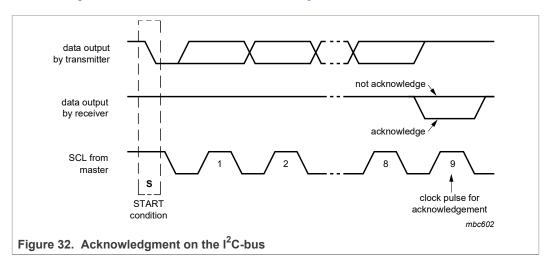

| Reset value | 0 | 0 | 0                                    | 0 | 0 | 0 | 0 | 0 |