SNAS744A - JULY 2017-REVISED OCTOBER 2017

LMS3655

# LMS3655 5.5-A, 36-V Synchronous, 400-kHz DC-DC Step-Down Converter

#### **Features**

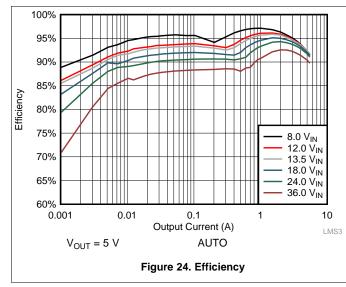

- 96% Peak Efficiency While Converting 12 V to 5 V

- Low EMI and Switch Noise

- Minimized Switch Node Ringing

- Pseudo-Random Spread Spectrum

- 400-kHz (±10%) Fixed Switching Frequency

- -40°C to +150°C Junction Temperature Range

- **External Frequency Synchronization**

- **RESET** Output With Internal Filter and 3-ms Release Timer

- Automatic Light Load Mode for Improved Efficiency

- Pin-Selectable Forced PWM Mode

- Built-In Compensation, Soft Start, Current Limit, Thermal Shutdown, and UVLO

- 0.35-V Dropout With 3.5-A Load at 25°C (Typical)

- 32-µA I<sub>O VIN</sub>: Quiescent Current at 3.3 V<sub>OUT</sub> and No Load (Typical)

- 5.5-A Continuous Load Current

- Adjustable Output Voltage (1 V to 15 V)

- ±1.5% Reference Voltage Tolerance

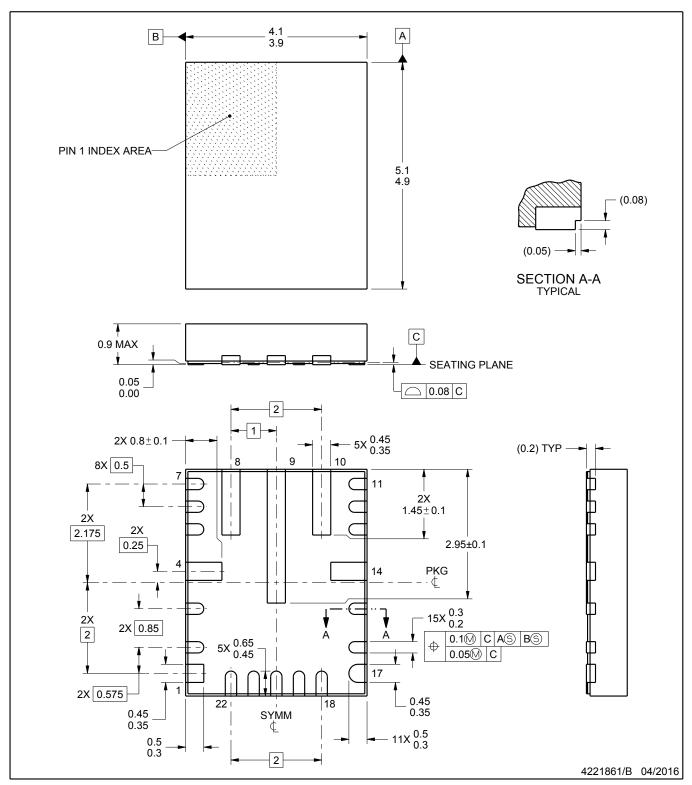

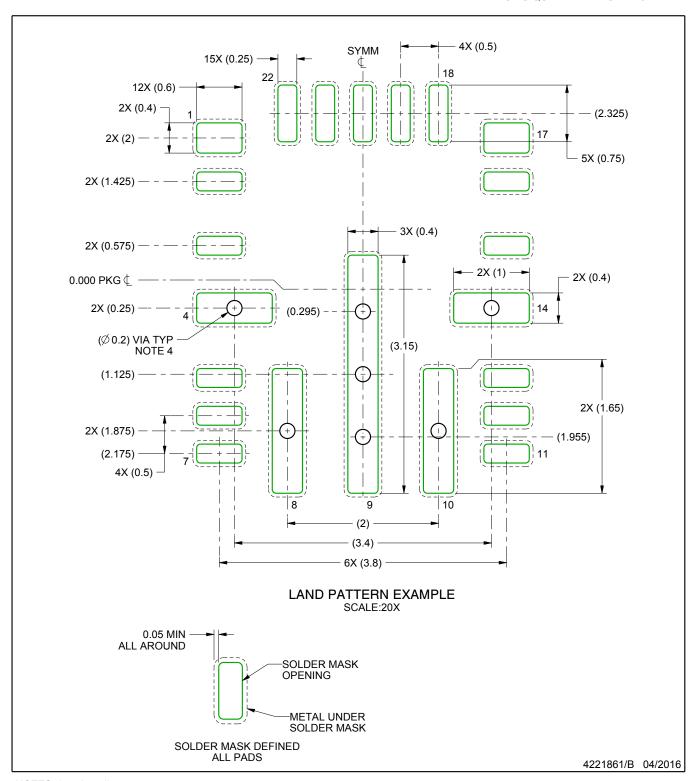

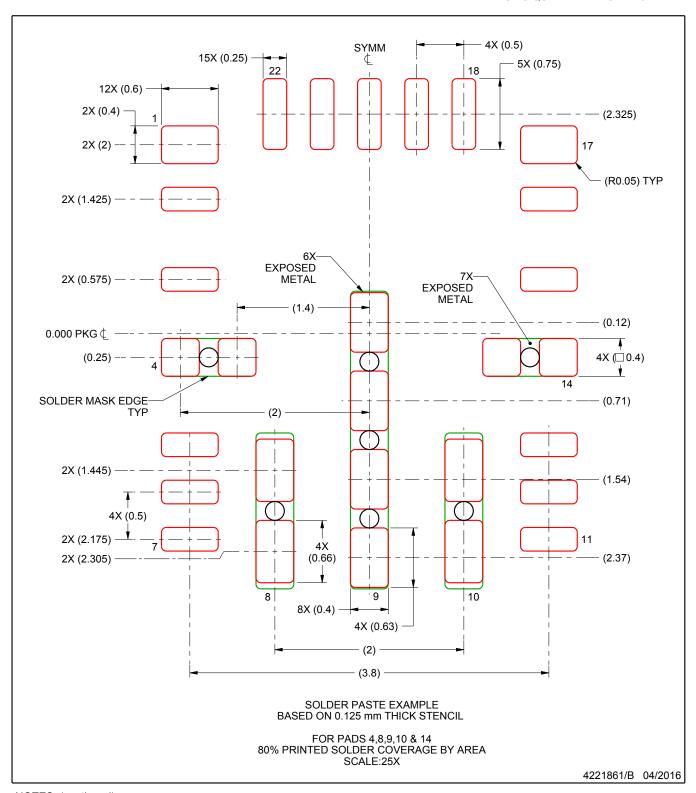

- 4-mm x 5-mm, 0.5-mm Pitch SON Package

### **Applications**

- **Noise-Sensitive Medical Applications**

- Telecom

- High Performance Industrial

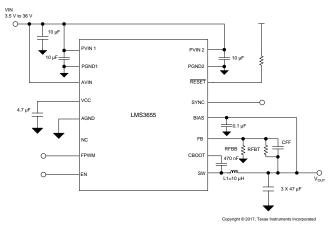

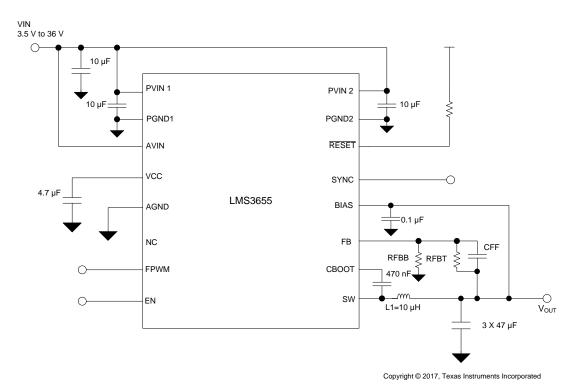

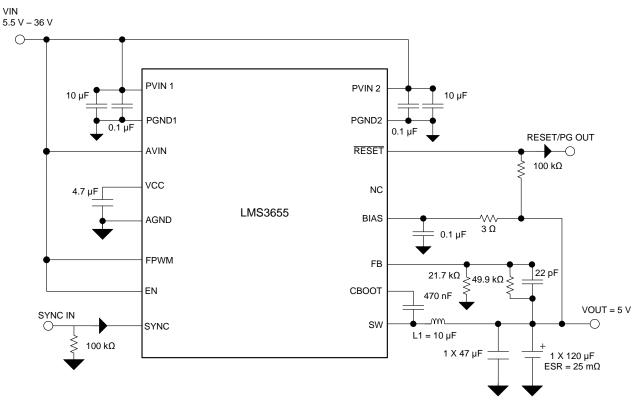

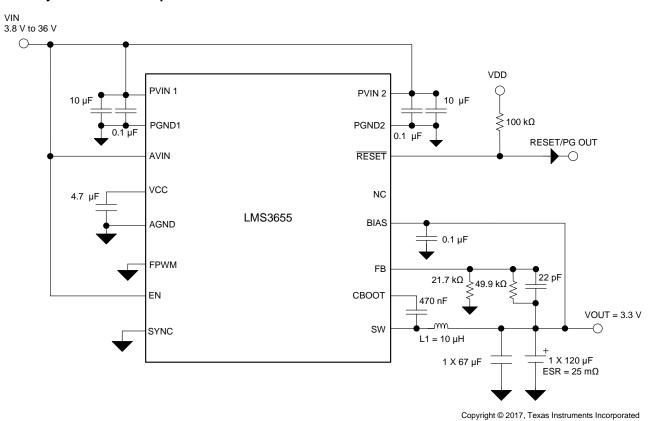

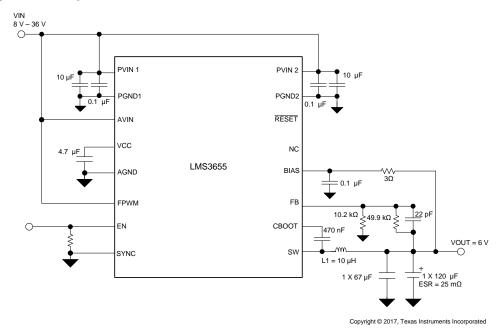

#### **Typical Application Circuit**

#### 3 Description

The LMS3655 synchronous buck regulators are high performance applications, optimized for providing an adjustable output of 1 V to 15 V. Seamless transition between PWM and PFM modes, along with a low quiescent current, ensures high efficiency and superior transient responses at all loads.

Advanced high-speed circuitry allows the LMS3655 to regulate an input of 24 V to an output of 3.3 V at a fixed frequency of 400 kHz while also enabling a continuous load current of 5.5 A. An innovative frequency foldback architecture allows this device to regulate a 3.3-V output from an input voltage of only 3.5 V. The input voltage can range up to 36 V, with transient tolerance up to 42 V, easing input surge protection design.

An open-drain reset output, with built-in filtering and delay, provides a true indication of system status. This feature negates the requirement for an additional supervisory component, saving cost and board space.

#### Device Information<sup>(1)</sup>

| DEVICE NAME | PACKAGE      | BODY SIZE         |

|-------------|--------------|-------------------|

| LMS3655     | VQFN-HR (22) | 4.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

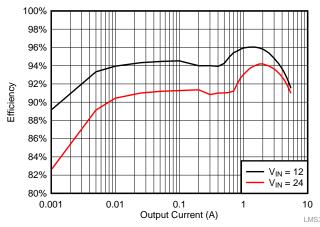

#### LMS3655 Efficiency: $V_{OUT} = 5 \text{ V}$

# **Table of Contents**

| 1 | Features 1                                            |    | 8.3 Feature Description                             | 14                 |

|---|-------------------------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 | Applications 1                                        |    | 8.4 Device Functional Modes                         | 19                 |

| 3 | Description 1                                         | 9  | Application and Implementation                      | 23                 |

| 4 | Revision History2                                     |    | 9.1 Application Information                         | 23                 |

| 5 | Device Comparison Table3                              |    | 9.2 Typical Applications                            | 23                 |

| 6 | Pin Configuration and Functions 4                     |    | 9.3 Do's and Don't's                                | 40                 |

| 7 | Specifications5                                       | 10 | Power Supply Recommendations                        | 40                 |

| • | 7.1 Absolute Maximum Ratings                          | 11 | Layout                                              | 40                 |

|   | 7.2 ESD Ratings                                       |    | 11.1 Layout Guidelines                              | 40                 |

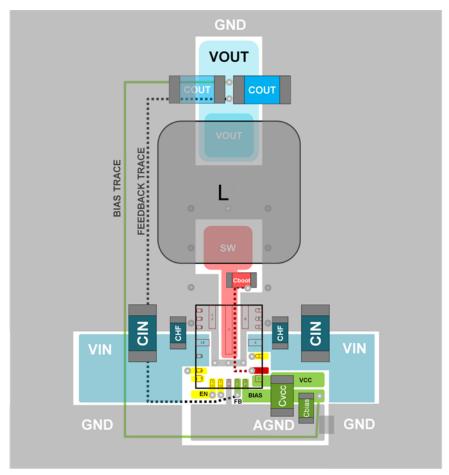

|   | 7.3 Recommended Operating Conditions                  |    | 11.2 Layout Example                                 | 42                 |

|   | 7.4 Thermal Information                               | 12 | Device and Documentation Support                    | 43                 |

|   | 7.5 Thermal Information (for Device Mounted on PCB) 6 |    | 12.1 Device Support                                 | 43                 |

|   | 7.6 Electrical Characteristics                        |    | 12.2 Documentation Support                          | 43                 |

|   | 7.7 System Characteristics 8                          |    | 12.3 Receiving Notification of Documentation Update | es <mark>43</mark> |

|   | 7.8 Timing Requirements                               |    | 12.4 Community Resources                            | 43                 |

|   | 7.9 Typical Characteristics                           |    | 12.5 Trademarks                                     | 43                 |

| 8 | Detailed Description 12                               |    | 12.6 Electrostatic Discharge Caution                | 43                 |

| • | 8.1 Overview                                          |    | 12.7 Glossary                                       | 43                 |

|   | 8.2 Functional Block Diagram                          | 13 | Mechanical, Packaging, and Orderable Information    | 44                 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Original (July 2017) to Revision A                                | Page |

|----|-------------------------------------------------------------------------------|------|

| •  | Changed symbol from: I <sub>B</sub> to: I <sub>B_NSW</sub>                    | 6    |

| •  | Added I <sub>B</sub> spec to System Characteristics                           | 8    |

| •  | Added System Characteristics crossreference links for the I <sub>B</sub> spec | 18   |

# 5 Device Comparison Table

Table 1. LMS3655 Devices (5.5-A Output)

| PART NUMBER   | OUTPUT VOLTAGE | SPREAD<br>SPECTRUM | PACKAGE QTY |

|---------------|----------------|--------------------|-------------|

| LMS3655AMRNLR | Adjustable     | No                 | 3000        |

| LMS3655AMRNLT | Adjustable     | No                 | 250         |

| LMS3655MMRNLR | Adjustable     | Yes                | 3000        |

| LMS3655MMRNLT | Adjustable     | Yes                | 250         |

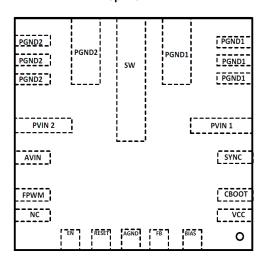

# 6 Pin Configuration and Functions

#### RNL Package 22-Pin VQFN Top View

#### **Pin Functions**

|     | PIN   | -x(1)               |                                                                                                                                                                                                             |  |  |  |

|-----|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME  | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                 |  |  |  |

| 1   | VCC   | А                   | Internal 3.1-V LDO output. Used as supply to internal control circuits. Connect a high-quality 4.7-μF capacitor from this pin to AGND.                                                                      |  |  |  |

| 2   | СВООТ | Р                   | Bootstrap capacitor connection for gate drivers. Connect a high quality 470-nF capacitor from this pin to the SW pin.                                                                                       |  |  |  |

| 3   | SYNC  | I                   | Synchronization input to regulator. Used to synchronize the device switching frequency to a system clock. Triggers on rising edge of external clock; frequency must be in the range of 250 kHz and 500 kHz. |  |  |  |

| 4   | PVIN1 | Р                   | out supply to regulator. Connect input bypass capacitors directly to this pin and PGND pins. Connect /IN1 and PVIN2 pins directly together at PCB.                                                          |  |  |  |

| 5   |       |                     |                                                                                                                                                                                                             |  |  |  |

| 6   | DCND4 | G                   | Power ground to internal low-side MOSFET. These pins must be tied together on the PCB. Connect                                                                                                              |  |  |  |

| 7   | PGND1 |                     | PGND1 and PGND2 directly together at PCB. Connect to AGND and system ground.                                                                                                                                |  |  |  |

| 8   |       |                     |                                                                                                                                                                                                             |  |  |  |

| 9   | SW    | Р                   | Regulator switch node. Connect to power inductor.                                                                                                                                                           |  |  |  |

| 10  |       |                     |                                                                                                                                                                                                             |  |  |  |

| 11  | PGND2 | G                   | Power ground to internal low-side MOSFET. These pins must be tied together. Connect PGND1 and                                                                                                               |  |  |  |

| 12  | PGND2 | GND2 G              | PGND2 directly together at PCB. Connect to AGND and system ground.                                                                                                                                          |  |  |  |

| 13  |       |                     |                                                                                                                                                                                                             |  |  |  |

| 14  | PVIN2 | Р                   | Input supply to regulator. Connect input bypass capacitors directly to this pin and PGND pins. Connect PVIN1 and PVIN2 pins directly together at PCB.                                                       |  |  |  |

| 15  | AVIN  | А                   | Analog VIN. Connect to PVIN1 and PVIN2 on PCB.                                                                                                                                                              |  |  |  |

| 16  | FPWM  | I                   | Mode control input of regulator. High = FPWM, low = Automatic light load mode. Do not float.                                                                                                                |  |  |  |

| 17  | NC    | _                   | No internal connection.                                                                                                                                                                                     |  |  |  |

| 18  | EN    | 1                   | Enable input to regulator. High = on, Low = off. Can be connected to VIN. Do not float.                                                                                                                     |  |  |  |

| 19  | RESET | 0                   | Open-drain reset output flag. Connect to suitable voltage supply through a current limiting resistor. High = regulator OK, Low = regulator fault. Goes low when EN = low.                                   |  |  |  |

| 20  | AGND  | G                   | Analog ground for regulator and system. All electrical parameters are measured with respect to this pin. Connect to PGND on PCB.                                                                            |  |  |  |

| 21  | FB    | А                   | Feedback input to regulator. Connect to feedback voltage divider.                                                                                                                                           |  |  |  |

| 22  | BIAS  | Р                   | Input to auxiliary bias regulator. Connect to output voltage node.                                                                                                                                          |  |  |  |

(1) A = Analog, O = Output, I = Input, G = Ground, P = Power

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to +150°C (unless otherwise noted). (1)

| PARAMETER                                                 | MIN  | MAX                   | UNIT |

|-----------------------------------------------------------|------|-----------------------|------|

| VIN (AVIN, PVIN1, and PVIN2) to AGND, PGND <sup>(2)</sup> | -0.3 | 40                    | V    |

| SW to AGND, PGND <sup>(3)</sup>                           | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| CBOOT to SW                                               | -0.3 | 3.6                   | V    |

| EN to AGND, PGND <sup>(2)</sup>                           | -0.3 | 40                    | V    |

| BIAS to AGND, PGND                                        | -0.3 | 16                    | V    |

| FB to AGND, PGND                                          | -0.3 | 16                    | V    |

| RESET to AGND, PGND                                       | -0.3 | 8                     | V    |

| RESET sink current <sup>(4)</sup>                         |      | 10                    | mA   |

| SYNC to AGND, PGND <sup>(2)</sup>                         | -0.3 | 40                    | V    |

| FPWM to AGND, PGND <sup>(2)</sup>                         | -0.3 | 40                    | V    |

| VCC to AGND, PGND                                         | -0.3 | 3.6                   | V    |

| Junction temperature                                      | -40  | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>                     | -40  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT  |

|--------------------|---------------|---------------------------------------------------------------------|-------|-------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | V     |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V<br> |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to +150°C (unless otherwise noted).

|                                                       | MIN | NOM MAX | UNIT |

|-------------------------------------------------------|-----|---------|------|

| Input voltage after start-up <sup>(1)</sup>           | 3.9 | 36      | V    |

| Output adjustment for LMS3655 <sup>(2)</sup>          | 3.3 | 6       | V    |

| Extended output adjustment for LMS3655 <sup>(3)</sup> | 1   | 15      | V    |

| Load current for LMS3655                              |     | 5.5     | Α    |

| Operating ambient temperature <sup>(4)</sup>          | -40 | 125     | °C   |

<sup>(1)</sup> An extended input voltage range to 3.5 V is possible; see System Characteristics table. See Input UVLO for start-up conditions.

(4) High junction temperatures degrade operating lifetime.

<sup>(2)</sup> A maximum of 42 V can be sustained at this pin for a duration of ≤ 500 ms at a duty cycle of ≤ 0.01%.

<sup>(3)</sup> A voltage of 2 V below PGND and 2 V above VIN can appear on this pin for ≤ 200 ns with a duty cycle of ≤ 0.01%.

<sup>(4)</sup> Do not exceed the voltage rating on this pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The output voltage must not be allowed to fall below zero volts during normal operation.

<sup>(3)</sup> Operation below 3.3 V and above 6 V may require changes to the typical application schematic, operation may not be possible over the full input voltage range, and some system specifications will not be achieved for this extended output voltage range. Consult the factory for further information.

#### 7.4 Thermal Information

|                        |                                              | LMS3655    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RNL (VQFN) | UNIT |

|                        |                                              | 22 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 38.5       | °C/W |

| $R_{\theta JC}$        | Junction-to-case (top) thermal resistance    | 16.3       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 16.4       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 2.0        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 16.4       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4.6        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Thermal Information (for Device Mounted on PCB)

|                      |                                              | LMS3655                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | THERMAL METRIC <sup>(1)</sup> RNL (VQFN)  22 PINS  on-to-ambient thermal resistance  on-to-case (top) thermal resistance  on-to-board thermal resistance  on-to-board thermal resistance  on-to-top characterization parameter  1.2  occurrence  very construction of the construct | UNIT |

|                      |                                              | 22 PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 29.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | °C/W |

| $R_{\theta JC}$      | Junction-to-case (top) thermal resistance    | 14.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | °C/W |

<sup>(1)</sup> Mounted on a thermally optimized FR4 four layer EVM with a size of 4000 mill x 3000 mill.

#### 7.6 Electrical Characteristics

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                         | PARAMETER                                                                                            | TEST CONDITIONS                                                                                             | MIN   | TYP  | MAX   | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V                       | Initial reference voltage for 5-V                                                                    | $V_{IN} = 3.8 \text{ V to } 36 \text{ V}, T_J = 25^{\circ}\text{C}$                                         | -1%   |      | 1%    |      |

| $V_{FB}$                | and 3.3-V options                                                                                    | V <sub>IN</sub> = 3.8 V to 36 V                                                                             | -1.5% |      | 1.5%  |      |

| IQ                      | Operating quiescent current;<br>measured at VIN pin when<br>enabled and not switching <sup>(1)</sup> | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 5 V                                                           |       | 7.5  | 16    | μΑ   |

|                         | Bias current into BIAS pin,                                                                          | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 5 V, FPWM = 0 V                                               |       | 53   | 62    | μA   |

| I <sub>B_NSW</sub>      | enabled, not switching                                                                               | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 3.3 V, FPWM<br>= 0 V                                          |       | 53   | 62    |      |

| I <sub>SD</sub>         | Shutdown quiescent current; measured at VIN pin                                                      | EN ≤ 0.4 V                                                                                                  |       | 2    | 3     | μΑ   |

|                         |                                                                                                      | Rising                                                                                                      | 3.2   | 3.55 | 3.90  |      |

| V <sub>IN-OPERATE</sub> | Minimum input voltage to operate                                                                     | Falling                                                                                                     | 2.95  | 3.25 | 3.55  | V    |

|                         |                                                                                                      | Hysteresis                                                                                                  | 0.28  | 0.3  | 0.4   |      |

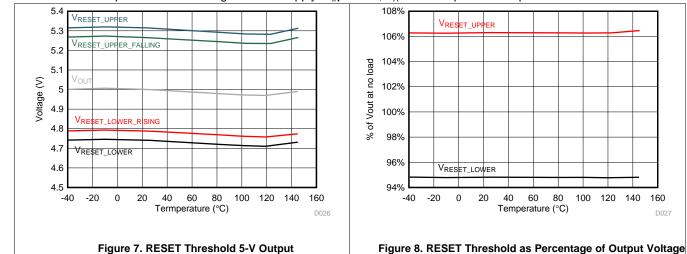

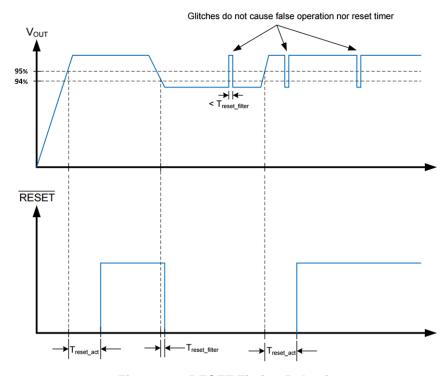

|                         | RESET upper threshold voltage                                                                        | Rising, % of V <sub>OUT</sub>                                                                               | 105%  | 107% | 110%  |      |

|                         | RESET lower threshold voltage                                                                        | Falling, % V <sub>OUT</sub>                                                                                 | 92%   | 94%  | 96.5% |      |

| V <sub>RESET</sub>      | Magnitude of RESET lower threshold from steady state output voltage                                  | Steady-state output voltage and RESET falling threshold read at the same T <sub>J</sub> and V <sub>IN</sub> |       |      | 96%   |      |

<sup>(1)</sup> This is the current used by the device while not switching, open loop on the ATE. It does not represent the total input current from the regulator system.

#### **Electrical Characteristics (continued)**

Limits apply over the recommended operating junction temperature range of -40°C to +150°C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at T<sub>J</sub> = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                                     | PARAMETER                                                | TEST CONDITIONS                                                                       | MIN  | TYP   | MAX  | UNIT  |

|-------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|------|-------|------|-------|

| V <sub>RESET_HYST</sub>             | RESET hysteresis as a percent of output voltage setpoint |                                                                                       |      | ±1%   |      |       |

| V <sub>RESET_VALID</sub>            | Minimum input voltage for proper RESET function          | 50- $\mu$ A pullup to RESET pin,<br>EN = 0 V, T <sub>J</sub> = 25°C                   |      |       | 1.5  | V     |

|                                     |                                                          | 50- $\mu$ A pullup to RESET pin,<br>V <sub>IN</sub> = 1.5 V, EN = 0 V                 |      |       | 0.4  |       |

| V <sub>OL</sub>                     | Low level RESET function output voltage                  | 0.5-mA pullup to $\overline{\text{RESET}}$ pin,<br>V <sub>IN</sub> = 13.5 V, EN = 0 V |      |       | 0.4  | V     |

|                                     |                                                          | 1-mA pullup to $\overline{RESET}$ pin,<br>V <sub>IN</sub> = 13.5 V, EN = 3.3 V        |      |       | 0.4  |       |

| F <sub>SW</sub> Switching frequency | Switching frequency                                      | V <sub>IN</sub> = 13.5 V, center frequency with spread spectrum, PWM operation        | 360  | 400   | 440  | kHz   |

|                                     | Contoning inequality                                     | V <sub>IN</sub> = 13.5 V, without spread spectrum, PWM operation                      | 360  | 400   | 440  | KIIZ  |

| F <sub>SYNC</sub>                   | Sync frequency range                                     |                                                                                       | 250  | 400   | 500  | kHz   |

| D <sub>SYNC</sub>                   | Sync input duty cycle range                              | High state input < 5.5 V and > 2.3 V                                                  | 25%  |       | 75%  |       |

|                                     |                                                          | FPWM input high (MODE = FPWM)                                                         | 1.5  |       |      |       |

| $V_{FPWM}$                          | FPWM input threshold voltage                             | FPWM input low (MODE = AUTO with diode emulation)                                     |      |       | 0.4  | V     |

|                                     |                                                          | FPWM input hysteresis                                                                 | 0.15 |       | 1    |       |

| FS <sub>SS</sub>                    | Frequency span of spread spectrum operation              |                                                                                       |      | ±3%   |      |       |

| F <sub>PSS</sub>                    | Spread-spectrum pattern frequency (2)                    |                                                                                       |      |       | 1.2  | Hz    |

| I <sub>FPWM</sub>                   | FPWM leakage current                                     | V <sub>IN</sub> = 13.5 V, V <sub>FPWM</sub> = 3.3 V                                   |      | 1     |      | μA    |

| 'FPWW                               |                                                          | $V_{IN} = V_{FPWM} = 13.5 \text{ V}$                                                  |      | 1     |      | μΛ    |

| I <sub>SYNC</sub>                   | SYNC leakage current                                     | V <sub>IN</sub> = 13.5 V, V <sub>SYNC</sub> = 3.3 V                                   |      | 1     |      | μΑ    |

| STING                               | OTTO loakago ourroin                                     | $V_{IN} = V_{SYNC} = 13.5 \text{ V}$                                                  |      | 1     |      | μ, ,  |

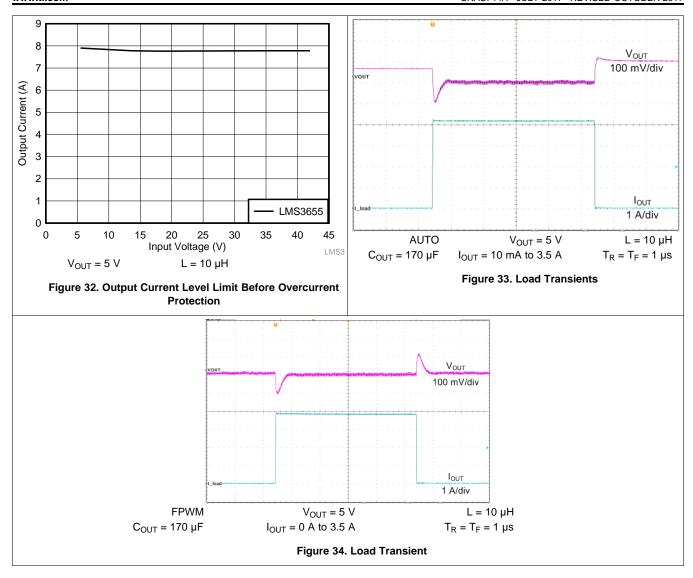

| I <sub>L-HS</sub>                   | High-side switch current limit                           | LMS3655                                                                               | 6.7  | 8.5   | 9.5  | Α     |

| I <sub>L-LS</sub>                   | Low-side switch current limit                            | LMS3655                                                                               | 6    | 7     | 7.7  | Α     |

| I <sub>L-ZC</sub>                   | Zero-cross current limit FPWM = low                      |                                                                                       |      | -0.02 |      | Α     |

| I <sub>L-NEG</sub>                  | Negative current limit FPWM = high                       |                                                                                       |      | -1.5  |      | ^     |

| R <sub>DSON</sub>                   | Power switch on-resistance                               | High-side MOSFET R <sub>DSON</sub> ,<br>V <sub>IN</sub> = 13 V, IL = 1 A              |      | 60    | 130  | mΩ    |

| NDSON                               | Tower switch of resistance                               | Low-side MOSFET $R_{DSON}$ , $V_{IN} = 13 \text{ V}$ , $IL = 1 \text{ A}$             |      | 40    | 80   | 11122 |

| V <sub>EN</sub>                     | Enable input threshold voltage - rising                  | Enable rising                                                                         | 1.7  |       | 2    | V     |

| V <sub>EN_HYST</sub>                | Enable threshold hysteresis                              |                                                                                       | 0.45 |       | 0.55 | V     |

| V <sub>EN_WAKE</sub>                | Enable wake-up threshold                                 |                                                                                       | 0.4  |       |      | V     |

| I <sub>EN</sub>                     | EN pin input current                                     | V <sub>IN</sub> = V <sub>EN</sub> = 13.5 V                                            |      | 2     | 3    | μΑ    |

| V <sub>CC</sub>                     | Internal V <sub>CC</sub> voltage                         | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 0 V                                     |      | 3.05  |      | V     |

| v CC                                | internal vec voltage                                     | V <sub>IN</sub> = 13.5 V, V <sub>BIAS</sub> = 3.3 V                                   |      | 3.15  |      | V     |

| V                                   | Internal V <sub>CC</sub> input undervoltage              | V <sub>IN</sub> rising                                                                |      | 2.7   |      | V     |

| V <sub>CC_UVLO</sub>                | lockout                                                  | Hysteresis below V <sub>CC-UVLO</sub>                                                 |      | 185   |      | mV    |

Product Folder Links: LMS3655

(2) Ensured by Design, Not tested at production.

Submit Documentation Feedback

#### **Electrical Characteristics (continued)**

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                    | PARAMETER                          | TEST CONDITIONS                                               | MIN       | TYP | MAX   | UNIT |

|--------------------|------------------------------------|---------------------------------------------------------------|-----------|-----|-------|------|

| $I_{FB}$           | Input current from FB to AGND      | FB = 1 V                                                      |           | 20  |       | nA   |

| .,                 | Poforonos voltago                  | $T_J = 25$ °C                                                 | 5°C 0.993 | 1   | 1.007 | V    |

| VREF               | V <sub>REF</sub> Reference voltage | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | 0.99      | 1   | 1.01  |      |

| R <sub>RESET</sub> | R <sub>DSON</sub> of RESEToutput   | Pull FB pin low. Sink 1-mA at RESET pin                       |           | 50  | 120   | Ω    |

|                    | V <sub>IH</sub>                    |                                                               | 1.5       |     |       |      |

| $V_{SYNC}$         | $V_{IL}$                           |                                                               |           |     | 0.4   | V    |

|                    | V <sub>HYST</sub>                  |                                                               | 0.15      |     | 1     |      |

| _                  | Thermal shutdown thresholds (2)    | Rising                                                        | 160       |     | 185   | °C   |

| $T_{SD}$           | Thermal shutdown thresholds (=)    | Hysteresis                                                    |           | 15  |       | 10   |

| D <sub>MAX</sub>   | Manipular quitale dute quala       | F <sub>sw</sub> = 400 kHz                                     |           | 96% |       |      |

|                    | Maximum switch duty cycle          | While in dropout <sup>(2)</sup>                               | 98%       |     |       |      |

#### 7.7 System Characteristics

The following specifications are ensured by design provided that the component values in the typical application circuit are used. These parameters are not ensured by production testing. Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $+150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                     | PARAMETER                                                                                                    | TEST CONDITIONS                                                                                                             | MIN    | TYP  | MAX   | UNIT |

|---------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|------|-------|------|

| V                   | Minimum input voltage for full functionality at 3.5-A load, after start-up.                                  | V <sub>OUT</sub> = 3.3 V +2% or –3% regulation                                                                              |        | 3.5  |       | V    |

| V <sub>IN-MIN</sub> | Minimum input voltage for full functionality at maximum rated load 5.5 A after start-up.                     | V <sub>OUT</sub> = 3.3 V +2% or –3% regulation                                                                              |        | 3.8  |       | V    |

| V <sub>OUT</sub>    | Output voltage                                                                                               | V <sub>IN</sub> = V <sub>OUT</sub> + 1 V to 36 V, I <sub>OUT</sub> = 3.5 A                                                  | -2.25% |      | 2.25% |      |

| F <sub>SW</sub>     | Switching frequency                                                                                          | $V_{\text{IN}}$ = 24 V, FPWM = 24V, $V_{\text{OUT}}$ = 3.3 V, $I_{\text{OUT}}$ = 200 mA                                     |        | 400  |       | kHz  |

|                     | Input ourrent to VIN nin                                                                                     | $\begin{array}{l} V_{IN}=13.5~V,~V_{OUT}=3.3~V,~I_{OUT}=0~A~,\\ FPWM=0,~RFBT=49.9~k\Omega,~RFBB=21.7\\ k\Omega \end{array}$ | 32     |      |       |      |

| I <sub>Q_VIN</sub>  | Input current to VIN pin                                                                                     | $\begin{array}{l} V_{IN}=13.5~V,~V_{OUT}=5.0~V,~I_{OUT}=0~A,\\ FPWM=0,~RFBT=49.9~k\Omega,~RFBB=12.4\\ k\Omega \end{array}$  |        | 57   |       | μА   |

| I <sub>B</sub>      | Bias current in AUTO mode at no load                                                                         | V <sub>IN</sub> = 13.5 V, I <sub>OUT</sub> = 0 A, FPWM = 0                                                                  |        | 32   | 42    | μΑ   |

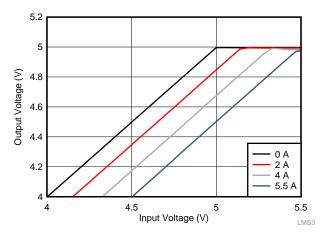

|                     | Minimum input to output voltage differential to                                                              | V <sub>OUT</sub> = 3.3 V or 5 V, I <sub>OUT</sub> = 3.5 A, +2% or –3% output accuracy                                       | 0.35   | 0.6  | V     |      |

| V <sub>DROP1</sub>  | maintain regulation accuracy without inductor<br>DCR drop                                                    | V <sub>OUT</sub> = 3.3 V or 5 V, I <sub>OUT</sub> = 5.5 A, +2% or –3% output accuracy                                       |        | 0.65 | 0.85  | V    |

| V                   | Minimum input to output voltage differential to maintain F <sub>SW</sub> ≥ 330 kHz without inductor DCR drop | $V_{OUT}$ = 3.3 V or 5 V, $I_{OUT}$ = 3.5 A, $F_{SW}$ = 330 kHz, 2% regulation accuracy                                     |        | 0.5  | 0.7   | V    |

| V <sub>DROP2</sub>  |                                                                                                              | $V_{OUT}$ = 3.3 V or 5 V, $I_{OUT}$ = 5.5 A, $F_{SW}$ = 330 kHz, 2% regulation accuracy                                     |        | 0.7  | 1.2   | V    |

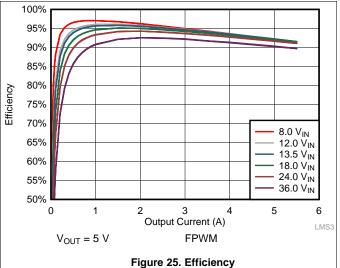

|                     |                                                                                                              | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 3.5 A                                                  |        | 94%  |       |      |

| Efficiency          | Typical efficiency                                                                                           | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 3.5 A                                                |        | 92%  |       |      |

|                     |                                                                                                              | V <sub>IN</sub> = 13.5 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 100 mA                                                 |        | 92%  |       |      |

#### 7.8 Timing Requirements

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to +150°C, unless otherwise noted. Minimum and maximum limits are ensured through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 \text{ V}$ .

|                           |                                                                                     | MIN | NOM | MAX | UNIT |

|---------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>ON</sub>           | Minimum switch on-time, V <sub>IN</sub> = 18 V, I <sub>L</sub> = 1 A                |     | 60  | 84  | ns   |

| t <sub>OFF</sub>          | Minimum switch off-time, $V_{IN} = 3.8 \text{ V}$ , $I_L = 1 \text{ A}$             |     | 65  | 80  | ns   |

| t <sub>RESET-act</sub>    | Delay time to RESET high signal                                                     | 2   | 3   | 4   | ms   |

| t <sub>RESET-filter</sub> | Glitch filter time for RESET function <sup>(1)</sup>                                |     | 24  |     | μs   |

| t <sub>SS</sub>           | Soft-start time from first switching pulse to V <sub>REF</sub> at 90%               | 2.5 | 4   | 5   | ms   |

| t <sub>EN</sub>           | Turnon delay, $C_{VCC} = 4.7 \mu F^{(2)}$                                           |     | 0.8 |     | ms   |

| t <sub>W</sub>            | Short-circuit wait time (hiccup time)(3)                                            |     | 6   |     | ms   |

| t <sub>FPWM</sub>         | Change transition time from AUTO to FPWM MODE, 10-mA load, $V_{\rm IN}$ = 13.5 V    |     | 250 |     |      |

|                           | Change transition time from FPWM to AUTO MODE, 10-mA load, V <sub>IN</sub> = 13.5 V |     | 450 |     | μs   |

<sup>(1)</sup> See Detailed Description.

<sup>(2)</sup> This is the time from the rising edge of EN to the time that the soft-start ramp begins.

<sup>(3)</sup> T<sub>w</sub> is the wait time between current limit trip and restart. T<sub>w</sub> is proportional to the soft-start time. However, provision must be made to make T<sub>w</sub> longer to ensure survivability during an output short circuit.

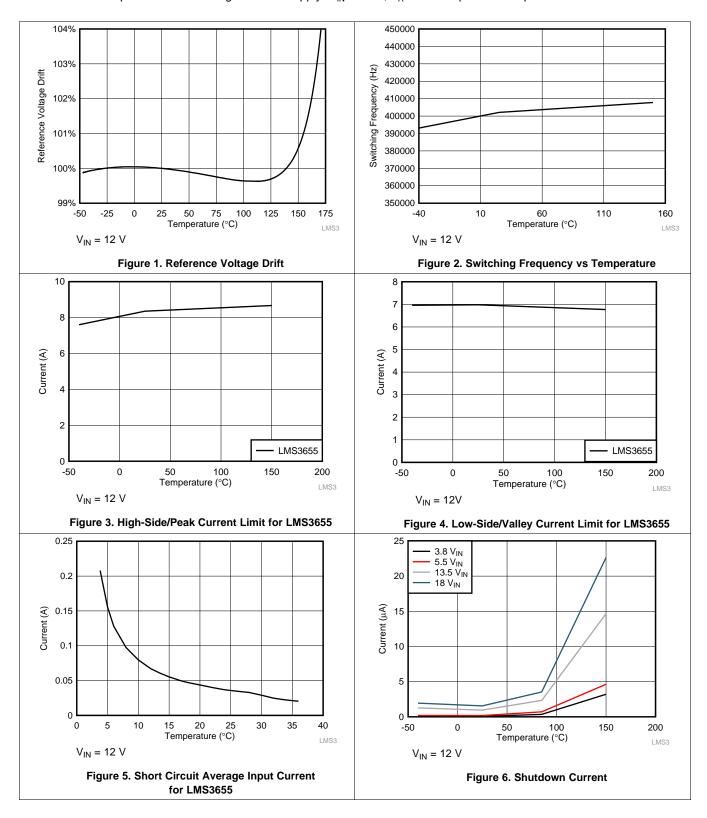

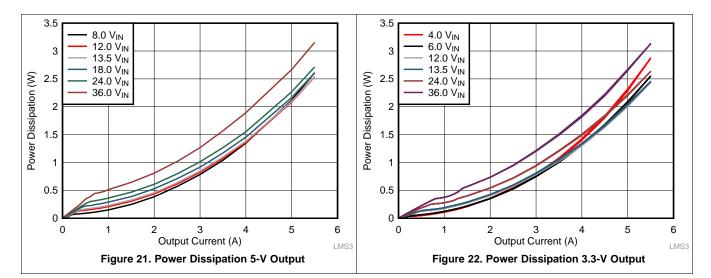

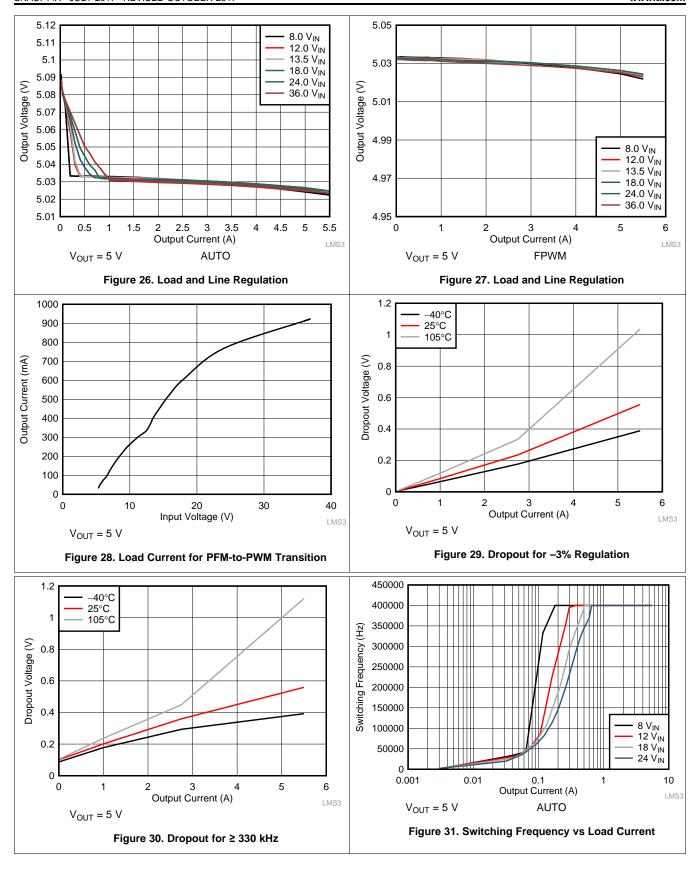

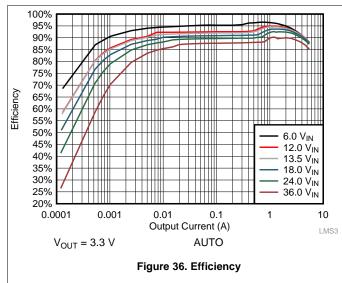

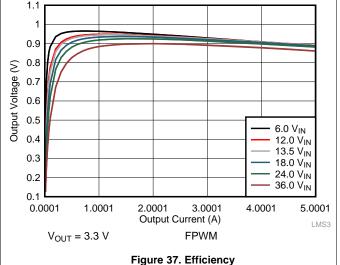

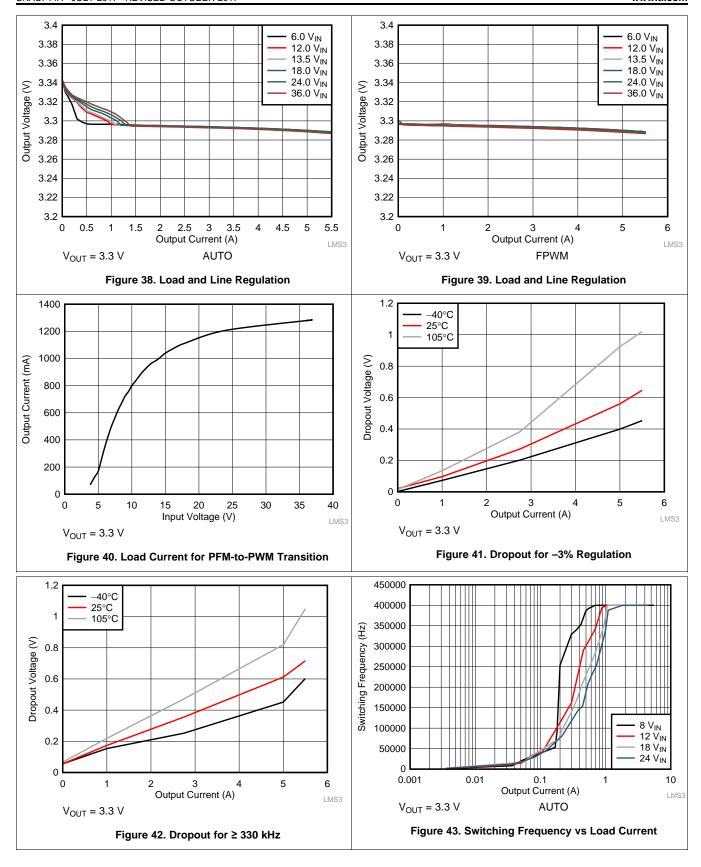

#### 7.9 Typical Characteristics

Unless otherwise specified the following conditions apply:  $V_{IN} = 12 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . Specified temperatures are ambient.

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

80

100 120

140 160

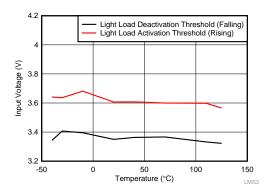

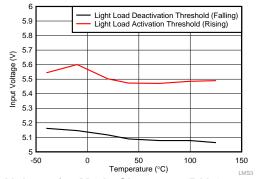

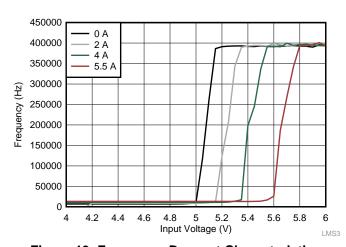

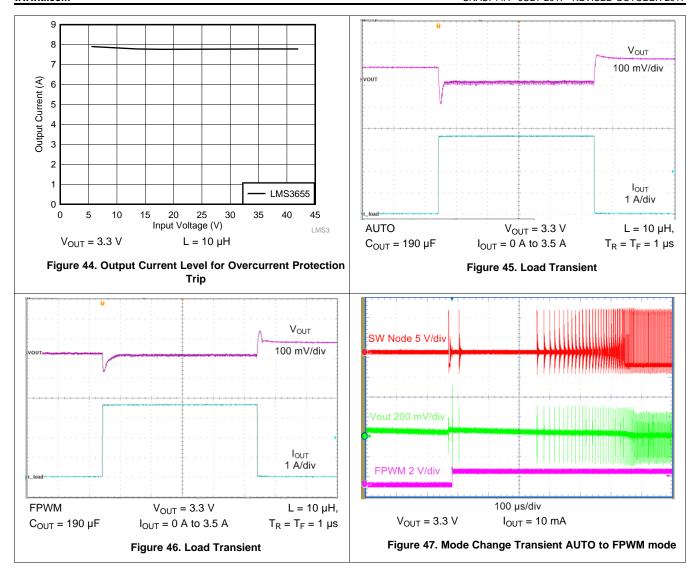

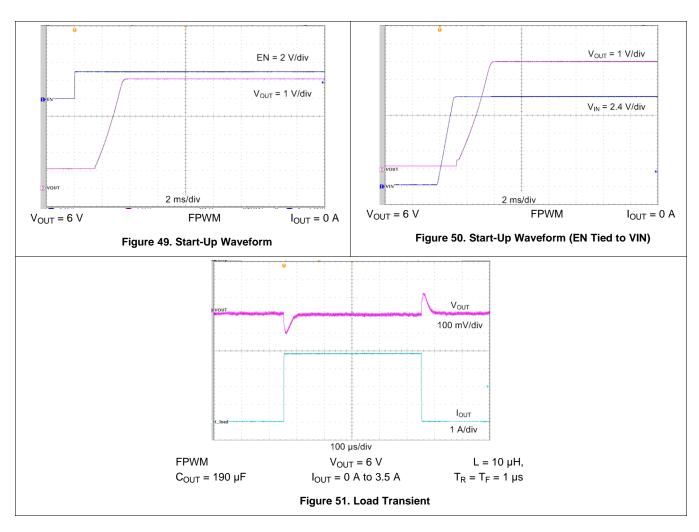

### **Typical Characteristics (continued)**

Unless otherwise specified the following conditions apply:  $V_{IN} = 12 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . Specified temperatures are ambient.

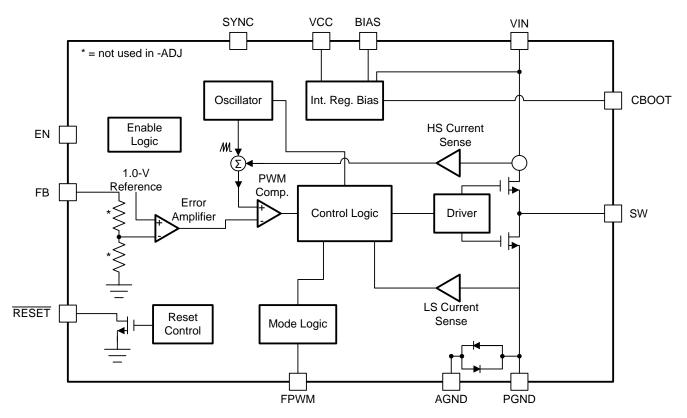

#### 8 Detailed Description

#### 8.1 Overview

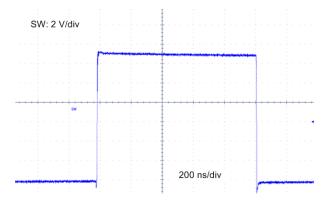

The LMS3655 devices are wide-input voltage range, low quiescent current, high-performance regulators with internal compensation. This device is designed to minimize end-product cost and size while operating in demanding high-performance industrial environments. Normal operating frequency is 400 kHz allowing the use of small passive components. This device has a low unloaded current consumption, eliminating the need for an external backup LDO. The LMS3655 low shutdown current and high maximum operating voltage also allow for the elimination of an external load switch. To further reduce system cost, an advanced reset output is provided, which can often eliminate the use of an external reset or supervisor device.

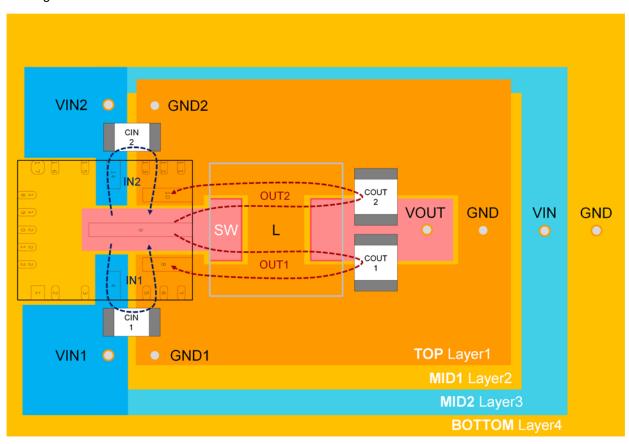

The LMS3655 family is designed with a flip-chip or HotRod™ technology, greatly reducing the parasitic inductance of the pins. In addition, the layout of the device allows for partial cancellation of the current generated magnetic field which reduces the radiated noise generated by the switching action.

As a result the switch-node waveform exhibits less overshoot and ringing.

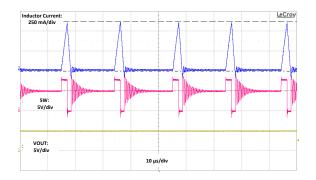

Figure 9. Switch Node Waveform ( $V_{IN} = 13.5 \text{ V}$ ,  $I_{OUT} = 5.5 \text{ A}$ )

The LMS3655 is available in a VQFN package with wettable flanks which allows easy inspection of the soldering without the requirement of x-ray checks.

# 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### Functional Block Diagram (continued)

#### 8.2.1 Control Scheme

The LMS3655 control scheme allows this device to operate under a wide range of conditions with a low number of external components. Peak current mode control allows a wide range of input voltages and output capacitance values while maintaining a constant switching frequency. Stable operation is maintained while output capacitance is changed during operation as well. This allows use in systems that require high performance during load transients and which have load switches that remove loads as the operating state changes. Short minimum on and off times ensure constant frequency regulation over a wide range of conversion ratios.

This architecture uses frequency spreading to achieve low dropout voltage maintaining output regulation as the input voltage falls close to output voltage. The frequency spreading is smooth and continuous, and activated as the off time approaches its minimum. Under these conditions, the LMS3655 operates like a constant off-time converter, allowing the maximum duty cycle to reach 98% and output voltage regulation with 650-mV dropout. As load current is reduced, the LMS3655 transitions to light load mode. In this mode, diode emulation is used to reduce RMS inductor current and switching frequency. Average output voltage increases slightly while lightly loaded as well.

#### 8.3 Feature Description

#### 8.3.1 RESET Flag Output

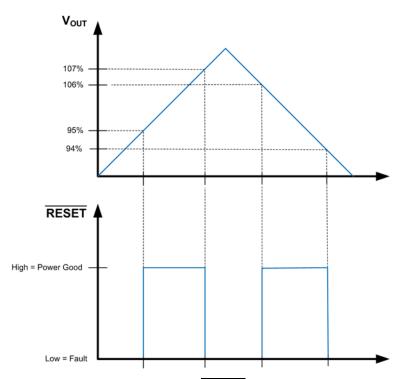

While the LMS3655 reset function resembles a standard Power-Good function, its functionality is designed to replace a discrete reset device, reducing additional component cost. There are three major differences between the reset function and the normal power good function seen in most regulators.

- A delay has been added between the point at which the output voltage is within specified limits and the flag

asserts Power Good. A glitch filter prevents false flag operation for short excursions in the output voltage,

such as during line and load transients. See Figure 11 and Figure 12 for more detail.

- RESET output signals a fault (pulls its output to ground) while the part is disabled.

- RESET continues to operate with input voltage as low as 1.5 V. Below this input voltage, RESET output may be high impedance.

Because the  $\overline{\text{RESET}}$  comparator and the regulation loop share the same reference, the thresholds track with the output voltage. When EN is pulled low, the  $\overline{\text{RESET}}$  flag output is forced low. When the device is disabled, RESET remains valid as long as the input voltage is  $\geq$  1.5 V. RESET operation can best be understood by reference to Figure 10 and Figure 11. Output voltage excursions lasting less than  $T_{\text{RESET-filter}}$  do not trip RESET. Once the output voltage is within the prescribed limits, a delay of  $T_{\text{RESET-act}}$  is imposed before RESET goes high. This enables tighter tolerance than is possible with an external supervisor device while also expanding the system allowance for transient response without the need for extremely accurate internal circuitry.

This output consists of an open-drain NMOS; requiring an external pullup resistor to a suitable logic supply. It can also be pulled up to either  $V_{CC}$  or  $V_{OUT}$ , through an appropriate resistor, as desired. The pin can be left floating or grounded if the  $\overline{RESET}$  function is not used in the application. The maximum current into this pin must be limited to 10 mA, and the maximum voltage must be less than 8 V.

# **Feature Description (continued)**

Figure 10. Static RESET Operation

Figure 11. RESET Timing Behavior

Copyright © 2017, Texas Instruments Incorporated Product Folder Links: *LMS*3655

#### **Feature Description (continued)**

The threshold voltage for the RESET function takes advantage of the availability of the LMS3655 internal feedback threshold to the RESET circuit. This allows a maximum threshold of 96.5% of selected output voltage to be specified at the same time as 96% of actual set point.

#### 8.3.2 Enable and Start-Up

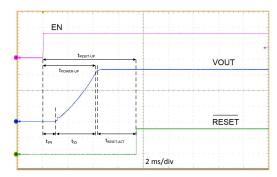

Start-up and shutdown of the LMS3655 are controlled by the EN input. Applying a voltage of ≥ 2 V activates the device, while a voltage of ≤ 1.45 V is required for shutdown. The EN input may also be connected directly to the input voltage supply. This input must not be left floating. The LMS3655 uses a reference-based soft start that prevents output voltage overshoots and large inrush currents as the regulator is starting up.

A typical start-up waveform is shown in Figure 12 along with timing definitions. This waveform indicates the sequence and timing between the enable input, output voltage, and RESET. From the figure, the user can define several different start-up times depending on what is relevant to the application. Table 2 lists the timing definitions and typical values.

Figure 12. Typical Start-Up Waveform

**DEFINITION VALUE** UNIT **PARAMETER** Time from EN to RESET released Total start-up sequence time 7.5 ms Time from EN to 90% of VOLIT 4 Start-up time ms Rise time of  $V_{OUT}$  from 10% to 90% Soft-start time 3.2 ms 1 Time from EN to start of VOUT rising ms

**Table 2. Typical Start-Up Times**

Time from output voltage within 94% and

#### 8.3.3 Soft-Start Function

Delay time

RESET time

Soft-start time is fixed internally at about 4 ms. Soft start is achieved by ramping the internal reference. The LMS3655 operates correctly even if there is a voltage present on the output before activation of the LMS3655 (prebiased start-up). The device operates in AUTO mode during soft start, and the state of the FPWM pin is ignored during that period.

RESET released

#### 8.3.4 Current Limit

t<sub>RESET-READY</sub>

t<sub>POWER-UP</sub>

t<sub>RESET-ACT</sub>

$t_{SS}$

$t_{EN}$

The LMS3655 incorporates a valley current limit for normal overloads and for short-circuit protection. A precision low-side current limit prevents excessive average output current from the buck converter of the LMS3655. A high-side peak-current limit is employed for protection of the top N MOSFET and inductors. The two current limits enable use of smaller inductors than a system with a single current limit. This scheme allows use of inductors with saturation current rated less than twice the operating current of the LMS3655.

Product Folder Links: LMS3655

3

ms

During overloads the low-side current limit,  $I_{L-LS}$  (see *Electrical Characteristics*), determines the maximum load current that the LMS3655 can supply. When the low-side switch turns on, the inductor current begins to ramp down. If the current does not fall below  $I_{L-LS}$  before the next turnon cycle, then that cycle is skipped, and the low-side FET is left on until the current falls below  $I_{L-LS}$ . This is different than the more typical peak current limit, and results in Equation 1 for the maximum load current.

$$I_{OUT}\big|_{max} = I_{LS} + \frac{\left(V_{IN} - V_{OUT}\right)}{2 \cdot F_{S} \cdot L} \cdot \frac{V_{OUT}}{V_{IN}}$$

(1)

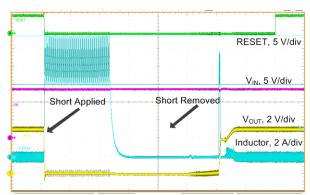

If the converter continues triggering valley current limit for more than about 64 clock cycles, the device turns off both high and low side switches for approximately 6 ms (see T<sub>W</sub> in *Timing Requirements*). If the overload is still present after the hiccup time, another 64 cycles is counted, and the process is repeated. If the current limit is not tripped for two consecutive clock cycles, the counter is reset. The hiccup time allows the inductor current to fall to zero, resetting the inductor volt-second balance. Of course the output current is greatly reduced in this condition (see *Typical Characteristics*). A typical short-circuit transient and recovery is shown in Figure 13.

Figure 13. Short-Circuit Transient and Recovery

The high-side current limit trips when the peak inductor current reaches I<sub>L-HS</sub> (see *Electrical Characteristics*). This is a cycle-by-cycle current limit and does not produce any frequency or current foldback. It is meant to protect the high-side MOSFET from excessive current. Under some conditions, such as high input voltage, this current limit may trip before the low-side protection. The peak value of this current limit varies with duty cycle.

In response to a short circuit, the peak current limit prevents excessive peak current while valley current limit prevents excessive average inductor current and keeps the power dissipation low during a fault. After a small number of cycles of valley current limit triggers, hiccup mode is activated.

In addition, the  $I_{NEG}$  current limit also protects the low-side switch from excessive negative current when the device is in FPWM mode. If this current exceeds  $I_{NEG}$ , the low-side switch is turned off until the next clock cycle. When the device is in AUTO mode, the negative current limit is increased to about  $I_{ZC}$  (about 0 A). This allows the device to operate in DCM.

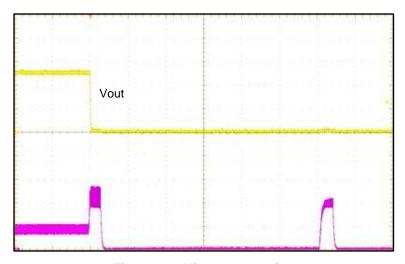

#### 8.3.5 Hiccup Mode

Hiccup mode prevents excessive heating and power consumption under sustained short-circuit conditions. If an overcurrent condition is maintained, the LMS3655 shuts off its output and waits for  $T_W$  (approximately 6 ms), after which the LMS3655 restarts operation by activating soft start.

Figure 14. Hiccup Operation

During hiccup mode operation, the switch node of the LMS3655 is high impedance after a short circuit or overcurrent persists for a short duration. Periodically, the LMS3655 attempts to restart. If the short has been removed before one of these restart attempts, the LMS3655 operates normally.

#### 8.3.6 Synchronizing Input

It is often desirable to synchronize the operation of multiple regulators in a single system. This technique results in better-defined EMI and can reduce the need for capacitance on some power rails. The LMS3655 provides a SYNC input which allows synchronization with an external clock. The LMS3655 implements an in-phase locking scheme—the rising edge of the clock signal provided to the SYNC input corresponds to turning on the high-side device within the LMS3655. The SYNC mode operation is implemented using phase locking over a limited frequency range eliminating large glitches upon initial application of an external clock. The clock fed into the LMS3655 replaces the internal free running clock but does not affect frequency foldback operation. Output voltage continues to be well regulated with duty factors outside of the normal 4% through 96% range though at reduced frequency.

The SYNC input recognizes a valid high level as that  $\geq$  1.5 V, and a valid low as that  $\leq$  0.4 V. The frequency synchronization signal must be in the range of 250 kHz to 500 kHz with a duty cycle of 10% to 90%. The internal clock is synced to the rising edge of the external clock. Ground this input if not used; this input must not be allowed to float. See *Device Functional Modes* to determine which modes are valid for synchronizing the clock.

The device remains in FPWM mode and operates in CCM for light loads when a synchronization input is provided. To prevent frequency foldback behavior at low duty cycles, provide a 200-mA load.

#### 8.3.7 Undervoltage Lockout (UVLO) and Thermal Shutdown (TSD)

The LMS3655 incorporates an input UVLO function. The device accepts an EN command when the input voltage rises above about 3.64 V and shuts down when the input falls below about 3.3 V. See *Electrical Characteristics* under  $V_{IN-OPERATE}$  for detailed specifications.

TSD is provided to protect the device from excessive temperature. When the junction temperature reaches about 165°C, the device shuts down; restart occurs at a temperature of about 150°C.

#### 8.3.8 Input Supply Current

The LMS3655 is designed to have very low input supply current when regulating light loads. This is achieved by powering much of the internal circuitry from the output. The BIAS pin is the input to the LDO that powers the majority of the control circuits. By connecting the BIAS input to the output of the regulator, this current acts as a small load on the output. This current is reduced by the ratio of  $V_{OLIT} / V_{IN}$ , just like any other load.

(2)

$I_{Q\_VIN}$  is defined as the current consumed by a converter using a LMS3655 device while regulating without a load. To calculate the theoretical total quiescent current, the below equation can be used with parameters from the *Electrical Characteristics* and *System Characteristics* tables. While operating without a load, the LMS3655 only powers itself. The device draws power from three sources: the  $V_{IN}$  pin ( $I_{Q}$ ), the EN pin ( $I_{EN}$ ), and the BIAS pin ( $I_{B}$ ). Because the BIAS input is connected to the output of the circuit, the power consumed is converted from input power with an effective efficiency,  $\eta$ eff. Here, effective efficiency is the added input power needed when lightly loading the converter of the LMS3655 device and is divided by the corresponding additional load. This allows unloaded current to be calculated in Equation 2:

$$I_{Q_{-}VIN} = I_{Q} + I_{EN} + \left(I_{B} + I_{div}\right) \frac{Output \ Voltage}{\eta_{eff} \times Input \ Voltage}$$

#### where

- I<sub>Q VIN</sub> is the current consumed by the operating (switching) buck converter while unloaded.

- I<sub>Q</sub> is the current drawn by the LMS3655 from its V<sub>IN</sub> terminal. See I<sub>Q</sub> in *Electrical Characteristics*.

- I<sub>EN</sub> is current drawn by the LMS3655 from its EN terminal. Include this current if EN is connected to VIN. See

I<sub>EN</sub> in *Electrical Characteristics*. Note that this current drops to a very low value if connected to a voltage less

than 5 V

- I<sub>B</sub> is bias current drawn by the unloaded LMS3655. See I<sub>B</sub> in System Characteristics.

- I<sub>div</sub> is the current drawn by the feedback voltage divider used to set output voltage.

- η<sub>eff</sub> is the light load efficiency of the Buck converter with I<sub>Q\_VIN</sub> removed from the input current of the buck converter.

The EN pin consumes a few micro-amperes when tied to high; see  $I_{EN}$ . Add  $I_{EN}$  to  $I_Q$  as shown in Equation 2 if EN is tied to  $V_{IN}$ . If EN is tied to a voltage less than 5 V, virtually no current is consumed allowing EN to be used as an UVLO pin once a voltage divider is added.

NOTE

#### 8.4 Device Functional Modes

Refer to Table 3 and the following paragraphs for a detailed description of the functional modes for the LMS3655.

These modes are controlled by the FPWM input as listed in Table 3. This input can be controlled by any compatible logic while the regulator is operating. If it is desired to fix the mode for a given application, the input can be either connected to ground, a logic supply, the VIN pin, or the VCC pin, as desired. The FPWM pin must not be allowed to float.

**Table 3. Mode Selection**

| FPWM INPUT VOLTAGE | OPERATING MODE                                                                                                                                         |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|