SBOS710B - OCTOBER 2014-REVISED JANUARY 2015

LMH5401

# LMH5401 8-GHz, Low-Noise, Low-Power, Fully-Differential Amplifier

### **Features**

Gain Bandwidth Product (GBP): 8 GHz

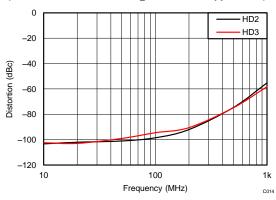

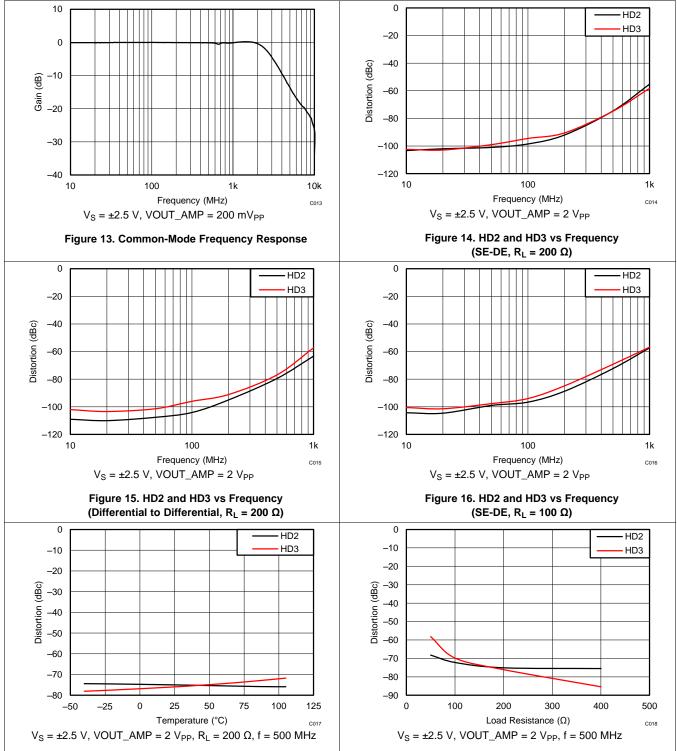

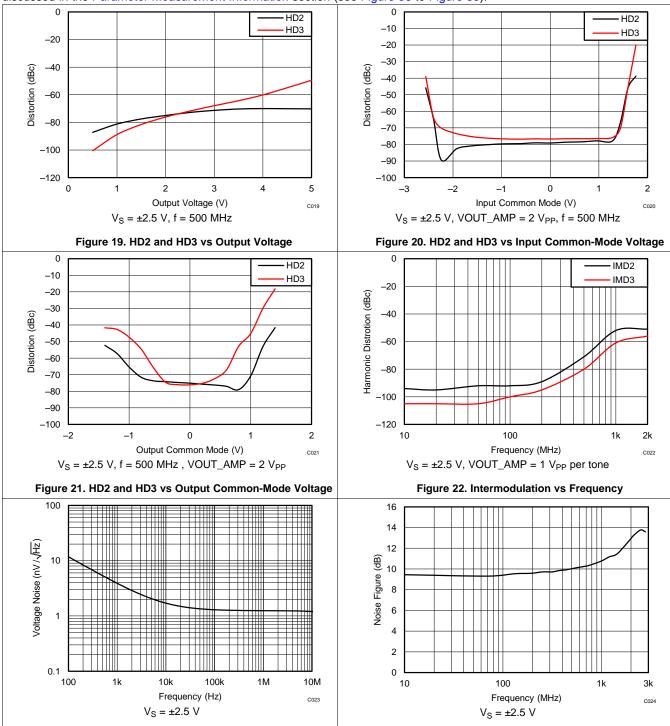

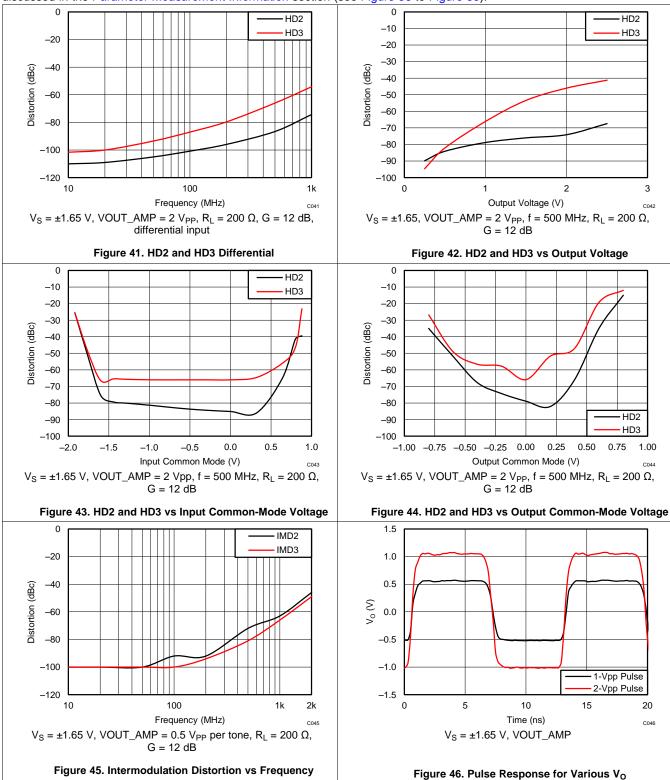

**Excellent Linearity Performance:** DC to 2 GHz, G = 12 dB

Slew Rate: 17,500 V/µs

Low HD2, HD3 Distortion

(1  $V_{PP}$ , 200  $\Omega$ , DE-DE, G = 12 dB):

100 MHz: HD2 at -104 dBc, HD3 at -96 dBc

200 MHz: HD2 at -95 dBc, HD3 at -92 dBc

500 MHz: HD2 at -80 dBc, HD3 at -77 dBc

1 GHz: HD2 at –64 dBc, HD3 at –58 dBc

Low IMD2, IMD3 Distortion (2  $V_{PP}$ , 200  $\Omega$ , DE-DE, G = 12 dB):

200 MHz: IMD2 at -96 dBc, IMD3 at -95 dBc

500 MHz: IMD2 at -80 dBc. IMD3 at -83 dBc

1 GHz: IMD2 at -70 dBc, IMD3 at -63 dBc

Input Voltage Noise: 1.25 nV/√Hz

Input Current Noise: 3.5 pA/√Hz

Supports Single- and Dual-Supply Operation

Power Consumption: 55 mA

Power-Down Feature

## Applications

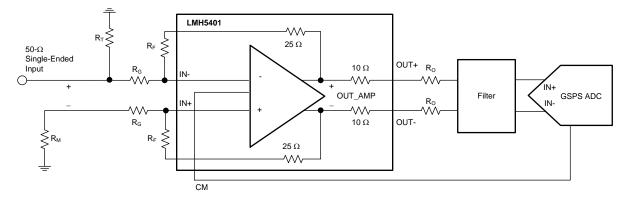

- **GSPS ADC Drivers**

- ADC Drivers for High-Speed Data Acquisition

- ADC Drivers for 1-GBPS Ethernet over Microwave

- **DAC Buffers**

- IF, RF, and Baseband Gain Blocks

- SAW Filter Buffers and Drivers

- Balun Replacement DC to 2 GHz

- Level Shifters

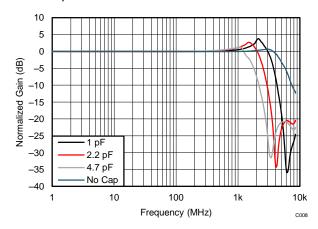

## **Distortion versus Frequency** $(G = 12 \text{ dB}, \text{ SE-DE}, R_1 = 200 \Omega, V_{PP} = 2 \text{ V})$

## 3 Description

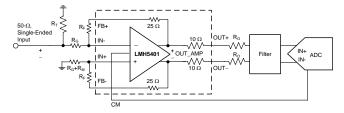

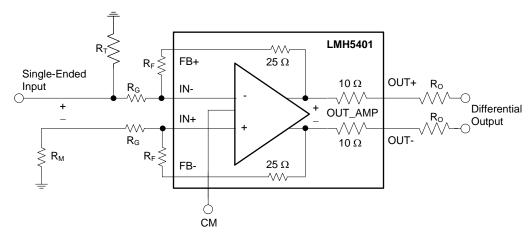

The LMH5401 is a very high-performance, differential amplifier optimized for radio frequency (RF), intermediate frequency (IF), or high-speed, dccoupled, time-domain applications. The device is ideal for dc- or ac-coupled applications that may single-ended-to-differential conversion when drivina an analog-to-digital converter (ADC). The LMH5401 generates very low levels of second- and third-order distortion when operating in SE-DE or differential-to-differential (DE-DE) mode.

The amplifier is optimized for use in both SE-DE and DE-DE systems. The device has unprecedented usable bandwidth from dc to 2 GHz. The LMH5401 can be used for SE-DE conversions in the signal chain without external baluns in a wide range of applications such as test and measurement, broadband communications, and high-speed data acquisition.

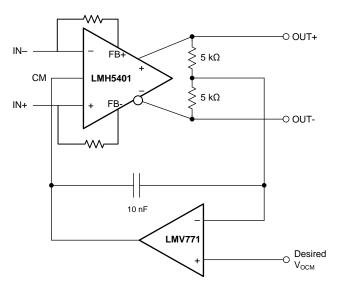

A common-mode reference input pin is provided to align the amplifier output common-mode with the ADC input requirements. Power supplies between 3.3 V and 5.0 V can be selected and dual-supply operation is supported when required by the application. A power-down feature is also available for power savings.

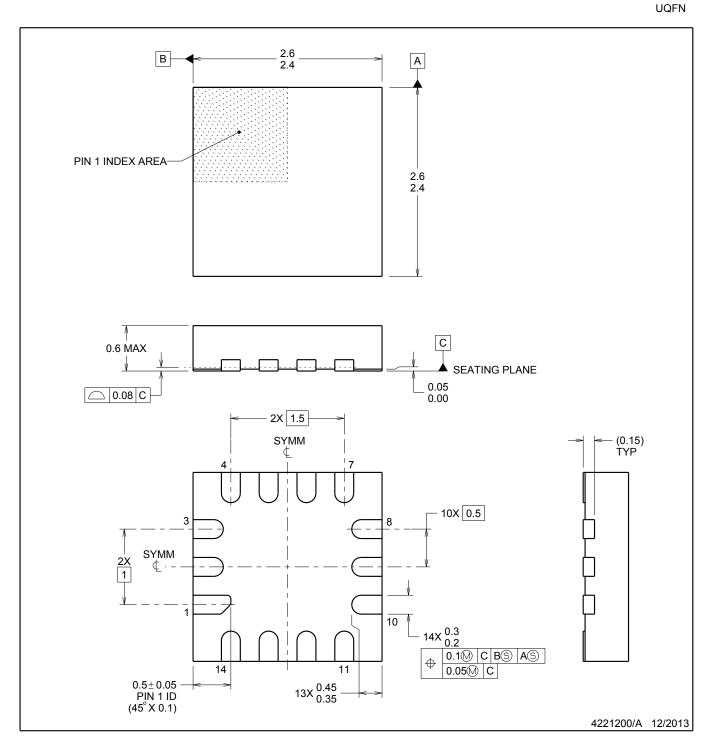

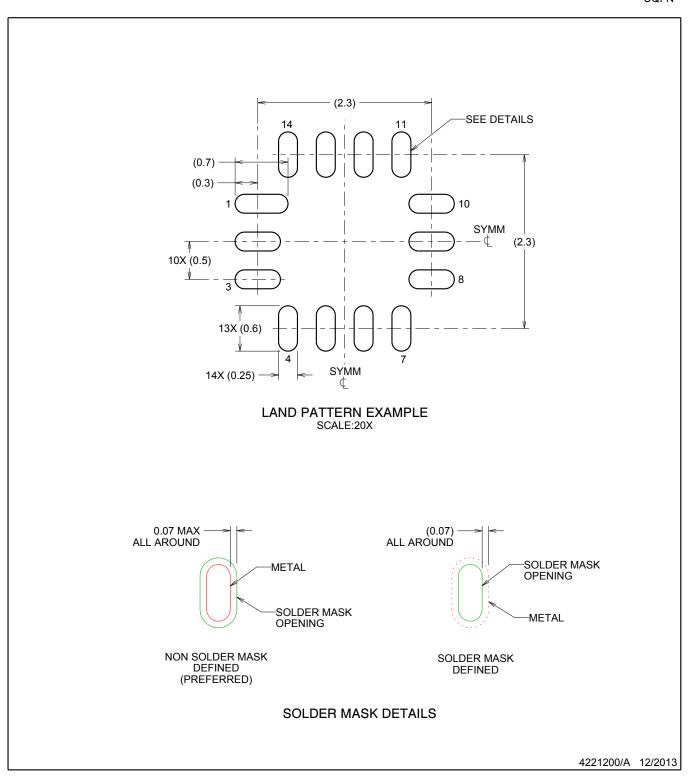

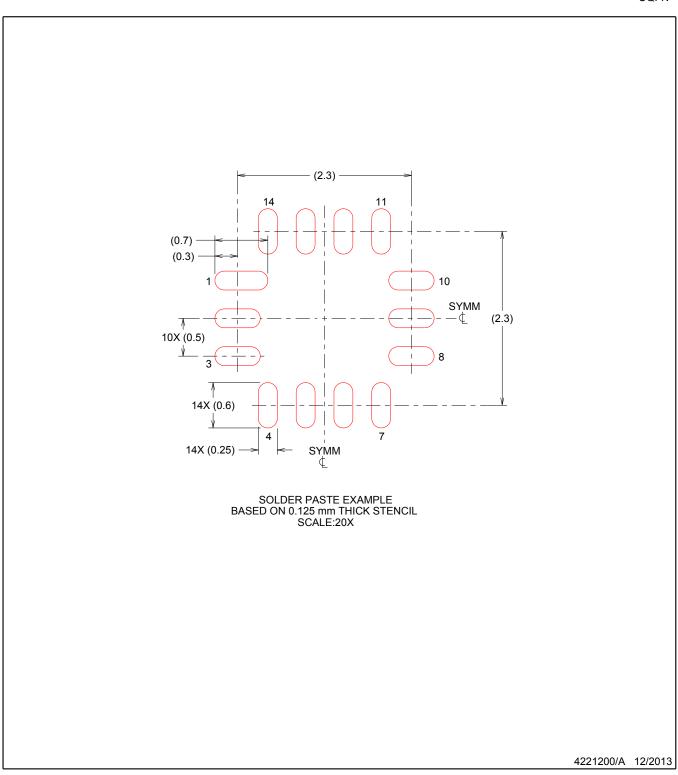

This level of performance is achieved at a very low power level of 275 mW when a 5.0-V supply is used. The device is fabricated in Texas Instruments' advanced complementary BiCMOS process and is available in a space-saving, UQFN-14 package for higher performance.

## Device Information<sup>(1)</sup>

| DEVICE NAME | PACKAGE   | BODY SIZE         |

|-------------|-----------|-------------------|

| LMH5401     | UQFN (14) | 2.50 mm × 2.50 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

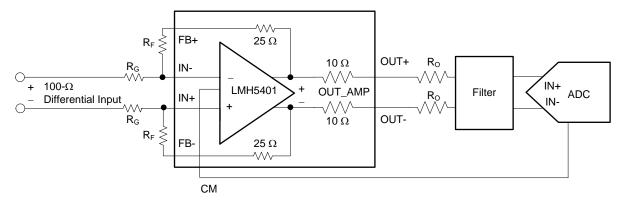

### LMH5401 Driving an ADC12J4000

# **Table of Contents**

| 1 | Features 1                                            |    | 8.10 V <sub>CM</sub> Frequency Response          |                 |

|---|-------------------------------------------------------|----|--------------------------------------------------|-----------------|

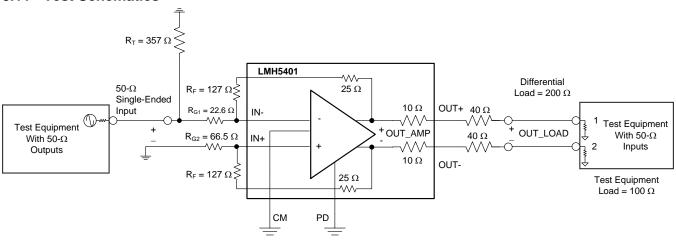

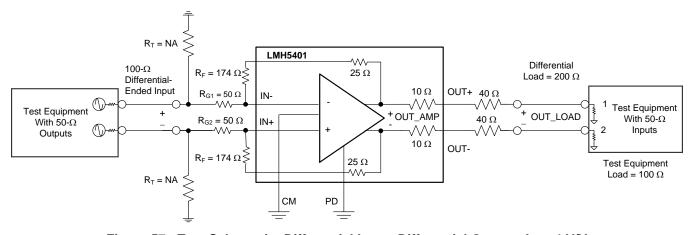

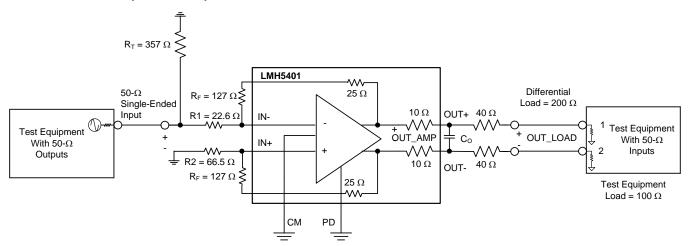

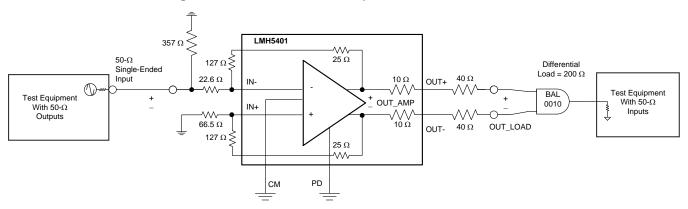

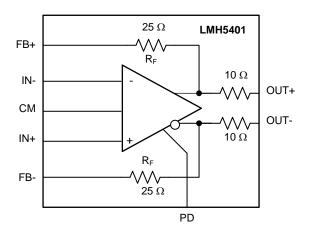

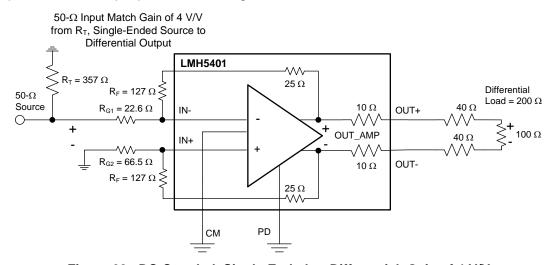

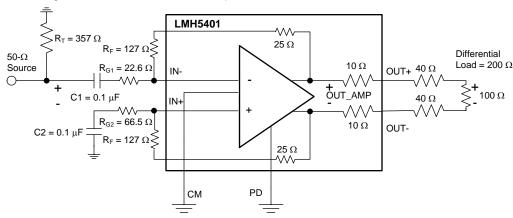

| 2 | Applications 1                                        |    | 8.11 Test Schematics                             | <mark>22</mark> |

| 3 | Description 1                                         | 9  | Detailed Description                             | 24              |

| 4 | Revision History2                                     |    | 9.1 Overview                                     | 24              |

| 5 | Device Comparison Table 4                             |    | 9.2 Functional Block Diagram                     | 24              |

| 6 | Pin Configuration and Functions 4                     |    | 9.3 Feature Description                          | 24              |

| 7 | Specifications 5                                      |    | 9.4 Device Functional Modes                      | 30              |

| ′ | 7.1 Absolute Maximum Ratings 5                        | 10 | Application and Implementation                   | 31              |

|   | 7.2 ESD Ratings                                       |    | 10.1 Application Information                     | 31              |

|   | 7.2 ESD Ratings                                       |    | 10.2 Typical Application                         | 34              |

|   | 7.4 Thermal Information                               |    | 10.3 Do's and Don'ts                             | 42              |

|   | 7.5 Electrical Characteristics: $V_S = 5 \text{ V}$   | 11 | Power-Supply Recommendations                     | 43              |

|   | 7.5 Electrical Characteristics: $V_S = 3.3 \text{ V}$ |    | 11.1 Supply Voltage                              |                 |

|   | 7.7 Typical Characteristics: 5 V                      |    | 11.2 Single Supply                               | 43              |

|   | 7.8 Typical Characteristics: 3.3 V                    |    | 11.3 Split Supply                                | 43              |

|   | 7.9 Typical Characteristics: 3.3-V to 5-V Supply      |    | 11.4 Supply Decoupling                           | 43              |

|   | Range                                                 | 12 | Layout                                           | 44              |

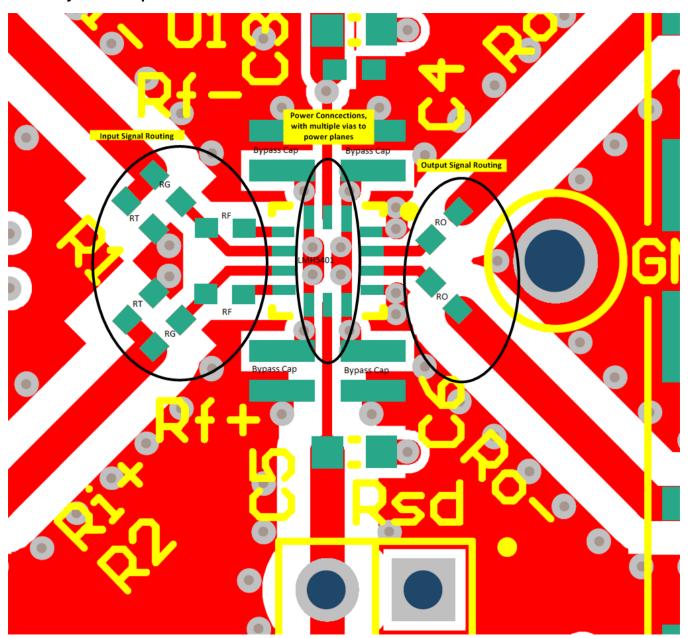

| 8 | Parameter Measurement Information                     |    | 12.1 Layout Guidelines                           |                 |

| • | 8.1 Output Reference Points                           |    | 12.2 Layout Example                              | 45              |

|   | 8.2 ATE Testing and DC Measurements                   | 13 | Device and Documentation Support                 | 47              |

|   | 8.3 Frequency Response                                |    | 13.1 Device Support                              | 47              |

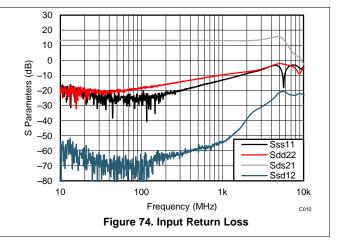

|   | 8.4 S-Parameters                                      |    | 13.2 Documentation Support                       | 47              |

|   | 8.5 Frequency Response with Capacitive Load 21        |    | 13.3 Trademarks                                  | 48              |

|   | 8.6 Distortion                                        |    | 13.4 Electrostatic Discharge Caution             | 48              |

|   | 8.7 Noise Figure                                      |    | 13.5 Glossary                                    | 48              |

|   | 8.8 Pulse Response, Slew Rate, and Overdrive Recovery | 14 | Mechanical, Packaging, and Orderable Information | 48              |

|   | 8.9 Power Down                                        |    |                                                  |                 |

# 4 Revision History

| <ul> <li>Added <i>dc-coupled</i> to first sentence of Description section</li> <li>Changed second sentence of second paragraph in Description section</li> <li>Updated ESD Ratings table to current standards</li> <li>Changed AC Performance, <i>IMD3</i> and <i>IMD2</i> parameter test conditions in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 3.3-V Electrical Characteristics table</li> <li>Changed Output, <i>V<sub>OCRH</sub></i> parameter test condition from <i>Output voltage range low</i> to <i>T<sub>A</sub></i> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added <i>Large-Signal</i> to title of Figure 2, Figure 4, and Figure 6</li> <li>Added <i>Large-Signal</i> to title of Figure 8</li> <li>Changed <i>Differential-Ended</i> to <i>Differential</i> in title of Figure 11</li> <li>Added <i>Large-Signal</i> to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added <i>Large-Signal</i> to titles of Figure 36</li> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed header for last column in Table 1</li> <li>Changed Figure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> <li>Deleted last sentence from first paragraph of the <i>Fully-Differential Amplifier</i> section</li> </ul> | C | hanges from Revision A (October 2014) to Revision B                                                       | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Updated ESD Ratings table to current standards</li> <li>Changed AC Performance, <i>IMD3</i> and <i>IMD2</i> parameter test conditions in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 3.3-V Electrical Characteristics table</li> <li>Changed Output, <i>V<sub>OCRH</sub></i> parameter test condition from <i>Output voltage range low</i> to <i>T<sub>A</sub></i> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added <i>Large-Signal</i> to title of Figure 2, Figure 4, and Figure 6</li> <li>Added <i>Large-Signal</i> to title of Figure 8</li> <li>Changed <i>Differential-Ended</i> to <i>Differential</i> in title of Figure 11</li> <li>Added <i>Large-Signal</i> to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added <i>Large-Signal</i> to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> </ul>                                                                                                                                                                                                                                                                | • | Added dc-coupled to first sentence of Description section                                                 | 1    |

| <ul> <li>Changed AC Performance, <i>IMD3</i> and <i>IMD2</i> parameter test conditions in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 3.3-V Electrical Characteristics table</li> <li>Changed Output, <i>V<sub>OCRH</sub></i> parameter test condition from <i>Output voltage range low</i> to <i>T<sub>A</sub></i> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added <i>Large-Signal</i> to title of Figure 2, Figure 4, and Figure 6</li> <li>Added <i>Large-Signal</i> to title of Figure 8</li> <li>Changed <i>Differential-Ended</i> to <i>Differential</i> in title of Figure 11</li> <li>Added <i>Large-Signal</i> to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added <i>Large-Signal</i> to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed Figure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> <li>2</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> </ul>                                                                                                                                                                                                                                    | • | Changed second sentence of second paragraph in Description section                                        | 1    |

| <ul> <li>Changed AC Performance, <i>IMD3</i> and <i>IMD2</i> parameter test conditions in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 5-V Electrical Characteristics table</li> <li>Changed Input, <i>V<sub>ICL</sub></i> parameter maximum specification in 3.3-V Electrical Characteristics table</li> <li>Changed Output, <i>V<sub>OCRH</sub></i> parameter test condition from <i>Output voltage range low</i> to <i>T<sub>A</sub></i> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added <i>Large-Signal</i> to title of Figure 2, Figure 4, and Figure 6</li> <li>Added <i>Large-Signal</i> to title of Figure 8</li> <li>Changed <i>Differential-Ended</i> to <i>Differential</i> in title of Figure 11</li> <li>Added <i>Large-Signal</i> to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added <i>Large-Signal</i> to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed Figure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> <li>2</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added <i>A<sub>V</sub></i> = 4 <i>V/V</i> to titles</li> </ul>                                                                                                                                                                                                                                    | • | Updated ESD Ratings table to current standards                                                            | 5    |

| <ul> <li>Changed Input, V<sub>ICL</sub> parameter maximum specification in 3.3-V Electrical Characteristics table</li> <li>Changed Output, V<sub>OCRH</sub> parameter test condition from <i>Output voltage range low</i> to T<sub>A</sub> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added Large-Signal to title of Figure 2, Figure 4, and Figure 6</li> <li>Added Large-Signal to title of Figure 8</li> <li>Changed Differential-Ended to Differential in title of Figure 11</li> <li>Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • |                                                                                                           |      |

| <ul> <li>Changed Output, V<sub>OCRH</sub> parameter test condition from <i>Output voltage range low</i> to T<sub>A</sub> = -40°C to 85°C in 3.3-V Electrical Characteristics table</li> <li>Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves</li> <li>Added <i>Large-Signal</i> to title of Figure 2, Figure 4, and Figure 6</li> <li>Added <i>Large-Signal</i> to title of Figure 8</li> <li>Changed <i>Differential-Ended</i> to <i>Differential</i> in title of Figure 11</li> <li>Added <i>Large-Signal</i> to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added <i>Large-Signal</i> to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | Changed Input, V <sub>ICL</sub> parameter maximum specification in 5-V Electrical Characteristics table   | 6    |

| Electrical Characteristics table  Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves  Added Large-Signal to title of Figure 2, Figure 4, and Figure 6  Added Large-Signal to title of Figure 8  Changed Differential-Ended to Differential in title of Figure 11  Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34  Added Large-Signal to title of Figure 36  Changed correction to reduction in second paragraph of Output Reference Points section  Changed header for last column in Table 1  ChangedFigure 56 through Figure 59: modifications to figures, added A <sub>V</sub> = 4 V/V to titles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | Changed Input, V <sub>ICL</sub> parameter maximum specification in 3.3-V Electrical Characteristics table | 8    |

| <ul> <li>Added Large-Signal to title of Figure 2, Figure 4, and Figure 6</li> <li>Added Large-Signal to title of Figure 8</li> <li>Changed Differential-Ended to Differential in title of Figure 11</li> <li>Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • |                                                                                                           | g    |

| <ul> <li>Added Large-Signal to title of Figure 8</li> <li>Changed Differential-Ended to Differential in title of Figure 11</li> <li>Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added <math>A_V = 4 \text{ V/V}</math> to titles</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves         | 10   |

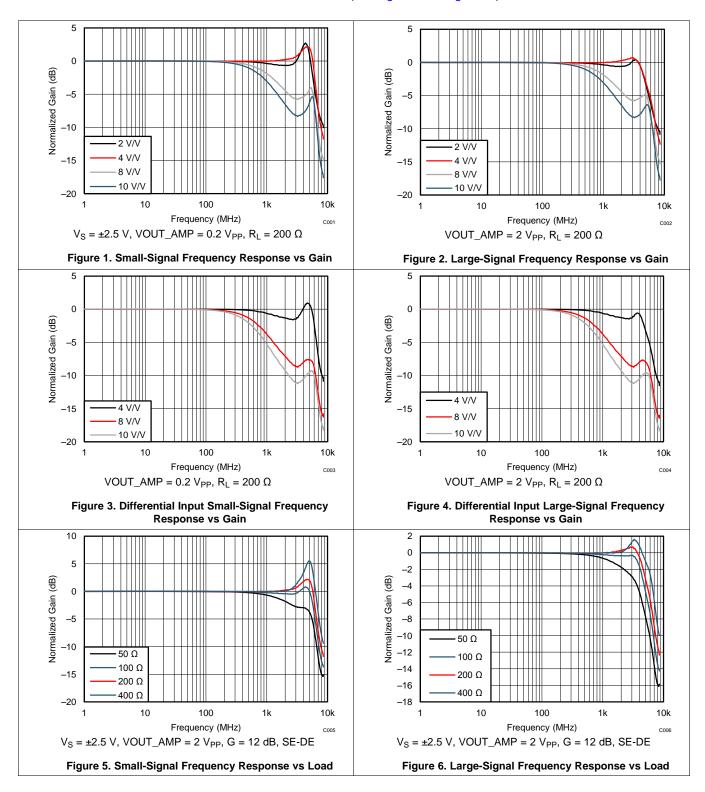

| <ul> <li>Changed Differential-Ended to Differential in title of Figure 11</li> <li>Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> <li>2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | Added Large-Signal to title of Figure 2, Figure 4, and Figure 6                                           | 10   |

| <ul> <li>Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34</li> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | Added Large-Signal to title of Figure 8                                                                   | 11   |

| <ul> <li>Added Large-Signal to title of Figure 36</li> <li>Changed correction to reduction in second paragraph of Output Reference Points section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | Changed Differential-Ended to Differential in title of Figure 11                                          | 11   |

| <ul> <li>Changed correction to reduction in second paragraph of <i>Output Reference Points</i> section</li> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34                                       | 15   |

| <ul> <li>Changed header for last column in Table 1</li> <li>ChangedFigure 56 through Figure 59: modifications to figures, added A<sub>V</sub> = 4 V/V to titles</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | Added Large-Signal to title of Figure 36                                                                  | 16   |

| • ChangedFigure 56 through Figure 59: modifications to figures, added $A_V = 4 \text{ V/V}$ to titles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | Changed correction to reduction in second paragraph of Output Reference Points section                    | 20   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • | Changed header for last column in Table 1                                                                 | 21   |

| Deleted last sentence from first paragraph of the Fully-Differential Amplifier section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • |                                                                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • | Deleted last sentence from first paragraph of the Fully-Differential Amplifier section                    | 25   |

# **Revision History (continued)**

| •  | Changed 1.2 V to the specified minimum voltage in the third paragraph of the Fully-Differential Amplifier section  Added sixth sentence stating the feedback path must always be dc-coupled to the AC-Coupled Signal Path  Considerations section |      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added $A_V = 4 \text{ V/V}$ to title of Figure 62                                                                                                                                                                                                 |      |

| •  | Deleted example from the Operation with a Single Supply section                                                                                                                                                                                   |      |

| •  | Added Stability section                                                                                                                                                                                                                           |      |

| •  | Changed 15 dB to 19 dB in third paragraph of SFDR Considerations section                                                                                                                                                                          | 37   |

| •  | Added Figure 74 to the Active Balun section                                                                                                                                                                                                       | 41   |

| CI | hanges from Original (October 2014) to Revision A                                                                                                                                                                                                 | Page |

| •  | Changed Output Common-Mode Control Pin, V <sub>CM</sub> voltage range low and high parameter typical specifications in 5-V Electrical Characteristics                                                                                             |      |

| •  | Changed Output Common-Mode Control Pin, $V_{CM}$ voltage range low and high parameter specifications in 3.3-V                                                                                                                                     | c    |

# 5 Device Comparison Table

| DEVICE  | BW (A <sub>V</sub> = 12 dB) | DISTORTION                          | NOISE (nV/√Hz) |

|---------|-----------------------------|-------------------------------------|----------------|

| LMH3401 | 7 GHz, G = 16 dB            | -79-dBc HD2, -77-dBc HD3 at 500 MHz | 1.4            |

| LMH6554 | 1.6 GHz                     | –79-dBc HD2, –70-dBc HD3 at 250 MHz | 0.9            |

| LMH6552 | 0.8 GHz                     | -74-dBc HD2, -84-dBc HD3 at 70 MHz  | 1.1            |

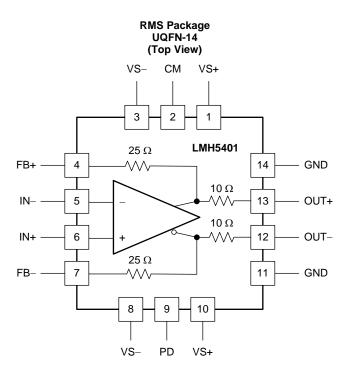

# 6 Pin Configuration and Functions

**Pin Functions**

| PIN  |        | 1/0 | DESCRIPTION                                           |  |

|------|--------|-----|-------------------------------------------------------|--|

| NAME | NO.    | 1/0 | DESCRIPTION                                           |  |

| СМ   | 2      | 1   | Input pin to set amplifier output common-mode voltage |  |

| FB-  | 7      | 0   | Negative output feedback component connection         |  |

| FB+  | 4      | 0   | Positive output feedback component connection         |  |

| GND  | 11, 14 | Р   | Printed circuit board (PCB) ground                    |  |

| IN-  | 5      | I   | Negative input pin                                    |  |

| IN+  | 6      | I   | Positive input pin                                    |  |

| OUT- | 12     | 0   | Negative output pin                                   |  |

| OUT+ | 13     | 0   | Positive output pin                                   |  |

| PD   | 9      | I   | Power-down (logic 1 = power down)                     |  |

| VS-  | 3, 8   | Р   | Negative supply voltage                               |  |

| VS+  | 1, 10  | Р   | Positive supply voltage                               |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|               |                                                                           | MIN                           | MAX         | UNIT |

|---------------|---------------------------------------------------------------------------|-------------------------------|-------------|------|

| Valtage       | Power supply                                                              |                               | 5.5         | V    |

| Voltage       | Input voltage range                                                       | (VS-) - 0.7                   | (VS+) + 0.7 | V    |

| Current       | Input current                                                             |                               | 10          | mA   |

| Current       | Output current (sourcing or sinking) OUT+, OUT-                           |                               | 100         | mA   |

| Continuous po | ower dissipation                                                          | See Thermal Information table |             |      |

|               | Maximum junction temperature, T <sub>J</sub>                              |                               | 150         | °C   |

| Tomporotura   | Maximum junction temperature, continuous operation, long-term reliability |                               | 125         | °C   |

| Temperature   | Operating free-air, T <sub>A</sub>                                        | -40                           | 85          | °C   |

|               | Storage, T <sub>stg</sub>                                                 | -40                           | 150         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±3500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                   | MIN  | NOM | MAX  | UNIT |

|---------------------------------------------------|------|-----|------|------|

| Supply voltage ( $V_S = VS+ - VS-$ )              | 3.15 | 5   | 5.25 | V    |

| Operating junction temperature, T <sub>J</sub>    | -40  |     | 125  | °C   |

| Ambient operating air temperature, T <sub>A</sub> | -40  | 25  | 85   | °C   |

### 7.4 Thermal Information

|                        |                                              | LMH5401    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RMS (UQFN) | UNIT |

|                        |                                              | 14 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 101        |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 51         |      |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 61         | °C/W |

| Ψлт                    | Junction-to-top characterization parameter   | 4.2        | C/VV |

| ΨЈВ                    | Junction-to-board characterization parameter | 61         |      |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | N/A        |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics: $V_S = 5 V$

At  $T_A$  = 25°C, VS+ = 2.5 V, VS- = -2.5 V,  $V_{CM}$  = 0 V,  $R_L$  = 200- $\Omega$  differential, G = 12 dB (4 V/V), single-ended input, differential output, and  $R_S$  = 50  $\Omega$ , unless otherwise noted. (1)

|                  | PARAMETER                       | TEST CONDITIONS                                          | MIN          | TYP         | MAX          | UNIT               | TEST<br>LEVEL <sup>(2)</sup> |

|------------------|---------------------------------|----------------------------------------------------------|--------------|-------------|--------------|--------------------|------------------------------|

| AC PER           | FORMANCE                        |                                                          | ·            |             |              |                    |                              |

| GBP              | Gain bandwidth product          | G = 30 dB (32 V/V)                                       |              | 8           |              | GHz                | С                            |

| SSBW             | Small-signal, -3-dB bandwidth   | V <sub>O</sub> = 200 mV <sub>PP</sub>                    |              | 6.2         |              | GHz                | С                            |

| LSBW             | Large-signal, -3-dB bandwidth   | $V_O = 2.0 V_{PP}$                                       |              | 4.8         |              | GHz                | С                            |

|                  | Bandwidth for 0.1-dB flatness   | $V_O = 2.0 V_{PP}$                                       |              | 800         |              | MHz                | С                            |

| SR               | Slew rate                       | 2-V step                                                 |              | 17500       |              | V/µs               | С                            |

|                  | Rise and fall time              | 1-V step, 10% to 90%                                     |              | 80          |              | ps                 | С                            |

|                  | Overdrive recovery              | Overdrive = ±0.5 V                                       |              | 300         |              | ps                 | С                            |

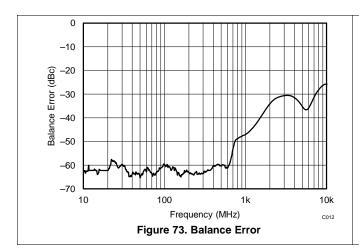

|                  | Output balance error            | f = 1 GHz                                                |              | 47          |              | dBc                | С                            |

| z <sub>o</sub>   | Output impedance                | At dc, differential                                      | 16           | 20          | 24           | Ω                  | А                            |

|                  | 0.1% settling time              | 2 V, R <sub>L</sub> = 200 Ω                              |              | 1           |              | ns                 | С                            |

|                  |                                 | f = 100 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -99         |              | dBc                | С                            |

| LIDO             | Second-order harmonic           | f = 200 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -92         |              | dBc                | С                            |

| HD2              | distortion                      | f = 500 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -75         |              | dBc                | С                            |

|                  |                                 | f = 1 GHz, V <sub>O</sub> = 2 V <sub>PP</sub>            |              | -56         |              | dBc                | С                            |

|                  | Third-order harmonic distortion | f = 100 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -94         |              | dBc                | С                            |

|                  |                                 | f = 200 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -90         |              | dBc                | С                            |

| HD3              |                                 | f = 500 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>          |              | -75         |              | dBc                | С                            |

|                  |                                 | f = 1 GHz, V <sub>O</sub> = 2 V <sub>PP</sub>            |              | -58         |              | dBc                | С                            |

|                  |                                 | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -95         |              | dBc                | С                            |

|                  |                                 | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -91         |              | dBc<br>dBc         | С                            |

| IMD3             | Third-order intermodulation     | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -75         |              | dBc                | С                            |

|                  |                                 | f = 1 GHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone   |              | -60         |              | dBc                | С                            |

|                  |                                 | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -95         |              | dBc                | С                            |

|                  |                                 | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -89         |              | dBc                | С                            |

| IMD2             | Second-order intermodulation    | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone |              | -71         |              | dBc                | С                            |

|                  |                                 | f = 1 GHz, V <sub>O</sub> = 1 V <sub>PP</sub> per tone   |              | -52         |              | dBc                | С                            |

| NOISE F          | PERFORMANCE                     |                                                          | <u> </u>     |             |              |                    |                              |

| e <sub>n</sub>   | Input voltage noise density     |                                                          |              | 1.25        |              | nV/√ <del>Hz</del> | С                            |

| i <sub>n</sub>   | Input noise current             |                                                          |              | 3.5         |              | pA/√ <del>Hz</del> | С                            |

| NF               | Noise figure                    | $R_S = 50 \Omega$ , SE-DE, 200 MHz (see Figure 59)       |              | 9.6         |              | dB                 | С                            |

| INPUT            |                                 |                                                          |              |             |              |                    |                              |

|                  | Differential resistance         | Open-loop                                                |              | 4600        |              | Ω                  | С                            |

| V <sub>ICL</sub> | Input common-mode low voltage   |                                                          |              | VS-         | (VS-) + 0.41 | V                  | Α                            |

| V <sub>ICH</sub> | Input common-mode high voltage  |                                                          | (VS+) - 1.41 | (VS+) - 1.2 |              | V                  | А                            |

| CMRR             | Common-mode rejection ratio     | Differential, 1-V <sub>PP</sub> input shift, dc          |              | 72          |              | dBc                | С                            |

<sup>(1)</sup> The input resistance and corresponding gain are obtained with the external resistance added.

<sup>(2)</sup> Test levels: (A) 100% tested at 25°C. Overtemperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

# **Electrical Characteristics:** V<sub>S</sub> = 5 V (continued)

At  $T_A$  = 25°C, VS+ = 2.5 V, VS- = -2.5 V,  $V_{CM}$  = 0 V,  $R_L$  = 200- $\Omega$  differential, G = 12 dB (4 V/V), single-ended input, differential output, and  $R_S$  = 50  $\Omega$ , unless otherwise noted. (1)

|                   | PARAMETER                                                                     | TEST                         | CONDITIONS                         | MIN         | TYP         | MAX         | UNIT     | TEST<br>LEVEL <sup>(2)</sup> |

|-------------------|-------------------------------------------------------------------------------|------------------------------|------------------------------------|-------------|-------------|-------------|----------|------------------------------|

| OUTPU             | Γ                                                                             |                              |                                    |             |             |             |          |                              |

|                   | O. da. da. alkana ana alakah                                                  | Measured                     | T <sub>A</sub> = 25°C              | (VS+) - 1.3 | (VS+) - 1.1 |             | V        | А                            |

| V <sub>OCRH</sub> | Output voltage range, high                                                    | single-ended                 | $T_A = -40$ °C to 85°C             |             | (VS+) - 1.2 |             | V        | С                            |

|                   | 0.444                                                                         | Measured                     | T <sub>A</sub> = 25°C              | (VS-) + 1.3 | (VS-) + 1.1 |             | V        | А                            |

| V <sub>OCRL</sub> | Output voltage range, low                                                     | single-ended                 | $T_A = -40$ °C to 85°C             |             | (VS-) + 1.2 |             | V        | С                            |

| V <sub>OD</sub>   | Differential output voltage swing                                             | Differential                 | Differential                       |             | 5.8         |             | $V_{PP}$ | С                            |

| I <sub>OD</sub>   | Differential output current                                                   | $V_O = 0 \ V^{(3)}$          |                                    | 40          | 50          |             | mA       | А                            |

| POWER             | SUPPLY                                                                        |                              |                                    |             |             |             |          |                              |

| Vs                | Supply voltage                                                                |                              |                                    | 3.15        |             | 5.25        | V        | А                            |

| DODD              | B                                                                             | VS-                          |                                    | -50         | -80         |             | dB       | Α                            |

| PSRR              | Power-supply rejection ratio                                                  | VS+                          |                                    | -60         | -82         |             | dB       | А                            |

|                   | 0                                                                             | PD = 0                       |                                    | 50          | 55          | 62          | mA       | Α                            |

| lα                | Quiescent current                                                             | PD = 1                       | PD = 1                             |             | 3           | 6           | mA       | Α                            |

| OUTPU             | COMMON-MODE CONTROL PIN                                                       | (V <sub>CM</sub> )           |                                    |             |             |             |          |                              |

| SSBW              | Small-signal bandwidth                                                        | $V_{OCM} = 100 \text{ mV}_F$ | PP                                 |             | 1.2         |             | GHz      | С                            |

|                   | V <sub>CM</sub> slew rate                                                     | $V_{OCM} = 500 \text{ mV}_F$ | PP                                 |             | 2900        |             | V/µs     | С                            |

|                   | V <sub>CM</sub> voltage range low                                             | Differential gain            | shift < 1 dB                       |             | (VS-) + 1.4 | (VS-) + 2.0 | V        | А                            |

|                   | V <sub>CM</sub> voltage range high                                            | Differential gain            | shift < 1 dB                       | (VS+) - 2.0 | (VS+) - 1.4 |             | V        | А                            |

|                   | V <sub>CM</sub> gain                                                          | V <sub>CM</sub> = 0 V        |                                    | 0.98        | 1.0         | 1.01        | V/V      | Α                            |

|                   | V <sub>OCM</sub> output common-mode offset from V <sub>CM</sub> input voltage | V <sub>CM</sub> = 0 V        |                                    |             | -27         |             | mV       | С                            |

| V <sub>OCM</sub>  | Common-mode offset voltage                                                    | Output-referred              |                                    |             | 0.4         |             | mV       | Α                            |

| POWER             | DOWN (PD Pin)                                                                 |                              |                                    |             |             | *           |          | !                            |

| $V_{T}$           | Enable or disable voltage threshold                                           | Device powers d              | on below 0.8 V,<br>own above 1.2 V | 0.9         | 1.1         | 1.2         | V        | А                            |

|                   | Power-down quiescent current                                                  |                              |                                    | 1           | 3           | 6           | mA       | А                            |

|                   | PD bias current                                                               | PD = 2.5 V                   |                                    |             | 10          | ±100        | μΑ       | С                            |

|                   | Turn-on time delay                                                            | Time to V <sub>O</sub> = 90  | % of final value                   |             | 10          |             | ns       | С                            |

|                   | Turn-off time delay                                                           | Time to $V_O = 10^\circ$     | % of original value                |             | 10          |             | ns       | С                            |

<sup>(3)</sup> This test shorts the outputs to ground (mid supply) then sources or sinks 60 mA and measures the deviation from the initial condition.

## 7.6 Electrical Characteristics: $V_S = 3.3 \text{ V}$

Test conditions are at  $T_A = 25$ °C, VS+ = 1.65 V, VS- = -1.65 V,  $V_{CM} = 0$  V,  $R_L = 200-\Omega$  differential, G = 12 dB (4 V/V), single-ended input and differential output, and input and output referenced to midsupply, unless otherwise noted. Measured using an EVM as discussed in the section.

|                  | PARAMETER                               | TEST CONDITIONS                                            | MIN          | TYP         | MAX          | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|------------------|-----------------------------------------|------------------------------------------------------------|--------------|-------------|--------------|--------------------|------------------------------|

| AC PER           | FORMANCE                                |                                                            |              |             |              |                    |                              |

| GBP              | Gain bandwidth product                  | G = 30 dB (32 V/V)                                         |              | 8           |              | MHz                | С                            |

| SSBW             | Small-signal, -3-dB bandwidth           | $V_O = 200 \text{ mV}_{PP}$                                |              | 6           |              | GHz                | С                            |

| LSBW             | Large-signal, -3-dB bandwidth           | $V_O = 2 V_{PP}$                                           | 4            |             |              | GHz                | С                            |

|                  | Bandwidth for 0.1-dB flatness           | V <sub>O</sub> = 2 V <sub>PP</sub>                         |              | 700         |              | MHz                | С                            |

| SR               | Slew rate                               | 2-V step                                                   |              | 17500       |              | V/µs               | С                            |

|                  | Rise and fall time                      | 1-V step, 10% to 90%                                       |              | 90          |              | ps                 | С                            |

|                  | Overdrive recovery                      | Overdrive = ±0.5 V                                         |              | 400         |              | ps                 | С                            |

|                  | Output balance error                    | f = 1 GHz                                                  |              | 47          |              | dBc                | С                            |

| Z <sub>o</sub>   | Output impedance                        | At dc                                                      | 16           | 20          | 24           | Ω                  | Α                            |

|                  | 0.1% settling time                      | 2 V, R <sub>L</sub> = 200 Ω                                |              | 1           |              | ns                 | С                            |

|                  | ·                                       | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -100        |              | dBc                | С                            |

| LIDO             | Second-order harmonic                   | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -94         |              | dBc                | С                            |

| HD2              | distortion                              | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -78.5       | -78.5        |                    | С                            |

|                  |                                         | f = 1 GHz, V <sub>O</sub> = 1 V <sub>PP</sub>              |              | -58         |              | dBc                | С                            |

|                  | Third-order harmonic distortion         | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -86         |              | dBc                | С                            |

|                  |                                         | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -78         |              | dBc                | С                            |

| HD3              |                                         | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>            |              | -64         |              | dBc                | С                            |

|                  |                                         | f = 1 GHz, V <sub>O</sub> = 1 V <sub>PP</sub>              |              | -52         |              | dBc                | С                            |

|                  | Second-order intermodulation distortion | $f = 100 \text{ MHz}, V_O = 0.5 V_{PP} \text{ per tone}$   |              | -95         |              | dBc                | С                            |

| IMPO             |                                         | f = 200 MHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone |              | -95         |              | dBc                | С                            |

| IMD2             |                                         | f = 500 MHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone | -81          |             | dBc          | С                  |                              |

|                  |                                         | f = 1 GHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone   |              | -66         |              | dBc                | С                            |

|                  | Third-order intermodulation distortion  | $f = 100 \text{ MHz}, V_O = 0.5 V_{PP} \text{ per tone}$   |              | -101        |              | dBc                | С                            |

|                  |                                         | f = 200 MHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone |              | -95         |              | dBc                | С                            |

| IMD3             |                                         | f = 500 MHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone |              | -82         |              | dBc                | С                            |

|                  |                                         | f = 1 GHz, V <sub>O</sub> = 0.5 V <sub>PP</sub> per tone   |              | -66         |              | dBc                | С                            |

| NOISE P          | PERFORMANCE                             |                                                            |              |             |              |                    |                              |

| e <sub>n</sub>   | Input voltage noise density             |                                                            |              | 1.25        |              | nV/√ <del>Hz</del> | С                            |

| in               | Input noise current                     |                                                            |              | 3.5         |              | pA/√ <del>Hz</del> | С                            |

| NF               | Noise figure                            | $R_S = 50 \Omega$ , SE-DE, $G = 12 dB$ , 200 MHz           |              | 9.6         |              | dB                 | С                            |

| INPUT            |                                         |                                                            | •            |             |              |                    |                              |

| Z <sub>id</sub>  | Differential impedance                  |                                                            |              | 4600        |              | Ω                  | С                            |

| V <sub>ICL</sub> | Input common-mode low voltage           |                                                            |              | (VS-)       | (VS-) + 0.41 | V                  | А                            |

| $V_{\rm ICH}$    | Input common-mode high voltage          |                                                            | (VS+) - 1.41 | (VS+) - 1.2 |              | V                  | А                            |

| CMRR             | Common-mode rejection ratio             | Differential, 1-V <sub>PP</sub> input shift, dc            |              | -72         |              | dBc                | С                            |

|                  |                                         |                                                            |              |             |              |                    |                              |

<sup>(1)</sup> Test levels: (A) 100% tested at 25°C. Overtemperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

# **Electrical Characteristics:** V<sub>S</sub> = 3.3 V (continued)

Test conditions are at  $T_A = 25$ °C, VS+ = 1.65 V, VS- = -1.65 V,  $V_{CM} = 0$  V,  $R_L = 200$ - $\Omega$  differential, G = 12 dB (4 V/V), single-ended input and differential output, and input and output referenced to midsupply, unless otherwise noted. Measured using an EVM as discussed in the section.

|                   | PARAMETER                                                                     | TEST (                                                       | CONDITIONS             | MIN          | TYP          | MAX          | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------|--------------|--------------|--------------|----------|------------------------------|

| OUTPUT            | Γ                                                                             |                                                              |                        |              |              | •            |          | •                            |

| V                 | Output valtage range high                                                     | Measured                                                     | T <sub>A</sub> = 25°C  | (VS+) - 1.3  | (VS+) - 1.1  |              | V        | Α                            |

| V <sub>OCRH</sub> | Output voltage range, high                                                    | single-ended                                                 | $T_A = -40$ °C to 85°C |              | (VS+) - 1.2  |              | V        | С                            |

| V <sub>OCRL</sub> | Output voltage range, low                                                     | Measured single-ended                                        | T <sub>A</sub> = 25°C  | (VS-) + 1.3  | (VS-) + 1.1  |              | V        | Α                            |

|                   |                                                                               |                                                              | $T_A = -40$ °C to 85°C |              | (VS-) + 1.2  |              | V        | С                            |

| V <sub>OD</sub>   | Differential output voltage swing                                             | Differential                                                 |                        |              | 2.8          |              | $V_{PP}$ | С                            |

| I <sub>OD</sub>   | Differential output current                                                   | V <sub>O</sub> = 0 V <sup>(2)</sup>                          |                        | 30           | 40           |              | mA       | Α                            |

| POWER             | SUPPLY                                                                        |                                                              |                        |              |              |              |          |                              |

| Vs                | Supply voltage                                                                |                                                              |                        | 3.15         |              | 5.25         | V        | Α                            |

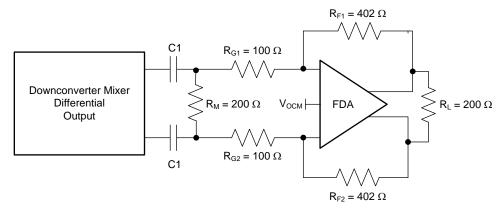

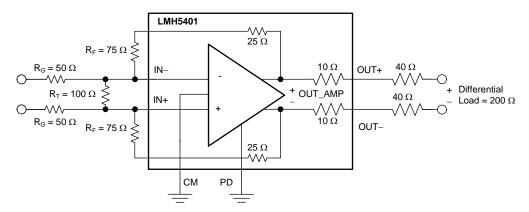

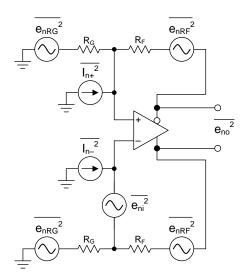

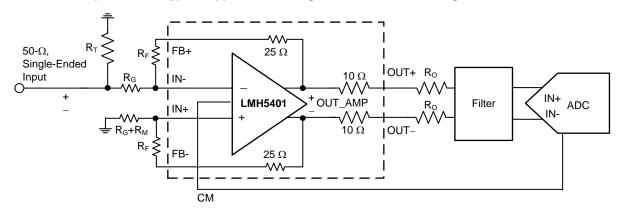

| DODD              | Power-supply rejection ratio                                                  | VS-                                                          |                        | -50          | -80          |              | dB       | Α                            |