Sample &

Buv

#### LM53602, LM53603 SNVSAR0-NOVEMBER 2016

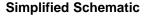

LM53603 (3 A), LM53602 (2 A) 3.5 V to 36 V Wide-V<sub>IN</sub> Synchronous 2.1 MHz Step-Down Converters

Technical

Documents

## 1 Features

- 3-A or 2-A Maximum Load Current

- Input Voltage Range From 3.5 V to 36 V: Transients to 42 V

- Adjustable Output Voltage From 3.3 V to 10 V

- 2.1-MHz Fixed Switching Frequency

- ±2% Output Voltage Tolerance

- -40°C to 150°C Junction Temperature Range

- 1.7-µA Shutdown Current (Typical)

- 24-µA Input Supply Current at No Load (Typical)

- Reset Output With Filter and Delay

- Automatic Light Load Mode for Improved Efficiency

- User-Selectable Forced PWM Mode (FPWM)

- Built-In Loop Compensation, Soft-Start, Current Limit, Thermal Shutdown, UVLO, and External Frequency Synchronization

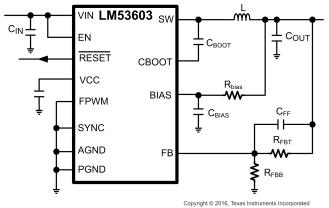

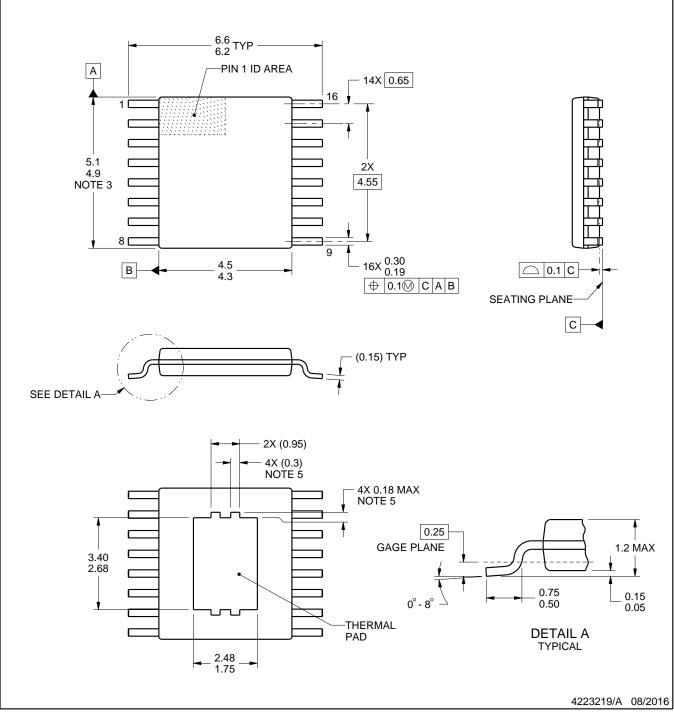

- Thermally Enhanced 16-Lead Package: 5 mm × 4.4 mm × 1 mm

## 2 Applications

- Industrial Power Supplies in Building and Factory Automation

- Battery Operated Devices

- Low-noise and Low-EMI Applications

- Optical Communication Systems

## 3 Description

Tools &

Software

The LM53603 and LM53602 buck regulators are specifically designed for 12-V industrial and automotive applications, providing an adjustable output voltage from 3.3 V to 10 V at 3 A or 2 A, from an input voltage of up to 36 V. Advanced high-speed circuitry allows the device to regulate from an input of up to 20 V, while providing an output of 5 V at a switching frequency of 2.1 MHz. The innovative architecture allows the device to regulate a 3.3-V output from an input voltage of only 3.5 V. All aspects of this product are optimized for the industrial and automotive customer. An input voltage range up to 36 V, with transient tolerance up to 42 V, eases input surge protection design. An open-drain reset output, with filtering and delay, provides a true indication of system status. This feature negates the requirement for an additional supervisory component, saving cost and board space. Seamless transition between PWM and PFM modes, along with a no-load operating current of only 24 µA, ensures high efficiency and superior transient response at all loads.

Support &

Community

## Device Information<sup>(1)</sup>

| PART NUMBER        | PACKAGE     | BODY SIZE (NOM)   |  |  |

|--------------------|-------------|-------------------|--|--|

| LM53603<br>LM53602 | HTSSOP (16) | 5.00 mm x 4.40 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## Industrial Power Supply With 5-V, 3-A Output

Texas Instruments

www.ti.com

# **Table of Contents**

| 1 | Feat | ures 1                            |

|---|------|-----------------------------------|

| 2 | Арр  | lications1                        |

| 3 | Des  | cription 1                        |

| 4 | Rev  | ision History2                    |

| 5 | Dev  | ice Comparison Table 3            |

| 6 | Pin  | Configuration and Functions 3     |

| 7 | Spe  | cifications 4                     |

|   | 7.1  | Absolute Maximum Ratings 4        |

|   | 7.2  | ESD Ratings 4                     |

|   | 7.3  | Recommended Operating Conditions5 |

|   | 7.4  | Thermal Information 5             |

|   | 7.5  | Electrical Characteristics 6      |

|   | 7.6  | System Characteristics7           |

|   | 7.7  | Timing Requirements 8             |

|   | 7.8  | Typical Characteristics 9         |

| 8 | Deta | ailed Description 10              |

|   | 8.1  | Overview 10                       |

|   | 8.2  | Functional Block Diagram 10       |

|   | 8.3  | Feature Description 11            |

|   | 8.4  | Device Functional Modes 15        |

| 9  | Арр  | lication and Implementation                       | 18 |

|----|------|---------------------------------------------------|----|

|    | 9.1  | Application Information                           | 18 |

|    | 9.2  | Typical Applications                              | 18 |

|    | 9.3  | Typical Adjustable Industrial Application Circuit | 28 |

|    | 9.4  | Do's and Don't's                                  | 28 |

| 10 | Pow  | ver Supply Recommendations                        | 29 |

| 11 | Lay  | out                                               | 30 |

|    | 11.1 | Layout Guidelines                                 | 30 |

|    | 11.2 | Layout Example                                    | 32 |

| 12 | Dev  | ice and Documentation Support                     | 33 |

|    | 12.1 | Device Support                                    | 33 |

|    | 12.2 | Documentation Support                             | 33 |

|    | 12.3 | Related Links                                     | 33 |

|    | 12.4 | Receiving Notification of Documentation Updates   | 34 |

|    | 12.5 | Community Resources                               | 34 |

|    | 12.6 | Trademarks                                        | 34 |

|    | 12.7 | Electrostatic Discharge Caution                   | 34 |

|    | 12.8 | Glossary                                          | 34 |

| 13 | Mec  | hanical, Packaging, and Orderable                 |    |

|    | Info | rmation                                           | 34 |

|    |      |                                                   |    |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| November 2016 | *        | Initial release. |

## 5 Device Comparison Table

| PART NUMBER <sup>(1)</sup> | OUTPUT VOLTAGE | MAXIMUM OUTPUT<br>CURRENT | PACKAGE QTY |

|----------------------------|----------------|---------------------------|-------------|

| LM53603AMPWPR              | Adjustable     | 3 A                       | 2000        |

| LM53603AMPWPT              | Adjustable     | 3 A                       | 250         |

| LM53602AMPWPR              | Adjustable     | 2 A                       | 2000        |

| LM53602AMPWPT              | Adjustable     | 2 A                       | 250         |

(1) Some text and images in this datasheet refer to fixed 3.3-V or 5-V output devices which are only available in the automotive grade version of this device as the LM53603-Q1 and LM53602-Q1. Refer to the automotive datasheet for more information on those output voltage options.

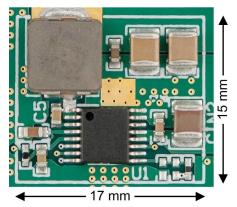

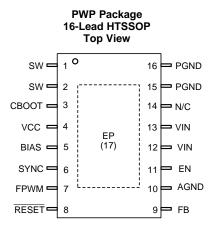

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN    |       | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                         |

|--------|-------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME  | 100                | DESCRIPTION                                                                                                                                                                                                                         |

| 1, 2   | SW    | Р                  | Regulator switch node. Connect to power inductor. Connect pins 1 and 2 directly together at the PCB.                                                                                                                                |

| 3      | CBOOT | Р                  | Bootstrap supply input for gate drivers. Connect a high-quality, 470-nF capacitor from this pin to SW.                                                                                                                              |

| 4      | VCC   | 0                  | Internal 3.15-V regulator output. Used as supply to internal control circuits. Do not connect to any external loads. Can be used as logic supply for control inputs. Connect a high-quality, 3.3-µF capacitor from this pin to GND. |

| 5      | BIAS  | Ρ                  | Input to internal voltage regulator. Connect to output voltage point. Do not ground. Connect a high-<br>quality, 0.1-µF capacitor from this pin to GND.                                                                             |

| 6      | SYNC  | Ι                  | Synchronization input to regulator. Used to synchronize the regulator switching frequency to the system clock. When not used connect to GND; do not float.                                                                          |

| 7      | FPWM  | Ι                  | Mode control input to regulator. High = forced PWM (FPWM). Low = auto mode; automatic transition between PFM and PWM. Do not float.                                                                                                 |

| 8      | RESET | 0                  | Open-drain reset output. Connect to suitable voltage supply through a current limiting resistor. High = power OK. Low = fault. RESET goes low when EN = low.                                                                        |

| 9      | FB    | Ι                  | Feedback input to regulator. Connect to output voltage sense point for fixed 5-V and 3.3-V output. Connect to feedback divider tap point for ADJ option. Do not float or ground.                                                    |

| 10     | AGND  | G                  | Analog ground for regulator and system. All electrical parameters are measured with respect to this pin. Connect to EP and PGND on PCB.                                                                                             |

| 11     | EN    | Ι                  | Enable input to the regulator. High = ON. Low = OFF. Can be connected directly to VIN. Do not float.                                                                                                                                |

| 12, 13 | VIN   | Ρ                  | Input supply to the regulator. Connect a high-quality bypass capacitor(s) from this pin to PGND. Connect pins 12 and 13 directly together at the PCB.                                                                               |

| 14     | N/C   | _                  | This pin has no connection to the device.                                                                                                                                                                                           |

(1) O = Output, I = Input, G = Ground, P = Power

3

STRUMENTS

XAS

### **Pin Functions (continued)**

| F      | IN   | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                       |  |

|--------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| NO.    | NAME | 1/0 ( )            | DESCRIPTION                                                                                                                       |  |

| 15, 16 | PGND | G                  | Power ground to internal low-side MOSFET. Connect to AGND and system ground. Connect pins 15 and 16 directly together at the PCB. |  |

| 17     | EP   | G                  | Exposed die attach paddle. Connect to ground plane for adequate heat sinking and noise reduction.                                 |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                              | MIN  | MAX                   | UNIT |

|----------------------------------------|------|-----------------------|------|

| VIN to AGND, PGND <sup>(2)</sup>       | -0.3 | 40                    | V    |

| SW to AGND, PGND <sup>(3)</sup>        | -0.3 | V <sub>IN</sub> + 0.3 | V    |

| CBOOT to SW                            | -0.3 | 3.6                   | V    |

| EN to AGND, PGND <sup>(2)</sup>        | -0.3 | 40                    | V    |

| BIAS to AGND, PGND                     | -0.3 | 16                    | V    |

| FB to AGND, PGND : fixed 5 V and 3.3 V | -0.3 | 16                    | V    |

| FB to AGND, PGND : ADJ                 | -0.3 | 5.5                   | V    |

| RESET to AGND, PGND                    | -0.3 | 8                     | V    |

| SYNC, FPWM, to AGND, PGND              | -0.3 | 5.5                   | V    |

| VCC to AGND, PGND                      | -0.3 | 4.2                   | V    |

| RESET pin current <sup>(4)</sup>       | -0.1 | 1.2                   | mA   |

| AGND to PGND <sup>(5)</sup>            | -0.3 | 0.3                   | V    |

| Storage temperature, T <sub>stg</sub>  | -40  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. Values given are D.C.

(2) A maximum of 42 V can be sustained at this pin for a duration of  $\leq$  500 ms at a duty cycle of  $\leq$  0.01%.

(3) Transients on this pin, not exceeding –3 V or +40 V, can be tolerated for a duration of ≤ 100 ns. For transients between 40 V and 42 V, see note <sup>(2)</sup>.

(4) Positive current flows into this pin.

(5) A transient voltage of  $\pm 2$  V can be sustained for  $\leq 1$  µs.

## 7.2 ESD Ratings

|                                               |                    |                                                 |                            | VALUE | UNIT |

|-----------------------------------------------|--------------------|-------------------------------------------------|----------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic<br>discharge |                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS- | Pins 1, 2, 3, 12, 13,      | ±1500 |      |

|                                               | 001 <sup>(1)</sup> | Pins 11, 5, 8, 9, 6, 7, 4                       | ±2500                      |       |      |

|                                               |                    | Pins 3, 4, 5, 6, 7, 11, 12<br>and 13            | ±750                       | V     |      |

|                                               |                    |                                                 | Pins 1, 2, 8, 9, 15 and 16 | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)

|                                                        | MIN | NOM | MAX | UNIT |

|--------------------------------------------------------|-----|-----|-----|------|

| Input voltage <sup>(1)</sup>                           | 3.9 |     | 36  | V    |

| Output voltage : fixed 5 V <sup>(2)</sup>              | 0   | 5   |     | V    |

| Output voltage : fixed 3.3 V <sup>(2)</sup>            | 0   | 3.3 |     | V    |

| Output voltage adjustment range: ADJ <sup>(2)(3)</sup> | 3.3 |     | 10  | V    |

| Output current for LM53603                             | 0   |     | 3   | А    |

| Output current for LM53602                             | 0   |     | 2   | А    |

| RESET pin current                                      | 0   |     | 1   | mA   |

| Operating junction temperature <sup>(4)</sup>          | -40 |     | 150 | °C   |

(1) See *System Characteristics* for details of input voltage range.

(2) Under no conditions should the output voltage be allowed to fall below zero volts.

(3) An extended output voltage range to 10 V is possible with changes to the typical application schematic. Also, some system

specifications are not achieved for output voltages greater than 6 V. Consult the factory for further information.

(4) High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

## 7.4 Thermal Information

|                       | <i>w</i>                                     | LM53603,<br>LM53602 |      |

|-----------------------|----------------------------------------------|---------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP)        | UNIT |

|                       |                                              | 16 PINS             |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 42.5                | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 22.6                | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 16.2                | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.6                 | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 16.0                | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1                 | °C/W |

(1) The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD 51-7, and simulated on a 4-layer JEDEC board. They do not represent the performance obtained in an actual application. For design information please see the *Maximum Ambient Temperature* section. For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report and the *Using New Thermal Metrics* (SBVA025) application report.

## 7.5 Electrical Characteristics

Limits apply to the recommended operating junction temperature range of -40°C to 150°C, unless otherwise noted. Minimum and maximum limits are verified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at T<sub>1</sub> = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5 V.$

|                             | PARAMETER                                                             | TEST CONDITIONS                                                                                            | MIN <sup>(1)</sup> | TYP   | MAX <sup>(1)</sup> | UNIT |

|-----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|-------|--------------------|------|

| V <sub>FB</sub>             | Initial reference voltage accuracy                                    | $V_{IN}$ = 3.8 V to 36 V, FPWM,<br>T <sub>J</sub> = 25°C                                                   | -1%                |       | 1%                 |      |

| 1 D                         | for 5-V and 3.3-V options                                             | V <sub>IN</sub> = 3.8 V to 36 V, FPWM                                                                      | -1.25%             |       | 1.25%              |      |

|                             |                                                                       | $V_{IN} = 3.8 \text{ V to } 36 \text{ V}, \text{ FPWM},$<br>T <sub>J</sub> = 25°C                          | 0.993              | 1     | 1.007              | V    |

| V <sub>REF</sub>            | Reference voltage for ADJ option                                      | $V_{IN} = 3.8 V \text{ to } 36 V, \text{ FPWM}, T_J = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | 0.99               | 1     | 1.01               | V    |

|                             |                                                                       | Rising                                                                                                     | 3.2                |       | 3.95               |      |

| V <sub>IN-operate</sub>     | Minimum input voltage to<br>operate <sup>(2)</sup>                    | Falling                                                                                                    | 2.9                |       | 3.55               | V    |

|                             | operate                                                               | Hysteresis, below                                                                                          | 0.34               |       |                    |      |

| l <sub>Q</sub>              | Operating quiescent current;<br>measured at VIN pin <sup>(3)(4)</sup> | V <sub>BIAS</sub> = 5 V,<br>T <sub>J</sub> = -40°C to 125°C                                                |                    | 8     | 13                 | μA   |

| I                           | Shutdown quiescent current;                                           | EN ≤ 0.4 V, T <sub>J</sub> = 25°C                                                                          |                    | 1.7   |                    |      |

| I <sub>SD</sub>             | measured at VIN pin                                                   | EN ≤ 0.4 V, T <sub>J</sub> = 125°C                                                                         |                    |       | 3.5                | μA   |

| I <sub>B</sub>              | Current into the BIAS pin <sup>(4)</sup>                              | V <sub>BIAS</sub> = 5 V, FPWM = 3.3 V                                                                      |                    | 47    | 78                 | μA   |

| I <sub>EN</sub>             | Current into EN pin                                                   | V <sub>IN</sub> = V <sub>EN</sub> = 13.5 V                                                                 |                    | 2.3   |                    | μA   |

| I <sub>FB</sub>             | Bias current into FB pin                                              | ADJ option                                                                                                 |                    | 10    |                    | nA   |

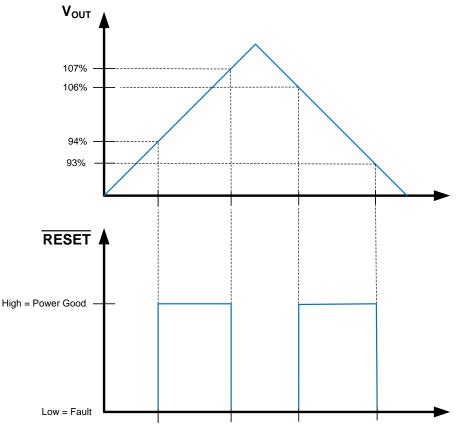

| V <sub>RESET</sub>          | RESET upper threshold voltage                                         | Rising, % of nominal V <sub>out</sub>                                                                      | 105%               | 107%  | 110%               |      |

|                             | RESET lower threshold voltage                                         | Falling, % of nominal V <sub>out</sub>                                                                     | 92%                | 94%   | 96.5%              |      |

|                             | RESET lower threshold voltage with respect to output voltage          | Falling, % actual V <sub>out</sub>                                                                         |                    | 94.5% | 95.7%              |      |

| V <sub>RESET-</sub><br>Hyst | RESET hysteresis as a percent of output voltage set point             |                                                                                                            |                    | 1.5%  |                    |      |

| V <sub>MIN</sub>            | Minimum input voltage for proper<br>RESET function                    | 50- $\mu$ A pullup to RESET pin, V <sub>EN</sub> = 0 V,<br>T <sub>J</sub> = 25°C                           |                    |       | 1.5                | V    |

|                             |                                                                       | 50- $\mu$ A pullup to RESET pin, V <sub>in</sub> = 1.5 V, EN = 0 V                                         |                    |       | 0.4                |      |

| V <sub>OL</sub>             | Low level RESET pin output voltage                                    | 0.5-mA pullup to $\overline{\text{RESET}}$ pin, $V_{\text{in}}$ = 13.5 V, EN = 0 V                         |                    |       | 0.4                | V    |

|                             |                                                                       | 1-mA pullup to $\overline{\text{RESET}}$ pin, V <sub>in</sub> = 13.5 V, EN = 3.3 V                         |                    |       | 0.4                |      |

| V                           | Enable input threshold voltage                                        | Rising                                                                                                     | 1.7                |       | 2                  | V    |

| V <sub>EN</sub>             |                                                                       | Hysteresis, below                                                                                          | 0.45               |       | 0.55               | v    |

| V <sub>EN-off</sub>         | Enable input threshold for full shutdown <sup>(5)</sup>               | EN input voltage required for complete shutdown of the regulator, falling.                                 | 0.8                |       |                    | V    |

|                             | Logic input levels on FPWM and                                        | V <sub>IH</sub>                                                                                            | 1.5                |       |                    | V    |

| V <sub>LOGIC</sub>          | SYNC pins                                                             | V <sub>IL</sub>                                                                                            |                    |       | 0.4                | V    |

|                             | High aide quitch current limit                                        | LM53603                                                                                                    | 4.5                |       | 6.2                | ٨    |

| HS                          | High-side switch current limit                                        | LM53602                                                                                                    | 2.4                |       | 4.4                | A    |

| I                           | Low aide owitch ourrent list (6)                                      | LM53603                                                                                                    | 3                  | 3.6   | 4.3                | ٨    |

| I <sub>LS</sub>             | Low-side switch current limit <sup>(6)</sup>                          | LM53602                                                                                                    | 2                  | 2.4   | 2.8                | A    |

(1) Minimum and maximum limits are 100% production tested at 25°C. Limits over the operating temperature range are verified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) This is the input voltage at which the device starts to operate (rising). The device shuts down when the input voltage goes below this value minus the hysteresis.

This is the current used by the device, open loop. It does not represent the total input current of the system when in regulation. See (3) $I_{supply}$  in System Characteristics The FB pin is set to 5.5 V for this test.

(4)

(5) Below this voltage on the EN input, the device shuts down completely.

(6) See the Current Limit section for an explanation of valley current limit.

6 Submit Documentation Feedback

## **Electrical Characteristics (continued)**

Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are verified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 13.5$  V.

| PARAMETER                            |                                  | TEST CONDITIONS             | MIN <sup>(1)</sup>              | TYP   | MAX <sup>(1)</sup> | UNIT |  |

|--------------------------------------|----------------------------------|-----------------------------|---------------------------------|-------|--------------------|------|--|

| I <sub>ZC</sub>                      | Zero-cross current limit         | FPWM = 0 V                  |                                 | -0.02 |                    | А    |  |

| I <sub>NEG</sub>                     | Negative current limit           | FPWM = 3.3 V                |                                 | -1.5  |                    | А    |  |

| R <sub>dson</sub> Power switch on-re | Dower owitch on registeres       | High-side MOSFET resistance |                                 | 135   | 290                |      |  |

|                                      | Power switch on-resistance       | Low-side MOSFET resistance  |                                 | 60    | 125                | mΩ   |  |

| -                                    |                                  | Curitatian francisco au     | V <sub>IN</sub> = 3.8 V to 18 V | 1.85  | 2.1                | 2.35 |  |

| F <sub>SW</sub>                      | Switching frequency              | V <sub>IN</sub> = 36 V      |                                 | 1.2   |                    | MHz  |  |

| F <sub>SYNC</sub>                    | Synchronizing frequency range    |                             | 1.9                             | 2.1   | 2.3                | MHz  |  |

| V <sub>CC</sub>                      | Internal V <sub>CC</sub> voltage | $V_{BIAS} = 3.3 V$          |                                 | 3.15  |                    | V    |  |

| -                                    |                                  | Rising                      | 162                             |       | 178                | °C   |  |

| T <sub>SD</sub>                      | Thermal shutdown thresholds      | Hysteresis, below           | 18                              |       |                    |      |  |

## 7.6 System Characteristics

The following specifications apply only to the typical application circuit, shown in Figure 15 with nominal component values. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. The parameters in this table are not ensured.

|                     | PARAMETER                                             | TEST CONDITIONS                                                                                         | MIN      | TYP     | MAX | UNIT |  |

|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------|---------|-----|------|--|

| V                   | Minimum input voltage for V <sub>out.</sub> to        | $V_{OUT} = 3.3 \text{ V}, I_{OUT} = 3 \text{ A}$                                                        |          | 3.9     |     | V    |  |

| V <sub>IN-MIN</sub> | stay within ±2% of regulation <sup>(1)</sup>          | $V_{OUT}$ = 3.3 V, $I_{OUT}$ = 1 A                                                                      |          | 3.55    |     | v    |  |

|                     |                                                       | $V_{OUT}$ = 5 V, $V_{IN}$ = 8 V to 36 V, $I_{OUT}$ = 3 A                                                |          | 7       |     |      |  |

|                     | Line Regulation                                       | $V_{OUT}$ = 3.3 V, $V_{IN}$ = 6 V to 36 V, $I_{OUT}$ = 3 A                                              |          | 5       |     | mV   |  |

|                     | Lood Domilation - Auto Made                           | $V_{OUT}$ = 5 V, $V_{IN}$ = 12 V, $I_{OUT}$ = 10 µA to 3 A                                              |          | 77      |     |      |  |

| Regulation          | Load Regulation : Auto Mode                           | <b>V<sub>OUT</sub> = 3.3 V</b> , $V_{IN}$ = 12 V, $I_{OUT}$ = 10 µA to 3 A                              |          | 53      |     | mV   |  |

|                     | Lead Derivation - EDW/M Made                          | $V_{OUT}$ = 5 V, $V_{IN}$ = 12 V, $I_{OUT}$ = 10 µA to 3 A                                              |          | 12<br>9 |     | mV   |  |

|                     | Load Regulation : FPWM Mode                           | <b>V<sub>OUT</sub> = 3.3 V</b> , $V_{IN}$ = 12 V, $I_{OUT}$ = 10 µA to 3 A                              |          |         |     |      |  |

| 1                   | Input supply current when in                          | $V_{IN} = 13.5 \text{ V}, V_{OUT} = 3.3 \text{ V}, I_{OUT} = 0 \text{ A}$                               | = 0 A 24 |         |     | μA   |  |

| ISUPPLY             | regulation <sup>(2)</sup>                             | $V_{IN} = 13.5 \text{ V}, V_{OUT} = 5 \text{ V}, I_{OUT} = 0 \text{ A}$                                 |          | 34      |     |      |  |

|                     |                                                       | 5-V Option: $V_{OUT}$ = 4.95 V, I <sub>OUT</sub> = 3 A, F <sub>SW</sub> < 1.85 MHz                      |          | 0.7     |     |      |  |

|                     |                                                       | <b>5-V Option:</b><br>V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 3 A, F <sub>SW</sub> = 1.85 MHz        |          | 1.8     |     |      |  |

| V <sub>DROP</sub>   | Dropout voltage (V <sub>IN</sub> – V <sub>OUT</sub> ) | <b>3.3-V Option:</b><br>V <sub>OUT</sub> = 3.27 V, I <sub>OUT</sub> = 3 A, F <sub>SW</sub> < 1.85 MHz   |          | 0.65    |     | V    |  |

|                     |                                                       | <b>3.3-V Option:</b><br>V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 3 A, F <sub>SW</sub> = 1.85<br>MHz |          | 1.8     |     |      |  |

(1) This parameter is valid once the input voltage has risen above  $V_{IN-operate}$  and the device has started up.

(2) Includes current into the EN pin, but does not include current due to the external resistive divider in adjustable output versions. See Input Supply Current section.

## 7.7 Timing Requirements

Limits apply to the recommended operating junction temperature range of  $-40^{\circ}$ C to  $150^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are verified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at T<sub>J</sub> = 25°C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply: VIN = 13.5 V.

|                           |                                                             | MIN | NOM | MAX | UNIT |

|---------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| T <sub>ON</sub>           | Minimum switch on-time, $V_{IN} = 20 V$                     |     | 50  | 80  | ns   |

| T <sub>OFF</sub>          | Minimum switch off-time, $V_{IN} = 3.8 V$                   |     | 125 | 200 | ns   |

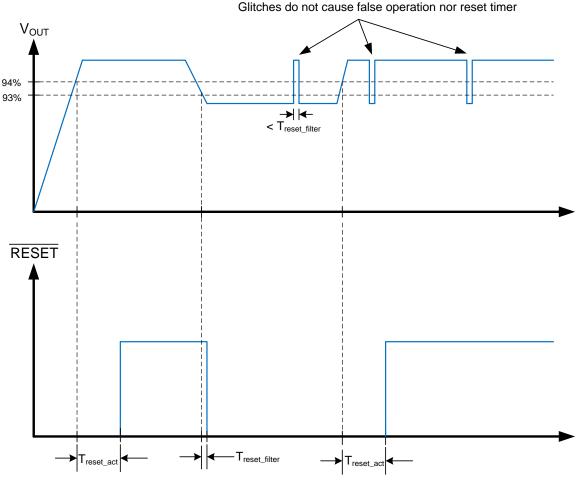

| T <sub>RESET-act</sub>    | Delay time to RESET high signal                             | 2   | 3   | 4   | ms   |

| T <sub>RESET-filter</sub> | Glitch filter time for RESET function                       | 12  | 25  | 45  | μs   |

| T <sub>SS</sub>           | Soft-start time                                             | 1   | 2   | 3   | ms   |

| T <sub>EN</sub>           | Turnon delay, $C_{VCC}$ = 1 µF, $T_J$ = 25°C <sup>(1)</sup> |     | 1   |     | ms   |

| T <sub>W</sub>            | Short-circuit wait time (Hiccup time)                       |     | 5.5 |     | ms   |

(1) This is the time from the rising edge of EN to the time that the soft-start ramp begins.

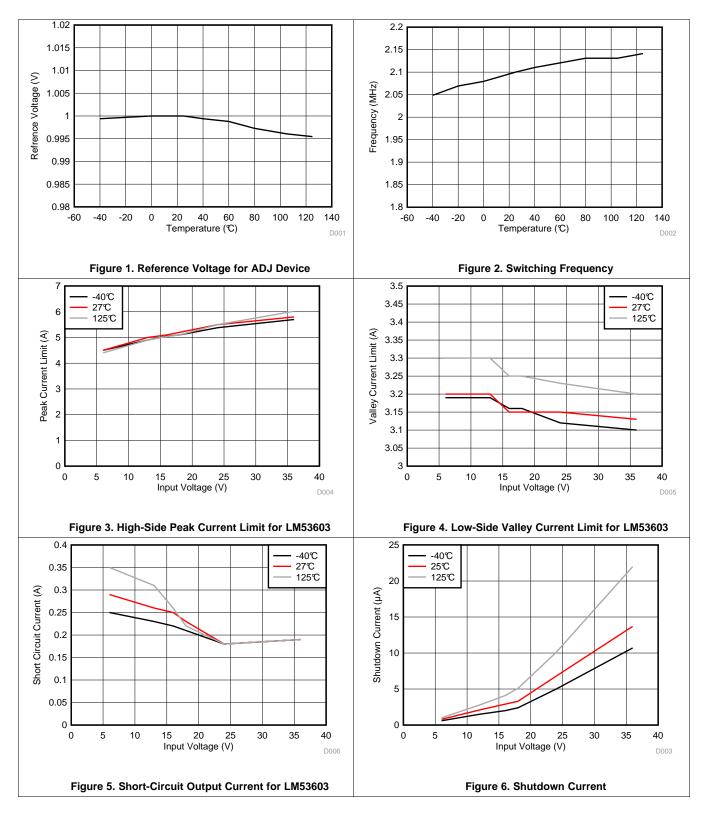

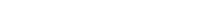

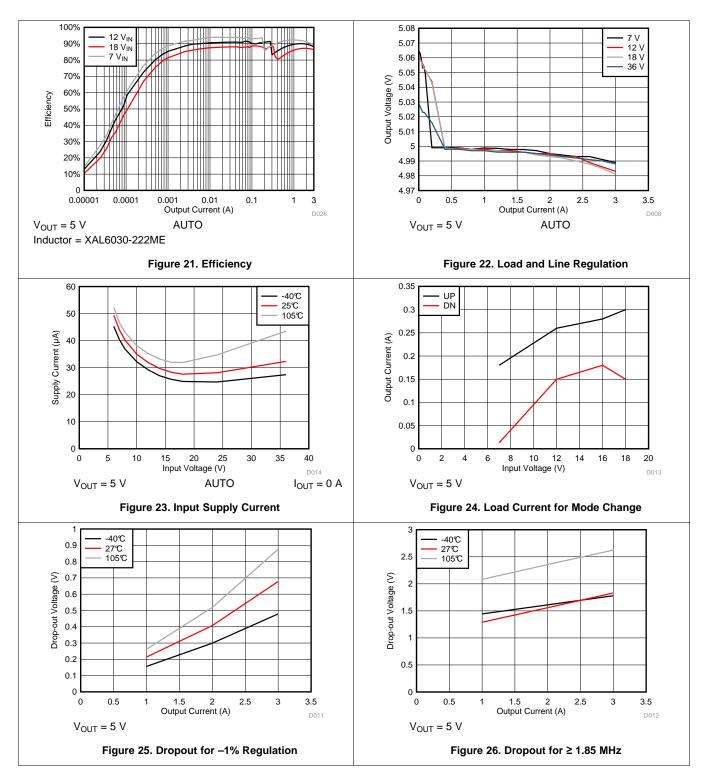

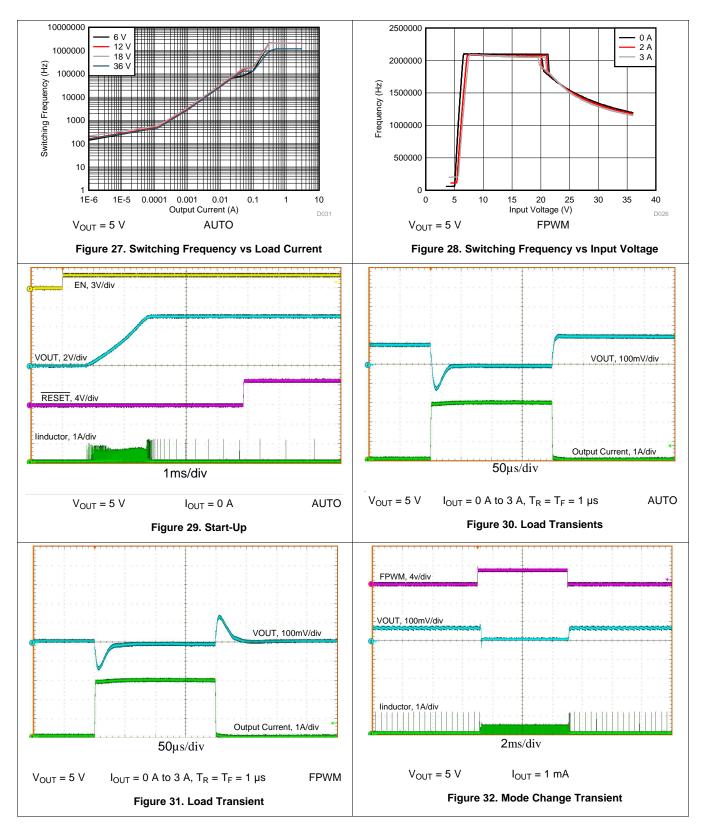

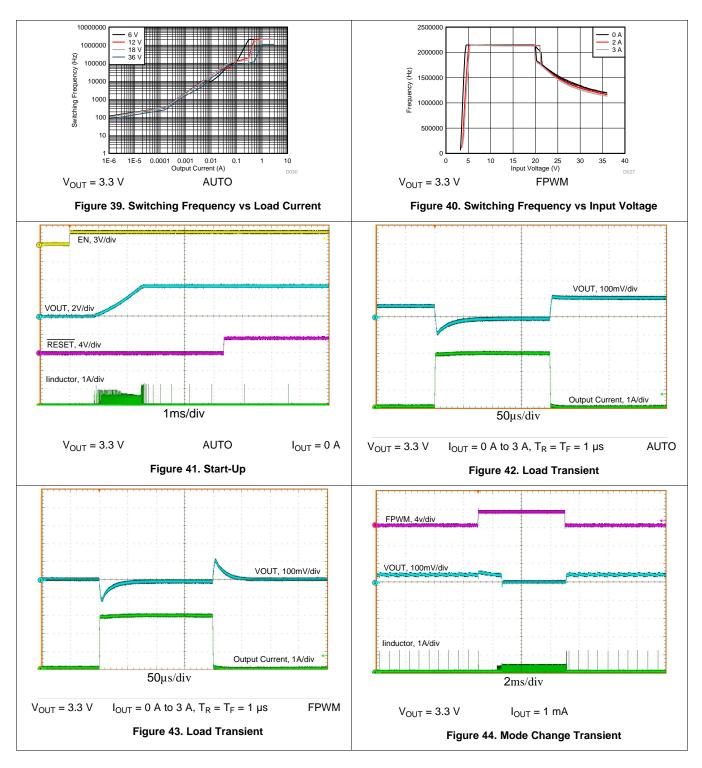

## 7.8 Typical Characteristics

Unless otherwise specified the following conditions apply:  $V_{IN}$  = 12 V,  $T_A$  = 25°C. Specified temperatures are ambient.

TEXAS INSTRUMENTS

<u>www.ti.</u>com

## 8 Detailed Description

### 8.1 Overview

The LM5360x family of devices are synchronous current mode buck regulators designed specifically for the Wide Input voltage Industrial and automotive market. The regulator automatically switches between PWM and PFM depending on load. At heavy loads the device operates in PWM at a switching frequency of 2.1 MHz. The regulator's oscillator can also be synchronized to an external system clock. At input voltages above about 20 V, the switching frequency reduces to maintain regulation during conditions of abnormally high battery voltage. At light loads the mode changes to PFM, with diode emulation allowing DCM. This reduces input supply current and keeps the efficiency high. The user can also choose to lock the mode in PWM (FPWM) so that the switching frequency remains constant regardless of load.

A RESET flag is provided to indicate when the output voltage is near its regulation point. This feature includes filtering and a delay before asserting. This helps to prevent false flag operation during output voltage transients.

Note that, throughout this data sheet, references to the LM53603 apply equally to the LM53602. The difference between the two devices is the maximum output current and specified MOSFET current limits.

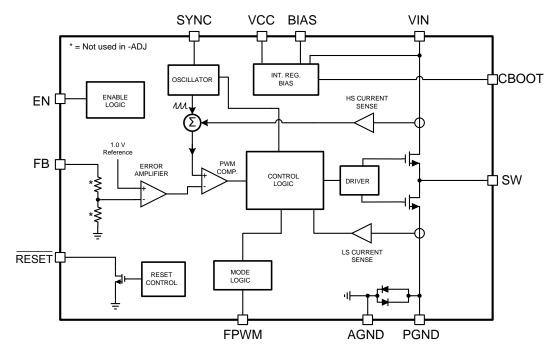

### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 8.3 Feature Description

## 8.3.1 RESET Flag Output

LM53602, LM53603 SNVSAR0-NOVEMBER 2016

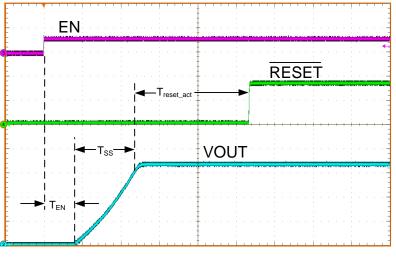

function. A glitch filter prevents false flag operation for short excursions in the output voltage, such as during line and load transients. Furthermore, there is a delay between the point at which the output voltage is within specified limits and the flag asserts Power Good. Because the RESET comparator and the regulation loop share the same reference, the thresholds track with the output voltage. This allows the LM53603 to be specified with a 96.5% maximum threshold, while at the same time specifying a 95% threshold with respect to the actual output voltage for that device. This allows tighter tolerance than is possible with an external supervisor device. The net result is a more accurate power-good function while expanding the system allowance for transients, and so forth. RESET operation can best be understood by reference to Figure 7 and Figure 8. The values for the various filter and delay times can be found in the *Timing Requirements* table. Output voltage excursions lasting less than T<sub>RESET-filter</sub>, do not trip RESET. Once the output voltage is within the prescribed limits, a delay of T<sub>RESET-act</sub> is imposed before RESET goes high.

This output consists of an open-drain NMOS; requiring an external pullup resistor to a suitable logic supply. It can also be pulled up to either VCC or V<sub>OUT</sub>, through an appropriate resistor, as desired. If this function is not needed, the pin should be left floating or grounded. When EN is pulled low, the flag output is also forced low. With EN low, RESET remains valid as long as the input voltage is  $\geq$  1.5 V. The maximum current into this pin should be limited to 1 mA, while the maximum voltage should be less than 8 V.

Figure 7. Static RESET Operation

## Feature Description (continued)

#### 8.3.2 Enable and Start-Up

Start-up and shutdown of the LM53603 are controlled by the EN input. Applying a voltage of  $\ge 2$  V activates the device, while a voltage of  $\le 0.8$  V is required to shut it down. The EN input may also be connected directly to the input voltage supply, if this feature is not needed. This input must not be left floating. The LM53603 uses a reference based soft-start, that prevents output voltage overshoots and large inrush currents as the regulator is starting up. A typical start-up waveform is shown in Figure 9 along with typical timings.

## Feature Description (continued)

1ms/div

Figure 9. Typical Start-Up Waveform

### 8.3.3 Current Limit

The LM53603 incorporates valley current limit for normal overloads and for short-circuit protection. In addition, the low side switch is also protected from excessive negative current when the device is in FPWM mode. Finally, a high-side peak current limit is employed for protection of the top NMOS FET.

During overloads the low-side current limit,  $I_{LS}$  (see *Electrical Characteristics*), determines the maximum load current that the LM53603 can supply. When the low-side switch turns on, the inductor current begins to ramp down. If the current does not fall below  $I_{LS}$  before the next turnon cycle, then that cycle is skipped and the low-side FET is left on until the current falls below  $I_{LS}$ . This is somewhat different than the more typical peak current limit, and results in Equation 1 for the maximum load current.

$$I_{OUT}\big|_{max} = I_{LS} + \frac{(V_{IN} - V_{OUT})}{2 \cdot F_{S} \cdot L} \cdot \frac{V_{OUT}}{V_{IN}}$$

(1)

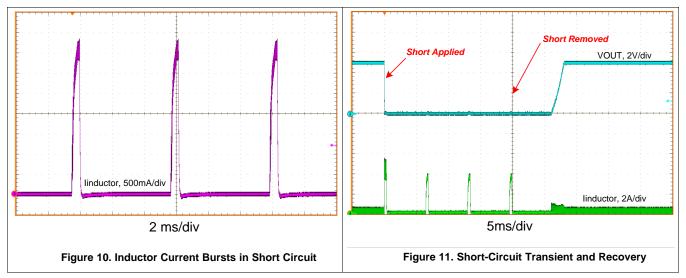

If the above situation persists for more than about 64 clock cycles, the device turns off both high-side and lowside switches for approximately 5.5 ms (see  $T_W$  in *Timing Requirements*). If the overload is still present after the *hiccup* time, another 64 cycles is counted and the process is repeated. If the current limit is not tripped for two consecutive clock cycles, the counter is reset. Figure 10 shows the inductor current with a hard short on the output. The *hiccup* time allows the inductor current to fall to zero, resetting the inductor volt-second balance. This is the method used for short-circuit protection and keeps the power dissipation low during a fault. Of course the output current is greatly reduced in this condition (see *Typical Characteristics*). A typical short-circuit transient and recovery is shown in Figure 11.

#### LM53602, LM53603 SNVSAR0-NOVEMBER 2016

www.ti.com

## Feature Description (continued)

The high-side current limit trips when the peak inductor current reaches  $I_{HS}$  (see *Electrical Characteristics*). This is a cycle-by-cycle current limit and does not produce any frequency or current fold-back. It is meant to protect the high-side MOSFET from excessive current. Under some conditions, such as high input voltage, this current limit may trip before the low-side protection. The peak value of this current limit varies with duty-cycle.

In FPWM mode, the inductor current is allowed to go negative. Should this current exceed  $I_{NEG}$ , the low-side switch is turned off until the next clock cycle. This is used to protect the low-side switch from excessive negative current. When the device is in AUTO mode, the negative current limit is increased to about 0 A;  $I_{ZC}$ . This allows the device to operate in DCM.

## 8.3.4 Synchronizing Input

The internal clock of the LM53603 can be synchronized to a system clock through the SYNC input. This input recognizes a valid high level as that  $\geq$  1.5 V, and a valid low as that  $\leq$  0.4 V. The frequency synchronization signal should be in the range of 1.9 MHz to 2.3 MHz with a duty cycle of from 10% to 90%. The internal clock is synced to the rising edge of the external clock. If this input is not used, it should be grounded. The maximum voltage on this input is 5.5 V; and should not be allowed to float. See the *Device Functional Modes* section to determine which modes are valid for synchronizing the clock.

## 8.3.5 Input Supply Current

The LM53603 is designed to have very low input supply current when regulating light loads. One way this is achieved is by powering much of the internal circuitry from the output. The BIAS pin is the input to the LDO that powers the majority of the control circuits. By connecting the BIAS input to the output of the regulator, this current acts as a small load on the output. This current is reduced by the ratio of  $V_{OUT}/V_{IN}$ , just like any other load. Another advantage of the LM53603 is that the feedback divider is integrated into the device. This allows the use of much larger resistors than can be used externally; >> 100 k $\Omega$ . This results in much lower divider current than is possible with external resistors. Equation 2 can be used to estimate the total input supply current when the device is regulating with no external loads. The terms of the equation are as follows:

- I<sub>IN</sub>: Input supply current with no load.

- I<sub>Q</sub>: Device quiescent current, see *Electrical Characteristics*.

- I<sub>EN</sub>: Current into EN pin; see *Electrical Characteristics*.

- I<sub>B</sub>: Current into BIAS pin; see *Electrical Characteristics*.

- K: ≈ 0.9

$$\mathbf{I_{IN}} = \mathbf{I_Q} + \mathbf{I_{EN}} + \frac{\mathbf{V_{OUT}}}{\mathbf{V_{IN}} \cdot \mathbf{K}} \cdot \left(\mathbf{I_B} + \frac{\mathbf{V_{OUT}}}{\mathbf{R_{FB}}}\right)$$

(2)

### Feature Description (continued)

Equation 2 can be used as a guide to indicate how the various terms affect the input supply current. The *Application Curves* show measured values for the input supply current for both 3.3-V and 5-V output voltage versions.

### 8.3.6 UVLO and TSD

The LM53603 incorporates an input undervoltage lockout (UVLO) function. The device accepts an EN command when the input voltage rises above about 3.64 V and shuts down when the input falls below about 3.3 V. See the *Electrical Characteristics* table under  $V_{IN-operate}$  for detailed specifications.

Thermal shutdown is provided to protect the device from excessive temperature. When the junction temperature reaches about 162°C, the device shuts down; restart occurs at a temperature of about 144°C.

### 8.4 Device Functional Modes

See Table 1 and the following paragraphs for a detailed description of the functional modes for the LM53603. These modes are controlled by the FPWM input as shown in Table 1. This input can be controlled by any compatible logic, and the mode changed while the regulator is operating. If it is desired to lock the mode for a given application, the input can be either connected to ground, a logic supply, or the VCC pin, as desired. The maximum input voltage on this pin is 5.5 V and it should not be allowed to float.

| FPWM INPUT VOLTAGE | OPERATING MODE                                                                                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| > 1.5 V            | Forced PWM: The regulator operates as a constant frequency, current mode, full-<br>synchronous converter for all loads; without diode emulation. |

| < 0.4 V            | AUTO: The regulator moves between PFM and PWM as the load current changes, using diode-emulation-mode to allow DCM (see the <i>Glossary</i> ).   |

#### Table 1. Mode Selection

#### 8.4.1 AUTO Mode

In AUTO mode the device moves between PWM and PFM as the load changes. At light loads the regulator operates in PFM. At higher loads the mode changes to PWM. The load currents for which the devices moves from PWM to PFM can be found in the *Application Curves*.

In PWM, the converter operates as a constant frequency, current mode, full synchronous converter using PWM to regulate the output voltage. While operating in this mode the output voltage is regulated by switching at a constant frequency and modulating the duty cycle to control the power to the load. This provides excellent line and load regulation and low output voltage ripple. When in PWM, the converter synchronizes to any valid clock signal on the SYNC input (see *Dropout* and *Input Voltage Frequency Fold-Back*).

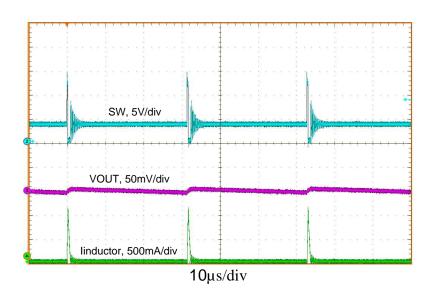

In PFM the high-side FET is turned on in a burst of one or more cycles to provide energy to the load. The frequency of these bursts is adjusted to regulate the output, while diode emulation is used to maximize efficiency. This mode provides high light load efficiency by reducing the amount of input supply current required to regulate the output voltage at small loads *Glossary*. This trades off very good light load efficiency for larger output voltage ripple and variable switching frequency. Also, a small increase in the output voltage occurs in PFM. The actual switching frequency and output voltage ripple depend on the input voltage, output voltage, and load. Typical switching waveforms for PFM are shown in Figure 12. See the *Application Curves* for output voltage variation in AUTO mode. The SYNC input is ignored during PFM operation.

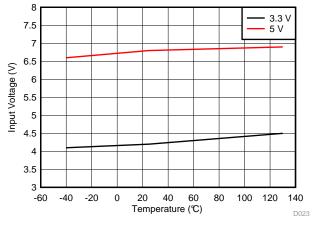

A unique feature of this device, is that a minimum input voltage is required for the regulator to switch from PWM to PFM at light load. This feature is a consequence of the advanced architecture employed to provide high efficiency at light loads. Figure 13 indicates typical values of input voltage required to switch modes at no-load. Also, once the regulator switches to PFM, at light load, it remains in that mode if the input voltage is reduced.

Figure 12. Typical PFM Switching Waveforms

Figure 13. Input Voltage for Mode Change

## 8.4.2 FPWM Mode

With a logic high on the FPWM input, the device is locked in PWM mode. This operation is maintained, even at no-load, by allowing the inductor current to reverse its normal direction. This mode trades off reduced light load efficiency for low output voltage ripple, tight output voltage regulation, and constant switching frequency. In this mode, a negative current limit of I<sub>NEG</sub> is imposed to prevent damage to the regulators low-side FET. When in FPWM, the converter synchronizes to any valid clock signal on the SYNC input (see *Dropout* and *Input Voltage Frequency Fold-Back*).

#### 8.4.3 Dropout

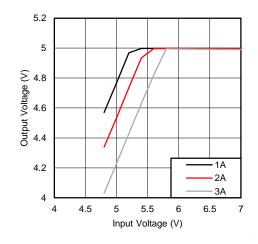

One of the parameters that influences the dropout performance of a buck regulator is the minimum off-time. As the input voltage is reduced, to near the output voltage, the off-time of the high-side switch starts to approach the minimum value (see *Timing Requirements*). Beyond this point the switching may become erratic or the output voltage falls out of regulation. To avoid this problem, the LM53603 automatically reduces the switching frequency to increase the effective duty cycle. This results in two specifications regarding dropout voltage, as shown in the *System Characteristics* table. One specification indicates when the switching frequency drops to 1.85 MHz; avoiding the A.M. radio band. The other specification indicates when the output voltage has fallen to 1% of nominal. See the *Application Curves* for typical values of dropout. The overall dropout characteristic for the 5-V option, can be seen in Figure 14. The SYNC input is ignored during frequency fold-back in dropout.

Figure 14. Overall Dropout Characteristic  $V_{OUT} = 5V$

#### 8.4.4 Input Voltage Frequency Fold-Back

At higher input voltages the on-time of the high-side switch becomes small. When the minimum is reached (see *Timing Requirements*), the switching may become erratic or the output voltage falls out of regulation. To avoid this behavior, the LM53603 automatically reduces the switching frequency at input voltages above about 20 V (see *Application Curves*). In this way the device avoids the minimum on-time restriction and maintains regulation at abnormally high battery voltages. The SYNC input is ignored during frequency fold-back at high input voltages.

Texas Instruments

www.ti.com

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining the suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The LM53603 and LM53602 are step-down DC-DC converters, typically used to convert a higher DC voltage to a lower DC voltage with a maximum output current of either 3 A or 2 A. The following design procedure can be used to select components for the LM53603 or LM53602. Alternately, the WEBENCH<sup>®</sup> Design Tool may be used to generate a complete design. This tool uses an iterative design procedure and has access to a comprehensive database of components. This allows the tool to create an optimized design and allows the user to experiment with various design options.

### 9.2 Typical Applications

### 9.2.1 Typical and Full-Featured Industrial Application Circuits

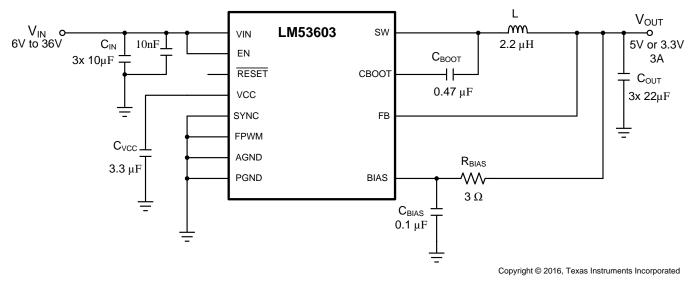

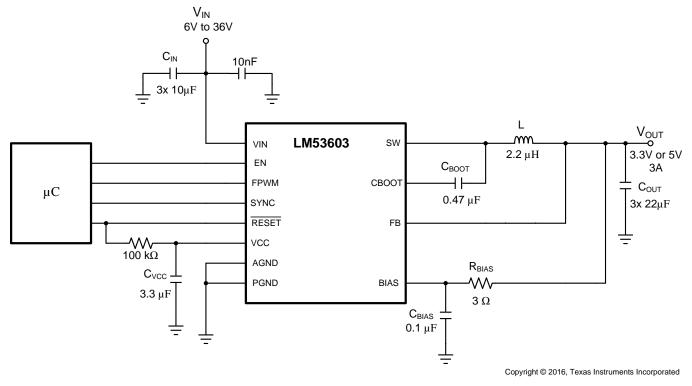

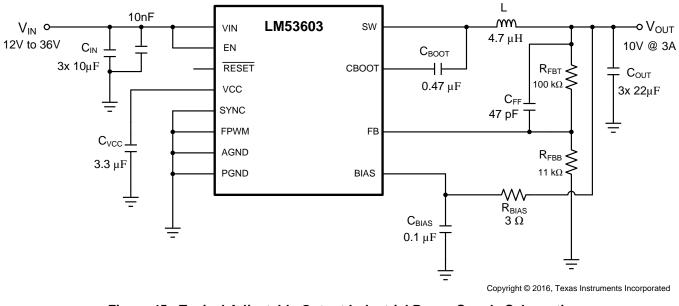

Figure 15 shows the minimum required application circuit for the fixed output voltage versions, while Figure 16 shows the connections for complete processor control of the LM53603. See these figures while following the design procedures. Table 2 provides an example of typical design requirements.

Figure 15. Typical Industrial Power Supply Schematic

## **Typical Applications (continued)**

Figure 16. Full-Featured Industrial Power Supply Schematic

### 9.2.1.1 Design Parameters

There are a few design parameters to take into account. Most of those choices decide which version of the device to use. The desired output current steers the designer toward a LM53602 type or LM53603 type part. If the output voltage is 3.3 V or 5 V, a fixed output version of the device can be used. Any other voltage level within the tolerance of the part can be achieved by using an adjustable version of the device. Most but not all parameters are independent of the of the IC choice. The output filter components (inductor and output capacitors) might vary with the choice of output voltage, especially for output voltages higher than 5 V. See *Detailed Design Procedure* for help in choosing these components.

| DESIGN PARAMETER       | EXAMPLE VALUE |

|------------------------|---------------|

| Input voltage          | 12 V          |

| Output voltage         | 5 V           |

| Maximum output current | 3 A           |

Table 2. Design Parameters

#### 9.2.1.2 Detailed Design Procedure

The following detailed design procedure applies to Figure 15, Figure 16, and Figure 45.

## 9.2.1.2.1 Setting the Output Voltage

For the fixed output voltage versions, the FB input is connected directly to the output voltage node. Preferably, near the top of the output capacitor. If the feed-back point is located further away from the output capacitors (that is, remote sensing), then a small 100-nF capacitor may be needed at the sensing point.

For output voltages other than 5 V or 3.3 V, a feedback divider is required. For the ADJ version of the device, the regulator holds the FB pin at 1 V. The range of adjustable output voltage can be found in the *Recommended Operating Conditions*. Equation 3 can be used to determine  $R_{FBB}$  for a desired output voltage and a given  $R_{FBT}$ . Usually  $R_{FBT}$  is limited to a maximum value of 100 k $\Omega$ .

Copyright © 2016, Texas Instruments Incorporated

(3)

$$R_{FBB} = R_{FBT} \cdot \left\lfloor \frac{1V}{V_{OUT} - 1V} \right\rfloor$$

In addition, a feed-forward capacitor  $C_{FF}$  may be required to optimize the transient response. For output voltages greater than 6 V, the WEBENCH Design Tool can be used to optimize the design. Recommended  $C_{FF}$  values for some cases are given in the table below. It is important to note that these values provide a first approximation only and need to be verified for each application by the designer.

| V <sub>OUT</sub> | C <sub>OUT</sub> (nominal) <sup>(1)</sup> | L     | R <sub>FBT</sub> | R <sub>FBB</sub> | C <sub>FF</sub> |

|------------------|-------------------------------------------|-------|------------------|------------------|-----------------|

| 3.2V             | 44µF                                      | 2.2µH | 69.8kΩ           | 31.6kΩ           | 33pF            |

| 3.2V             | 110µF                                     | 2.2µH | 69.8kΩ           | 31.6kΩ           | 120pF           |

| 5.1V             | 44µF                                      | 2.2µH | 80.6kΩ           | 19.6kΩ           | 33pF            |

| 5.1V             | 110µF                                     | 2.2µH | 80.6kΩ           | 19.6kΩ           | 220pF           |

| 8V               | 66µF                                      | 4.7µH | 86.6kΩ           | 12.4kΩ           | 120pF           |

| 8V               | 100µF                                     | 4.7µH | 86.6kΩ           | 12.4kΩ           | 220pF           |

| 10V              | 66µF                                      | 4.7µH | 90.9kΩ           | 10.0kΩ           | 120pF           |

#### Table 3. Recommended C<sub>FF</sub>capacitors

(1) 16V X7R capacitors used : C3225X7R1C226M250AC (TDK)

#### 9.2.1.2.2 Output Capacitors

The LM53603 is designed to work with low-ESR ceramic capacitors. The *effective* value of these capacitors is defined as the actual capacitance under voltage bias and temperature. All ceramic capacitors have a large voltage coefficient, in addition to normal tolerances and temperature coefficients. Under DC bias, the capacitance value drops considerably. Larger case sizes or higher voltage capacitors are better in this regard. To help mitigate these effects, multiple small capacitors can be used in parallel to bring the minimum *effective* capacitance up to the desired value. This can also ease the RMS current requirements on a single capacitor. Table 4 shows the nominal and minimum values of total output capacitance recommended for the LM53603. The values shown also provide a starting point for other output voltages, when using the ADJ option. Also shown are the measured values of *effective* capacitance for the indicated capacitor. More output capacitance can be used to improve transient performance and reduce output voltage ripple.

In practice, the output capacitor has the most influence on the transient response and loop phase margin. Load transient testing and Bode plots are the best way to validate any given design, and should always be completed before the application goes into production. A careful study of temperature and bias voltage variation of any candidate ceramic capacitor should be made to ensure that the minimum value of *effective* capacitance is provided. The best way to obtain an optimum design is to use the Texas Instruments WEBENCH Design Tool.

In ADJ applications the feed-forward capacitor, C<sub>FF</sub>, provides another degree of freedom when stabilizing and optimizing the design. Application report *Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor* (SLVA289) should prove helpful when adjusting the feed-forward capacitor.

In addition to the capacitance shown in Table 4, a small ceramic capacitor placed on the output can help to reduce high frequency noise. Small case size ceramic capacitors in the range of 1 nF to 100 nF can be very helpful in reducing spikes on the output caused by inductor parasitics.

The maximum value of total output capacitance should be limited to between 300  $\mu$ F and 400  $\mu$ F. Large values of output capacitance can prevent the regulator from starting-up correctly and adversely effect the loop stability. If values in the range given above, or greater, are to be used, then a careful study of start-up at full load and loop stability must be performed.

|                     | • •                  |                                        |                      |                                        |                               |  |  |  |  |  |

|---------------------|----------------------|----------------------------------------|----------------------|----------------------------------------|-------------------------------|--|--|--|--|--|

| OUTPUT<br>VOLTAGE   | NOMINAL OUTPU        | JT CAPACITANCE                         |                      | JTPUT CAPACITANCE                      | PART NUMBER<br>(MANUFACTURER) |  |  |  |  |  |

|                     | RATED<br>CAPACITANCE | MEASURED<br>CAPACITANCE <sup>(1)</sup> | RATED<br>CAPACITANCE | MEASURED<br>CAPACITANCE <sup>(1)</sup> |                               |  |  |  |  |  |

| 3.3 V               | 3 × 22 μF            | 63 µF                                  | 2 × 22 μF            | 42 µF                                  | C3225X7R1C226M250AC (TDK)     |  |  |  |  |  |

| 5 V                 | 3 × 22 μF            | 60 µF                                  | 2 × 22 μF            | 40 µF                                  | C3225X7R1C226M250AC (TDK)     |  |  |  |  |  |

| 6 V                 | 3 × 22 μF            | 59 µF                                  | 2 × 22 μF            | 39 µF                                  | C3225X7R1C226M250AC (TDK)     |  |  |  |  |  |

| 10 V <sup>(2)</sup> | 3 × 22 μF            | 48 µF                                  | 2 × 22 μF            | 32 µF                                  | C3225X7R1C226M250AC (TDK)     |  |  |  |  |  |

#### **Table 4. Recommended Output Capacitors**

(1) Measured at indicated V<sub>OUT</sub> at 25°C.

(2) The following components were used:  $C_{FF} = 47 \text{ pF}$ ,  $R_{FBT} = 100 \text{ k}\Omega$ ,  $R_{FBB} = 11 \text{ k}\Omega$ ,  $L = 4.7 \mu\text{H}$ .

#### 9.2.1.2.3 Input Capacitors

The ceramic input capacitors provide a low impedance source to the regulator in addition to supplying ripple current and isolating switching noise from other circuits. Table 5 shows the nominal and minimum values of total input capacitance recommenced for the LM53603. Also shown are the measured values of *effective* capacitance for the indicated capacitor. In addition, small high frequency bypass capacitors connected directly between the VIN and PGND pins are very helpful in reducing noise spikes and aid in reducing conducted EMI. TI recommends that a small case size 10-nF ceramic capacitor be placed across the input, as close as possible to the device (see Figure 47). Additional high frequency capacitors can be used to help manage conducted EMI or voltage spike issues that may be encountered.

#### **Table 5. Recommended Input Capacitors**

| NOMINAL INPUT        | <b>CAPACITANCE</b>                     | MINIMUM INPU         | T CAPACITANCE                          | PART NUMBER (MANUFACTURER) |

|----------------------|----------------------------------------|----------------------|----------------------------------------|----------------------------|

| RATED<br>CAPACITANCE | MEASURED<br>CAPACITANCE <sup>(1)</sup> | RATED<br>CAPACITANCE | MEASURED<br>CAPACITANCE <sup>(1)</sup> |                            |

| 3 x 10 µF            | 22.5 µF                                | 2 × 10 µF            | 15 µF                                  | CL32B106KBJNNNE (Samsung)  |

(1) Measured at 14 V and 25°C.

Many times it is desirable to use an electrolytic capacitor on the input, in parallel with the ceramics. This is especially true if longs leads or traces are used to connect the input supply to the regulator. The moderate ESR of this capacitor can help damp any ringing on the input supply caused by long power leads. The use of this additional capacitor also helps with voltage dips caused by input supplies with unusually high impedance.

Most of the input switching current passes through the ceramic input capacitor(s). The approximate RMS value of this current can be calculated from Equation 4 and should be checked against the manufacturers' maximum ratings.

$$I_{RMS} \cong \frac{I_{OUT}}{2}$$

(4)

#### 9.2.1.2.4 Inductor

The LM53603 and LM53602 are optimized for a nominal inductance of 2.2  $\mu$ H for the 5-V and 3.3-V versions. This gives a ripple current that is approximately 20% to 30% of the full load current of 3 A. For output voltages greater than 5 V, a proportionally larger inductor can be used. This keeps the ratio of inductor current slope to internal compensating slope constant.

The most important inductor parameters are saturation current and parasitic resistance. Inductors with a saturation current of between 5 A and 6 A are appropriate for most applications, when using the LM53603. For the LM53602, inductors with a saturation current of between 4 A and 5 A are appropriate. Of course the inductor parasitic resistance should be as low as possible to reduce losses at heavy loads. Table 6 gives a list of several possible inductors that can be used with the LM53603.

Texas Instruments

www.ti.com

| MANUFACTURER | R PART NUMBER SATURATIO |       | DC RESISTANCE |

|--------------|-------------------------|-------|---------------|

| Würth        | 7440650022              | 6 A   | 15 mΩ         |

| Coilcraft    | DO3316T-222MLB          | 7.8 A | 11 mΩ         |

| Coiltronics  | MPI4040R3-2R2-R         | 7.9 A | 48 mΩ         |

| Vishay       | IHLP2525CZER2R2M01      | 14 A  | 18 mΩ         |

| Vishay       | IHLP2525BDER2R2M01      | 14 A  | 28 mΩ         |

| Coilcraft    | XAL6030-222ME           | 16 A  | 13 mΩ         |

#### Table 6. Recommenced Inductors

#### 9.2.1.2.5 VCC

The VCC pin is the output of the internal LDO, used to supply the control circuits of the LM53603. This output requires a  $3.3-\mu$ F to  $4.7-\mu$ F, ceramic capacitor connected from VCC to GND for proper operation. An X7R device with a rating of 10 V is highly recommended. In general this output should not be loaded with any external circuitry. However, it can be used to supply a logic level to the FPWM input, or for the pullup resistor used with the RESET output (see Figure 16). The nominal output of the LDO is 3.15 V.

#### 9.2.1.2.6 BIAS

The BIAS pin is the input to the internal LDO. As mentioned in *Input Supply Current*, this input is connected to  $V_{OUT}$  to provide the lowest possible supply current at light loads. Because this input is connected directly to the output, it should be protected from negative voltage transients. Such transients may occur when the output is shorted at the end of a long PCB trace or cable. If this is likely, in a given application, then a small resistor should be placed in series between the BIAS input and  $V_{OUT}$ , as shown in Figure 15. The resistor should be sized to limit the current out of the BIAS pin to <100 mA. Values in the range of 2  $\Omega$  to 5  $\Omega$  are usually sufficient. Values greater than 5  $\Omega$  are not recommended. As a rough estimate, assume that the full negative transient appears across  $R_{BIAS}$  and design for a current of < 100 mA. In severe cases, a Schottky diode can be placed in parallel with the output to limit the transient voltage and current.

#### 9.2.1.2.7 CBOOT

The LM53603 requires a *boot-strap* capacitor between the CBOOT pin and the SW pin. This capacitor stores energy that is used to supply the gate drivers for the power MOSFETs. A ceramic capacitor of 0.47  $\mu$ F,  $\geq$  6.3 V is required. A 10-V rated capacitor or higher is highly recommended.

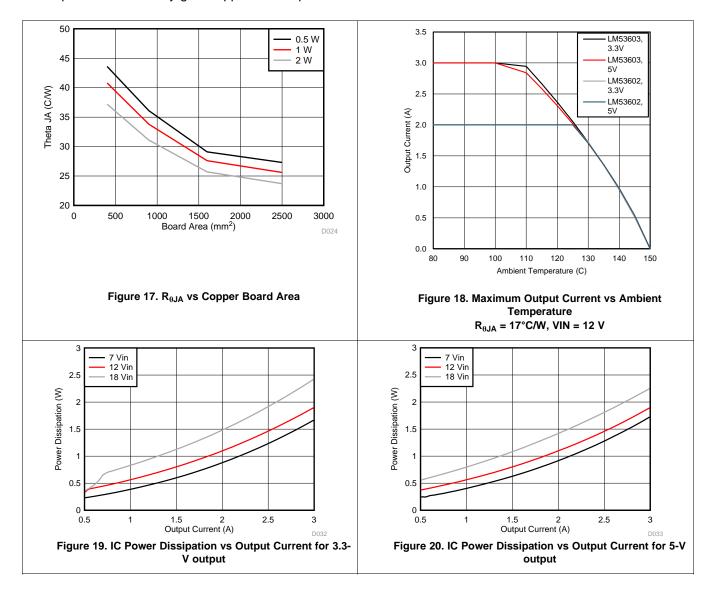

#### 9.2.1.2.8 Maximum Ambient Temperature

As with any power conversion device, the LM53603 dissipates internal power while operating. The effect of this power dissipation is to raise the internal temperature of the converter, above ambient. The internal die temperature (T<sub>J</sub>) is a function of the ambient temperature, the power loss and the effective thermal resistance,  $R_{\theta JA}$  of the device and PCB combination. The maximum internal die temperature for the LM53603 is 150°C, thus establishing a limit on the maximum device power dissipation and therefore load current at high ambient temperatures. Equation 5 shows the relationships between the important parameters.

$$I_{OUT} = \frac{(T_J - T_A)}{R_{\theta JA}} \cdot \frac{\eta}{(1 - \eta)} \cdot \frac{1}{V_{OUT}}$$

(5)

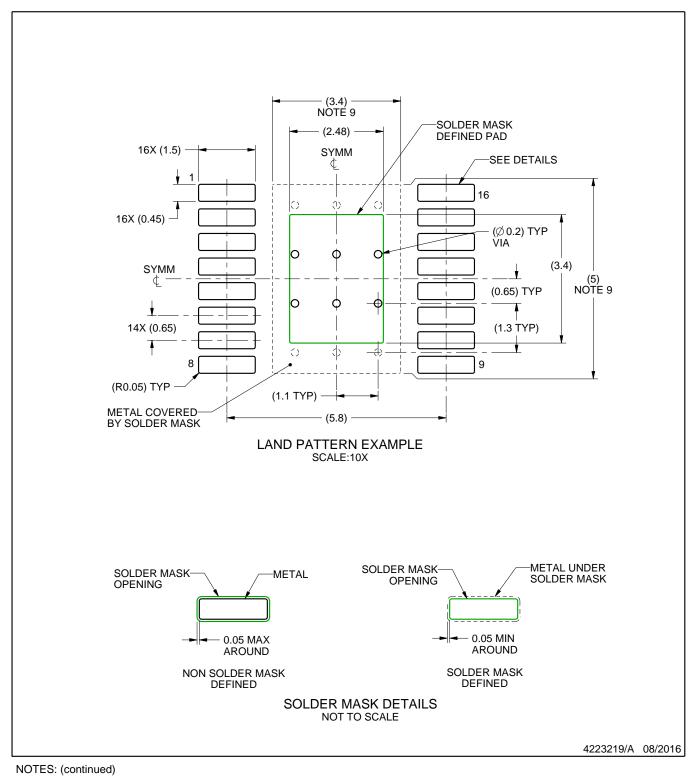

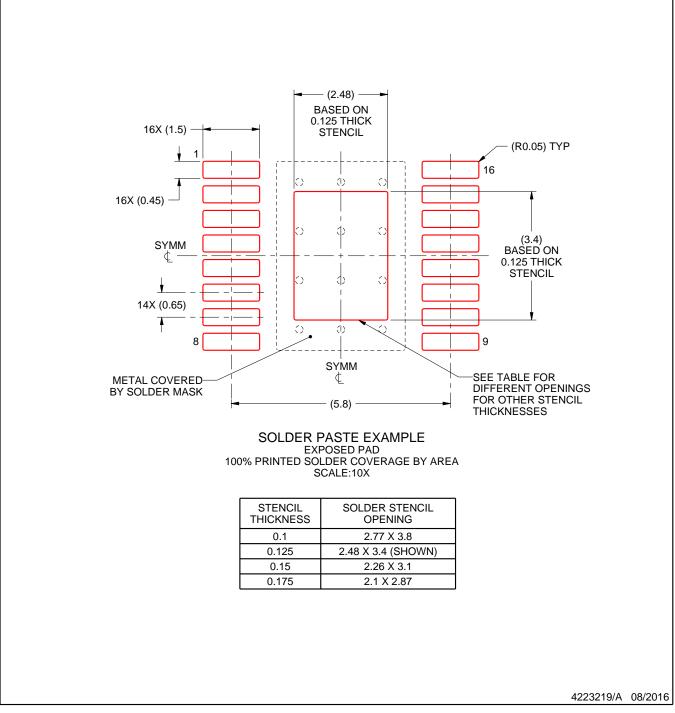

It is easy to see that larger ambient temperatures ( $T_A$ ) and larger values of  $R_{\theta JA}$  reduce the maximum available output current. As stated in *Semiconductor and IC Package Thermal Metrics*, the values given in the *Thermal Information* table are not valid for design purposes and must not be used to estimate the thermal performance of the application. The values reported in that table were measured under a specific set of conditions that are never obtained in an actual application. The effective  $R_{\theta JA}$  is a critical parameter and depends on many factors such as power dissipation, air temperature, PCB area, copper heat sink area, number of thermal vias under the package, air flow, and adjacent component placement. The LM53603 uses an advanced package with a heat spreading pad (EP) on the bottom. This must be soldered directly to the PCB copper ground plane to provide an effective heat sink, as well as a proper electrical connection. The resources in *Ground and Thermal Plane Considerations* can be used as a guide to optimal thermal PCB design and estimating  $R_{\theta JA}$  for a given application environment. A typical example of  $R_{\theta JA}$  versus copper board area is shown in Figure 17. The copper area in this graph is that

for each layer of a four-layer board; the inner layers are 1 oz. (35  $\mu$ m), while the outer layers are 2 oz. (70  $\mu$ m). A typical curve of maximum load current versus ambient temperature, for both the LM53603 and LM53602, is shown in Figure 18. This data was taken with the device soldered to a PCB with an R<sub>0JA</sub> of about 17°C/W and an input voltage of 12 V. It must be remembered that the data shown in these graphs are for illustration only and the actual performance in any given application depends on all of the factors mentioned above.

Submit Documentation Feedback

24

#### LM53602, LM53603 SNVSAR0-NOVEMBER 2016

#### 9.2.1.3 Application Curves

STRUMENTS

XAS

# 9.3 Typical Adjustable Industrial Application Circuit

Figure 45 shows a typical example of a design with an output voltage of 10 V; while Table 7 gives typical design parameters. See *Detailed Design Procedure* for the design procedure.

Figure 45. Typical Adjustable Output Industrial Power Supply Schematic CD/DVD/Blu-ray Disc<sup>™</sup> Motor Drive Applications V<sub>OUT</sub> = 10 V

## 9.3.1 Design Parameters for Typical Adjustable Output Industrial Power Supply

There are a few design parameters to take into account. Most of those choices decide which version of the device to use. The desired output current steers the designer toward a LM53602 type or LM53603 type part. Most but not all parameters are independent of the of the IC choice. The output filter components (inductor and output capacitors) might vary with the choice of output voltage, especially for output voltages higher than 5 V. Refer to *Detailed Design Procedure* for details on choosing the components for the application.

#### **Table 7. Design Parameters**

| DESIGN PARAMETER       | EXAMPLE VALUE |

|------------------------|---------------|

| Input Voltage          | 12 V          |

| Output Voltage         | 10 V          |

| Maximum Output Current | 3 A           |

## 9.4 Do's and Don't's

28

- **Don't:** Exceed the *Absolute Maximum Ratings*.

- **Don't:** Exceed the *ESD Ratings*.

- **Don't:** Exceed the *Recommended Operating Conditions*.

- Don't: Allow the EN, FPWM or SYNC input to float.

- **Don't:** Allow the output voltage to exceed the input voltage, nor go below ground.

- Don't: Use the thermal data given in the *Thermal Information* table to design your application.

- **Do:** Follow all of the guidelines and suggestions found in this data sheet, before committing your design to production. TI Application Engineers are ready to help critique your design and PCB layout to help make your project a success.

- Do: Refer to the helpful documents found in *Layout Guidelines* and *Ground and Thermal Plane Considerations*.

## **10** Power Supply Recommendations

The characteristics of the input supply must be compatible with the *Absolute Maximum Ratings* and *Recommended Operating Conditions* found in this data sheet. In addition, the input supply must be capable of delivering the required input current to the loaded regulator. The average input current can be estimated with Equation 6, where  $\eta$  is the efficiency.

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta}$$

(6)

If the regulator is connected to the input supply through long wires or PCB traces, take special care to achieve good performance. The parasitic inductance and resistance of the input cables can have an adverse effect on the operation of the regulator. The parasitic inductance, in combination with the low-ESR ceramic input capacitors, can form an under-damped resonant circuit. This circuit may cause overvoltage transients at the VIN pin, each time the input supply is cycled on and off. The parasitic resistance causes the voltage at the VIN pin to dip when the load on the regulator is switched on, or exhibits a transient. If the regulator is operating close to the minimum input voltage, this dip may cause the device to shutdown or reset. The best way to solve these kinds of issues is to reduce the distance from the input supply to the regulator or use an aluminum or tantalum input capacitor in parallel with the ceramics. The moderate ESR of these types of capacitors helps to damp the input resonant circuit and reduce any voltage overshoots. A value in the range of 20  $\mu$ F to 100  $\mu$ F is usually sufficient to provide input damping and help to hold the input voltage steady during large load transients.

Sometimes, for other system considerations, an input filter is used in front of the regulator. This can lead to instability, as well as some of the effects mentioned above, unless it is designed carefully. The user guide *Simple Success with Conducted EMI for DC-DC Converters* (SNVA489), provides helpful suggestions when designing an input filter for any switching regulator

In some cases a Transient Voltage Suppressor (TVS) is used on the input of regulators. One class of this device has a *snap-back* V-I characteristic (thyristor type). The use of a device with this type of characteristic is not recommend. When the TVS *fires*, the clamping voltage drops to a very low value. If this holding voltage is less than the output voltage of the regulator, the output capacitors is discharged through the regulator back to the input. This uncontrolled current flow could damage the regulator.

## 11 Layout

### 11.1 Layout Guidelines

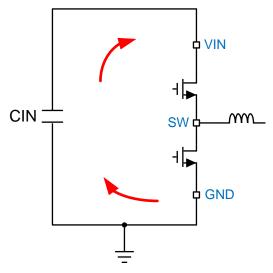

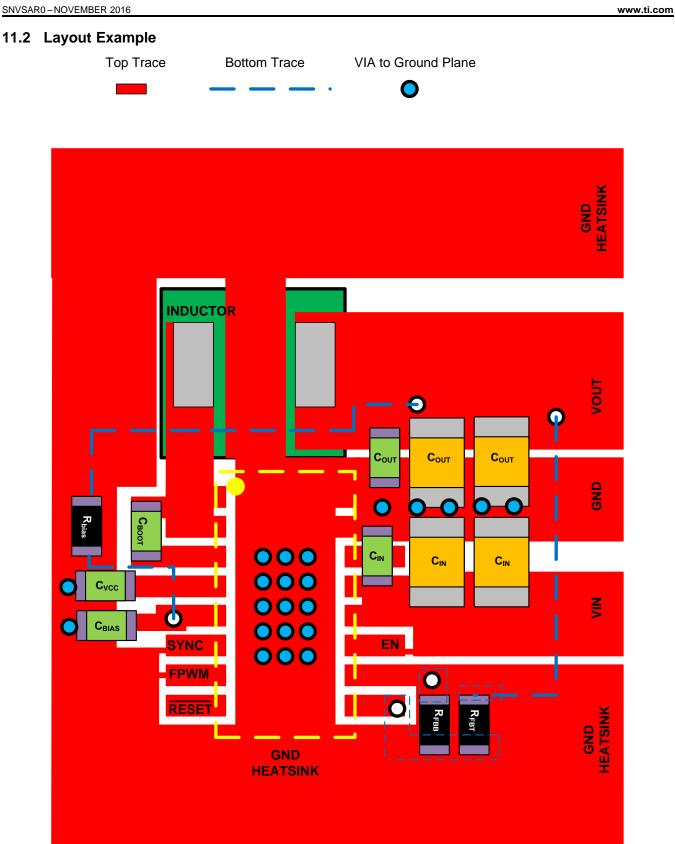

The PCB layout of any DC-DC converter is critical to the optimal performance of the design. Bad PCB layout can disrupt the operation of an otherwise good schematic design. Even if the converter regulates correctly, bad PCB layout can mean the difference between a robust design and one that cannot be mass produced. Furthermore, the EMI performance of the regulator is dependent on the PCB layout, to a great extent. In a buck converter, the most critical PCB feature is the loop formed by the input capacitor and power ground, as shown in Figure 46. This loop carries fast transient currents that can cause large transient voltages when reacting with the trace inductance. These unwanted transient voltages disrupt the proper operation of the converter. Because of this, the traces in this loop should be wide and short, and the loop area as small as possible to reduce the parasitic inductance. Figure 47 shows a recommended layout for the critical components of the LM53603. This PCB layout is a good guide for any specific application. The following important guidelines must also be followed:

- 1. Place the input capacitor(s) CIN as close as possible to the VIN and PGND terminals. VIN and GND are on the same side of the device, simplifying the input capacitor placement.

- Place bypass capacitors for VCC and BIAS close to their respective pins. These components must be placed close to the device and routed with short and wide traces to the pins and ground. The trace from BIAS to VOUT should be ≥10 mils wide. BIAS and VCC capacitors must be place within 4 mm of the BIAS and VCC pin (160 mils).

- 3. Use wide traces for the CBOOT capacitor. CBOOT must be placed close to the device with short and wide traces to the CBOOT and SW pins.

- 4. Place the feedback divider as close as possible to the FB pin on the device. If a feedback divider and C<sub>FF</sub> are used, they must be close to the device while the length of the trace from V<sub>OUT</sub> to the divider can be somewhat longer. However, this latter trace must not be routed near any noise sources that can capacitively couple to the FB input.

- 5. Use at least one ground plane in one of the middle layers. This plane acts as a noise shield and also act as a heat dissipation path.

- Connect the EP pad to the GND plane. This pad acts as a heat sink connection and a ground connection for the regulator. It must be solidly connected to a ground plane. The integrity of this connection has a direct bearing on the effective R<sub>θJA</sub>.

- 7. **Provide wide paths for VIN, VOUT and GND.** Making these paths as wide as possible reduces any voltage drops on the input or output paths of the converter and maximizes efficiency.