### PSI5 Transceiver IC

#### Datasheet - production data

#### **Features**

- 2-channel PSI5 transceiver compatible with rev. 1.3 and rev. 2.1

- Manchester coded digital data transmission

- High data transmission speed of 125 kbps (optional 83.3 kbps and 189 kbps)

- High EMC robustness and low emission

- Bootstrap circuits for sync pulses

- Current limitation and voltage clamp on interface pins

- Integrated charge pump stage for preregulation with spread spectrum approach

- Integrated FLL module for high accuracy timing control

- Reverse voltage protection structure

- Short to ground tolerant with ±1.5 V ground shift

- · 32-bit SPI interface with address multiplexing

- Operating voltage: V<sub>B</sub> = 4.8 V (5.2 V for sync pulses with 3.5 V step) to 35 V

- Ambient temperature range: -40°C to 140 °C

- Package: VFQFPN28 or TQFP32EP

## Description

The Peripheral Sensor Interface (PSI5) is an interface for automotive sensor applications. PSI5 is an open standard based on existing sensor interfaces for peripheral sensors and offers a universal and flexible solution for multiple sensor applications.

The PSI5 interface allows asynchronous or synchronous operations and different bus modes. The device is compatible with both v1.3 and v2.1 PSI5 revisions (limitations are specified inside this document). It operates with a wide range of sensor supply current and variable data word length (8 to 28 bit).

The sensors are connected to the ECU using the same line for power supply and data transmission. The transceiver IC provides a preregulated voltage to the sensors and reads in the transmitted sensor data.

The PSI5 interface allows either point to point connection or bussed mode.

**Table 1. Device summary**

| Order code | Package              | Packing     |

|------------|----------------------|-------------|

| L9663      | TOED32 (Exposed pad) | Tray        |

| L9663-TR   | TQFP32 (Exposed pad) | Tape & Reel |

| L9663-1    | VFQFPN28             | Tray        |

| L9663-TR-1 | VFQFFNZO             | Tape & Reel |

Contents L9663

# **Contents**

| 1 | Ove  | rall desc          | cription                                                        | 6  |

|---|------|--------------------|-----------------------------------------------------------------|----|

|   | 1.1  | Simplif            | ied block diagram                                               | 6  |

|   | 1.2  | Main fu            | unctionality                                                    | 7  |

|   | 1.3  | VQFPI              | N28 pins description                                            | 9  |

|   | 1.4  | TQFP3              | 32 pins description                                             | 11 |

|   | 1.5  | Maxim              | um ratings                                                      | 13 |

|   | 1.6  | Detaile            | d block diagram                                                 | 14 |

|   | 1.7  | Power              | up sequence                                                     | 16 |

| 2 | Pow  | er supp            | ly                                                              | 17 |

|   | 2.1  | Interna            | l supply                                                        | 17 |

|   | 2.2  | V <sub>AS</sub> su | pply and pre-regulator                                          | 18 |

|   | 2.3  | Voltage            | e supply for synchronous pulse generation $V_{	extstyle SYNCx}$ | 19 |

|   | 2.4  | Power              | supply for PSI5 sensor line                                     | 20 |

|   | 2.5  | Freque             | ency references                                                 | 22 |

|   | 2.6  | Reset              | handling                                                        | 24 |

| 3 | Sate | llite inte         | erface                                                          | 25 |

|   | 3.1  | Receiv             | er with digital sampling and filtering                          | 25 |

|   | 3.2  | Manch              | ester decoder and error detection                               | 26 |

|   | 3.3  | Receiv             | e block                                                         | 26 |

|   |      | 3.3.1              | PSI5 receive register                                           | 27 |

|   |      | 3.3.2              | Sensor data buffer                                              | 30 |

|   |      | 3.3.3              | Interrupt generator                                             |    |

|   |      | 3.3.4              | Automatic storage of sensor initialization data                 | 33 |

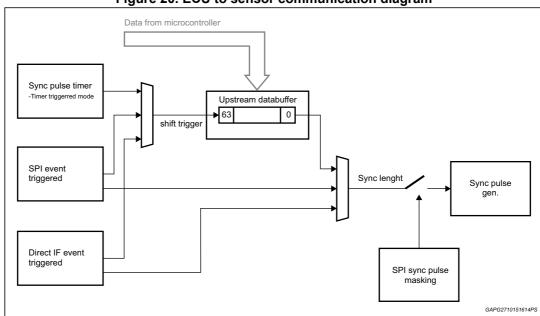

|   | 3.4  | Upstre             | am data buffer                                                  | 35 |

|   | 3.5  | Trigger            | pulse generator for synchronous pulses                          | 36 |

|   | 3.6  | Synchr             | onous pulse generator                                           | 37 |

|   | 3.7  | Safety             | concepts                                                        | 38 |

|   |      | 3.7.1              | Voltage monitoring check                                        | 38 |

|   |      | 3.7.2              | Sensor data consistency                                         | 38 |

|   |      | 3.7.3              | Buffer empty check                                              | 39 |

L9663 Contents

|   |      | 0.7.4              | DOLITA moth shoot                                 | 20  |

|---|------|--------------------|---------------------------------------------------|-----|

|   |      | 3.7.4              | DOUTx path check                                  |     |

|   |      | 3.7.5              | Cross coupling test                               | 40  |

| 4 | Diag | nosis .            |                                                   | 42  |

|   | 4.1  | PSIx c             | output voltage clamping circuit                   | 42  |

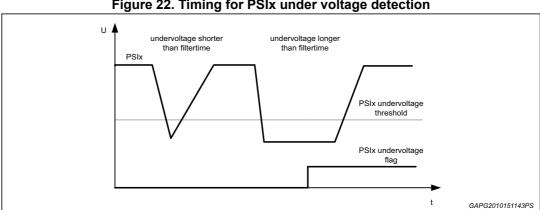

|   | 4.2  | PSIx c             | output under voltage monitoring                   | 42  |

|   | 4.3  | PSIx s             | short circuit detection                           | 43  |

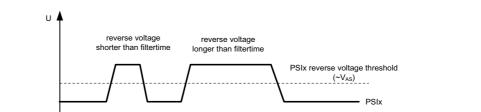

|   | 4.4  | PSIx r             | everse voltage monitoring                         | 44  |

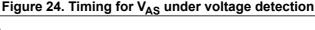

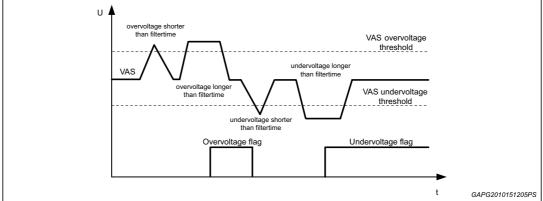

|   | 4.5  | V <sub>AS</sub> ur | nder/over voltage monitoring                      | 44  |

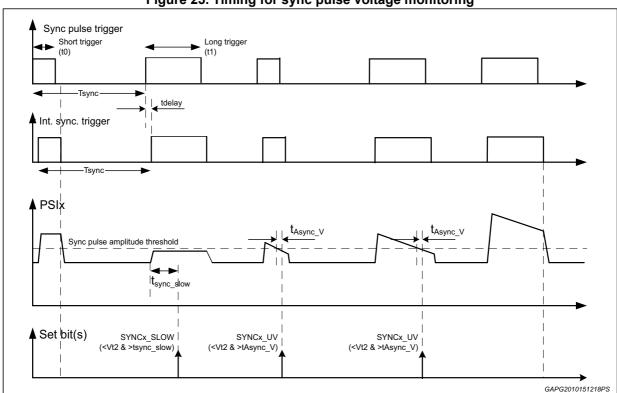

|   | 4.6  | Monito             | oring of Synchronous Pulse amplitude              | 45  |

| 5 | Com  | munica             | ation interface                                   | 47  |

|   | 5.1  | Device             | e registers                                       | 47  |

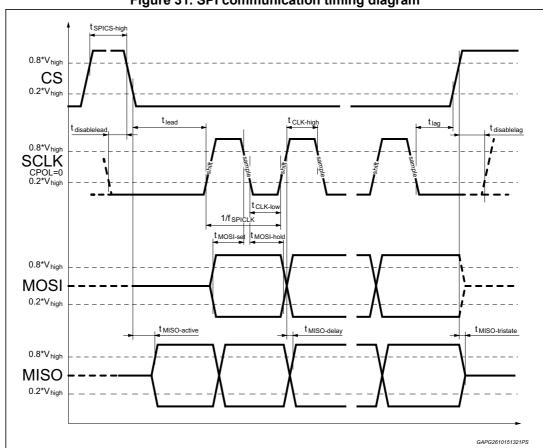

|   | 5.2  | SPI in             | terface                                           | 81  |

|   |      | 5.2.1              | Physical layer and signal description             | 81  |

|   |      | 5.2.2              | Clock and data characteristics                    | 82  |

|   |      | 5.2.3              | Frame definition                                  | 83  |

|   |      | 5.2.4              | Communication frames                              | 83  |

|   | 5.3  | Direct             | interface                                         | 86  |

| 6 | Elec | trical cl          | haracteristics                                    | 87  |

|   | 6.1  | SPI in             | terface                                           | 95  |

| 7 | Erra | ta                 |                                                   | 98  |

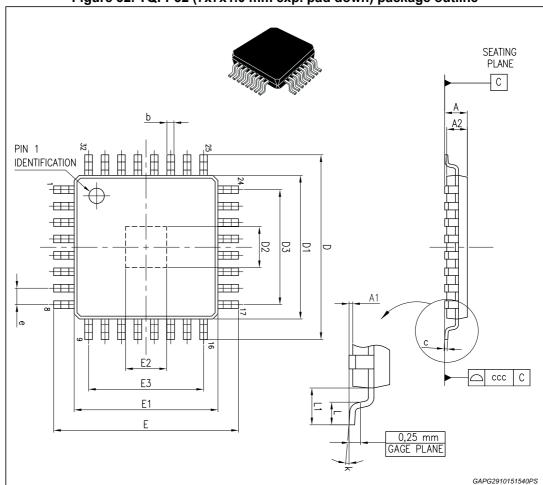

| 8 | Pack | kage inf           | formation                                         | 99  |

|   | 8.1  | TQFP               | 32 (7x7x1.0 mm exp. pad down) package information | 99  |

|   | 8.2  | VFQF               | PN-28 (5x5x1.0 mm) package information            | 101 |

| 9 | Revi | sion his           | story                                             | 103 |

List of tables L9663

# List of tables

| Table 1.  | Device summary                                            | 1   |

|-----------|-----------------------------------------------------------|-----|

| Table 2.  | VQFPN28 pin-out                                           | 9   |

| Table 3.  | TQFP32 pin-out                                            | 11  |

| Table 4.  | Pin maximum ratings                                       | 13  |

| Table 5.  | Time (t0-t2) vs SensorData                                | 30  |

| Table 6.  | Error codes in sensor communication                       | 31  |

| Table 7.  | Faults priority                                           |     |

| Table 8.  | Time (t0-t7) vs SensorData                                | 32  |

| Table 9.  | Doutx test mode bit value                                 | 39  |

| Table 10. | Operating conditions                                      | 87  |

| Table 11. | VINTx internal supply                                     | 87  |

| Table 12. | V <sub>AS</sub> supply                                    |     |

| Table 13. | V <sub>AS</sub> external MOS                              | 88  |

| Table 14. | V <sub>AS</sub> pre regulator                             | 89  |

| Table 15. | V <sub>SYNCx</sub>                                        | 90  |

| Table 16. | PSI5 output supply                                        | 90  |

| Table 17. | PSI5 receiver                                             | 91  |

| Table 18. | Sync generator                                            | 92  |

| Table 19. | Reset                                                     |     |

| Table 20. | VAS under/over voltage monitoring                         |     |

| Table 21. | Synchronous pulse amplitude monitoring                    | 94  |

| Table 22. | Time slot monitoring                                      |     |

| Table 23. | Digital I/O                                               |     |

| Table 24. | Frequency references                                      |     |

| Table 25. | SPI communication timing                                  | 96  |

| Table 26. | Direct interface                                          |     |

| Table 27. | Errata                                                    |     |

| Table 28. | TQFP32 (7x7x1.0 mm exp. pad down) package mechanical data |     |

| Table 29. | VFQFPN-28 (5x5x1.0 mm) package mechanical data            | 101 |

| Table 30  | Document revision history                                 | 103 |

L9663 List of figures

# List of figures

| igure 1.   | Simplified block diagram                                                                     | 6   |

|------------|----------------------------------------------------------------------------------------------|-----|

| igure 2.   | VQFPN28 pins connection diagram (top view)                                                   | 9   |

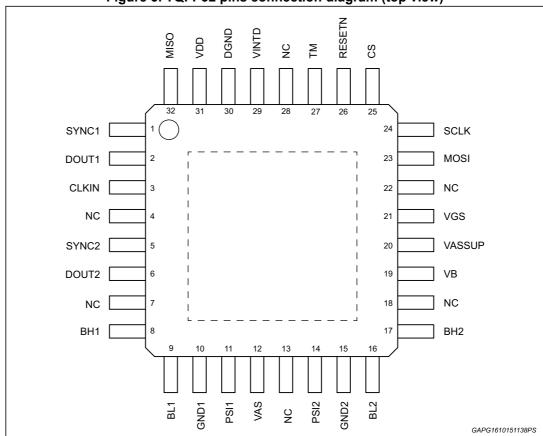

| Figure 3.  | TQFP32 pins connection diagram (top view)                                                    | 11  |

| igure 4.   | Detailed block diagram                                                                       | 14  |

| igure 5.   | Supply line model for PSI5                                                                   | 15  |

| igure 6.   | Power-up sequence of transceiver IC                                                          |     |

| igure 7.   | Internal power supply and reset generation                                                   | 17  |

| igure 8.   | Input structure of supply                                                                    |     |

| igure 9.   | V <sub>AS</sub> application diagram                                                          |     |

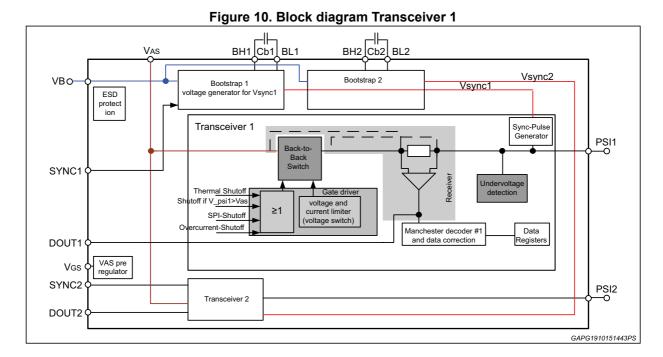

| Figure 10. | Block diagram Transceiver 1                                                                  | 21  |

| Figure 11. | Internal oscillator vs external clock frequency                                              | 23  |

| igure 12.  | FLL clock error detection                                                                    |     |

| igure 13.  | Block diagram of incoming data buffer                                                        |     |

| igure 14.  | PSI5 v1.3 frame                                                                              |     |

| Figure 15. | PSI5 v2.0 frame                                                                              |     |

| igure 16.  | Sensor buffer in synchronous mode diagram                                                    |     |

| igure 17.  | Sensor buffer in asynchronous mode diagram                                                   |     |

| igure 18.  | Block diagram with interrupt pins                                                            |     |

| Figure 19. | Timing diagram                                                                               |     |

| igure 20.  | ECU to sensor communication diagram                                                          |     |

| igure 21.  | Short (in case 1 $\mu$ s < $t_w$ < 5 $\mu$ s) Sync Pulse trigger, compliant to PSI5 standard |     |

| Figure 22. | Timing for PSIx under voltage detection                                                      |     |

| igure 23.  | Timing for PSIx reverse voltage detection                                                    |     |

| Figure 24. | Timing for V <sub>AS</sub> under voltage detection                                           |     |

| igure 25.  | Timing for sync pulse voltage monitoring                                                     |     |

| igure 26.  | SPI interface                                                                                |     |

| igure 27.  | Operation on internal register (with upstream data buffer)                                   |     |

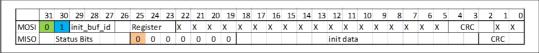

| igure 28.  | Init data reading                                                                            |     |

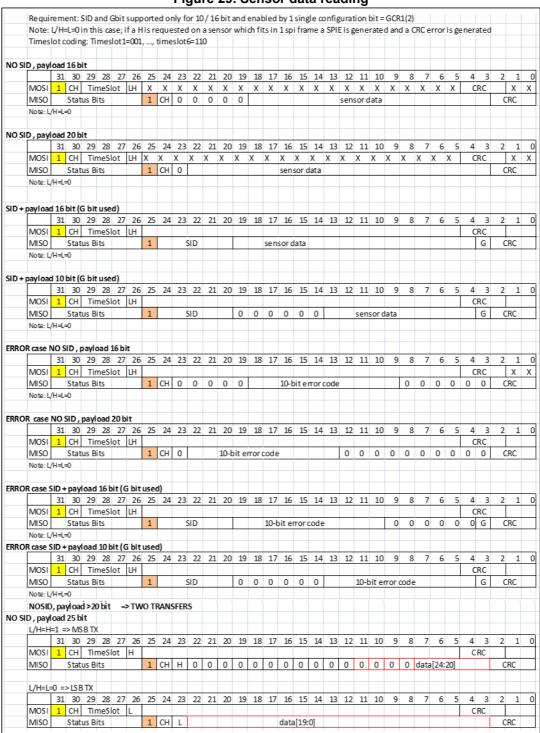

| igure 29.  | Sensor data reading                                                                          |     |

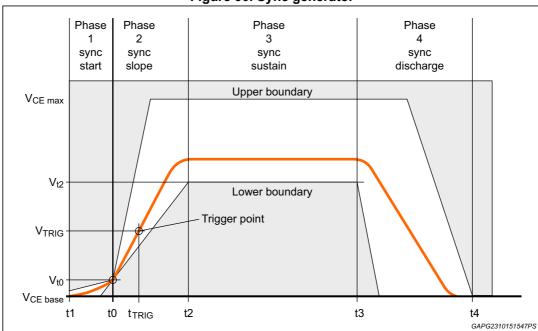

| igure 30.  | Sync generator                                                                               |     |

| igure 31.  | SPI communication timing diagram                                                             |     |

| igure 32.  | TQFP32 (7x7x1.0 mm exp. pad down) package outline                                            | 99  |

| igure 33.  | VFQFPN-28 (5x5x1.0 mm) package outline                                                       | 101 |

Overall description L9663

# 1 Overall description

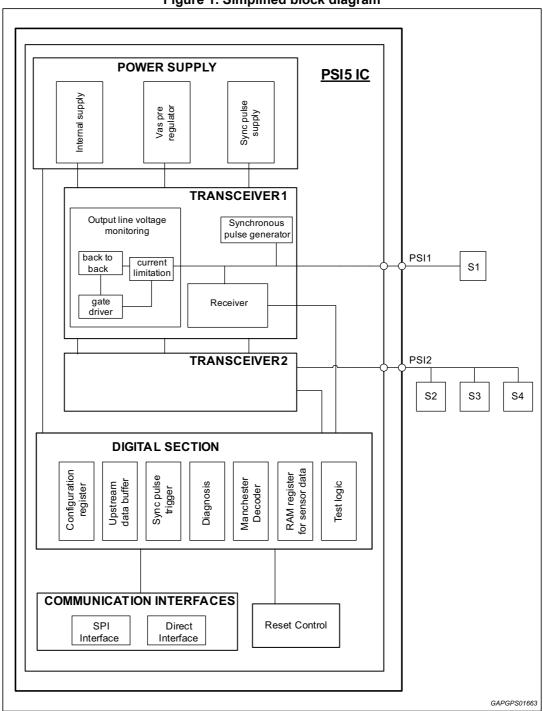

# 1.1 Simplified block diagram

Figure 1. Simplified block diagram

L9663 Overall description

# 1.2 Main functionality

The transceiver IC can be used in two different modes (Mode 1 or Mode 2)<sup>(a)</sup>. The system configuration called Mode 1 performs the decoding effort of sensor signals in the IC. The system configuration called Mode 2 is a frontend to a PSI5 decoder contained in an external device (typically a  $\mu$ C with a dedicated module).

The transceiver IC can monitor all internally generated relevant voltages, such as  $V_{SYNCx}$   $V_{AS}$  and  $V_{PSIx}$ .

The PSI5 interfaces inside the IC are supplied by a separate input pin VAS. If only asynchronous mode is required, the VAS voltage is sufficient for the sensor power supply. When synchronous mode is required, a higher voltage than VAS is needed in order to generate the synchronous pulses. This voltage VSYNCx is generated by a dedicated bootstrap circuit for each channel.

For direct supply from battery, the transceiver IC includes a  $V_{AS}$  pre-regulator supplied by VASSUP-pin: the pre-regulator can drive an external FET to regulate the VAS voltage to 7.6 V or 5.3 V. In case of low voltage level at VASSUP, an integrated charge pump is implemented, with supply from VASSUP.

The internal analog and digital circuits are supplied by VB. The external voltage on VDD pin is used to supply the digital output pins; VDD pin can be used to switch the digital outputs from 5 V output level (default) to 3.3 V output level.

The PSI5 transceiver is functional in the whole  $V_{DD}$ , VB, VASSUP and  $V_{AS}$  power supply range.

The internal voltage supplies (V<sub>SYNCx</sub>) are automatically activated by the transceiver IC depending on the operating mode whenever they are needed.

Each transceiver interface can be activated and deactivated by an SPI command. At startup, the interfaces are off by default.

The communication interface block includes two different interfaces. In mode 1, SPI is used for data transfer. In mode 2, the direct interface is used. The data from and to the sensors will be transmitted bit-wise between the transceiver IC and the  $\mu$ C. The data evaluation and error handling for frame errors will be done in the PSI5 controller which is integrated in the  $\mu$ C.

Transceiver 1 and 2 supply the sensors and generate the synchronous pulses for synchronous data transfer (if required) from the sensors to the transceiver and for data transfer from the ECU to the sensors.

A data transfer from the ECU to the sensors can be performed:

- by using sync pulses with different duration (PSI5 2.x standard)

- by masking of sync pulses (PSI5 1.3 and 2.x standard)

The sync pulse trigger can be generated by an SPI command, by a dedicated pin (for connection to the Synchronous Pulse Output Block included in the microcontroller) or by an integrated automatic timer.

DocID028693 Rev 1 7/104

a. Mode 1 and Mode 2 are two system architectures which relate on the way L9663 communicates with the microcontroller. Depending on the chosen architecture, the µC must configure the IC with the correct setup.

Overall description L9663

The Transceivers 1 and 2 limit the current and the PSIx voltage (PSI5-requirement when VAS is too high because of failure in the VAS power supply, less than 11 V in data transmission or less than 16.5 V in sync pulse).

The current modulated signal received from sensor is detected and digitally converted. This sensor data will then either be:

- First Manchester decoded by the Manchester Decoder block with mark space error correction and then transferred to the "receive data buffer" module (Mode 1). The data from the new sensor frames will be saved in a buffer and then will be transferred to the μC via SPI.

- Transferred directly to the µC (Mode 2). In this case the output of the transceiver is a Manchester-coded signal without error correction that falls under microcontroller responsibility.

8/104

L9663 Overall description

# 1.3 VQFPN28 pins description

RESETN VINTD DGND Σ CS SYNC1 21 SCLK DOUT1 20 MOSI 2 CLKIN 3 19 NC SYNC2 4 18 VGS 17 DOUT2 5 VASSUP 6 **16** VΒ NC BH1 15 BH2 GAPGPS01664

Figure 2. VQFPN28 pins connection diagram (top view)

Table 2. VQFPN28 pin-out

| Pin | Name              | Name Description                                                           |        | type   |

|-----|-------------------|----------------------------------------------------------------------------|--------|--------|

| 1   | SYNC1             | Direct interface sync pulse trigger 1                                      | I      | local  |

| 2   | DOUT1             | Direct interface 1/Interrupt 1                                             | 0      | local  |

| 3   | CLKIN             | External clock input                                                       | I      | local  |

| 4   | SYNC2             | Direct Interface sync pulse trigger 2                                      | I      | local  |

| 5   | DOUT2             | Direct interface 2/Interrupt 2                                             | 0      | local  |

| 6   | NC <sup>(1)</sup> | -                                                                          | -      | -      |

| 7   | BH1               | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 1 | I/O    | local  |

| 8   | BL1               | Bootstrap capacitor pin 2, transceiver 1                                   | I/O    | local  |

| 9   | GND1              | Ground return for PSI5 interface (analog ground and substrate ground)      | supply | local  |

| 10  | PSI1              | PSI5 Interface 1                                                           | I/O    | global |

| 11  | V <sub>AS</sub>   | PSI5 Interface pre-regulated voltage supply                                | supply | local  |

| 12  | PSI2              | PSI5 Interface 2                                                           | I/O    | global |

| 13  | GND2              | Ground return for PSI5 interface (analog ground and substrate ground)      | supply | local  |

| 14  | BL2               | Bootstrap capacitor pin 2, transceiver 2                                   | I/O    | local  |

| 15  | BH2               | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 2 | I/O    | local  |

Overall description L9663

Table 2. VQFPN28 pin-out (continued)

| Pin | Name               | Description Pin typ                              |        | type   |

|-----|--------------------|--------------------------------------------------|--------|--------|

| 16  | V <sub>B</sub>     | Input voltage supply                             | supply | global |

| 17  | V <sub>ASSUP</sub> | VAS pre-regulator and charge pump voltage supply | supply | global |

| 18  | V <sub>GS</sub>    | Gate driver for V <sub>AS</sub> pre-regulator    | I/O    | local  |

| 19  | NC <sup>(2)</sup>  | -                                                | -      | -      |

| 20  | MOSI               | SPI input                                        | I      | local  |

| 21  | SCLK               | SPI Clock                                        | I      | local  |

| 22  | CS                 | SPI Chip Select                                  | I      | local  |

| 23  | RESETN             | Reset                                            | I      | local  |

| 24  | TM                 | Test-mode pin <sup>(3)</sup>                     | I      | local  |

| 25  | V <sub>INTD</sub>  | Internal digital supply voltage                  | supply | local  |

| 26  | DGND               | Digital ground                                   | supply | local  |

| 27  | V <sub>DD</sub>    | Digital I/O supply                               | supply | local  |

| 28  | MISO               | SPI output                                       | 0      | local  |

<sup>1.</sup> Not connected internally, must be left open.

<sup>2.</sup> Not connected internally, it can be connected to GND externally.

<sup>3.</sup> It must be connected to GND, for safety reasons.

L9663 Overall description

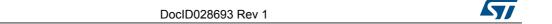

# 1.4 TQFP32 pins description

Figure 3. TQFP32 pins connection diagram (top view)

Note:

The exposed pad is electrically shorted to the substrate and to pins GND1 and GND2. These three nodes have to be kept shorted on the application.

Table 3. TQFP32 pin-out

| Pin | Name              | Description                                                                |     | type  |

|-----|-------------------|----------------------------------------------------------------------------|-----|-------|

| 1   | SYNC1             | Direct interface sync pulse trigger 1                                      | I   | local |

| 2   | DOUT1             | Direct interface 1/Interrupt 1                                             | 0   | local |

| 3   | CLKIN             | External clock input                                                       | I   | local |

| 4   | NC <sup>2</sup>   | -                                                                          | -   | -     |

| 5   | SYNC2             | Direct Interface sync pulse trigger 2                                      | I   | local |

| 6   | DOUT2             | Direct interface 2/Interrupt 2                                             | 0   | local |

| 7   | NC <sup>(1)</sup> | -                                                                          | -   | -     |

| 8   | BH1               | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 1 |     | local |

| 9   | BL1               | Bootstrap capacitor pin 2, transceiver 1                                   | I/O | local |

Overall description L9663

Table 3. TQFP32 pin-out (continued)

| Pin Name Description Pin type |                    |                                                                            |          |        |  |

|-------------------------------|--------------------|----------------------------------------------------------------------------|----------|--------|--|

| PIN                           | Name               | Description                                                                | Pin type |        |  |

| 10                            | GND1               | Ground return for PSI5 interface (analog ground and substrate ground)      | supply   | local  |  |

| 11                            | PSI1               | PSI5 Interface 1                                                           | I/O      | global |  |

| 12                            | $V_{AS}$           | PSI5 Interface pre-regulated voltage supply                                | supply   | local  |  |

| 13                            | NC <sup>(2)</sup>  | -                                                                          | -        | -      |  |

| 14                            | PSI2               | PSI5 Interface 2                                                           | I/O      | global |  |

| 15                            | GND2               | Ground return for PSI5 interface (analog ground and substrate ground)      | supply   | local  |  |

| 16                            | BL2                | Bootstrap capacitor pin 2, transceiver 2                                   | I/O      | local  |  |

| 17                            | BH2                | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 2 | I/O      | local  |  |

| 18                            | NC <sup>(1)</sup>  | -                                                                          | -        | -      |  |

| 19                            | V <sub>B</sub>     | Input voltage supply                                                       | supply   | global |  |

| 20                            | V <sub>ASSUP</sub> | VAS pre-regulator and charge pump voltage supply                           | supply   | global |  |

| 21                            | V <sub>GS</sub>    | Gate driver for V <sub>AS</sub> pre-regulator                              | I/O      | local  |  |

| 22                            | NC <sup>2</sup>    | -                                                                          | -        | -      |  |

| 23                            | MOSI               | SPI input                                                                  | I        | local  |  |

| 24                            | SCLK               | SPI Clock                                                                  | I        | local  |  |

| 25                            | CS                 | SPI Chip Select                                                            | I        | local  |  |

| 26                            | RESETN             | Reset                                                                      | I        | local  |  |

| 27                            | TM                 | Test-mode pin <sup>(3)</sup>                                               | I        | local  |  |

| 28                            | NC <sup>(2)</sup>  | -                                                                          | -        | -      |  |

| 29                            | V <sub>INTD</sub>  | Internal digital supply voltage                                            | supply   | local  |  |

| 30                            | DGND               | Digital ground                                                             | supply   | local  |  |

| 31                            | $V_{\mathrm{DD}}$  | Digital I/O supply                                                         | supply   | local  |  |

| 32                            | MISO               | SPI output                                                                 | 0        | local  |  |

<sup>1.</sup> Not connected internally, must be left open.

<sup>2.</sup> Not connected internally, it can be left open or connected to GND externally.

<sup>3.</sup> It must be connected to GND, for safety reasons.

L9663 Overall description

# 1.5 Maximum ratings

Within the maximum ratings, no damage to the component shall occur. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

All maximum ratings can occur at the same time.

All analog voltages are related to the potential at substrate ground (GND1 and GND2, internally shorted), all digital voltages are related to DGND.

Operative voltage conditions are specified in Section 6.

Table 4. Pin maximum ratings

| Symbol                                   | Description                                                                                  | Min   | Max                      | Unit |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------|-------|--------------------------|------|--|--|--|

| Power supp                               | Power supply                                                                                 |       |                          |      |  |  |  |

| V <sub>B</sub> , V <sub>ASSUP</sub>      | Input voltage range                                                                          | -0.3  | 40                       | V    |  |  |  |

| V <sub>AS</sub>                          | Pre-regulated voltage range                                                                  | -0.3  | 40                       | V    |  |  |  |

| $V_{DD}$                                 | Supply voltage range for digital I/O pins                                                    | -0.3  | 6.5                      | V    |  |  |  |

| V <sub>INTD</sub>                        | Internal digital supply voltage                                                              | -0.3  | 4.6                      | V    |  |  |  |

| BHx, BLx                                 | Voltage range of bootstrap capacitor or SYNC voltage supply (from ECU)                       | -0.3  | 40                       | V    |  |  |  |

| Other pins                               |                                                                                              |       |                          | •    |  |  |  |

| PSI1, PSI2                               | Voltage of sensor interface                                                                  | -1.5  | 40                       | V    |  |  |  |

| V <sub>GS</sub>                          | Pre-regulator gate voltage range                                                             | -0.3  | 40                       | V    |  |  |  |

| RESETN                                   | Reset input pin range                                                                        | -0.3  | 6.5                      | V    |  |  |  |

| TM                                       | Test mode input pin range                                                                    | -0.3  | 6.5                      | V    |  |  |  |

| CLKIN                                    | Clock input pin range                                                                        | -0.3  | 6.5                      | V    |  |  |  |

| CS, SCLK,<br>MOSI                        | SPI communication pin range                                                                  | -0.3  | 6.5                      | V    |  |  |  |

| MISO                                     | SPI communication pin range                                                                  | -0.3  | V <sub>DD</sub> +0.3≤6.5 | V    |  |  |  |

| D <sub>OUT1</sub> ,<br>D <sub>OUT2</sub> | Direct interface pin range                                                                   | -0.3  | V <sub>DD</sub> +0.3≤6.5 | V    |  |  |  |

| SYNC1,<br>SYNC2                          | Sync pulse trigger input range                                                               | -0.3  | 6.5                      | V    |  |  |  |

| ESD robusti                              | ness                                                                                         |       |                          | •    |  |  |  |

| -                                        | ESD according to Human Body Model (HBM), Q100-002 for pins PSIx, VB, VASSUP; (100 pF/1.5 kΩ) | ±4000 | -                        | V    |  |  |  |

| -                                        | ESD according to Human Body Model (HBM), Q100-002 for all other pins; (100 pF/1,5 kΩ)        | ±2000 | -                        | V    |  |  |  |

| -                                        | ESD according to Charged Device Model (CDM), Q100-011 Corner pins                            | ±750  | -                        | V    |  |  |  |

| -                                        | ESD according to Charged Device Model (CDM), Q100-011 Non-corner pins                        | ±500  | -                        | V    |  |  |  |

Overall description L9663

Table 4. Pin maximum ratings (continued)

| Symbol         | Description                                    | Min | Max | Unit |  |  |

|----------------|------------------------------------------------|-----|-----|------|--|--|

| Temperature    | Temperature                                    |     |     |      |  |  |

| T <sub>a</sub> | Ambient operating temperature range            | -40 | 140 | °C   |  |  |

| T <sub>j</sub> | Junction operating temperature range           |     | 175 | °C   |  |  |

| Rthja          | Package thermal resistance (on PCB JEDEC 2s2p) |     | 45  | °C/W |  |  |

The device offers a high level of flexibility on power supply configuration. The calculated maximum power dissipation can reach 1.6 W considering the worst case configuration.

# 1.6 Detailed block diagram

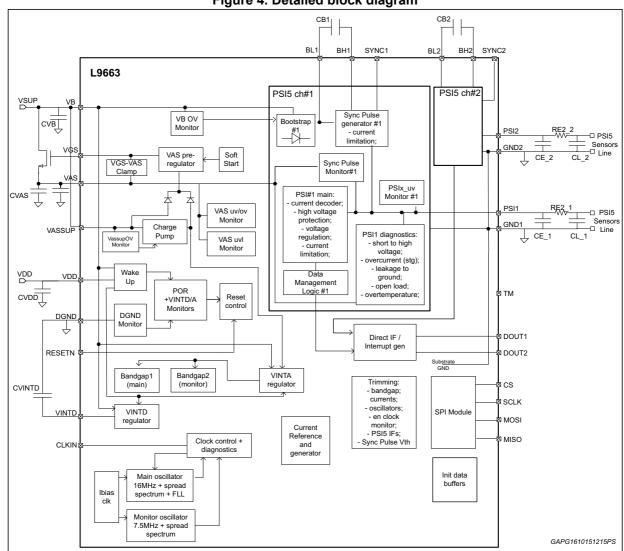

Figure 4. Detailed block diagram

L9663 Overall description

The high supply voltage of the IC can be a battery or a regulated voltage provided by the ECLI

To reduce disturbances on the voltage supply which might have a negative influence on the PSIx interface and therefore lead to bit errors, a PI filter can be employed in the supply line.

Possible power supply configurations<sup>(b)</sup> are:

- VB, VASSUP connected to VSUP, VAS and V<sub>SYNCx</sub> generated by the IC with external components (as in the above figure);

- VAS, VB, VASSUP connected to VSUP, V<sub>SYNCx</sub> generated by bootstrap, no external MOS, VGS pin open;

- VB, VASSUP, BH1, BH2 connected to VSUP, no external capacitors CBx, VAS generated by IC pre-regulator and external MOS;

- VB connected to VSUP, VASSUP connected to 0V (charge pump off), VAS supplied by an external source and VSYNCx generated by the IC with external components.

The values of the external components RE2\_x, CE\_x and CL\_x are specified in PSI5 standard.

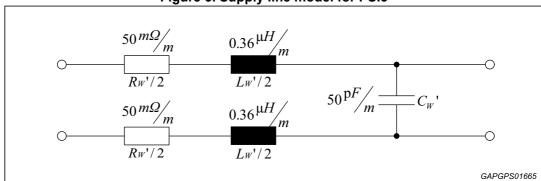

The assumed line model for the PSI5 interface on which the transceiver IC operates is as follows:

Figure 5. Supply line model for PSI5

b. The high supply voltage VSUP must be in the correct operative range of connected pins.

DocID028693 Rev 1

**Overall description** L9663

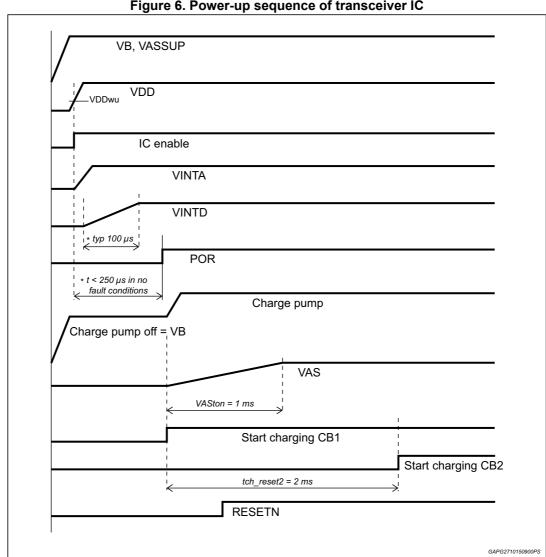

#### 1.7 Power up sequence

When VDD is higher than the startup threshold and VB is available the IC is switched on.

To reduce disturbances on its voltage supply, the transceiver IC does a staggered startup of its internal voltage supplies.

While RESETN is low, the PSIx lines are deactivated to reduce power consumption and to increase system safety.

The transceiver IC can be configured to operate in the standard current mode (4 mA up to 19 mA) or in the extended current mode (4 mA up to 35 mA). Moreover, both channels can be configured to allow the extension to a maximum quiescent current of 45 mA, only in case of asynchronous mode.

The synchronous sensors send data only after a synchronous pulse is triggered via the dedicated pin or by SPI.

The following figure shows a power-up example.

Figure 6. Power-up sequence of transceiver IC

L9663 Power supply

#### 2 **Power supply**

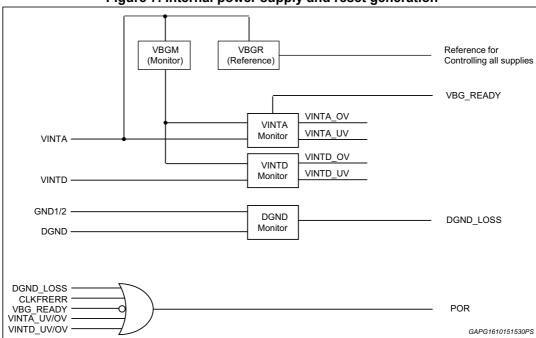

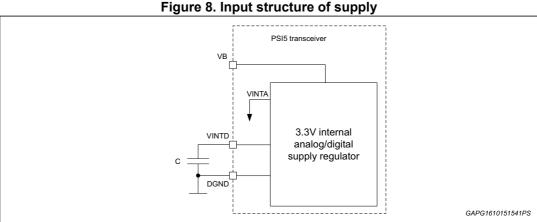

#### Internal supply 2.1

The internal analog and digital part is supplied by the supply voltage VB. The necessary power supply for the internal digital and analog parts is generated internally by the transceiver IC. The generated voltage is monitored. In case of under/over voltage, the transceiver IC performs a power on reset (POR).

Figure 7. Internal power supply and reset generation

### Basic features:

- Voltage regulator

- Under / Over voltage monitoring

- Reset generation of the IC in case of under / over voltage

Power supply L9663

A ceramic capacitor with a typical capacitance of 100 nF is required as a blocking capacitor close to the pins  $V_{DD}$  and VB.

The internal supply voltages  $V_{INTD}$  (supply voltage for digital part) and  $V_{INTA}$  (supply voltage for analog part) are monitored for under voltage and over voltage to prevent the transceiver IC from malfunction. The reference for the voltage monitoring is a bandgap voltage, supplied by  $V_{INTA}$ . The device integrates two separated instances of bandgap voltage regulators; one of these bandgaps is used as voltage reference for the internal regulators, while the other one is used for monitoring the voltage levels. In case of under or over voltage, the transceiver IC is set into reset: outside reset thresholds full functionality is granted.

The functionality of the digital part only depends on the voltages on  $V_{\text{INTD}}$ . In order to improve noise emissions and stability of the regulator, the digital supply line needs an external decoupling 100 nF ceramic capacitor to be connected between  $V_{\text{INTD}}$  and DGND and close to them.

DGND ground line is protected against ground loss scenarios. In case DGND line would be at least DGND<sub>OPEN</sub> above the reference ground lines GND1/2, a POR is asserted.

The transceiver IC returns to normal operation with full functionality as soon as the POR is released.

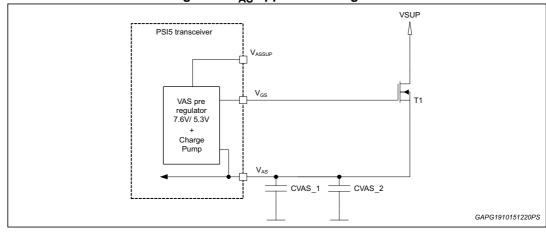

# 2.2 V<sub>AS</sub> supply and pre-regulator

The  $V_{AS}$  pre-regulator sets the  $V_{AS}$  voltage if no regulated voltage with the necessary value is available in the ECU.

The pre-regulator is designed for two different regulated voltages at  $V_{AS}$ : 5.3 V or 7.6 V, selectable by a SPI command. The supply of external FET can be chosen at application level according to the required voltage at VAS pin.

Two possible applications are:

- V<sub>AS</sub> typical of 5.3 V; external FET supplied by ECU internal voltage, typically 6 V.

- V<sub>AS</sub> typical of 7.6 V; external FET directly supplied from battery, from 8 V to 35 V.

#### Basic features:

- Gate control for an external n-ch FET transistor with integrated charge pump stage

- Gate control is switched on if no power on reset condition is present

- Configurable output voltage: either 5.3 V or 7.6 V.

577

L9663 Power supply

Figure 9. V<sub>AS</sub> application diagram

When POR is active, the  $V_{GS}$  output pin is driven low to keep external N-ch switched off. The  $V_{AS}$  pre-regulator is automatically activated with a soft start at POR and automatically switched off, after a filter time, if  $V_{AS}$  falls below  $V_{VASU\_off}$ . It can be later controlled off or on by means of a dedicated VAS\_EN bit. To protect the external component from exceeding maximum allowed gate to source voltage if VAS is shorted to ground by a fault, an internal passive clamp is implemented on  $V_{GS}$ .

The integrated charge pump, supplied by VASSUP, assures proper voltage regulation in case of low voltage conditions. It is automatically switched off in case the voltage on  $V_{ASSUP}$  is high enough to allow proper regulation.

If the pre-regulator is not needed, the VAS\_EN bit can be set to '0' to switch off the pre-regulator itself. The pin  $V_{GS}$  can be left open, and the  $V_{AS}$  pin directly connected to the regulated voltage in the ECU.

The pre-regulator is active independently of RESETN input pin if the supply voltage of the internal analog/digital circuits is available.

# 2.3 Voltage supply for synchronous pulse generation V<sub>SYNCx</sub>

To use synchronous PSI5 sensors and for ECU-to-sensor communication, the transceiver IC needs to generate synchronization pulses. These require a voltage which is higher than  $V_{AS}$ .

This module generates the necessary voltage  $V_{SYNCx}$  by two bootstrap circuits. Two capacitors with two transceiver IC pins each are used as external components of this module.

The bootstrap blocks start pre-charging the external capacitors after POR (with a 2 ms time gap between the first and second block).

The bootstrap circuits are enabled by default, activated by internal logic with timing sync pulses dependent, and can be disabled later on through a dedicated SPI command. The bootstrap block can recharge the capacitor so that subsequent sync pulses are allowed with a minimum period of 200  $\mu$ s.

A useful option is the possibility to connect the BHx pin directly to a high voltage rail. In this configuration, VB has also to be connected to the same high voltage rail and the bootstrap

Power supply L9663

circuit can be bypassed by disabling it through the dedicated SPI command (bit 12 of CH1 CR2, CH2 CR2, writable during PROG phase).

The bootstrap blocks are automatically switched off in case the voltage on VB is high enough to allow proper regulation. In this case both CBx capacitors should be omitted.

The  $V_{SYNCx}$  voltage can supply a 2.5 V minimum sync pulse as per PSI5 v2.x low power mode down to  $V_B$  = 4.8 V and a 3.5 V minimum sync pulse down to  $V_B$  = 5.2 V, with a maximum quiescent current level of 35mA and down to minimum 200  $\mu$ s period between sync pulses. The block is protected against reverse feeding to  $V_B$ .

The bootstrap module is fully functional while V<sub>B</sub> and V<sub>DD</sub> are all inside their specified voltage ranges.

## 2.4 Power supply for PSI5 sensor line

Basic features:

- Reverse voltage protection structure

- Voltage limitation and current limitation for PSIx input/output

- Protection against negative voltages on PSIx transceiver pin due to ground shifts

- Disconnection of PSIx from V<sub>AS</sub> in failure cases

The PSI5 transceiver IC is supplied directly from the pin  $V_{AS}$ . It includes blocks with the following functionalities:

- Reverse voltage protection structure and gate driver block for

- Voltage clamp on PSIx in case of V<sub>AS</sub> fault

- Backward voltage supply blocking mechanism from PSIx to V<sub>AS</sub>

- Sensor supply by switching V<sub>AS</sub> to the PSIx pin

- Disconnection of PSIx from the VAS if required or in failure cases

- Under voltage detection block to implement cross coupling test between the two channels (see Section 3.7.5 and 4.2)

- Receiver block for Sensor Data receive (see Section 3.1 for details).

The reverse voltage protection structure is also used to switch off the PSIx transceiver channel, if:

- the local junction temperature exceeds its maximum rating and the channel is in overcurrent

- an overcurrent condition on PSIx is detected (STG)

- a short to battery is detected

- it is requested via SPI or RESETN pin.

In case of short to battery on the PSIx lines, there is no interference to any other IC pin/supply including SPI.

The two interfaces can be enabled by SPI command, and the enable has effect only if VAS under voltage signals are not asserted.

If an over temperature condition (OT) occurs, the interface that is also in overcurrent condition is switched off and a failure bit is set. The fault bit is latched and cleared only when a SPI switch off command is sent for confirmation on the line that was automatically switched off. The shutoff of one interface does not affect the second interface.

20/104 DocID028693 Rev 1

L9663 Power supply

If an overcurrent condition on PSIx is detected, the current limitation is active and after a filter time  $t_{\text{filt}}$  a fault bit is set and the interface is shut off. In order to switch on again, the interface must be first switched off by SPI and then switched on, as for over temperature.

The channels' switch off by overcurrent can be disabled if the corresponding bits STG MASK for every channel are set in the SPI registers.

During start up, a configurable blanking time is implemented (128  $\mu$ s/5 ms/10 ms, see BLANKING\_SEL bits in SPI register); during this time current limitation is active, even though the interface will not shut off for overcurrent, thermal shutdown is always active, the PSI5 receiver is disabled, and some fault flags are masked (short to battery, under voltage, leakage to ground).

The quiescent current is monitored for minimum and maximum value, depending on the range selected by SPI (CH1\_CR1, QC\_SEL bits). In failure case the corresponding bit in the diagnostic register is set (SR2).

The voltage at PSIx is compared with VAS to monitor short to battery condition: if an over voltage occurs PSIx is disconnected from VAS and the corresponding bit in diagnostic register is set (STBx in SR2), In over voltage condition also low quiescent current bit is set (OLx in SR2) after a transient time.

Power supply L9663

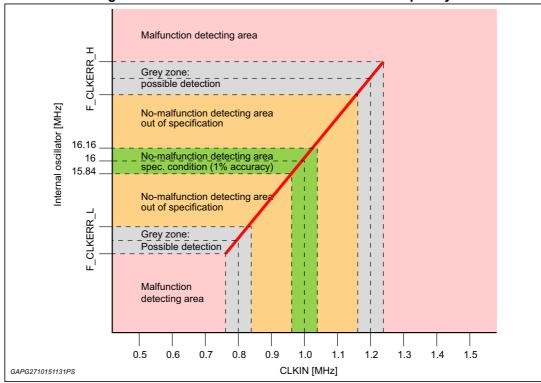

## 2.5 Frequency references

The device comes with an integrated accurate oscillator, used for any of the internal circuitry, with no need of external connections or components. The nominal clock frequency is 16 MHz with a ±5% accuracy.

Should the application need some more accurate timing reference, a discrete pin CLKIN is provided. An external clock reference can be connected to this pin. The PSI5 transceiver IC offers an integrated FLL module that tracks this input to provide a high accurate clock reference (±1%). This feature can be used especially if accurate timeslot control needs to be achieved.

External signal on CLKIN can be configured as follows (see CLKIN\_CFG bits in GCR1 SPI register):

- 1 MHz square signal

- 4 MHz square signal

- No signal (Not connected pin)

Pin CLKIN can be grounded when not used. The pin input circuit implements a pull-down structure.

The FLL module tracking the CLKIN signal is off by default.

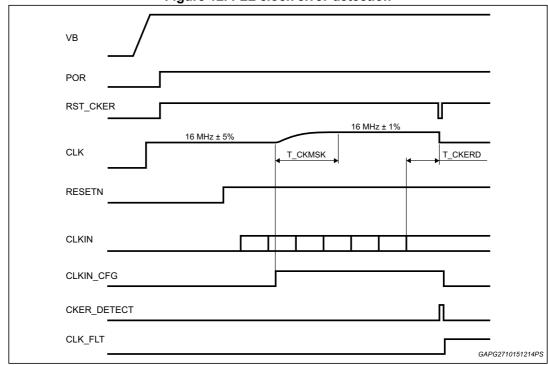

The PSI5 transceiver IC implements a safety function for monitoring the device clock reference, both in case it is derived from the CLKIN signal through the FLL module or internally generated. In the first condition the monitoring is always activated, while in the second condition it can be enabled by programming in ST (storing a '1' in a dedicated OTP<sup>(c)</sup> bit) and another oscillator generator is used for monitoring.<sup>(d)</sup>

When the CLKIN\_CFG is set, the FLL tries to close the LOOP and a mask counter of T\_CKMSK (16 ms MAX) is used to count the maximum transient time.

During this time, regardless the CLK frequency the CKER\_DETECT is masked, i.e the device doesn't detect a clock error.

After this time, if the CLKIN frequency is in the correct range, the loop is closed and the CLK frequency is inside the 1% tolerance; if the CLKIN frequency is outside the malfunction detecting range, a clock error is detected after a detection time  $T_CKERD$ , the device is reset and the  $CLK_FLT$  is set so that the  $\mu C$  can read the reset source.

The T\_CKERD and the transient during detection time depend on the CLKIN frequency behavior; the figure below shows the behavior of the internal oscillator as function of the external one.

22/104 DocID028693 Rev 1

c. One Time Programmable bit: it can be programmed by ST only.

d. For clock error detection by internal monitor oscillator see errata n.3367, Section 7: Errata.

L9663 Power supply

Figure 11. Internal oscillator vs external clock frequency

If the CLKIN is stuck the device behavior is shown in the figure below: in this case during the detection time the tolerance is still inside the 1% tolerance until the device enters reset (T\_CKERD max 260  $\mu$ s).

Figure 12. FLL clock error detection

Power supply L9663

## 2.6 Reset handling

Four different sources are considered in resetting the IC:

- POR (Power On Reset, see Section 2.1)

- RESETN pin

- SW\_RESET

- CKER\_DETECT

All these sources of reset, when asserted, will switch off the PSIx lines and reset to default value the device registers (including those registers for configuration).

Additionally to the hardware resets (by pin/POR), a reset can also be initiated by software (SW\_RESET).

The command SW\_RESET initiates a soft reset-sequence if all of the following conditions are fulfilled (see also the DCR register in SPI section):

- unlocked state: it means that if the UNLOCK command is not received the command SW\_RESET has no effect;

- The command SW\_RESET is sent in next SPI communication of the unlock command.

A SW\_RESET initiates soft reset-sequence and resets all digital parts of the device, except POR and RST flag that is set in SR3 register.

24/104 DocID028693 Rev 1

L9663 Satellite interface

## 3 Satellite interface

## 3.1 Receiver with digital sampling and filtering

This module has the following features:

- The output current signal is mirrored and converted to the digital domain

- Automatic synchronization on entire PSI5 frames

- Fast DAC digital conversion of sensed currents with digital filtering

- Static DC current set point tracking of PSI5 guiescent current.

- Tracking of modulated PSI5 current signal

The quiescent current tracking can be configured to work in two ways (reg. ADVSET1, ADVSET3, bits FREEZE\_DIS): continuous mode tracking or tracking between consecutive frames till the first edge of a new frame is recognized. In the second case, the quiescent current is frozen till the end of the frame.

To recognize the PSI5 current signal level the receiver compares the digitally converted and filtered current with a threshold. This threshold can be fixed or dynamic, depending on the configuration selected by SPI (reg. ADVSET).

In fixed threshold mode the user must program the right delta current threshold, according to the application requirements. The threshold is obtained as tracked quiescent current plus the programmed threshold.

In dynamic threshold mode, the threshold is dynamically adapted considering the PSI5 current input signal.

For detailed explanation on all the possible configurations refer to ADVSET registers section.

Depending on the selected configuration, the threshold for the sensor signal can be permanently tracked, separately for each PSI5 interface. The IC is designed to compensate erratic changes of the quiescent current in the bus according to PSI5 standard requirements.

The v2.x standard low power mode is not supported with dynamic threshold mode.

Micro cuts up to 10µs do not affect the DC current tracking in a way that more than one frame will be lost.

The PSI5 Receiver is designed to operate at:

- 83.3 Kbps typical (slow mode)

- 125 Kbps typical (standard mode)

- 189 Kbps typical (fast mode).

Satellite interface L9663

### 3.2 Manchester decoder and error detection

Basic features:

- Detection of start bits "00"

- Synchronization with sensor to ECU frame

- Manchester decoding according to PSI5 specification (v 1.3 or v 2.x, depending on the chosen configuration)

The Manchester decoder takes the bit stream which the receiver has as its output and decodes the incoming data frames from this bit stream.

It can be programmed to measure the period of start bits sent by the sensors and double-check the timing of the following data bits with respect to the synchronization given by the start bits or to validate the data bits according to the PSI5 protocol baud rate configured by the microcontroller. The tolerance for timing checks is 20%: in case of timing error a Manchester error is reported.

A Manchester Decoder Error occurs if one or more of the following are true:

- Start bit error outside of selected operating range

- Data length error or stop bit error

- Bit time error (a data bit edge is not received inside the expected time window)

- Timing violation on slot when standard timeslot monitor is enabled

In case a Manchester error is detected the corresponding error code is set [v. Error codes table, Section 3.3.2].

#### 3.3 Receive block

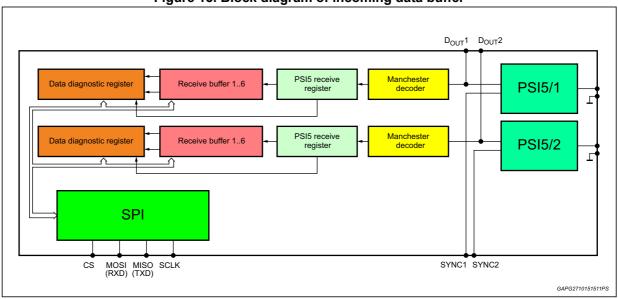

This block includes the buffer for incoming sensor data and diagnostic results. It includes:

- PSI5 receive registers

- Sensor data buffer

- Interrupt generation for the microcontroller

L9663 Satellite interface

### 3.3.1 PSI5 receive register

This module includes the sensor data storage and diagnostic.

Basic features:

- Storage of Sensor data

- Error handling

Figure 13. Block diagram of incoming data buffer

#### **PSI5** Receive Register

The transceiver IC has a PSI5 Receive Register for each PSI5 transceiver.

Each PSI5 Receive Register can store up to 28Bit data and up to 3Bit error check (CRC or parity) for each of the incoming frames. According to the PSI5 powertrain substandard, up to 6 frames can be sent between two synchronous pulses. For every frame, a frame configuration register is available which defines:

- Data Region 8 ... 28 bit

- CRC or Parity Bit (3 or 1 bit)

Depending on the desired configuration (SPI bit CRC\_CK of GCR1 register), the parity/CRC bits handling can be done in the following ways:

- Parity/CRC bits are generated by the sensor; the transceiver IC simply passes data+parity/CRC bits to the  $\mu$ C via SPI and the  $\mu$ C performs parity/CRC check

- Parity/CRC bits are calculated by the transceiver IC and in case of a correct parity bit/checksum, the payload of the frame is stored in the receive buffer; otherwise, if the CRC calculation shows a wrong result, the Parity Error code is stored.

The SPI register bit CRC\_CK is valid for all sensors of both interfaces.

After all bits have been received the data will be transmitted into the corresponding part of the receive buffer.

Satellite interface L9663

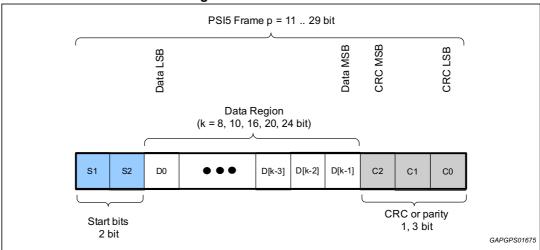

Each PSI5 data frame consists of a total p bits containing:

- two start bits (S1 and S2),

- one parity bit (P) with even parity or alternatively 3 CRC bits (C0, C1, C2), and

- a data region (D0 ... D[k-1]) with k = 8...28 bit.

The total length of a PSI5 frame is p=k+3 data bits (in case of frames with parity bit) or p=k+5 data bits (in case of frames with CRC).

Data bits are transmitted LSB first. The parity or CRC check bits cover the bits of the entire data region.

Figure 14. PSI5 v1.3 frame

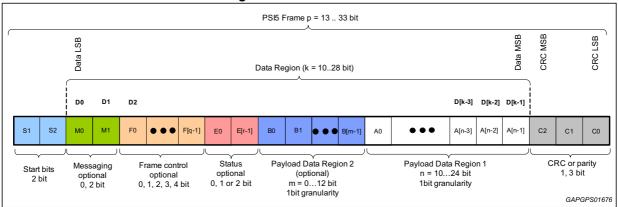

Figure 15. PSI5 v2.0 frame

L9663 Satellite interface

In case of PSI5 v2.x, the length of the data region can vary between  $k = 10 \dots 28$  bits, with 1-bit granularity. The data region can be split into the following fields and regions:

- Signal payload region 1 with data bits A0 ... A[n-1] (scalable n = 10...24 with 1-bit granularity)

- Signal payload region 2 with data bits B0 ... B[m-1] (scalable m = 0...12 with 1-bit granularity)

- Sensor status E0.. E[r-1] (optional r = 0, 1 or 2 bit)

- This optional status bit can be used to show that the data of the current frame are faulty.

- Frame control, type of frame F0, ... F[q-1] (optional q = 0, 1, 2, 3 or 4 bit)

- This frame control can be used to number the frames which are sent after a sync pulse.

- Serial (slow) messaging channel (optional) M0, M1 (optional 0 or 2 bit)

#### Time slot monitoring

The time slot monitoring is active only in synchronous mode.

The time slot monitoring is required to check if the sensors connected to the transceiver work properly in terms of timing, i.e. if they are sending data frames within their defined time slot.

#### Basic features:

- 3 configurable modes

- Failure bit

During a synchronous pulse period ( $T_{SYNC}$ ), a maximum number of 6 frames can be configured. Each frame has its own time slot, to be configured through dedicated configuration registers. The registers contain the reference time needed to check if the sensor data is transmitted during the defined time slot.

The resolution of time slots is 1  $\mu$ s. The time slot monitoring timings are applied starting from the internal sync pulse trigger. This internal trigger falls  $t_{d\_SPI}$  (or  $t_{d\_SYNC}$ , depending on sync pulse trigger configuration) after the external one (via  $\overline{SPI}$  or  $\overline{SYNC}$  pin).

Three different configurations for the time slot monitoring are available:

- Standard configuration: monitoring the correct start and end time of a unique frame within a time slot

- Simple configuration: monitoring only the end time of a frame within a time slot

- No monitoring configuration: monitoring is disabled and data are stored in successive slots.

The time slot monitoring can be activated/deactivated separately for each interface (registers CHx\_CR1, bits TSMx\_SEL).

In case of standard configuration, the IC accepts as valid frame in a timeslot only a frame which starts and ends within its timeslot; if more than one valid frame is received within its timeslot, only the last one received is kept.

On the other side, in case frames span across slots, the frame is discarded and the error code 1FC (timing violation) is stored in the correspondent buffer; in this case the decoder is reset at every slot start. After this reset if a frame was being decoded, a slot error is set in the previous slot but no slot error is set. Then the Manchester FSM after reset checks again

Satellite interface L9663

for two valid start bits and so a new incoming frame can be stored without error in the new timeslot.

In the simple configuration, the last valid message which ends in a timeslot is stored in the buffer of the slot (so if a frame is currently stored in a timeslot and an incoming frame ends in this timeslot, the old data are overwritten). In this mode slot error is never set.

It is also possible to disable the time slot monitoring and in this case, no timing check is done: the first frame is assigned to the first buffer, the second to the second, and so on. This means that the buffer index is incremented every time a frame is received both valid and invalid (Manchester communication error).

After reset, the default mode for the time slot monitoring is "monitoring disabled".

### 3.3.2 Sensor data buffer

To avoid loss of data, a data buffer for each PSI5 transceiver is necessary. While the data buffer is being read by SPI, at the beginning of the sensor data transfer the data register is cleared and a new data frame can be accepted.

The incoming PSI5 sensor data, together with CRC and SID/GBIT (if selected) are written into a receive buffer, which is large enough to hold the data of one sync pulse cycle (i.e. up to six sensors). In order to avoid data-mixing between different cycle times the data must be fetched by the  $\mu$ C before the next transmission cycle starts.

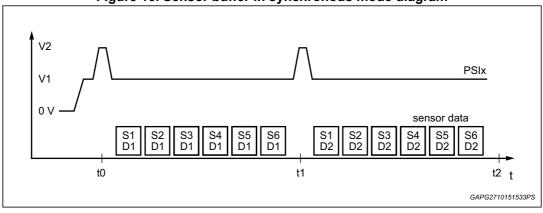

The figure below shows how sensor buffers are updated in synchronous mode.

At t<sub>0</sub> the buffers contain no data; then a sync pulse is sent and data are received and stored in each register during the cycle time; so at t1/t2 the buffers contain sensors data of the current cycle time.

Figure 16. Sensor buffer in synchronous mode diagram

Table 5. Time (t0-t2) vs SensorData

| Time/Sensor | tO           | t1  | t2  |

|-------------|--------------|-----|-----|

| SensorData1 | Buffer Empty | D11 | D12 |

| SensorData2 | Buffer Empty | D21 | D22 |

| SensorData3 | Buffer Empty | D31 | D32 |

| SensorData4 | Buffer Empty | D41 | D42 |

L9663 Satellite interface

Table 5. Time (t0-t2) vs SensorData (continued)

| Time/Sensor | t0           | t1  | t2  |

|-------------|--------------|-----|-----|

| SensorData5 | Buffer Empty | D51 | D52 |

| SensorData6 | Buffer Empty | D61 | D62 |

In case of sensor or channel fault conditions, the following codes are sent in the first 10 bits of the data field. The lower 10 bits are filled with '0'.

Table 6. Error codes in sensor communication

| Error Code | Definition                                                                                   |  |  |

|------------|----------------------------------------------------------------------------------------------|--|--|

| 1FC        | Manchester error (non-valid start bits, incorrect number of bits received, timing violation) |  |  |

| 1F8        | Parity / CRC error <sup>(1)</sup>                                                            |  |  |

| 1F1        | Physical layer error (short to ground, leakage to GND, over-temperature, open load)          |  |  |

| 1F0        | Data buffer empty                                                                            |  |  |

| 1F2        | Short to battery                                                                             |  |  |

| 1F9        | Sync pulse error                                                                             |  |  |

Used only in case the CRC check computation is assigned to the IC (CRC\_CK bit set to 1); otherwise the sensor data will be written in the buffer.

If more than one data is present, the faults are handled with this priority scale:

Table 7. Faults priority

| rable 111 date priority |                                                                         |                |      |  |  |  |  |

|-------------------------|-------------------------------------------------------------------------|----------------|------|--|--|--|--|

| Priority                | Data                                                                    | Fault type     | Code |  |  |  |  |

| 1 (highest)             | Valid data                                                              | -              | -    |  |  |  |  |

| 2                       | Over Temperature                                                        | channel        | 1F1  |  |  |  |  |

| 3                       | Short To Ground                                                         | channel        | 1F1  |  |  |  |  |

| 4                       | Short To Battery                                                        | channel        | 1F2  |  |  |  |  |

| 5                       | Leakage To Ground                                                       | channel        | 1F1  |  |  |  |  |

| 6                       | Open Load                                                               | channel        | 1F1  |  |  |  |  |

| 7                       | Manchester Error                                                        | Sensor related | 1FC  |  |  |  |  |

| 8                       | CRC/Parity Error                                                        | Sensor related | 1F8  |  |  |  |  |

| 9                       | Sync Pulse under voltage (both Slow Vsync detection and sync UV faults) |                | 1F9  |  |  |  |  |

| 10                      | Data Buffer Empty                                                       | Sensor related | 1F0  |  |  |  |  |

In synchronous communication mode each sensor (time slot) has its own range in the data buffer. The buffer range content is overwritten if new data arrives before the old data has been read out.

Satellite interface L9663

If a channel fault occurs, the content of every sensor buffer is affected regardless the moment inside the timeslots cycle in which the fault occurs. This value will be held until the fault is cleared (reading the appropriate bit in the Status Register) or a fault with higher priority occurs.

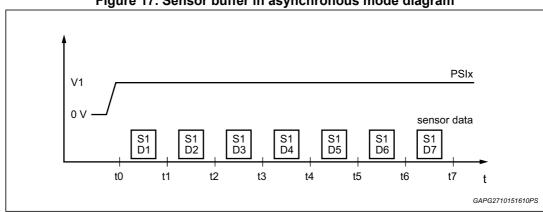

In asynchronous communication mode a six stages FIFO is implemented: the newest data is always in the data buffer range corresponding to sensor no. 1, the oldest data is in the data buffer range corresponding to sensor no. 6. When the buffer is full, the FIFO shifts the incoming data to keep always the newest data. As soon as the first data is read by SPI, the FIFO will be locked to writing, until it is emptied<sup>(e)</sup>. This situation is reported through SPI bit FIFO\_LCK.

Figure 17. Sensor buffer in asynchronous mode diagram

Table 8. Time (t0-t7) vs SensorData

| Time/Sensor | t0           | t1              | t2              | t3              | t4              | t5              | t6 | t7 |

|-------------|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|----|

| SensorData1 | Buffer Empty | D1              | D2              | D3              | D4              | D5              | D6 | D7 |

| SensorData2 | Buffer Empty | Buffer<br>Empty | D1              | D2              | D3              | D4              | D5 | D6 |

| SensorData3 | Buffer Empty | Buffer<br>Empty | Buffer<br>Empty | D1              | D2              | D3              | D4 | D5 |

| SensorData4 | Buffer Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | D1              | D2              | D3 | D4 |

| SensorData5 | Buffer Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | D1              | D2 | D3 |

| SensorData6 | Buffer Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | Buffer<br>Empty | D1 | D2 |

If a fault occurs and FIFO is unlocked, the correspondent code is written in the FIFO buffer at the current position; if more than one fault occurs at the same time the fault with the highest priority is written in the FIFO.

In both synchronous and asynchronous mode, when a valid data is read, the buffer empty code 1F0 is written in the buffer.

32/104 DocID028693 Rev 1

e. For the lock of the FIFO see errata n.1526, Section 7: Errata.

L9663 Satellite interface

As safety feature, the IC always checks that after a valid data read the code 1F0 is written in the buffer.

If this check fails a Buffer Empty Fault is latched (BEx bits in SR2 register) and it's cleared after SPI read. Buffer empty fault asserts also Global Status Bit.

In order to allow the  $\mu$ C to test this feature a test of buffer empty check is implemented (see Section 3.7.3 and STSR register for details).

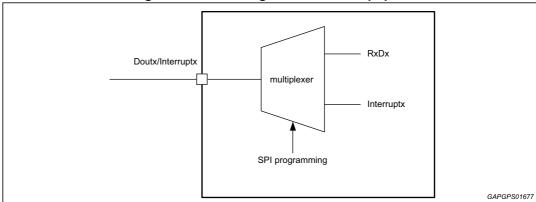

### 3.3.3 Interrupt generator

The microcontroller interrupt module describes the function of the interrupt pins to generate a microcontroller interrupt if the data buffers are filled with sensor data.

#### Basic features:

- Configurable interrupt pins

- Interrupt generation when data buffer is full

The interrupt pins generate an interrupt for the microcontroller if the receive buffer corresponding to a transceiver interface is filled completely: the interrupt pin is then reset when the receive buffer is empty.

Asynchronous operation:

The interrupt pin is set to high when the number of received data since the last reading of register is as large as the size of the receive buffer. The interrupt pin is set to low when all the buffers are empty.

Synchronous operation:

The interrupt pin is set to high when all the buffers configured by SPI are full. The interrupt pin is set to low when all the buffers are empty.

Figure 18. Block diagram with interrupt pins

After reset, the output pin is configured as DOUTx.

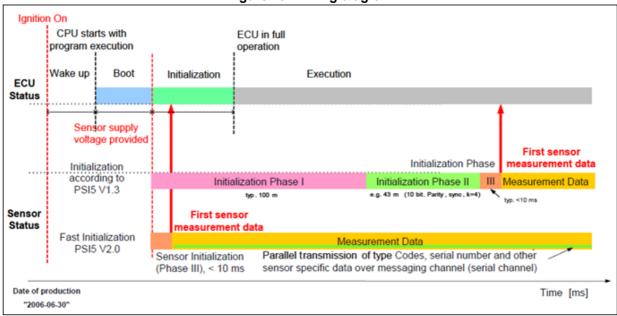

### 3.3.4 Automatic storage of sensor initialization data

If the sensor uses a data range initialization procedure and the PSI5 payload is 20 bit with 3 frame control bits, 1 status bit, 16 bit data, the device can be configured so that the initialization data is stored in the transceiver IC and can be read via SPI.

In case of serial messaging method, the data must be extracted at application layer.

Satellite interface L9663

#### Basic features:

Registers for initialization data (up to 8 init data buffer by 16 word available)

- Automatic detection of init data

- Reading via SPI

Figure 19. Timing diagram

After the activation of an interface, the transceiver IC can check for incoming sensor initialization data on that interface and store the data for further processing. This behavior is triggered by the configuration bit READ\_INIT\_DATA on that channel.

If the bit is set, an internal FSM checks for IDn and data blocks Dn in the incoming payload data on that interface and stores data in the init buffer id (init\_buf\_id) of the corresponding frame id at address n-1 in the following format:

| RegAddr | 15 (MSB) 10                                             | 9         | 6            | 5 | 0 (LSB)                                   |

|---------|---------------------------------------------------------|-----------|--------------|---|-------------------------------------------|

| n-1     | additional data from blockid<br>message (6 bits 0 bits) | data bloc | c ( 4 bits ) |   | onal data from data<br>ge (6 bits 0 bits) |

The frame control bits allow using up to 8 init data buffers when automatic storage of init data is activated and both interfaces are used (READ\_INIT\_DATA1 = READ\_INIT\_DATA2 = 1). In case only one interface is active, the IC can store up to 6 init data on that interface.

As specified in PSI5, data nibbles D2 and D3 contain the number of datablock expected for the all init procedure for each particular frame id; when all the init data are received for the engaged sensors (i.e. for the sensors which had sent at least one correct data blocks) on both the interfaces, the init\_data\_rdy is set and the  $\mu$ C can read all the init data by SPI. During reset, the incoming data buffer is cleared and the counters for each initialization data block are set to "00".

577

L9663 Satellite interface

The interface can be configured both in asynchronous and synchronous mode (in the second case, the number of bits must be the same for all the timeslots). The accepted configuration for init data is based on 20 total bits, as follows:

- 16 data bits

- 1 status bit

- 3 frame control

## 3.4 Upstream data buffer

Basic features:

- Adapts the signals delivered by Sync Pulse Timer block in order to make possible a bidirectional communication ECU to sensor

- Generates the trigger signal necessary for an event triggered sync pulse

- Provides the Sync Pulse Trigger signal to the Sync Pulse Generator

Figure 20. ECU to sensor communication diagram

The synchronization bits in the ECU to sensor communication must be programmed in the upstream data buffer by the microcontroller.

The upstream data buffer has 64 bits. The clock for the register is the output of the Sync Pulse Timer together with the trigger commands via SPI. After each request for a sync pulse, the register is shifted by one and the last bit is fed into the sync pulse trigger generator.

Depending on the data length, only a part of the upstream data buffer is used. After the writing of the relevant part of the buffer, the  $\mu$ C writes the upstream data confirm bit in the UDBCR register (bit UDBx\_RDY). After this confirmation, the trigger source can start the communication. If these data are sent, the upstream data buffer is ready for new data. This is indicated by the SPI flag UDBx\_BUSY='0'. If new data is written to the buffer while UDBx\_BUSY is still '1', the write command is ignored and the error flag UDBx\_FLT is set.

Satellite interface L9663

Besides if a new trigger is sent while the buffer is busy, again the command is ignored and the fault bit is set.

The buffer register can be reset by writing 0x00FF for channel 1 (respectively 0xFF00 for channel 2) to the SPI register DCR. After such a reset, the module will flag that it is ready for new data.

The behaviour of the sync pulse trigger generator then depends on the configuration of the transceiver IC:

- In PSI5 1.3 and 2.x mode (tooth gap method), it will mask out (i.e. ignore) the incoming sync pulse trigger if the bit is '0'. The resulting gap is defined to be a '0' in the ECU-to-sensor communication.

- In PSI5 2.x mode (pulse length method), it will generate a long sync pulse if the bit is '1' and a standard sync pulse otherwise.

The transceiver IC provides a transparent interface for ECU-to-sensor communication. This means that any data in the upstream data buffer will directly be transmitted onto the PSIx interface. The CRC calculation and data layer handling are done by the microcontroller.

# 3.5 Trigger pulse generator for synchronous pulses

This module generates the trigger signals for the transceiver interfaces. It has the following sub-modules:

- SPI-programmable sync pulse timer

- SPI command triggering

- 2 pins named SYNC1, SYNC2

The module contains the sync pulse trigger generators (one for each transceiver).

Basic features:

- Generates the sync pulse trigger at the configured time intervals

- Generates the sync pulse trigger upon the corresponding command via SPI or discrete SYNCx pins.

The trigger pulse generator generates the trigger signal which the sync pulse generator uses as its input.

The trigger pulse generator has five different configurations, which can be properly selected via SPI command:

- Triggering via SPI without upstream data buffer. The microcontroller sends the

corresponding SPI command for a sync pulse. The sync pulse trigger generator then

internally generates the appropriate sync pulses, based on the specific SPI command

sent.

- Triggering via SPI with upstream data buffer. The microcontroller sends the

corresponding SPI command for a sync pulse. Then the sync pulse trigger generator

internally generates the appropriate sync pulses, depending on the value in the

upstream data buffer.

- Triggering via SYNCx pins without upstream data buffer. When the SYNCx pin is triggered, the sync pulse trigger generator internally generates the appropriate sync pulses, based on the type of trigger (length) received on the input pin.

36/104 DocID028693 Rev 1

L9663 Satellite interface

Triggering via SYNCx pins with upstream data buffer. When the SYNCx pin is triggered, the sync pulse trigger generator internally generates the appropriate sync pulses, depending on the value in the upstream data buffer.

• Triggering via trigger pulse timer: the transceiver IC automatically generates the sync pulses at fixed time intervals, depending on the value in the upstream data buffer.

The default configuration at startup is to use the triggering via SYNCx pins without upstream data buffer.

If the triggering with upstream data buffer is used and there aren't data to be sent to the sensor, a short pulse is sent.

The switch matrix is configurable by an SPI command. It determines whether the sync pulses are triggered via SPI by the trigger generator (transceiver IC in mode 1) or by the external trigger pins (transceiver IC in mode 2).

If the trigger pulse timer is used to generate the sync pulse trigger, the interval between two pulses on interface x is configured by the SPI register SYNC Pulse Timer (SPT). It's possible also to program the delay between interface 1 and interface 2 sync pulses through the SYNC\_DELAY\_PSI1\_PSI2 bits in ADVSET2 register. In case the sync pulse trigger comes from SPI commands or SYNCx pins, the programmed pulse timer still has the functionality of a filtering time with respect to those triggering commands.

If full flexibility for the sync pulse interval is required, use direct triggering either via SPI or direct interface.

## 3.6 Synchronous pulse generator

The Synchronous Pulse Generator is designed to generate synchronous pulses conform to PSI5 rev. 1.3 (min  $V_{t2}$  = 3.5 V) as well PSI5 rev. 2.x (min  $V_{t2}$  = 2.5 V).

The sync pulse is granted according to PSI5 standard with the I<sub>base</sub> current range up to 35 mA.

If the pulse trigger generation is configured with an external trigger and without the upstream data buffer, the external source must manage the encoding via SPI CHCNT register (for tooth gap and pulse width methods) or via PIN (tooth gap method only), for what concerns the duration of the sync pulse (i.e. ECU to sensor communication), otherwise the IC manages the encoding (tooth gap or pulse width methods, specified in register GCR1, bit PSIx\_TGAP\_PW).

An automatic hardware based slew rate control (SRC) ensures PSI5 compliant slew rates for the rising and falling edge of the sync pulse for an overall capacitive bus load of 15 to 107 nF. The Sync Pulse is shaped like raised cosine instead of trapezoidal to reduce EMC emission.

During the duration of the sync pulse, the corresponding PSI5 receiver is frozen to avoid erroneous data detection.