# DS2745 Low-Cost I<sup>2</sup>C Battery Monitor

#### www.maxim-ic.com

#### **FEATURES**

16-Bit Bidirectional Current Measurement

.56μV LSB, ±51.2mV Dynamic Range

104μA LSB, ±3.4A Dynamic Range (RSNS =

15mΩ)

Current Accumulation Register Resolution

6.25μVhr LSB, ±204.8mVh Range

0.417mAhr LSB, ±13.65Ah Range

(R<sub>SNS</sub> = 15mΩ)

11-Bit Voltage Measurement

88mV LSB, 0V to 4.5V Input Range

11-Bit Temperature Measurement

.125°C Resolution, -20°C to +70°C

Industry Standard I<sup>2</sup>C\* Interface

Low Power Consumption:

Active Current:

70µA typical, 100µA max

70μA typical, 100μA max Sleep Current: 1μA typical, 3μA max

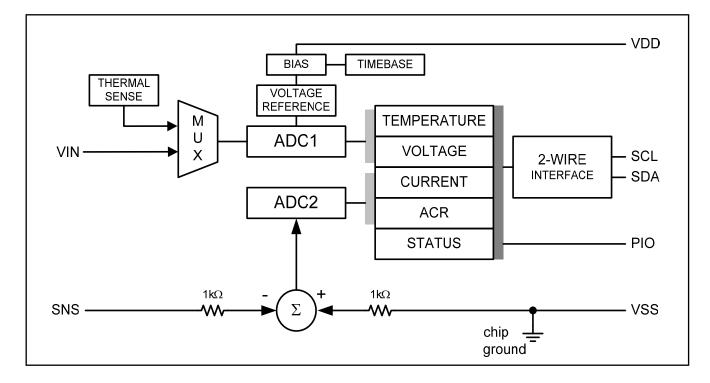

### **BLOCK DIAGRAM**

### **Table 1. ORDERING INFORMATION**

| PART        | MARKING | PIN-PACKAGE               |

|-------------|---------|---------------------------|

| DS2745U+    | 2745    | μMAX package              |

| DS2745U+T&R | 2745    | DS2745U+ in Tape-and-Reel |

+Denotes lead(Pb)-free/RoHS-compliant package.

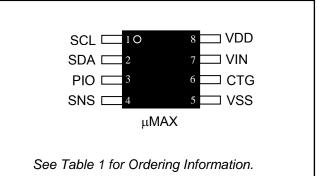

#### **PIN CONFIGURATION**

#### DESCRIPTION

The DS2745 provides current-flow, voltage, and temperature measurement data to support batterycapacity monitoring in cost-sensitive applications. The DS2745 can be mounted on either the host side or pack side of the application. Current measurement and coulomb counting is accomplished by monitoring the voltage drop across an external sense resistor, voltage measurement is accomplished through a separate voltage-sense input, and temperature measurement takes place on-chip. A standard I<sup>2</sup>C interface with software programmable address gives the controlling microprocessor access to all data and status registers inside the DS2745. A low-power sleep mode state conserves energy when the cell pack is in storage.

#### APPLICATIONS

Cellular GPS PDAs Handheld Products

<sup>\*</sup> $^{\ell}C$  is a trademark of Philips Corp. Purchase of  $^{\ell}C$  components from Maxim Integrated Products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips  $^{\ell}C$  Patent Rights to use these components in an  $^{\ell}C$  system, provided that the system conforms to the  $^{\ell}C$  Standard Specification as defined by Philips.

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on All Pins Relative to  $V_{SS}$ Operating Temperature Range Storage Temperature Range Soldering Temperature -0.3V to +6V -40°C to +85°C -55°C to +125°C See IPC/JEDECJ-STD-020A

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS**

$(2.5V \le V_{DD} \le 4.5V; T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER            | SYMBOL          | CONDITIONS | MIN  | TYP MAX              | UNITS |  |  |  |

|----------------------|-----------------|------------|------|----------------------|-------|--|--|--|

| Supply Voltage       | V <sub>DD</sub> | (Note 1)   | +2.5 | +4.5                 | V     |  |  |  |

| Serial Data I/O Pin  | SDA             | (Note 1)   | -0.3 | +5.5                 | V     |  |  |  |

| Serial Clock Pin     | SCL             | (Note 1)   | -0.3 | +5.5                 | V     |  |  |  |

| Programmable I/O Pin | PIO             | (Note 1)   | -0.3 | +5.5                 | V     |  |  |  |

| VIN Pin              | V <sub>IN</sub> | (Note 1)   | -0.3 | V <sub>DD</sub> +0.3 | V     |  |  |  |

### DC ELECTRICAL CHARACTERISTICS

$(2.5V \le V_{DD} \le 4.5V; T_A = 0^{\circ}C$  to +70°C, unless otherwise noted.)

| PARAMETER                         | SYMBOL             | CONDITIONS                                     | MIN   | TYP   | MAX   | UNITS            |

|-----------------------------------|--------------------|------------------------------------------------|-------|-------|-------|------------------|

| Active Current                    |                    |                                                |       | 70    | 100   |                  |

| Active Current                    | ACTIVE             | V <sub>DD</sub> = 4.5V                         |       |       | 105   | μΑ               |

| Sleep-Mode Current                | I <sub>SLEEP</sub> | SCL = SDA = $V_{SS}$ ,<br>PIO = $V_{SS}$       |       | 1     | 3     | μΑ               |

| Current Resolution                | I <sub>LSB</sub>   |                                                |       | 1.56  |       | μV/R             |

| Current Full-Scale<br>Magnitude   | I <sub>FS</sub>    | (Note 1)                                       |       | 51.2  |       | mV/R             |

| Current Offset                    | I <sub>OERR</sub>  | (Note 2)                                       | -7.82 |       | +12.5 | μV/R             |

| Current Gain Error                | I <sub>GERR</sub>  |                                                | -1.0  |       | +1.0  | % of<br>reading  |

| Accumulated Current<br>Resolution | q <sub>CA</sub>    |                                                |       | 6.25  |       | μVh/R            |

| Accumulated Current<br>Offset     | q <sub>oerr</sub>  | $V_{SNS}$ = $V_{SS}$ , (Notes 4, 5)            | -188  |       | +0    | μVh/R<br>per day |

| Voltage Resolution                | V <sub>LSB</sub>   |                                                |       | 4.88  |       | mV               |

| Voltage Full-Scale                | V <sub>FS</sub>    |                                                | 0     |       | 4.992 | V                |

| Voltage Error                     | $V_{\text{GERR}}$  | (Note 12)                                      | -25   |       | +25   | mV               |

| Temperature Resolution            | T <sub>LSB</sub>   |                                                |       | 0.125 |       | °C               |

| Temperature Error                 | T <sub>ERR</sub>   |                                                | -3    |       | +3    | °C               |

| Current Sample Clock<br>Frequency | f <sub>SAMP</sub>  |                                                |       | 18.6  |       | kHz              |

| Timebase Accuracy                 | t <sub>ERR</sub>   | V <sub>DD</sub> = 3.8V, T <sub>A</sub> = +25°C |       |       | ±1    | %                |

|                                    |                    |                                                                                                                                                                 |      |     | ,  |

|------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

|                                    |                    |                                                                                                                                                                 |      | ±2  |    |

|                                    |                    | $\begin{array}{l} -20^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +70^{\circ}\text{C}, \\ 2.5\text{V} \leq \text{V}_{\text{DD}} \leq 4.5\text{V} \end{array}$ |      | ±3  |    |

| Input Resistance, VIN              | R <sub>IN</sub>    |                                                                                                                                                                 | 15   |     | MΩ |

| Input Logic High:<br>SCL, SDA, PIO | V <sub>IH</sub>    | (Note 1)                                                                                                                                                        | 1.5  |     | V  |

| Input Logic Low:<br>SCL, SDA, PIO  | V <sub>IL</sub>    | (Note 1)                                                                                                                                                        |      | 0.6 | V  |

| Output Logic Low:<br>SDA, PIO      | V <sub>OL</sub>    | I <sub>OL</sub> = 4mA (Note 1)                                                                                                                                  |      | 0.4 | V  |

| Pulldown Current: SCL,<br>SDA, PIO | I <sub>PD</sub>    |                                                                                                                                                                 | 0.25 |     | μA |

| Input Capacitance: SCL,<br>SDA     | C <sub>BUS</sub>   |                                                                                                                                                                 |      | 50  | pF |

| SLEEP Timeout                      | t <sub>sleep</sub> | (Note 3)                                                                                                                                                        |      | 2.2 | S  |

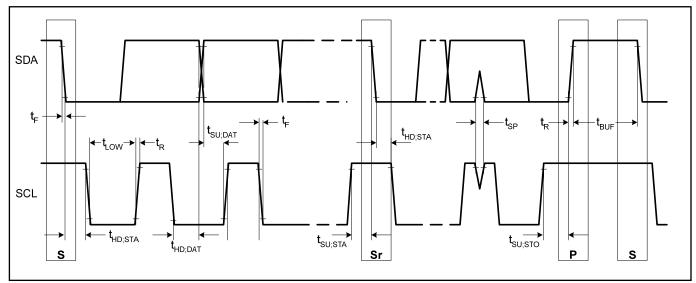

#### 2-WIRE INTERFACE TIMING SPECIFICATIONS ~ /

| PARAMETER                                        | SYMBOL              | CONDITIONS  | MIN TYP                | MAX | UNITS |

|--------------------------------------------------|---------------------|-------------|------------------------|-----|-------|

| SCL Clock Frequency                              | <sup>f</sup> SCL    | (Note 6)    | 0                      | 400 | KHz   |

| Bus Free Time Between a STOP and START Condition | <sup>t</sup> BUF    |             | 1.3                    |     | μs    |

| Hold Time (Repeated)<br>START Condition          | <sup>t</sup> HD:STA | (Note 7)    | 0.6                    |     | μs    |

| Low Period of SCL Clock                          | <sup>t</sup> LOW    |             | 1.3                    |     | μs    |

| High Period of SCL Clock                         | thigh               |             | 0.6                    |     | μs    |

| Setup Time for a Repeated START Condition        | <sup>t</sup> SU:STA |             | 0.6                    |     | μs    |

| Data Hold Time                                   | <sup>t</sup> HD:DAT | (Note 8, 9) | 0                      | 0.9 | μs    |

| Data Setup Time                                  | <sup>t</sup> SU:DAT | (Note 8)    | 100                    |     | ns    |

| Rise Time of Both SDA and SCL Signals            | t <sub>R</sub>      |             | 20 + 0.1C <sub>B</sub> | 300 | ns    |

| Fall Time of Both SDA and SCL Signals            | tF                  |             | 20 + 0.1C <sub>B</sub> | 300 | ns    |

| Setup Time for STOP<br>Condition                 | <sup>t</sup> SU:STO |             | 0.6                    |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input Filter | tSP                 | (Note 10)   | 0                      | 50  | ns    |

| Capacitive Load for Each<br>Bus<br>Line          | CB                  | (Note 11)   |                        | 400 | pF    |

| SCL, SDA Input<br>Capacitance                    | C <sub>BIN</sub>    |             |                        | 60  | pF    |

| Note 1:  | All voltages are referenced to V <sub>SS</sub> .                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------------|

| Note 2:  | Offset specified after auto-calibration cycle and Current Offset Bias register (COBR) set to 00h.                               |

| Note 3:  | To properly enter sleep mode, SMOD=1, and the application should hold SDA and SCL low for longer than the maximum $t_{SLEEP}$ . |

| Note 4:  | NBEN = 0, Current Offset Bias Register (COBR) set to 00h, and Accumulation Bias Register (ABR) set to 00h.                      |

| Note 5:  | Parameters guaranteed by design.                                                                                                |

| Note 6:  | Timing must be fast enough to prevent the DS2745 from entering sleep mode due to SDA,SCL low for period >                       |

|          | t <sub>SLEEP</sub> .                                                                                                            |

| Note 7:  | f <sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.                                                 |

| Note 8:  | The maximum $t_{HD:DAT}$ has only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.      |

| Note 9:  | This device internally provides a hold time of at least 100 ns for the SDA signal (referred to the VIHmin of                    |

|          | the SCL signal) to bridge the undefined region of the falling edge of SCL.                                                      |

| Note 10: | Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.                               |

| Note 11: | Ce—total capacitance of one bus line in pE.                                                                                     |

Note 11:C<sub>B</sub>—total capacitance of one bus line in pF.Note 12:The first voltage measurement after writing the ACR or after device POR is not valid.

# Figure 1. I<sup>2</sup>C Bus Timing Diagram

### **PIN DESCRIPTION**

| PIN | SYMBOL          | FUNCTION                                                                                                                                                                                                           |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCL             | <b>Serial Clock Input.</b> 2-Wire clock line. Input only. Connect this pin to the CLOCK terminal of the battery pack. Pin has an internal pulldown (I <sub>PD</sub> ) for sensing disconnection.                   |

| 2   | SDA             | <b>Serial Data Input/Output.</b> 2-Wire data line. Open-drain output driver. Connect this pin to the DATA terminal of the battery pack. Pin has an internal pulldown (I <sub>PD</sub> ) for sensing disconnection. |

| 3   | PIO             | <b>General Purpose Input/Output.</b> Open-drain output driver with input sense. Connect to a pull up resistor for bidirectional operation.                                                                         |

| 4   | SNS             | Sense Resistor Connection. Connect to the negative terminal of the battery pack. Connect the sense resistor between $V_{SS}$ and SNS.                                                                              |

| 5   | V <sub>SS</sub> | <b>Device Ground.</b> Connect to the negative terminal of the Li+ cell outside the cell protection FETs. Connect the sense resistor between $V_{SS}$ and SNS.                                                      |

| 6   | CTG             | <b>Connect to Ground.</b> Connect to the negative terminal of the Li+ cell outside the cell protection FETs.                                                                                                       |

| 7   | VIN             | Voltage Sense Input. The voltage of the Li+ cell is monitored through this input pin.                                                                                                                              |

| 8   | V <sub>DD</sub> | <b>Power-Supply Input.</b> Connect to the positive terminal of the Li+ cell through a decoupling network.                                                                                                          |

# Figure 2. BLOCK DIAGRAM

### DETAILED DESCRIPTION

Current is measured bidirectionally over a dynamic range of  $\pm 51.2$ mV with a resolution of  $1.56\mu$ V. Assuming a  $15m\Omega$  sense resistor, the current sense range is  $\pm 3.4$ A, with a 1 LSB resolution of  $104\mu$ A. Current measurements are performed at regular intervals and accumulated with each measurement to support accurate "coulomb counting". Each current measurement is reported with sign and magnitude in the two-byte Current register. The Accumulated Current register (ACR) reports the coulomb count and supports a wide range of battery sizes. Battery voltage measurements are reported in the two-byte Voltage register with 11-bit (4.88mV) resolution, and Temperature is reported in the two-byte Temperature register with 0.125C resolution.

The DS2745 measurements can be used directly to provide accurate fuel gauging in typical use conditions, or along with FuelPack<sup>™</sup> algorithms to form a complete and accurate solution for estimating remaining capacity over wide temperature and operating conditions.

Through its two wire  $I^2C$  interface, the DS2745 allows a host system read/write access to the Status, Configuration and Measurement registers. Additionally, the  $I^2C$  slave address can be changed from the default after power up.

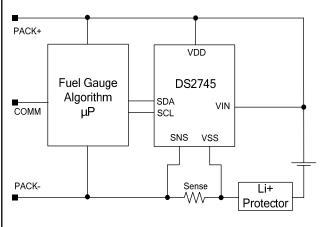

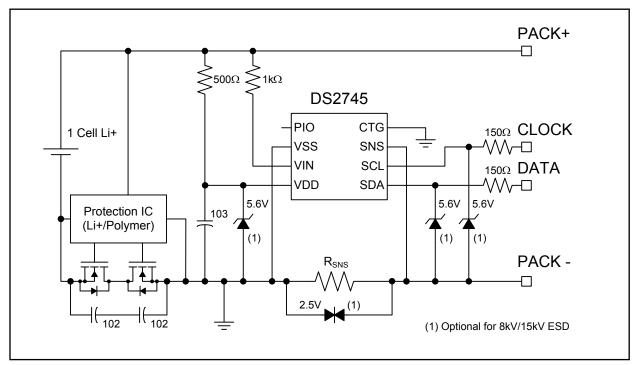

# Figure 3. APPLICATION EXAMPLE

FuelPack is a trademark of Maxim Integrated Products, Inc.

### POWER MODES

The DS2745 operates in one of two power modes: active and sleep. While in active mode, the DS2745 operates as a high-precision battery monitor with voltage, temperature, current and accumulated current measurements acquired continuously and the resulting values updated in the measurement registers. Read and write access is allowed to all registers.

In sleep mode, the DS2745 operates in a low-power mode with no measurement activity. Serial access to current, accumulated current, and status/control registers is allowed in sleep mode if  $V_{DD} > 2V$ .

The DS2745 operating mode transitions from SLEEP to ACTIVE when:

$SDA > V_{IH}$  OR  $SCL > V_{IH}$

The DS2745 operating mode transitions from ACTIVE to SLEEP when:

SMOD = 1 AND (SDA < VIL AND SCL < VIL) for  $t_{SLEEP}$ .

**CAUTION**: If SMOD = 1, pull-up resistors are required on SCL and/or SDA in order to ensure that the DS2745 transitions from SLEEP to ACTIVE mode when the battery is charged. If the bus is not pulled up, the DS2745 remains in SLEEP and cannot accumulate the charge current. This caution statement applies particularly to on a battery that is charged on a standalone charger.

#### VOLTAGE MEASUREMENT

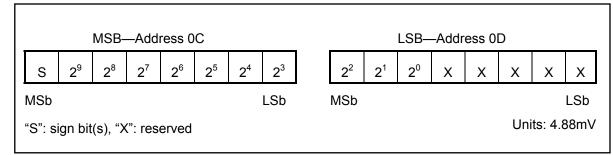

Battery voltage is measured at the VIN input with respect to VSS over a range of 0 to 4.992V (VIN pin is limited to VDD voltage) and with a resolution of 4.88mV. The result is updated every 440ms and placed in the VOLTAGE register in two's compliment form. Voltages above the maximum register value are reported as 7FFFh.

### Figure 4. VOLTAGE REGISTER FORMAT

The input impedance of VIN is sufficiently large (>15M $\Omega$ ) to be connected to a high impedance voltage divider in order to support multiple cell applications. The pack voltage should be divided by the number of series cells to present a single cell average voltage to the VIN input. Note that the first voltage measurement made after the DS2745 is powered or after the ACR register is written will not be valid. The host should wait one measurement cycle after either of these two conditions occur before reading voltage.

### **TEMPERATURE MEASUREMENT**

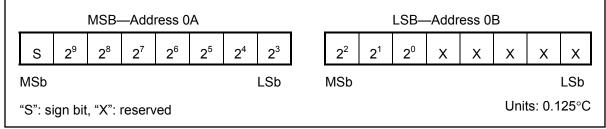

The DS2745 uses an integrated temperature sensor to measure battery temperature with a resolution of 0.125°C. Temperature measurements are updated every 440ms and placed in the Temperature Register in two's complement form.

### Figure 5. TEMPERATURE REGISTER FORMAT

### **CURRENT MEASUREMENT**

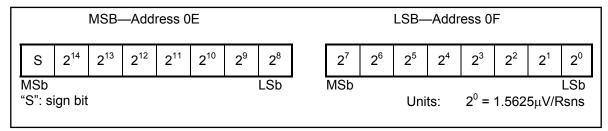

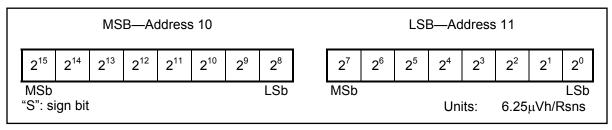

In the active mode of operation, the DS2745 continually measures the current flow into and out of the battery by measuring the voltage drop across a low-value current-sense resistor,  $R_{SNS}$ , connected between the SNS and VSS pins. The voltage sense range between SNS and VSS is ±51.2mV. Note that positive current values occur when  $V_{SNS}$  is less than  $V_{SS}$ , and negative current values occur when  $V_{SNS}$  is greater than  $V_{SS}$ . Peak signal amplitudes up to 102mV are allowed at the input as long as the continuous or average signal level does not exceed ±51.2mV over the conversion cycle period. The ADC samples the input differentially at with an 18.6kHz sample clock and updates the current register at the completion of each conversion cycle. Figure 6 describes the current measurement register format and resolution. Charge currents above the maximum register value are reported at the minimum value (7FFFh = +51.2mV).

# Figure 6. CURRENT REGISTER FORMATS

### Table 2. CURRENT RESOLUTION FOR VARIOUS RSNS VALUES

|                    | CURRENT RESOLUTION (1 LSB)         |                  |              |                     |             |  |

|--------------------|------------------------------------|------------------|--------------|---------------------|-------------|--|

| CONVERSION<br>TIME | V <sub>SS</sub> - V <sub>SNS</sub> | R <sub>SNS</sub> |              |                     |             |  |

|                    | 1 55 V 5N51                        | 20mΩ             | $15 m\Omega$ | $10 \text{m}\Omega$ | $5 m\Omega$ |  |

| 3.5s               | 1.5625μV                           | 78.13μA          | 104.2μA      | 156.3μA             | 312.5μA     |  |

### Table 3. CURRENT RANGE FOR VARIOUS RSNS VALUES

| CURRENT INPUT RANGE                |                  |        |        |             |  |  |  |

|------------------------------------|------------------|--------|--------|-------------|--|--|--|

| V <sub>SS</sub> - V <sub>SNS</sub> | R <sub>SNS</sub> |        |        |             |  |  |  |

| • 55 • 5N5                         | 20mΩ             | 15mΩ   | 10mΩ   | $5 m\Omega$ |  |  |  |

| ±51.2mV                            | ±2.56A           | ±3.41A | ±5.12A | ±10.24A     |  |  |  |

Every 1024th conversion, the ADC measures its input offset to facilitate offset correction. Offset correction occurs approximately once per hour. The resulting correction factor is applied to the subsequent 1023 measurements. During the offset correction conversion, the ADC does not measure the SNS to VSS signal. A maximum error of 1/1024 in the accumulated current register (ACR) is possible, however, to reduce the error, the current measurement just prior to the offset conversion is displayed in the current register and is substituted for the dropped current measurement in the current accumulation process. The error due to offset correction is typically much less than 1/1024.

### CURRENT ACCUMULATION

The Accumulated Current register (ACR) serves as an up/down counter holding a running count of charge stored in the battery. Current measurement results, plus a programmable bias value are internally summed, or accumulated, at the completion of each current measurement conversion period with the results displayed in the ACR. The ACR has a range of 0mVh to +409.6mVh with an LSb of  $6.25\mu$ VfAdditional registers hold fractional results of each accumulation, however, these bits are not user accessible. The ACR count clamps at FFFFh when accumulating charge values and at 0000h when accumulating discharge values.

Read and write access is allowed to the ACR. Whenever the ACR is written, fractional accumulation results are cleared. A write to the ACR also forces the ADC to measure its offset and update the offset correction factor. Current measurement and accumulation resume (using the new offset correction) with the second conversion following the write to the ACR. Figure 7 describes the ACR address, format, and resolution.

# Figure 7. ACCUMULATED CURRENT REGISTER FORMAT

### Table 4. ACCUMULATED CURRENT RANGE FOR VARIOUS RSNS VALUES

| ACR RANGE            |         |         |         |             |  |  |

|----------------------|---------|---------|---------|-------------|--|--|

| $V_{SS}$ - $V_{SNS}$ |         | R       | SNS     |             |  |  |

|                      | 20mµ    | 15mµ    | 10mΩ    | $5 m\Omega$ |  |  |

| 409.6mVh             | 20.48Ah | 27.31Ah | 40.96Ah | 81.92Ah     |  |  |

#### **CURRENT OFFSET BIAS**

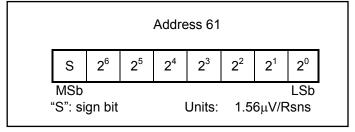

The Current Offset Bias register (COBR) allows a programmable offset value to be added to raw current measurements. The result of the raw current measurement plus the COBR value is displayed as the current measurement result in the CURRENT register, and is used for current accumulation. The COBR value can be used to correct for a static offset error, or can be used to intentionally skew the current results and therefore the current accumulation.

Read and write access is allowed to COBR. Whenever the COBR is written, the new value is applied to all subsequent current measurements. COBR can be programmed in  $1.56\mu$ V steps to any value between  $+198.1\mu$ V and  $-199.7\mu$ V. The COBR value is stored as a two's complement value in volatile memory, and must be initialized via the interface on power-up. Figure 8 describes the COBR address, format, and resolution.

# Figure 8. CURRENT OFFSET BIAS REGISTER FORMAT

#### CURRENT BLANKING

The Current Blanking feature modifies current measurement result prior to being accumulated in the ACR. Current Blanking occurs conditionally when a current measurement (raw current + COBR) falls in one of two defined ranges. The first range prevents charge currents less than  $100\mu$ V from being accumulated. The second range prevents discharge currents less than  $25\mu$ V in magnitude from being accumulated. Charge current blanking is always performed, however, discharge current blanking must be enabled by setting the NBEN bit in the Status/Config register. See the register description for additional information.

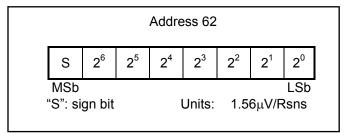

### **ACCUMULATION BIAS**

The Accumulation Bias register (ABR) allows a programmable offset value to be added to the current accumulation process. The new ACR value results from the addition of the Current register value plus ABR plus the previous ACR value. ABR can be used to intentionally skew the current accumulation to estimate system stand-by currents that are too small to measure. ABR value is not subject to the Current Blanking thresholds.

Read and write access is allowed to the ABR. Whenever the ABR is written, the new value is applied to all subsequent current measurements. ABR can be set to any value between +198.1 $\mu$ V and -199.7 $\mu$ V in 1.56 $\mu$ V steps. The ABR value is stored as a two's complement value in volatile memory, and must be initialized via the interface on power-up. Figure 9 describes the ABR address, format, and resolution.

# Figure 9. ACCUMULATION BIAS REGISTER FORMAT

### MEMORY

The DS2745 has memory space with registers for instrumentation, status, and control. When the MSB of a twobyte register is read, both the MSB and LSB are latched and held for the duration of the read data command to prevent updates during the read and ensure synchronization between the two register bytes. For consistent results, always read the MSB and the LSB of a two-byte register during the same read data command sequence.

| Table 5. MEMOR | ΥΜΑΡ                             |                   |             |

|----------------|----------------------------------|-------------------|-------------|

| ADDRESS (HEX)  | DESCRIPTION                      | <b>READ/WRITE</b> | POR DEFAULT |

| 00             | Reserved                         | —                 |             |

| 01             | Status/Config Register           | R/W               | 1100000b    |

| 02 to 08       | Reserved                         | —                 |             |

| 09 to 0D       | Reserved                         | —                 |             |

| 0A             | Temperature Register MSB         | R                 |             |

| 0B             | Temperature Register LSB         | R                 |             |

| 0C             | Voltage Register MSB             | R                 |             |

| 0D             | Voltage Register LSB             | R                 |             |

| 0E             | Current Register MSB             | R                 |             |

| 0F             | Current Register LSB             | R                 |             |

| 10             | Accumulated Current Register MSB | R/W               | No Change   |

| 11             | Accumulated Current Register LSB | R/W               | No Change   |

| 12 to 61       | Reserved                         | —                 |             |

| 61             | Offset Bias Register             | R/W               | 00h         |

| 62             | Accumulation Bias Register       | R/W               | 00h         |

| 63 to FF       | Reserved                         |                   |             |

### STATUS/CONFIG REGISTER

The Status/Config register is read/write with individual bits designated as read only. Bit values indicate status as well as program or select device functionality.

### Figure 10. STATUS/CONFIG REGISTER FORMAT

| ADDRESS 01 |       |       |       |       |       |       |       |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|

| BIT 7      | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

| Х          | PORF  | SMOD  | NBEN  | PIO   | A2    | A1    | A0    |  |

X — Reserved.

**PORF** — The Power-On-Reset Flag is set to indicate initial power-up. PORF is not cleared internally. The user must write this flag value to a 0 in order to use it to indicate subsequent power-up events. If PORF indicates a power-on-reset, the ACR could be misaligned with the actual battery state of charge. The system can request a charge to full in order to synchronize the ACR with the battery charge state. PORF is read/write-to-zero.

**SMOD** — SLEEP Mode Enable. A value of 1 allows the DS2745 to enter sleep mode when both SDA and SCL pins is low for 2s. A value of 0 disables the transition to sleep mode. The power-up default of SMOD = 0.

**NBEN** — Negative Blanking Enable. A value of 1 enables blanking of negative current values up to  $25\mu$ V. A value of 0 disables blanking of negative currents. The power-up default of NBEN = 0.

**PIO** — Programmable Input/Output. PIO provides both control of the PIO open-drain output driver and readback of the PIO pin logic level. Writing a 0 to PIO drives PIO pin low. Writing a 1 deactivates the PIO output and allows readback of an external signal. Reading PIO returns the logic state on the pin. PIO is RESET on POR.

**A2:A0** —  $I^2C$  Slave Address bits. A2:A0 set the lower 3 bits of the  $I^2C$  slave address. When modified from the power-up default slave address of **1001000b**, accessing the DS2745 requires the modified slave address following a start or repeated start.

### 2-WIRE BUS SYSTEM

The 2-Wire bus system supports operation as a slave only device in a single or multi-slave, and single or multimaster system. Up to 128 slave devices may share the bus by uniquely setting the 7-bit slave address. The 2-wire interface consists of a serial data line (SDA) and serial clock line (SCL). SDA and SCL provide bidirectional communication between the DS2745 slave device and a master device at speeds up to 400kHz. The DS2745's SDA pin operates bidirectionally, that is, when the DS2745 receives data, SDA operates as an input, and when the DS2745 returns data, SDA operates as an open-drain output, with the host system providing a resistive pull-up. The DS2745 always operates as a slave device, receiving and transmitting data under the control of a master device. The master initiates all transactions on the bus and generates the SCL signal as well as the START and STOP bits which begin and end each transaction.

#### Bit Transfer

One data bit is transferred during each SCL clock cycle, with the cycle defined by SCL transitioning low-to-high and then high-to-low. The SDA logic level must remain stable during the high period of the SCL clock pulse. Any change in SDA when SCL is high is interpreted as a START or STOP control signal.

#### Bus Idle

The bus is defined to be idle, or not busy, when no master device has control. Both SDA and SCL remain high when the bus is idle. The STOP condition is the proper method to return the bus to the idle state.

#### **START and STOP Conditions**

The master initiates transactions with a START condition (S), by forcing a high-to-low transition on SDA while SCL is high. The master terminates a transaction with a STOP condition (P), a low-to-high transition on SDA while SCL is high. A Repeated START condition (Sr) can be used in place of a STOP then START sequence to terminate one transaction and begin another without returning the bus to the idle state. In multimaster systems, a Repeated START allows the master to retain control of the bus. The START and STOP conditions are the only bus activities in which the SDA transitions when SCL is high.

#### Acknowledge Bits

Each byte of a data transfer is acknowledged with an Acknowledge bit (A) or a No Acknowledge bit (N). Both the master and the DS2745 slave generate acknowledge bits. To generate an Acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low until SCL returns low. To generate a No Acknowledge (also called NAK), the receiver releases SDA before the rising edge of the acknowledge SDA high until SCL returns low. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer can occur if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication.

#### Data Order

A byte of data consists of 8 bits ordered most significant bit (msb) first. The least significant bit (lsb) of each byte is followed by the Acknowledge bit. DS2745 registers composed of multi-byte values are ordered most significant byte (MSB) first. The MSB of multi-byte registers is stored on even data memory addresses.

#### Slave Address

A bus master initiates communication with a slave device by issuing a START condition followed by a Slave Address (SAddr) and the read/write (R/W) bit. When the bus is idle, the DS2745 continuously monitors for a START condition followed by its slave address. When the DS2745 receives a slave address that matches the value in its Status/Config register, it responds with an Acknowledge bit during the clock period following the R/W bit. The default Slave Address at power-up is 1001000. The lower three bits of the slave address can be re-programmed, refer to the Status/Config register description for details.

#### **Read/Write Bit**

The R/W bit following the slave address determines the data direction of subsequent bytes in the transfer. R/W = 0 selects a write transaction, with the following bytes being written by the master to the slave. R/W = 1 selects a read transaction, with the following bytes being read from the stave by the master.

#### **Bus Timing**

The DS2745 is compatible with any bus timing up to 400kHz. No special configuration is required to operate at any speed.

#### 2-Wire Command Protocols

The command protocols involve several transaction formats. The simplest format consists of the master writing the START bit, slave address, R/W bit, and then monitoring the acknowledge bit for presence of the DS2745. More complex formats such as the Write Data, Read Data and Function command protocols write data, read data and execute device specific operations. All bytes in each command format require the slave or host to return an Acknowledge bit before continuing with the next byte. Each function command definition outlines the required transaction format. The following key applies to the transaction formats.

#### Table 3. 2-Wire Protocol Key

| KEY   | DESCRIPTION                 | KEY  | DESCRIPTION                 |

|-------|-----------------------------|------|-----------------------------|

| S     | START bit                   | Sr   | Repeated START              |

| SAddr | Slave Address (7-bit)       | W    | R/W bit = 0                 |

| FCmd  | Function Command byte       | R    | R/W bit = 1                 |

| MAddr | Memory Address byte         | Р    | STOP bit                    |

| Data  | Data byte written by master | Data | Data byte returned by slave |

| А     | Acknowledge bit - Master    | A    | Acknowledge bit—Slave       |

| Ν     | No Acknowledge - Master     | Ν    | No Acknowledge—Slave        |

#### **Basic Transaction Formats**

Write: S SAddr W A MAddr A Data0 A P

A write transaction transfers one or more data bytes *to* the DS2745. The data transfer begins at the memory address supplied in the MAddr byte. Control of the SDA signal is retained by the master throughout the transaction, except for the Acknowledge cycles.

Read: S SAddr W A MAddr A Sr SAddr R A Data0 N P

Write Portion

Read Portion

A read transaction transfers one or more bytes *from* the DS2745. Read transactions are composed of two parts, a write portion followed by a read portion, and is therefore inherently longer than a write transaction. The write portion communicates the starting point for the read operation. The read portion follows immediately, beginning with a Repeated START, Slave Address with R/W set to a 1. Control of SDA is assumed by the DS2745 beginning with the Slave Address Acknowledge cycle. Control of the SDA signal is retained by the DS2745 throughout the transaction, except for the Acknowledge cycles. The master indicates the end of a read transaction by responding to the last byte it requires with a No Acknowledge. This signals the DS2745 that control of SDA is to remain with the master following the Acknowledge clock.

#### Write Data Protocol

The write data protocol is used to write to register and shadow RAM data to the DS2745 starting at memory address MAddr. Data0 represents the data written to MAddr, Data1 represents the data written to MAddr + 1 and DataN represents the last data byte, written to MAddr + N. The master indicates the end of a write transaction by sending a STOP or Repeated START after receiving the last acknowledge bit.

S SAddr W A MAddr A Data0 A Data1 A ... DataN A P

The msb of the data to be stored at address MAddr can be written immediately after the MAddr byte is acknowledged. Because the address is automatically incremented after the least significant bit (lsb) of each byte is received by the DS2745, the msb of the data at address MAddr + 1 is can be written immediately after the acknowledgement of the data at address MAddr. If the bus master continues an auto-incremented write transaction beyond address FFh, the DS2745 ignores the data. Data is also ignored on writes to read-only addresses and reserved addresses. Incomplete bytes and bytes that are Not Acknowledged by the DS2745 are not written to memory.

#### **Read Data Protocol**

The Read Data protocol is used to read register and shadow RAM data from the DS2745 starting at memory address specified by MAddr. Data0 represents the data byte in memory location MAddr, Data1 represents the data from MAddr + 1 and DataN represents the last byte read by the master.

S SAddr W A MAddr A Sr SAddr R A Data0 A Data1 A ... DataN N P

Data is returned beginning with the most significant bit (msb) of the data in MAddr. Because the address is automatically incremented after the least significant bit (lsb) of each byte is returned, the msb of the data at address MAddr + 1 is available to the host immediately after the acknowledgement of the data at address MAddr. If the bus master continues to read beyond address FFh, the DS2745 outputs data values of FFh. Addresses labeled "Reserved" in the memory map return undefined data. The bus master terminates the read transaction at any byte boundary by issuing a No Acknowledge followed by a STOP or Repeated START.

#### **PACKAGE INFORMATION**

For the latest package outline information, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 µMAX       | U8+1         | <u>21-0036</u> |

### **REVISION HISTORY**

| REVISION<br>DATE | DESCRIPTION                                                                                          | PAGES<br>CHANGED |

|------------------|------------------------------------------------------------------------------------------------------|------------------|

| 51209            | Changed the $V_{DD}$ maximum operating range in the <i>Electrical Characteristics</i> table to 4.5V. | 2, 3             |

|                  | Added " $V_{IN}$ pin is limited to $V_{DD}$ voltage" text in the Voltage Measurement section.        | 7                |

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2009 Maxim Integrated Products

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.

15 of 15