# CY2305C CY2309C

# 3.3 V Zero Delay Clock Buffer

#### Features

- 10 MHz to 100–133 MHz operating range

- Zero input and output propagation delay

- Multiple low skew outputs

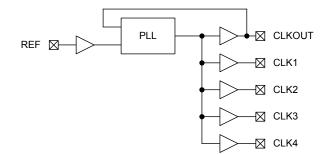

- One input drives five outputs (CY2305C)

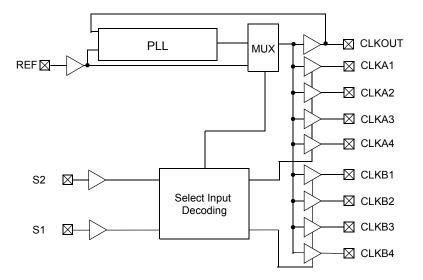

- One input drives nine outputs, grouped as 4 + 4 + 1 (CY2309C)

- 50 ps typical cycle-to-cycle jitter (15 pF, 66 MHz)

- Test mode to bypass phase locked loop (PLL) (CY2309C) only, see Select Input Decoding for CY2309C on page 5

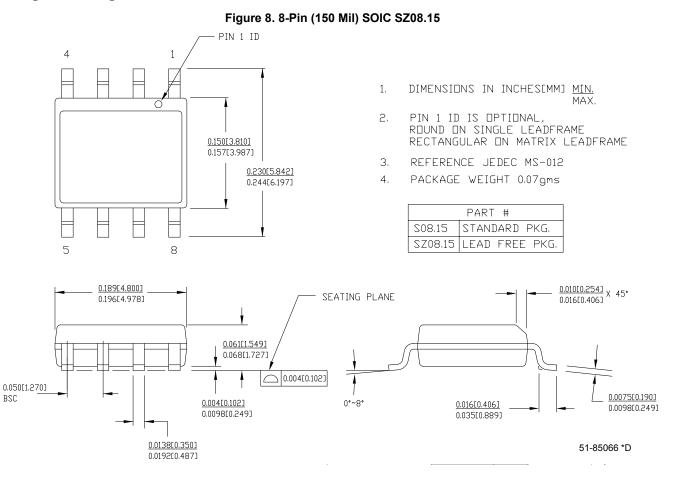

- Available in space saving 16-pin 150 Mil small outline integrated circuit (SOIC) or 4.4 mm thin shrunk small outline package (TSSOP) packages (CY2309C), and 8-pin, 150 Mil SOIC package (CY2305C)

- 3.3 V operation

- Commercial, industrial and automotive-A flows available

#### **Functional Description**

The CY2305C and CY2309C are die replacement parts for CY2305 and CY2309.

The CY2309C is a low-cost 3.3 V zero delay buffer designed to distribute high speed clocks and is available in a 16-pin SOIC or TSSOP package. The CY2305C is an 8-pin version of the CY2309C. It accepts one reference input and drives out five low skew clocks. The -1H versions of each device operate up to

Logic Block Diagram for CY2305C

100–133 MHz frequencies and have higher drive than the -1 devices. All parts have on-chip phase locked loops (PLLs) which lock to an input clock on the REF pin. The PLL feedback is on-chip and is obtained from the CLKOUT pad.

The CY2309C has two banks of four outputs each that are controlled by the select inputs as shown in the Select Input Decoding for CY2309C on page 5. If all output clocks are not required, Bank B is three-stated. The input clock is directly applied to the outputs by the select inputs for chip and system testing purposes.

The CY2305C and CY2309C PLLs enter a power down mode when there are no rising edges on the REF input. In this state, the outputs are three-stated and the PLL is turned off. This results in less than 12.0  $\mu$ A of current draw for commercial temperature devices and 25.0  $\mu$ A for industrial and automotive-A temperature parts. The CY2309C PLL shuts down in one additional case as shown in the Select Input Decoding for CY2309C on page 5.

In the special case when S2:S1 is 1:0, the PLL is bypassed and REF is output from DC to the maximum allowable frequency. The part behaves as a non-zero delay buffer in this mode and the outputs are not three-stated.

The CY2305C or CY2309C is available in two or three different configurations as shown in the Ordering Information on page 11. The CY2305C-1 or CY2309C-1 is the base part. The CY2305-1H or CY2309-1H is the high drive version of the -1. Its rise and fall times are much faster than the -1.

San Jose, CA 95134-1709 • 408-943-2600 Revised February 3, 2011

# Logic Block Diagram for CY2309C

### Contents

| Pinouts                                            | 4 |

|----------------------------------------------------|---|

| Zero Delay and Skew Control                        | 5 |

| Absolute Maximum Conditions                        | 6 |

| Operating Conditions for CY2305CSXC-XX and         |   |

| CY2309CSXC-XX                                      | 6 |

| Operating Conditions for CY2305CSXI-XX,            |   |

| CY2305CSXA-XX and CY2309CSXI-XX                    | 6 |

| Electrical Characteristics for CY2305CSXC-XX and   |   |

| CY2309CSXC-XX                                      | 6 |

| Switching Characteristics for CY2305CSXC-XX and    |   |

| CY2309CSXC-XX                                      | 7 |

| Switching Characteristics for CY2305CSXI-XX,       |   |

| CY2305CSXA-XX and CY2309CSXI-XX                    | 8 |

| Switching characteristics table for CY2305CSXI-1H, |   |

| CY2305CSXA-1H and CY2309CSXI-1H         | 9  |

|-----------------------------------------|----|

| Switching Waveforms                     | 9  |

| Test Circuits                           | 10 |

| Ordering Information                    | 11 |

| Ordering Code Definition                | 12 |

| Package Drawing and Dimensions          | 13 |

| Acronyms                                | 15 |

| Document Conventions                    | 15 |

| Units of Measure                        |    |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 17 |

| Worldwide Sales and Design Support      |    |

| Products                                | 17 |

| PSoC Solutions                          | 17 |

### Pinouts

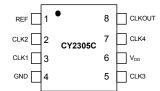

CY2305C

#### Figure 1. Pin Diagram - 8 Pin SOIC (Top View)

#### Table 1. Pin Description - 8 Pin SOIC

| Pin | Signal                | Description                                          |

|-----|-----------------------|------------------------------------------------------|

| 1   | REF <sup>[1]</sup>    | Input reference frequency                            |

| 2   | CLK2 <sup>[2]</sup>   | Buffered clock output                                |

| 3   | CLK1 <sup>[2]</sup>   | Buffered clock output                                |

| 4   | GND                   | Ground                                               |

| 5   | CLK3 <sup>[2]</sup>   | Buffered clock output                                |

| 6   | V <sub>DD</sub>       | 3.3 V supply                                         |

| 7   | CLK4 <sup>[2]</sup>   | Buffered clock output                                |

| 8   | CLKOUT <sup>[2]</sup> | Buffered clock output, internal feedback on this pin |

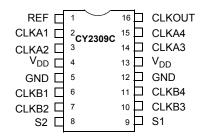

#### CY2309C

#### Figure 2. Pin Diagram - 16 Pin SOIC/TSSOP (Top View)

#### Table 2. Pin Definition - 16 Pin SOIC/TSSOP

| Pin | Signal               | Description                   |

|-----|----------------------|-------------------------------|

| 1   | REF <sup>[1]</sup>   | Input reference frequency     |

| 2   | CLKA1 <sup>[2]</sup> | Buffered clock output, Bank A |

| 3   | CLKA2 <sup>[2]</sup> | Buffered clock output, Bank A |

| 4   | V <sub>DD</sub>      | 3.3 V supply                  |

| 5   | GND                  | Ground                        |

| 6   | CLKB1 <sup>[2]</sup> | Buffered clock output, Bank B |

| 7   | CLKB2 <sup>[2]</sup> | Buffered clock output, Bank B |

| 8   | S2 <sup>[3]</sup>    | Select input, bit 2           |

Notes

1. Weak pull down.

2. Weak pull down on all outputs.

3. Weak pull ups on these inputs

| Pin | Signal                | Description                                    |

|-----|-----------------------|------------------------------------------------|

| 9   | S1 <sup>[4]</sup>     | Select input, bit 1                            |

| 10  | CLKB3 <sup>[5]</sup>  | Buffered clock output, Bank B                  |

| 11  | CLKB4 <sup>[5]</sup>  | Buffered clock output, Bank B                  |

| 12  | GND                   | Ground                                         |

| 13  | V <sub>DD</sub>       | 3.3 V supply                                   |

| 14  | CLKA3 <sup>[5]</sup>  | Buffered clock output, Bank A                  |

| 15  | CLKA4 <sup>[5]</sup>  | Buffered clock output, Bank A                  |

| 16  | CLKOUT <sup>[5]</sup> | Buffered output, internal feedback on this pin |

#### Table 2. Pin Definition - 16 Pin SOIC/TSSOP (continued)

#### Table 3. Select Input Decoding for CY2309C

| S2 | S1 | CLOCK A1-A4 | CLOCK B1–B4 | CLKOUT <sup>[6]</sup> | Output Source | PLL Shutdown |

|----|----|-------------|-------------|-----------------------|---------------|--------------|

| 0  | 0  | Three state | Three state | Driven                | PLL           | N            |

| 0  | 1  | Driven      | Three state | Driven                | PLL           | N            |

| 1  | 0  | Driven      | Driven      | Driven                | Reference     | Y            |

| 1  | 1  | Driven      | Driven      | Driven                | PLL           | N            |

### Zero Delay and Skew Control

All outputs must be uniformly loaded to achieve Zero Delay between the input and output. Since the CLKOUT pin is the internal feedback to the PLL, its relative loading can adjust the input or output delay.

For applications requiring zero input or output delay, all outputs including CLKOUT are equally loaded. Even if CLKOUT is not used, it must have a capacitive load equal to that on other outputs for obtaining zero input or output delay.

For zero output to output skew, all outputs must be loaded equally.

Notes

4. Weak pull ups on these inputs.

5

Weak pull down on all outputs. This output is driven and has an internal feedback for the PLL. The load on this output is adjusted to change the skew between the reference and output. 6.

### **Absolute Maximum Conditions**

| Supply voltage to ground potential–0.5 V to +4.6 V     |

|--------------------------------------------------------|

| DC input voltage (Except REF)0.5 V to V_{DD} + 0.5 V   |

| DC input voltage REF –0.5 V to $V_{\text{DD}}$ + 0.5 V |

| Storage temperature            | –65 °C to +150 °C |

|--------------------------------|-------------------|

| Junction temperature           | 150 °C            |

| Static discharge voltage       |                   |

| (per MIL-STD-883, Method 3015) | > 2,000 V         |

### Operating Conditions for CY2305CSXC-XX and CY2309CSXC-XX

Operating conditions table for CY2305CSXC-XX and CY2309CSXC-XX commercial temperature devices.

| Parameter       | Description                                                                                            | Min  | Max | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>DD</sub> | Supply voltage                                                                                         | 3.0  | 3.6 | V    |

| T <sub>A</sub>  | Operating temperature (ambient temperature)                                                            | 0    | 70  | °C   |

| CL              | Load capacitance, below 100 MHz                                                                        |      | 30  | pF   |

| CL              | Load capacitance, from 100 MHz to 133 MHz                                                              |      | 10  | pF   |

| C <sub>IN</sub> | Input capacitance                                                                                      |      | 7   | pF   |

| t <sub>PU</sub> | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps are monotonic) | 0.05 | 50  | ms   |

# Operating Conditions for CY2305CSXI-XX, CY2305CSXA-XX and CY2309CSXI-XX

Operating conditions table for CY2305CSXI-XX, CY2305CSXA-XX and CY2309CSXI-XX industrial/automotive-A temperature devices.

| Parameter       | Description                                                                                            | Min  | Max | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>DD</sub> | Supply voltage                                                                                         | 3.0  | 3.6 | V    |

| T <sub>A</sub>  | Operating temperature (ambient temperature)                                                            | -40  | 85  | °C   |

| CL              | Load capacitance, below 100 MHz                                                                        | -    | 30  | pF   |

| CL              | Load capacitance, from 100 MHz to 133 MHz                                                              | -    | 10  | pF   |

| C <sub>IN</sub> | Input capacitance                                                                                      | -    | 7   | pF   |

| t <sub>PU</sub> | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps are monotonic) | 0.05 | 50  | ms   |

### Electrical Characteristics for CY2305CSXC-XX and CY2309CSXC-XX

Electrical characteristics table for CY2305CSXC-XX and CY2309CSXC-XX commercial temperature devices.

| Parameter                 | Description                        | Test Conditions                                                | Min | Max | Unit |

|---------------------------|------------------------------------|----------------------------------------------------------------|-----|-----|------|

| V <sub>IL</sub>           | Input LOW voltage <sup>[7]</sup>   |                                                                | -   | 0.8 | V    |

| V <sub>IH</sub>           | Input HIGH voltage <sup>[7]</sup>  |                                                                | 2.0 | -   | V    |

| I <sub>IL</sub>           | Input LOW current                  | V <sub>IN</sub> = 0 V                                          | -   | 50  | μA   |

| I <sub>IH</sub>           | Input HIGH current                 | V <sub>IN</sub> = V <sub>DD</sub>                              | -   | 100 | μA   |

| V <sub>OL</sub>           | Output LOW voltage <sup>[8]</sup>  | I <sub>OL</sub> = 8 mA (–1)<br>I <sub>OH =</sub> 12 mA (–1H)   | _   | 0.4 | V    |

| V <sub>OH</sub>           | Output HIGH voltage <sup>[8]</sup> | I <sub>OH</sub> = -8 mA (-1)<br>I <sub>OL</sub> = -12 mA (-1H) | 2.4 | _   | V    |

| I <sub>DD</sub> (PD mode) | Power-down supply current          | REF = 0 MHz                                                    | -   | 12  | μA   |

| I <sub>DD</sub>           | Supply current                     | Unloaded outputs at 66.67 MHz, SEL inputs at $V_{DD}$          | -   | 32  | mA   |

#### Notes

7. REF input has a threshold voltage of V<sub>DD</sub>/2.

8. Parameter is guaranteed by design and characterization. Not 100% tested in production.

Document Number: 38-07672 Rev. \*K

### Electrical Characteristics for CY2305CSXI-XX, CY2305CSXA-XX and CY2309CSXI-XX

Electrical characteristics table for CY2305CSXI-XX, CY2305CSXA-XX and CY2309CSXI-XX industrial/automotive-A temperature devices.

| Parameter                 | Description                         | Test Conditions                                                 | Min | Max | Unit |

|---------------------------|-------------------------------------|-----------------------------------------------------------------|-----|-----|------|

| V <sub>IL</sub>           | Input LOW voltage <sup>[9]</sup>    |                                                                 | -   | 0.8 | V    |

| V <sub>IH</sub>           | Input HIGH voltage <sup>[9]</sup>   |                                                                 | 2.0 | -   | V    |

| IIL                       | Input LOW current                   | V <sub>IN</sub> = 0 V                                           | -   | 50  | μΑ   |

| I <sub>IH</sub>           | Input HIGH current                  | V <sub>IN</sub> = V <sub>DD</sub>                               | -   | 100 | μΑ   |

| V <sub>OL</sub>           | Output LOW voltage <sup>[10]</sup>  | I <sub>OL</sub> = 8 mA (–1)<br>I <sub>OH</sub> =12 mA (–1H)     | -   | 0.4 | V    |

| V <sub>OH</sub>           | Output HIGH voltage <sup>[10]</sup> | I <sub>OH</sub> = –8 mA (–1)<br>I <sub>OL</sub> = –12 mA (–1H)  | 2.4 | _   | V    |

| I <sub>DD</sub> (PD mode) | Power-down supply current           | REF = 0 MHz                                                     | -   | 25  | μΑ   |

| I <sub>DD</sub>           | Supply current                      | Unloaded outputs at 66.67 MHz,<br>SEL inputs at V <sub>DD</sub> | _   | 35  | mA   |

### Switching Characteristics for CY2305CSXC-XX and CY2309CSXC-XX

Switching characteristics table for CY2305CSXC-1 and CY2309CSXC-1 commercial temperature devices. All parameters are specified with loaded outputs.

| Parameter         | Name                                                            | Test Conditions                                                                   | Min      | Тур | Max           | Unit       |

|-------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|----------|-----|---------------|------------|

| t <sub>1</sub>    | Output frequency                                                | 30 pF load<br>10 pF load                                                          | 10<br>10 | -   | 100<br>133.33 | MHz<br>MHz |

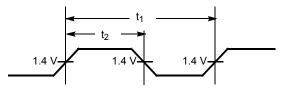

| t <sub>DC</sub>   | Output duty cycle <sup>[10]</sup> = $t_2 \div t_1$              | Measured at 1.4 V, F <sub>out</sub> > 50 MHz                                      | 40       | 50  | 60            | %          |

|                   |                                                                 | Measured at 1.4 V, $F_{out} \le 50 \text{ MHz}$                                   | 45       | 50  | 55            | %          |

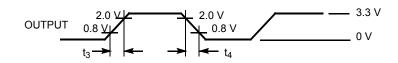

| t <sub>3</sub>    | Rise time <sup>[10]</sup>                                       | Measured between 0.8 V and 2.0 V                                                  | -        | -   | 2.25          | ns         |

| t <sub>4</sub>    | Fall time <sup>[10]</sup>                                       | Measured between 0.8 V and 2.0 V                                                  | -        | -   | 2.25          | ns         |

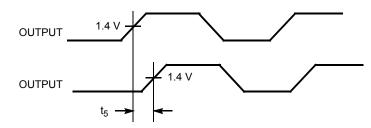

| t <sub>5</sub>    | Output-to-output skew <sup>[10]</sup>                           | All outputs equally loaded                                                        | -        | -   | 200           | ps         |

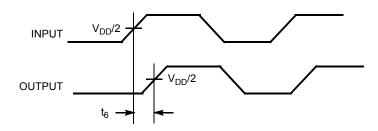

| t <sub>6A</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[10]</sup> | Measured at V <sub>DD</sub> /2                                                    | -        | 0   | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF rising edge to CLKOUT rising edge <sup>[10]</sup>    | Measured at V <sub>DD</sub> /2. Measured in PLL Bypass mode, CY2309C device only. | 1        | 5   | 8.7           | ns         |

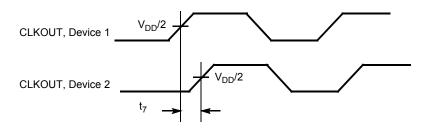

| t <sub>7</sub>    | Device-to-device skew <sup>[10]</sup>                           | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices                      | -        | 0   | 700           | ps         |

| tj                | Cycle-to-cycle jitter, peak <sup>[10]</sup>                     | Measured at 66.67 MHz, loaded outputs                                             | -        | 50  | 175           | ps         |

| t <sub>LOCK</sub> | PLL lock time <sup>[10]</sup>                                   | Stable power supply, valid clock<br>presented on REF pin                          | -        | -   | 1.0           | ms         |

<sup>.</sup>REF input has a threshold voltage of V<sub>DD</sub>/2.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

### Switching Characteristics for CY2305CSXC-XX and CY2309CSXC-XX

Switching characteristics table for CY2305CSXC-1H and CY2309CSXC-1H commercial temperature devices. All parameters are specified with loaded outputs.

| Parameter         | Name                                                            | Description                                                                          | Min      | Тур | Max           | Unit       |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|-----|---------------|------------|

| t <sub>1</sub>    | Output frequency                                                | 30-pF load<br>10-pF load                                                             | 10<br>10 | -   | 100<br>133.33 | MHz<br>MHz |

| t <sub>DC</sub>   | Output duty cycle <sup>[11]</sup> = $t_2 \div t_1$              | Measured at 1.4 V, F <sub>out</sub> > 50 MHz                                         | 40       | 50  | 60            | %          |

|                   |                                                                 | Measured at 1.4 V, $F_{out} \le 50 \text{ MHz}$                                      | 45       | 50  | 55            | %          |

| t <sub>3</sub>    | Rise time <sup>[11]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | -        | -   | 1.5           | ns         |

| t <sub>4</sub>    | Fall time <sup>[11]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | -        | _   | 1.5           | ns         |

| t <sub>5</sub>    | Output-to-output skew <sup>[11]</sup>                           | All outputs equally loaded                                                           | -        | -   | 200           | ps         |

| t <sub>6A</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[11]</sup> | Measured at V <sub>DD</sub> /2                                                       | -        | 0   | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[11]</sup> | Measured at V <sub>DD</sub> /2. Measured in PLL<br>Bypass mode, CY2309C device only. | 1        | 5   | 8.7           | ns         |

| t <sub>7</sub>    | Device-to-device skew <sup>[11]</sup>                           | Measured at $V_{DD}/2$ on the CLKOUT pins of devices                                 | -        | 0   | 700           | ps         |

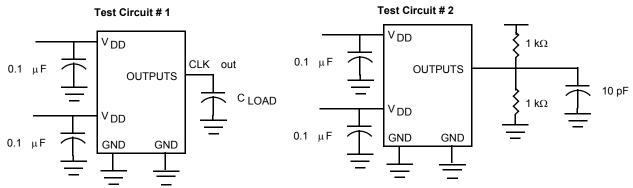

| t <sub>8</sub>    | Output slew rate <sup>[11]</sup>                                | Measured between 0.8 V and 2.0 V using<br>Test circuit #2                            | 1        | -   | -             | V/ns       |

| tj                | Cycle-to-cycle jitter, peak <sup>[11]</sup>                     | Measured at 66.67 MHz, loaded outputs                                                | _        | —   | 175           | ps         |

| t <sub>LOCK</sub> | PLL lock time <sup>[11]</sup>                                   | Stable power supply, valid clock<br>presented on REF pin                             | -        | -   | 1.0           | ms         |

# Switching Characteristics for CY2305CSXI-XX, CY2305CSXA-XX and CY2309CSXI-XX

Switching characteristics table for CY2305CSXI-1, CY2305CSXA-1, and CY2309CSXI-1 industrial temperature devices. All parameters are specified with loaded outputs.

| Parameter         | Name                                                            | Test Conditions                                                                      | Min      | Тур | Max           | Unit       |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|-----|---------------|------------|

| t <sub>1</sub>    | Output frequency                                                | 30 pF load<br>10 pF load                                                             | 10<br>10 | -   | 100<br>133.33 | MHz<br>MHz |

| t <sub>DC</sub>   | Output duty cycle <sup>[11]</sup> = $t_2 \div t_1$              | Measured at 1.4 V, F <sub>out</sub> > 50 MHz                                         | 40       | 50  | 60            | %          |

|                   |                                                                 | Measured at 1.4 V, F <sub>out</sub> <= 50 MHz                                        | 45       | 50  | 55            | %          |

| t <sub>3</sub>    | Rise time <sup>[11]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | _        | -   | 2.25          | ns         |

| t <sub>4</sub>    | Fall time <sup>[11]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | _        | _   | 2.25          | ns         |

| t <sub>5</sub>    | Output-to-output skew <sup>[11]</sup>                           | All outputs equally loaded                                                           | -        | -   | 200           | ps         |

| t <sub>6A</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[11]</sup> | Measured at V <sub>DD</sub> /2                                                       | -        | 0   | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[11]</sup> | Measured at V <sub>DD</sub> /2. Measured in PLL<br>Bypass mode, CY2309C device only. | 1        | 5   | 8.7           | ns         |

| t <sub>7</sub>    | Device-to-device skew <sup>[11]</sup>                           | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices                         | -        | 0   | 700           | ps         |

| tj                | Cycle-to-cycle jitter, peak <sup>[11]</sup>                     | Measured at 66.67 MHz, loaded outputs                                                | _        | 50  | 175           | ps         |

| t <sub>LOCK</sub> | PLL lock time <sup>[11]</sup>                                   | Stable power supply, valid clock<br>presented on REF pin                             | -        | -   | 1.0           | ms         |

Note 11. Parameter is guaranteed by design and characterization. Not 100% tested in production.

### Switching characteristics table for CY2305CSXI-1H, CY2305CSXA-1H and CY2309CSXI-1H

Switching characteristics table for CY2305CSXI-1H, CY2305CSXA-1H and CY2309CSXI-1H industrial/automotive-A temperature device. All parameters are specified with loaded outputs.

| Parameter         | Name                                                            | Description                                                                          | Min      | Тур | Max           | Unit       |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|-----|---------------|------------|

| t <sub>1</sub>    | Output frequency                                                | 30 pF load<br>10 pF load                                                             | 10<br>10 | -   | 100<br>133.33 | MHz<br>MHz |

| t <sub>DC</sub>   | Output duty cycle <sup>[12]</sup> = $t_2 \div t_1$              | Measured at 1.4 V, F <sub>out</sub> > 50 MHz                                         | 40       | 50  | 60            | %          |

|                   |                                                                 | Measured at 1.4 V, F <sub>out</sub> <= 50 MHz                                        | 45       | 50  | 55            | %          |

| t <sub>3</sub>    | Rise time <sup>[12]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | -        | -   | 1.5           | ns         |

| t <sub>4</sub>    | Fall time <sup>[12]</sup>                                       | Measured between 0.8 V and 2.0 V                                                     | -        | -   | 1.5           | ns         |

| t <sub>5</sub>    | Output-to-output skew <sup>[12]</sup>                           | All outputs equally loaded                                                           | -        | -   | 200           | ps         |

| t <sub>6A</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[12]</sup> | Measured at V <sub>DD</sub> /2                                                       | -        | 0   | ±350          | ps         |

| t <sub>6B</sub>   | Delay, REF rising edge to<br>CLKOUT rising edge <sup>[12]</sup> | Measured at V <sub>DD</sub> /2. Measured in PLL<br>Bypass mode, CY2309C device only. | 1        | 5   | 8.7           | ns         |

| t <sub>7</sub>    | Device-to-device skew <sup>[12]</sup>                           | Measured at V <sub>DD</sub> /2 on the CLKOUT pins of devices                         | -        | 0   | 700           | ps         |

| t <sub>8</sub>    | Output slew rate <sup>[12]</sup>                                | Measured between 0.8 V and 2.0 V using Test circuit #2                               | 1        | -   | -             | V/ns       |

| t <sub>J</sub>    | Cycle-to-cycle jitter, peak <sup>[12]</sup>                     | Measured at 66.67 MHz, loaded outputs                                                | _        | -   | 175           | ps         |

| t <sub>LOCK</sub> | PLL lock time <sup>[12]</sup>                                   | Stable power supply, valid clock<br>presented on REF pin                             | -        | -   | 1.0           | ms         |

### **Switching Waveforms**

#### Figure 3. Duty Cycle Timing

#### Figure 4. All Outputs Rise/Fall Time

Note 12. Parameter is guaranteed by design and characterization. Not 100% tested in production.

#### Figure 5. Output-Output Skew

Figure 6. Input-Output Propagation Delay

#### Figure 7. Device-Device Skew

# **Test Circuits**

For parameter t<sub>8</sub> (output slew rate) on -1H devices

# **Ordering Information**

| Ordering Code     | Package Type                        | Operating Range |

|-------------------|-------------------------------------|-----------------|

| Pb-free - CY2305C |                                     |                 |

| CY2305CSXC-1      | 8-pin 150 Mil SOIC                  | Commercial      |

| CY2305CSXC-1T     | 8-pin 150 Mil SOIC – Tape and reel  | Commercial      |

| CY2305CSXC-1H     | 8-pin 150 Mil SOIC                  | Commercial      |

| CY2305CSXC-1HT    | 8-pin 150 Mil SOIC – Tape and reel  | Commercial      |

| CY2305CSXI-1      | 8-pin 150 Mil SOIC                  | Industrial      |

| CY2305CSXI-1T     | 8-pin 150 Mil SOIC – Tape and reel  | Industrial      |

| CY2305CSXI-1H     | 8-pin 150 Mil SOIC                  | Industrial      |

| CY2305CSXI-1HT    | 8-pin 150 Mil SOIC – Tape and reel  | Industrial      |

| CY2305CSXA-1H     | 8-pin 150 Mil SOIC                  | Automotive-A    |

| CY2305CSXA-1HT    | 8-pin 150 Mil SOIC – Tape and reel  | Automotive-A    |

| Pb-free - CY2309C |                                     |                 |

| CY2309CSXC-1      | 16-pin 150 Mil SOIC                 | Commercial      |

| CY2309CSXC-1T     | 16-pin 150 Mil SOIC – Tape and reel | Commercial      |

| CY2309CSXC-1H     | 16-pin 150 Mil SOIC                 | Commercial      |

| CY2309CSXC-1HT    | 16-pin 150 Mil SOIC – Tape and reel | Commercial      |

| CY2309CSXI-1      | 16-pin 150 Mil SOIC                 | Industrial      |

| CY2309CSXI-1T     | 16-pin 150 Mil SOIC – Tape and reel | Industrial      |

| CY2309CSXI-1H     | 16-pin 150 Mil SOIC                 | Industrial      |

| CY2309CSXI-1HT    | 16-pin 150 Mil SOIC – Tape and reel | Industrial      |

| CY2309CZXC-1      | 16-pin 4.4 mm TSSOP                 | Commercial      |

| CY2309CZXC-1T     | 16-pin 4.4 mm TSSOP – Tape and reel | Commercial      |

| CY2309CZXC-1H     | 16-pin 4.4 mm TSSOP                 | Commercial      |

| CY2309CZXC-1HT    | 16-pin 4.4 mm TSSOP – Tape and reel | Commercial      |

| CY2309CZXI-1      | 16-pin 4.4 mm TSSOP                 | Industrial      |

| CY2309CZXI-1T     | 16-pin 4.4 mm TSSOP – Tape and reel | Industrial      |

| CY2309CZXI-1H     | 16-pin 4.4 mm TSSOP                 | Industrial      |

| CY2309CZXI-1HT    | 16-pin 4.4 mm TSSOP – Tape and reel | Industrial      |

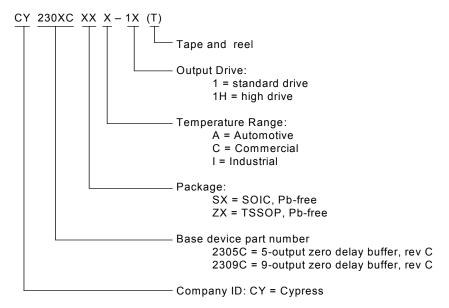

### **Ordering Code Definition**

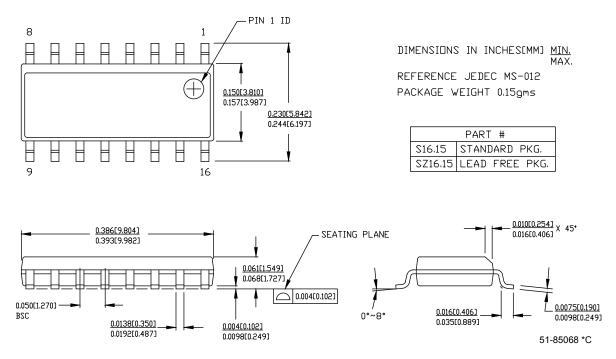

### **Package Drawing and Dimensions**

#### Figure 9. 16-Pin (150 Mil) SOIC SZ16.15

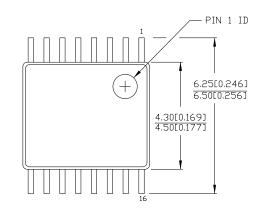

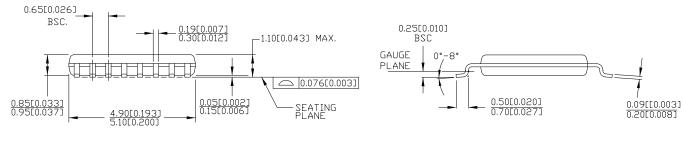

Figure 10. 16-Pin TSSOP 4.40 mm Body ZZ16.173

DIMENSIONS IN MMEINCHESJ MIN. Max.

REFERENCE JEDEC MD-153 PACKAGE WEIGHT 0.05gms

| PART #   |                |  |  |

|----------|----------------|--|--|

| Z16.173  | STANDARD PKG.  |  |  |

| ZZ16.173 | LEAD FREE PKG. |  |  |

51-85091 \*C

# Acronyms

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | Complementary metal oxide semiconductor |

| PLL     | phase locked loop                       |

| SOIC    | small outline integrated circuit        |

| TSSOP   | thin shrunk small outline package       |

### **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | degrees Celsius |

| V      | Volts           |

| kHz    | Kilohertz       |

| MHz    | megahertz       |

| μΑ     | microamperes    |

| mA     | milliamperes    |

| ms     | milliseconds    |

| ns     | nanoseconds     |

| pF     | picofarads      |

| ps     | picoseconds     |

# **Document History Page**

| REV. | ECN NO.   | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|-----------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 224421    | See ECN    | RGL                | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *A   | 268571    | See ECN    | RGL                | Added bullet for 5 V tolerant inputs in the features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *В   | 276453    | See ECN    | RGL                | Minor Change: Moved one sentence from the features to the Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *C   | 303063    | See ECN    | RGL                | Updated data sheet as per characterization data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *D   | 318315    | See ECN    | RGL                | Data sheet rewrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *E   | 344815    | See ECN    | RGL                | Minor Error: Corrected the header of all the AC/DC tables with the right part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *F   | 127988938 | See ECN    | KVM                | Changed title from ,low Cost 3.3 V Zero Delay Buffer to 3.3 V Zero Delay Clock<br>Buffer<br>Specified the VIL minimum value to -0.3 V<br>Specified the VIH maximum value to VDD + 0.3 V<br>Changed DC Input Voltage (REF) maximum value in Absolute Maximum sectio<br>Removed references to 5 V tolerant inputs (pages 1 and 2)<br>Removed Pentium compatibility reference<br>Added CY2305C block diagram<br>Added ,peak to the jitter specifications<br>Changed typical jitter from 75 ps to 50 ps for standard drive devices<br>For standard drive devices, tightened rise/fall times from 2.5 ns to 2.25 ns<br>Tightened cycle-to-cycle jitter from 200 ps to 175 ps<br>Tightened output-to-output skew from 250 ps to 200 ps |

| *G   | 1561504   | See ECN    | KVM/NSI<br>/AESA   | Added CY2305C Automotive-A grade devices<br>Extended duty cycle specs to cover entire frequency range<br>Changed from Preliminary to Final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *H   | 2558537   | 08/27/08   | KVM/AESA           | Added CY2305CSXA-1 and CY2305CSXA-1T parts in Ordering Information table under Pb-free CY2305C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *    | 2901743   | 03/30/2010 | VIVG               | Updated Package Drawing and Dimensions.<br>Added Ordering Code Definition<br>Added Sales, Solutions, and Legal Information URLs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *J   | 3080990   | 11/10/2010 | BASH               | Modified pin diagram of Figure 1.<br>Updated as per new template<br>Added Acronyms and Units of Measure table<br>Added TOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *K   | 3160535   | 02/03/2011 | BASH               | Removed min value of $V_{IL}$ and max value of $V_{IH}$ from Electrical Characteristic Table on page 6 and page 7.<br>Removed Prune parts CY2305CSXA-1 and CY2305CSXA-1T from the datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturers representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

| Products                 |                           |

|--------------------------|---------------------------|

| Automotive               | cypress.com/go/automotive |

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

|                          | cypress.com/go/plc        |

| Memory                   | cypress.com/go/memory     |

| Optical & Image Sensing  | cypress.com/go/image      |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2004-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress,Åô product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 38-07672 Rev. \*K

Revised February 3, 2011

Page 17 of 17

All products and company names mentioned in this document may be the trademarks of their respective holders.