# 1-Mbit (128 K × 8) Serial (SPI) nvSRAM with Real Time Clock

#### **Features**

- 1-Mbit nonvolatile static random access memory (nvSRAM)

- □ Internally organized as 128 K x 8

- □ STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by using SPI instruction (Software STORE) or HSB pin (Hardware STORE)

- RECALL to SRAM initiated on power-up (Power Up RECALL) or by SPI instruction (Software RECALL)

- □ Automatic STORE on power-down with a small capacitor

- High reliability

- □ Infinite read, write, and RECALL cycles

- □ 1 million STORE cycles to QuantumTrap

- □ Data retention: 20 years at 85 °C

- Real time clock (RTC)

- □ Full-featured RTC

- Watchdog timer

- Clock alarm with programmable interrupts

- ☐ Backup power fail indication

- □ Square wave output with programmable frequency (1 Hz, 512 Hz, 4096 Hz, 32.768 kHz)

- Capacitor or battery backup for RTC

- □ Backup current of 0.45 µA (typical)

- 40 MHz, and 104 MHz High-speed serial peripheral interface (SPI)

- □ 40 MHz clock rate SPI write and read with zero cycle delay

- □ 104 MHz clock rate SPI write and read (with special fast read instructions)

- □ Supports SPI mode 0 (0, 0) and mode 3 (1, 1)

- SPI access to special functions

- □ Nonvolatile STORE/RECALL

- □ 8-byte serial number

- Manufacturer ID and Product ID

- □ Sleep mode

- Write protection

- ☐ Hardware protection using Write Protect (WP) pin

- □ Software protection using Write Disable instruction

- ☐ Software block protection for 1/4, 1/2, or entire array

- Low power consumption

- □ Average active current of 3 mA at 40 MHz operation

- □ Average standby mode current of 250 µA

- □ Sleep mode current of 8 µA

- Industry standard configurations

- Operating voltages:

- CY14C101PA: V<sub>CC</sub> = 2.4 V to 2.6 V

- CY14B101PA: V<sub>CC</sub> = 2.7 V to 3.6 V

- CY14E101PA: V<sub>CC</sub> = 4.5 V to 5.5 V

- □ Industrial temperature

- ☐ 16-pin small outline integrated circuit (SOIC) package

- □ Restriction of hazardous substances (RoHS) compliant

#### Overview

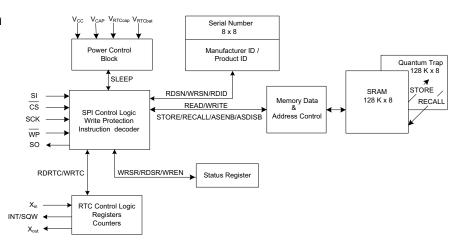

The Cypress CY14X101PA combines a 1 Mbit nvSRAM<sup>[1]</sup> with a full-featured RTC in a monolithic integrated circuit with serial SPI interface. The memory is organized as 128 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world's most reliable nonvolatile memory. The SRAM provides infinite read and write cycles, while the QuantumTrap cells provide highly reliable nonvolatile storage of data. Data transfers from SRAM to the nonvolatile elements (STORE operation) takes place automatically at power-down. On power-up, data is restored to the SRAM from the nonvolatile memory (RECALL operation). You can also initiate the STORE and RECALL operations through SPI instruction.

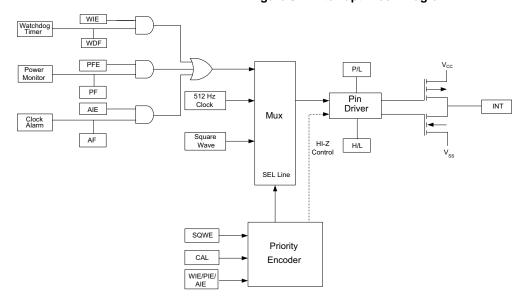

#### Logic Block Diagram

#### Note

1. This device will be referred to as nvSRAM throughout the document.

#### Contents

| Pinout3                                      | FAST_RDS            |

|----------------------------------------------|---------------------|

| Pin Definitions3                             | (Fast Serial Nur    |

| Device Operation4                            | Device ID           |

| SRAM Write4                                  | RDID (Dev           |

| SRAM Read4                                   | FAST_RDI            |

| STORE Operation4                             | <b>HOLD Pin Ope</b> |

| AutoStore Operation4                         | Real Time Cloc      |

| Software STORE Operation5                    | nvTIME Op           |

| Hardware STORE and HSB pin Operation5        | Clock Oper          |

| RECALL Operation5                            | Reading th          |

| Hardware RECALL (Power-Up)5                  | Setting the         |

| Software RECALL5                             | Backup Po           |

| Disabling and Enabling AutoStore5            | Stopping a          |

| Serial Peripheral Interface6                 | Calibrating         |

| SPI Overview6                                | Alarm               |

| SPI Modes7                                   | Watchdog            |

| SPI Operating Features8                      | Programma           |

| Power-Up8                                    | Power Mor           |

| Power-Down8                                  | Backup Po           |

| Active Power and Standby Power Modes8        | Interrupts .        |

| SPI Functional Description9                  | Interrupt R         |

| Status Register10                            | Flags Regi          |

| Read Status Register (RDSR) Instruction10    | Maximum Rati        |

| Fast Read Status Register                    | Operating Ran       |

| (FAST_RDSR) Instruction10                    | DC Electrical (     |

| · ·                                          | Data Retention      |

| Write Status Register (WRSR) Instruction     |                     |

| Write Protection and Block Protection11      | Capacitance         |

| Write Enable (WREN) Instruction              | Thermal Resis       |

| Write Disable (WRDI) Instruction             | AC Test Loads       |

| Block Protection                             | AC Test Condi       |

| Hardware Write Protection (WP Pin)12         | RTC Character       |

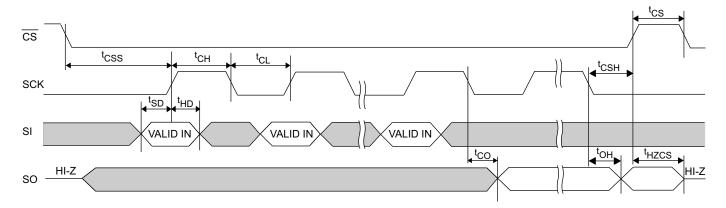

| Memory Access12                              | AC Switching        |

| Read Sequence (READ) Instruction             | Switching Way       |

| Fast Read Sequence (FAST_READ) Instruction12 | AutoStore or F      |

| Write Sequence (WRITE) Instruction13         | Switching Wav       |

| RTC Access15                                 | Software Cont       |

| READ RTC (RDRTC) Instruction15               | Switching Wav       |

| Fast Read Sequence                           | Hardware STO        |

| (FAST_RDRTC) Instruction15                   | Switching Wav       |

| WRITE RTC (WRTC) Instruction16               | Ordering Infor      |

| nvSRAM Special Instructions16                | Ordering C          |

| Software STORE (STORE) Instruction16         | Package Diagr       |

| Software RECALL (RECALL) Instruction16       | Acronyms            |

| AutoStore Enable (ASENB) Instruction16       | Document Cor        |

| AutoStore Disable (ASDISB) Instruction17     | Units of Me         |

| Special Instructions17                       | <b>Document His</b> |

| SLEEP Instruction17                          | Sales, Solution     |

| Serial Number17                              | Worldwide           |

| WRSN (Serial Number Write) Instruction17     | Products            |

| RDSN (Serial Number Read) Instruction18      | PSoC Solu           |

| FAST_RDSN                                   |          |

|---------------------------------------------|----------|

| (Fast Serial Number Read) Instruction       | 18       |

| Device ID                                   | 19       |

| RDID (Device ID Read) Instruction           | 19       |

| FAST_RDID (Fast Device ID Read) Instruction | 20       |

| HOLD Pin Operation                          |          |

| Real Time Clock Operation                   | 21       |

| nvTIME Operation                            | 21       |

| Clock Operations                            | 21       |

| Reading the Clock                           | 21       |

| Setting the Clock                           | 21       |

| Backup Power                                |          |

| Stopping and Starting the Oscillator        | 21       |

| Calibrating the Clock                       |          |

| Alarm                                       |          |

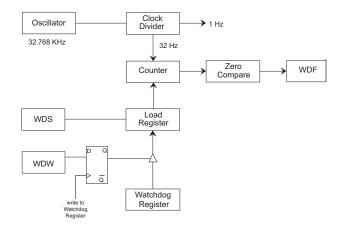

| Watchdog Timer                              |          |

| Programmable Square Wave Generator          |          |

| Power Monitor                               | 23       |

| Backup Power Monitor                        |          |

| Interrupts                                  |          |

| Interrupt Register                          |          |

| Flags Register                              |          |

| Maximum Ratings                             |          |

| Operating Range                             | 30       |

| DC Electrical Characteristics               |          |

| Data Retention and Endurance                |          |

| CapacitanceThermal Resistance               |          |

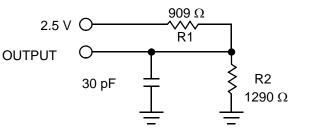

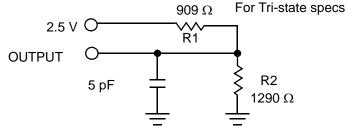

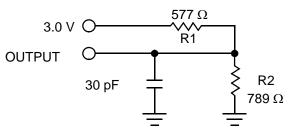

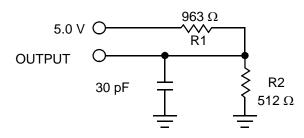

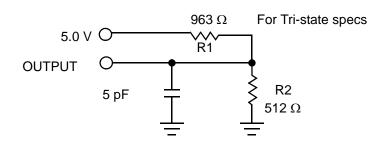

| AC Test Loads and Waveforms                 |          |

| AC Test Conditions                          |          |

| RTC Characteristics                         |          |

| AC Switching Characteristics                |          |

| Switching Waveforms                         |          |

| AutoStore or Power-Up RECALL                |          |

| Switching Waveforms                         |          |

| Software Controlled STORE/RECALL Cycles     |          |

| Switching Waveforms                         |          |

| Hardware STORE Cycle                        |          |

| Switching Waveforms                         | 37       |

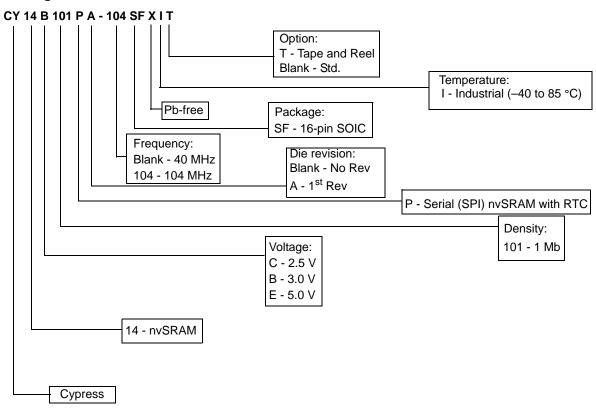

| Ordering Information                        |          |

| Ordering Code Definitions                   | 38       |

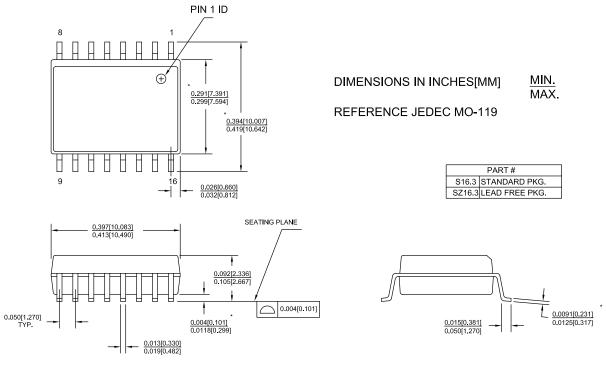

| Package Diagram                             | 39       |

| Acronyms                                    |          |

| Document Conventions                        |          |

| Units of Measure                            |          |

| Document History Page                       |          |

| Sales, Solutions, and Legal Information     |          |

| Worldwide Sales and Design Support          |          |

| Products                                    | 43<br>43 |

|                                             |          |

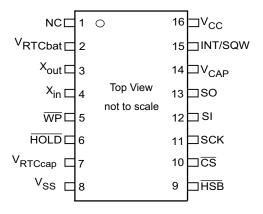

#### **Pinout**

Figure 1. 16-pin SOIC pinout

#### **Pin Definitions**

| Pin Name                | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                      | Input        | Chip select: Activates the device when pulled LOW. Driving this pin HIGH puts the device in low power standby mode.                                                                                                                                                                                                                                                                                     |

| SCK                     | Input        | Serial clock: Runs at speeds up to a maximum of f <sub>SCK</sub> . Serial input is latched at the rising edge of this clock. Serial output is driven at the falling edge of the clock.                                                                                                                                                                                                                  |

| SI                      | Input        | Serial input: Pin for input of all SPI instructions and data.                                                                                                                                                                                                                                                                                                                                           |

| SO                      | Output       | Serial output: Pin for output of data through SPI.                                                                                                                                                                                                                                                                                                                                                      |

| WP                      | Input        | Write Protect: Implements hardware write protection in SPI.                                                                                                                                                                                                                                                                                                                                             |

| HOLD                    | Input        | HOLD pin: Suspends Serial Operation                                                                                                                                                                                                                                                                                                                                                                     |

| HSB                     | Input/Output | Hardware STORE Busy: Output: Indicates busy status of nvSRAM when LOW. After each Hardware and Software STORE operation HSB is driven HIGH for a short time (t <sub>HHHD</sub> ) with standard output high current and then a weak internal pull-up resistor keeps this pin HIGH (external pull-up resistor connection optional). Input: Hardware STORE implemented by pulling this pin LOW externally. |

| V <sub>CAP</sub>        | Power supply | AutoStore capacitor. Supplies power to the nvSRAM during power loss to STORE data from the SRAM to nonvolatile elements. If AutoStore is not needed, this pin must be left as No Connect. It must never be connected to ground.                                                                                                                                                                         |

| V <sub>RTCcap</sub> [2] | Power supply | Capacitor backup for RTC: Left unconnected if V <sub>RTCbat</sub> is used.                                                                                                                                                                                                                                                                                                                              |

| V <sub>RTCbat</sub> [2] | Power supply | Battery backup for RTC: Left unconnected if V <sub>RTCcap</sub> is used.                                                                                                                                                                                                                                                                                                                                |

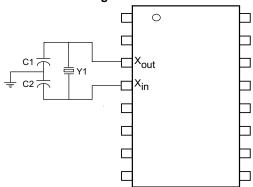

| Xout [2]                | Output       | Crystal output connection                                                                                                                                                                                                                                                                                                                                                                               |

| Xin <sup>[2]</sup>      | Input        | Crystal input connection                                                                                                                                                                                                                                                                                                                                                                                |

| INT/SQW [2]             | Output       | Interrupt output/calibration/square wave. Programmable to respond to the clock alarm, the watchdog timer, and the power monitor. Also programmable to either active HIGH (push or pull) or LOW (open drain). In calibration mode, a 512-Hz square wave is driven out. In the square wave mode, you may select a frequency of 1 Hz, 512 Hz, 4,096 Hz, or 32,768 Hz to be used as a continuous output.    |

| NC                      | No connect   | No connect. This pin is not connected to the die.                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>         | Power supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>CC</sub>         | Power supply | Power supply                                                                                                                                                                                                                                                                                                                                                                                            |

Note

2. Left unconnected if RTC feature is not used.

#### **Device Operation**

CY14X101PA is a 1-Mbit SPI nvSRAM memory with integrated RTC and SPI interface. All the reads and writes to nvSRAM happen to the SRAM, which gives nvSRAM the unique capability to handle infinite writes to the memory. The data in SRAM is secured by a STORE sequence that transfers the data in parallel to the nonvolatile QuantumTrap cells. A small capacitor (V<sub>CAP</sub>) is used to AutoStore the SRAM data in nonvolatile cells when power goes down providing power-down data security. The QuantumTrap nonvolatile elements built in the reliable SONOS technology make nvSRAM the ideal choice for secure data storage.

In CY14X101PA, the 1-Mbit memory array is organized as 128 K words × 8 bits. The memory can be accessed through a standard SPI interface that enables very high clock speeds up to 40 MHz with zero cycle delay read and write cycles. This nvSRAM chip also supports an SPI access speed of 104 MHz, with a special instruction for read operation. CY14X101PA supports SPI modes 0 and 3 (CPOL, CPHA = 0, 0 and 1, 1) and operates as SPI slave. The device is enabled using the Chip Select (CS) pin and accessed through Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins.

CY14X101PA provides the feature for hardware and software write protection through the WP pin and WRDI instruction. CY14X101PA also provides mechanisms for block write protection (1/4, 1/2, or full array) using BPO and BP1 pins in the Status Register. Further, the HOLD pin is used to suspend any serial communication without resetting the serial sequence.

CY14X101PA uses the standard SPI opcodes for memory access. In addition to the general SPI instructions for read and write, CY14X101PA provides four special instructions that allow access to four nvSRAM specific functions: STORE, RECALL, AutoStore Disable (ASDISB), and AutoStore Enable (ASENB).

The major benefit of nvSRAM over serial EEPROMs is that all reads and writes to nvSRAM are performed at the speed of SPI bus with zero cycle delay. Therefore, no wait time is required after any of the memory accesses. The STORE and RECALL operations need finite time to complete and all memory accesses are inhibited during this time. While a STORE or RECALL operation is in progress, the busy status of the device is indicated by the Hardware STORE Busy (HSB) pin and also reflected on the RDY bit of the Status Register.

#### **SRAM Write**

All writes to nvSRAM are carried out on the SRAM and do not use up any endurance cycles of the nonvolatile memory. This allows you to perform infinite write operations. A write cycle is performed through the WRITE instruction. The WRITE instruction is issued through the SI pin of the nvSRAM and consists of the WRITE opcode, three bytes of address, and one byte of data. Write to nvSRAM is done at SPI bus speed with zero cycle delay.

CY14X101PA allows burst mode writes to be performed through SPI. This enables write operations on consecutive addresses without issuing a new WRITE instruction. When the last address in memory is reached in burst mode, the address rolls over to 0x00000 and the device continues to write.

The SPI write cycle sequence is defined in the Memory Access section of SPI Protocol Description.

#### **SRAM Read**

A read cycle is performed at the SPI bus speed. The data is read out with zero cycle delay after the READ instruction is executed. The READ instruction can be used up to 40 MHz clock speed. The READ instruction is issued through the SI pin of the nvSRAM and consists of the READ opcode and three bytes of address. The data is read out on the SO pin.

Speeds higher than 40 MHz (up to 104 MHz) require a FAST\_READ instruction. The FAST\_READ instruction is issued through the SI pin of the nvSRAM and consists of the FAST\_READ opcode, three bytes of address, and one dummy byte. The data is read out on the SO pin.

CY14X101PA enables burst mode reads to be performed through SPI. This enables reads on consecutive addresses without issuing a new READ instruction. When the last address in memory is reached in burst mode read, the address rolls over to 0x00000 and the device continues to read.

The SPI read cycle sequence is defined in the Memory Access section of SPI Protocol Description

#### STORE Operation

STORE operation transfers the data from the SRAM to the nonvolatile QuantumTrap cells. The CY14X101PA STOREs data to the nonvolatile cells using one of the three STORE operations: AutoStore, activated on device power-down; Software STORE, activated by a STORE instruction; and Hardware STORE, activated by the HSB. During the STORE cycle, an erase of the previous nonvolatile data is first performed, followed by a program of the nonvolatile elements. After a STORE cycle is initiated, read/write to CY14X101PA is inhibited until the cycle is completed.

The  $\overline{\text{HSB}}$  signal or the  $\overline{\text{RDY}}$  bit in the Status Register can be monitored by the system to detect if a STORE or Software RECALL cycle is in progress. The busy status of nvSRAM is indicated by  $\overline{\text{HSB}}$  being pulled LOW or  $\overline{\text{RDY}}$  bit being set to '1'. To avoid unnecessary nonvolatile STOREs, AutoStore and Hardware STORE operations are ignored unless at least one write operation took place since the most recent STORE or RECALL cycle. However, software initiated STORE cycles are performed regardless of whether a write operation has taken place.

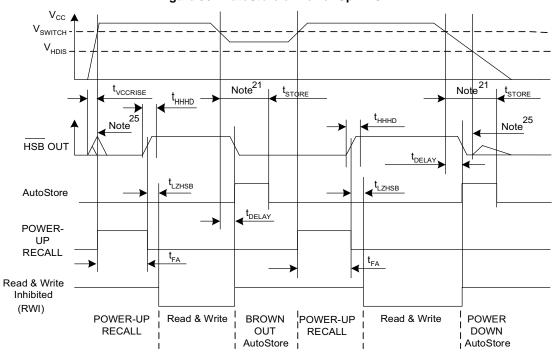

#### **AutoStore Operation**

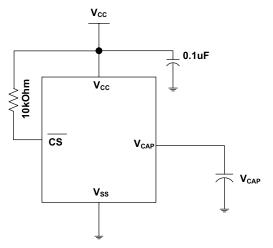

The AutoStore operation is a unique feature of nvSRAM which automatically stores the SRAM data to QuantumTrap cells during power-down. This STORE makes use of an external capacitor ( $V_{CAP}$ ) and enables the device to safely STORE the data in the nonvolatile memory when power goes down.

During normal operation, the device draws current from  $V_{CC}$  to charge the capacitor connected to the  $V_{CAP}$  pin. When the voltage on the  $V_{CC}$  pin drops below  $V_{SWITCH}$  during power-down, the device inhibits all memory accesses to nvSRAM and automatically performs a conditional STORE operation using the charge from the  $V_{CAP}$  capacitor. The AutoStore operation is not initiated if no write cycle has been performed since last RECALL.

**Note** If a capacitor is not connected to  $V_{CAP}$  pin, AutoStore must be disabled by issuing the AutoStore Disable instruction (AutoStore Disable (ASDISB) Instruction on page 17). If AutoStore is enabled without a capacitor on the  $V_{CAP}$  pin, the device attempts an AutoStore operation without sufficient charge

to complete the Store. This corrupts the data stored in nvSRAM, Status Register, and the serial number, and it unlocks the SNL bit. To resume normal functionality, the WRSR instruction must be issued to update the nonvolatile bits BP0, BP1, and WPEN in the Status Register.

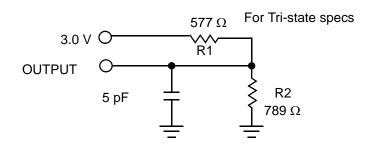

Figure 2 shows the proper connection of the storage capacitor ( $V_{CAP}$ ) for AutoStore operation. Refer to DC Electrical Characteristics on page 30 for the size of the  $V_{CAP}$

Figure 2. AutoStore Mode

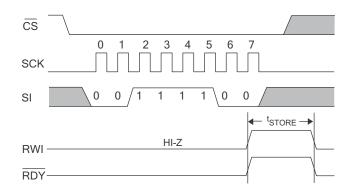

#### **Software STORE Operation**

Software STORE allows the user to trigger a STORE operation through a special SPI instruction. STORE operation is initiated by executing a STORE instruction regardless of whether or not a write has been performed since the last NV operation.

A STORE cycle takes  $t_{STORE}$  time to complete, during <u>whi</u>ch all the memory accesses to  $nv\underline{SRAM}$  are inhibited. The RDY bit of the Status Register or the HSB pin may be polled to find the Ready/Busy status of the nvSRAM. After the  $t_{STORE}$  cycle time is completed, the SRAM is activated again for read and write operations.

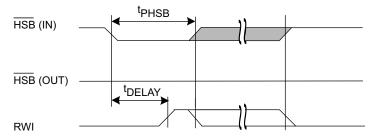

#### Hardware STORE and HSB pin Operation

The  $\overline{\text{HSB}}$  pin in CY14X101PA is used to control and acknowledge STORE operations. If no STORE/RECALL is in progress, this pin  $\underline{\text{can}}$  be used to request a Hardware STORE cycle. When the  $\overline{\text{HSB}}$  pin is driven LOW, the CY14X101PA conditionally initiates a STORE operation after  $t_{DELAY}$  duration. A STORE cycle starts only if a write to the SRAM has been performed since the last STORE or RECALL cycle. Reads and Writes to the memory are inhibited for  $t_{STORE}$  duration or as long as  $\overline{\text{HSB}}$  pin is LOW. The  $\overline{\text{HSB}}$  pin also acts as an open drain driver (internal 100 k $\Omega$  weak pull up resistor) that is internally driven LOW to indicate a busy condition when the STORE (initiated by any means) is in progress.

**Note** After each Hardware and Software STORE operation, HSB is driven HIGH for a short time ( $t_{HHHD}$ ) with standard output high current and then remains HIGH by an internal 100 k $\Omega$  pull-up resistor.

**Note** For successful last data byte STORE, a hardware STORE should be initiated at least one clock cycle after the last data bit D0 is received.

Upon completion of the STORE operation, the nvSRAM memory access is inhibited for  $t_{LZHSB}$  time after HSB pin returns HIGH. The HSB pin must be left unconnected if not used.

#### **RECALL Operation**

A RECALL operation transfers the data stored in the nonvolatile QuantumTrap elements to the SRAM. In CY14X101PA, a RECALL may be initiated in two ways: Hardware RECALL, initiated on power-up and Software RECALL, initiated by a SPI RECALL instruction.

Internally, RECALL is a two step procedure. First, the SRAM data is cleared. Next, the nonvolatile information is transferred into the SRAM cells. All memory accesses are inhibited while a RECALL cycle is in progress. The RECALL operation does not alter the data in the nonvolatile elements.

#### Hardware RECALL (Power-Up)

During power-up, when  $V_{CC}$  crosses  $V_{SWITCH}$ , an automatic RECALL sequence is initiated, which transfers the content of nonvolatile memory on to the SRAM. The data would have been previously stored on the nonvolatile memory through a STORE sequence.

A Power-Up RECALL cycle takes  $t_{FA}$  time to complete and the memory access is disabled during this time. The HSB pin is used to detect the Ready status of the device.

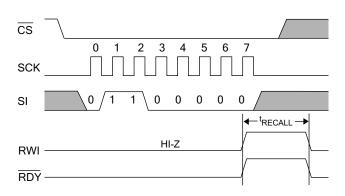

#### **Software RECALL**

Software RECALL allows you to initiate a RECALL operation to restore the content of nonvolatile memory on to the SRAM. In CY14X101PA, this can be done by issuing a RECALL instruction in SPI.

A Software RECALL takes  $t_{RECALL}$  time to complete during which all memory accesses to nvSRAM are inhibited. The controller must provide sufficient delay for the RECALL operation to complete before issuing any memory access instructions.

#### **Disabling and Enabling AutoStore**

If the application does not require the AutoStore feature, it can be disabled in CY14X101PA by using the ASDISB instruction. If this is done, the nvSRAM does not perform a STORE operation at power-down.

AutoStore can be re-enabled by using the ASENB instruction. However, these operations are not nonvolatile and if you need this setting to survive the power cycle, a STORE operation must be performed following AutoStore Disable or Enable operation.

**Note** CY14X101PA comes from the factory with AutoStore Enabled.

**Note** If AutoStore is disabled and  $V_{CAP}$  is not required, then the  $V_{CAP}$  pin must be left open. The  $V_{CAP}$  pin must never be connected to ground. The Power Up RECALL operation cannot be disabled in any case.

#### **Serial Peripheral Interface**

#### **SPI Overview**

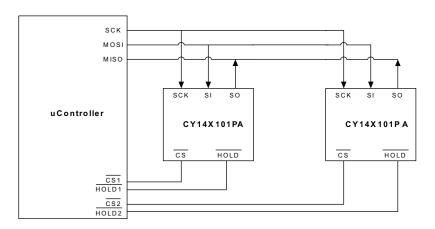

The SPI is a four-pin interface with Chip Select ( $\overline{CS}$ ), Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins. CY14X101PA provides serial access to nvSRAM through SPI interface. The SPI bus on CY14X101PA can run at speeds up to 104 MHz except RDRTC and READ instruction.

The SPI is a synchronous serial interface, which uses clock and data pins for memory access and supports multiple devices on the data bus. An SPI bus device is activated using the CS pin.

The relationship between chip select, clock, and data is dictated by the SPI mode. CY14X101PA supports SPI modes 0 and 3. In both these modes, data is clocked in the nvSRAM on the rising edge of SCK starting from the first rising edge after CS goes active.

The SPI protocol is controlled by opcodes. These opcodes specify the commands from the bus master to the slave device. After CS is activated, the first byte transferred from the bus master is the opcode. Following the opcode, any addresses and data are then transferred. The CS must go inactive after an operation is complete and before a new opcode can be issued.

The commonly used terms used in SPI protocol are given below:

#### SPI Master

The SPI master device controls the operations on a SPI bus. A SPI bus may have only one master with one or more slave devices. All the slaves share the same SPI bus lines and the master may select any of the slave devices using the CS pin. All the operations must be initiated by the master activating a slave device by pulling the CS pin of the slave LOW. The master also generates the SCK and all the data transmission on SI and SO lines are synchronized with this clock.

#### SPI Slave

The SPI slave device is activated by the master through the Chip Select line. A slave device gets the SCK as an input from the SPI master and all the communication is synchronized with this clock. SPI slave never initiates a communication on the SPI bus and acts on the instruction from the master.

CY14X101PA operates as a slave device and may share the SPI bus with multiple CY14X101PA devices or other SPI devices.

#### Chip Select (CS)

For selecting any slave device, the master needs to pull down the corresponding CS pin. Any instruction can be issued to a slave device only while the CS pin is LOW.

The CY14X101PA is selected when the  $\overline{CS}$  pin is LOW. When the device is not selected, data through the SI pin is ignored and the serial output pin (SO) remains in a high-impedance state.

**Note** A new instruction must begin with the falling edge of  $\overline{\text{CS}}$ . Therefore, only one opcode can be issued for each active Chip Select cycle.

#### Serial Clock (SCK)

Serial clock is generated by the SPI master  $\underline{and}$  the communication is synchronized with this clock after  $\overline{CS}$  goes LOW.

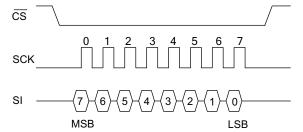

CY14X101PA allows SPI modes 0 and 3 for data communication. In both these modes, the inputs are latched by the slave device on the rising edge of SCK and outputs are issued on the falling edge. Therefore, the first rising edge of SCK signifies the arrival of the first bit (MSB) of SPI instruction on the SI pin. Further, all data inputs and outputs are synchronized with SCK.

#### Data Transmission SI/SO

SPI data bus consists of two lines, SI and SO, for serial data communication. The SI is also referred to as Master Out Slave In (MOSI) and SO is referred to as Master In Slave Out (MISO). The master issues instructions to the slave through the SI pin, while the slave responds through the SO pin. Multiple slave devices may share the SI and SO lines as described earlier.

CY14X101PA has two separate pins for SI and SO, which can be connected with the master as shown in Figure 3 on page 7.

#### Most Significant Bit (MSB)

The SPI protocol requires that the first bit to be transmitted is the Most Significant Bit (MSB). This is valid for both address and data transmission.

CY14X101PA requires a 3-byte address for any read or write operation. However, because the address is only 17 bits, it implies that the first seven bits that are fed in are ignored by the device. Although these seven bits are 'don't care', Cypress recommends that these bits are treated as 0s to enable seamless transition to higher memory densities.

#### Serial Opcode

After the slave device is selected with  $\overline{\text{CS}}$  going LOW, the first byte received is treated as the opcode for the intended operation.

CY14X101PA uses the standard opcodes for memory accesses. In addition to the memory accesses, CY14X101PA provides additional opcodes for the nvSRAM specific functions: STORE, RECALL, AutoStore Enable, and AutoStore Disable. Refer to Table 1 on page 9 for details on opcodes.

#### Invalid Opcode

If an invalid opcode is received, the opcode is ignored and the device ignores any <u>add</u>itional serial data on the SI pin until the next falling edge of CS and the SO pin remains tri-stated.

#### Status Register

CY14X101PA has an 8-bit Status Register. The bits in the Status Register are used to configure the SPI bus. These bits are described in the Table 3 on page 10.

Figure 3. System Configuration Using SPI nvSRAM

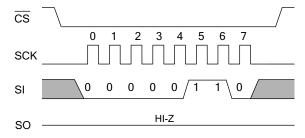

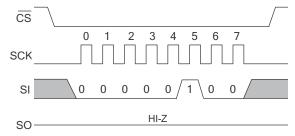

#### **SPI Modes**

CY14X101PA device may be driven by a microcontroller with its SPI peripheral running in either of these two modes:

- SPI Mode 0 (CPOL = 0, CPHA = 0)

- SPI Mode 3 (CPOL = 1, CPHA = 1)

For both these modes, the input data is latched in on the rising edge of SCK starting from the first rising edge after CS goes active. If the clock starts from a high state (in mode 3), the first rising edge after the clock toggles is considered. The output data is available on the falling edge of SCK.

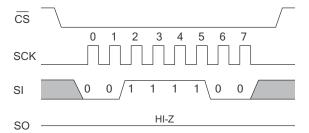

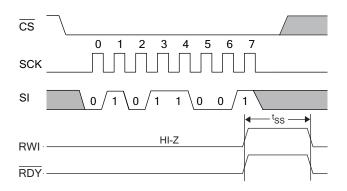

Figure 4. SPI Mode 0

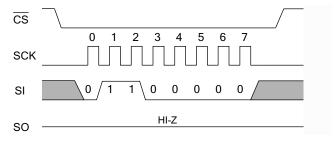

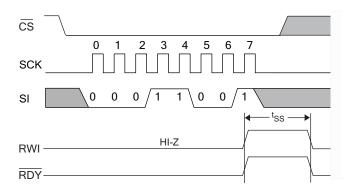

The two SPI modes are shown in Figure 4 and Figure 5. The status of clock when the bus master is in standby mode and not transferring data is:

- SCK remains at 0 for Mode 0

- SCK remains at 1 for Mode 3

CPOL and CPHA bits must be set in the SPI controller for the either Mode 0 or Mode 3. CY14X101PA detects the SPI mode from the status of SCK pin when device is selected by bringing the CS pin LOW. If SCK pin is LOW when the device is selected, SPI Mode 0 is assumed and if SCK pin is HIGH, CY14X101PA works in SPI Mode 3.

Figure 5. SPI Mode 3

#### **SPI Operating Features**

#### Power-Up

Power-up is defined as the condition when the power supply is turned on and  $\rm V_{CC}$  crosses  $\rm V_{switch}$  voltage.

As described earlier, at power-up nvSRAM performs a Power-Up RECALL operation for  $t_{\rm FA}$  duration during which, all memory accesses are disabled. The HSB pin can be probed to check the Ready/Busy status of nvSRAM after power-up.

The following are the device status after power-up:

- Selected (Active power mode) if CS pin is LOW

- Deselected (Standby power mode) if CS pin is HIGH

- Not in the Hold condition

- Status Register state:

- □ Write Enable (WEN) bit is reset to '0'.

- □ WPEN, BP1, BP0 unchanged from previous STORE operation

The WPEN, BP1, and BP0 bits of the Status Register are nonvolatile bits and remain unchanged from the previous STORE operation.

#### Power-Down

At power-down (continuous decay of  $V_{CC}$ ), when  $V_{CC}$  drops from the normal operating voltage and below the  $V_{SWITCH}$  threshold voltage, the device stops responding to any instruction sent to it. If a write cycle is in progress and the last data bit D0 has been received when the power goes down, it is allowed  $t_{DELAY}$  time to complete the write. After this, all memory accesses are inhibited and a conditional AutoStore operation is performed (AutoStore is not performed if no writes have happened since the last RECALL cycle). This feature prevents inadvertent writes to nvSRAM from happening during power-down. However, to avoid the possibility of inadvertent writes during power-down, ensure that the device is deselected and is in standby power mode and the  $\overline{CS}$  follows the voltage applied on  $V_{CC}$ .

#### **Active Power and Standby Power Modes**

When  $\overline{\text{CS}}$  is LOW, the device is selected and is in the active power mode. The device consumes I<sub>CC</sub> current, as specified in DC Electrical Characteristics on page 30. When  $\overline{\text{CS}}$  is HIGH, the device is deselected and the device goes into the standby power mode after t<sub>SB</sub> time if a STORE or RECALL cycle is not in progress. If a STORE/RECALL cycle is in progress, the device goes into the standby power mode after the STORE/RECALL cycle is completed. In the standby power mode the current drawn by the device drops to I<sub>SB</sub>.

#### **SPI Functional Description**

The CY14X101PA uses an 8-bit instruction register. Instructions and their operation codes are listed in Table 1. All instructions, addresses, and data are transferred with the MSB first and start with a <u>HIGH to LOW CS transition</u>. There are, in all, 21 SPI instructions that provide access to most of the functions in nvSRAM. Further, the WP, HOLD, and HSB pins provide additional functionality driven through hardware.

Table 1. Instruction Set

| Instruction Category       | Instruction Name | Opcode    | Operation                                                           |

|----------------------------|------------------|-----------|---------------------------------------------------------------------|

| Status Register Control In | structions       | •         |                                                                     |

|                            | RDSR             | 0000 0101 | Read Status Register                                                |

| Status Register access     | FAST_RDSR        | 0000 1001 | Fast Status Register read - SPI clock > 40 MHz                      |

|                            | WRSR             | 0000 0001 | Write Status Register                                               |

| Write protection and block | WREN             | 0000 0110 | Set Write Enable latch                                              |

| protection                 | WRDI             | 0000 0100 | Reset Write Enable latch                                            |

| SRAM Read/Write Instruct   | tions            | •         |                                                                     |

|                            | READ             | 0000 0011 | Read data from memory array                                         |

| Memory access              | FAST_READ        | 0000 1011 | Fast read - SPI clock > 40 MHz                                      |

|                            | WRITE            | 0000 0010 | Write data to memory array                                          |

| RTC Read/Write Instruction | ons              | -         | •                                                                   |

|                            | RDRTC            | 0001 0011 | Read RTC registers                                                  |

| RTC access                 | FAST_RDRTC       | 0001 1101 | Fast RTC register read - SPI clock > 25 MHz                         |

|                            | WRTC             | 0001 0010 | Write RTC registers                                                 |

| Special NV Instructions    |                  | •         | •                                                                   |

|                            | STORE            | 0011 1100 | Software STORE                                                      |

| nuCDAM anagial functions   | RECALL           | 0110 0000 | Software RECALL                                                     |

| nvSRAM special functions   | ASENB            | 0101 1001 | AutoStore enable                                                    |

|                            | ASDISB           | 0001 1001 | AutoStore disable                                                   |

| Special Instructions       |                  | •         | •                                                                   |

| Sleep                      | SLEEP            | 1011 1001 | Sleep mode enable                                                   |

|                            | WRSN             | 1100 0010 | Write serial number                                                 |

| Serial number              | RDSN             | 1100 0011 | Read serial number                                                  |

|                            | FAST_RDSN        | 1100 1001 | Fast serial number read - SPI clock > 40 MHz                        |

|                            | RDID             | 1001 1111 | Read manufacturer JEDEC ID and product ID                           |

| Device ID read             | FAST_RDID        | 1001 1001 | Fast manufacturer JEDEC ID and product ID Read - SPI clock > 40 MHz |

| Reserved                   | - Reserved -     | 0001 1110 |                                                                     |

The SPI instructions in CY14X101PA are divided based on their functionality in these types:

- Status Register control instructions:

- □ Status Register access: RDSR, FAST\_RDSR and WRSR instructions

- □ Write protection and <u>bloc</u>k protection: WREN and WRDI instructions along with WP pin and WEN, BP0, and BP1 bits

- SRAM Read/Write instructions

- □ Memory access: READ, FAST\_READ, and WRITE instructions

- RTC Read/Write instructions

- □ RTC access: RDRTC, FAST\_RDRTC and WRTC instructions

- Special NV instructions

- □ nvSRAM special instructions: STORE, RECALL, ASENB, and ASDISB

- Special instructions: SLEEP, WRSN, RDSN, FAST\_RDSN, RDID, FAST\_RDID

#### Status Register

The Status Register bits <u>are listed in Table 2</u>. The Status Register consists of a Ready bit (RDY) and data protection bits BP1, BP0, WEN, and WPEN. The RDY bit can be polled to check the Ready/Busy status while a nvSRAM STORE or Software RECALL cycle is in progress. The Status Register can be modified by WRSR instruction and read by RDSR or FAST\_RDSR instruction. However, only the WPEN, BP1, and BP0 bits of the Status Register can be modified by using the WRSR instruction. The WRSR instruction has no effect on WEN and RDY bits. The default value shipped from the factory for WEN, BP0, BP1, bits 4–5, SNL and WPEN is '0'.

SNL (bit 6) of the Status Register is used to lock the serial number written using the WRSN instruction. The serial number can be written using the WRSN instruction multiple times while this bit is still '0'. When set to '1', this bit prevents any modification to the serial number. This bit is factory programmed to '0' and can only be written to once. After this bit is set to '1', it can never be cleared to '0'.

**Table 2. Status Register Format**

| Bit 7    | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0 |

|----------|---------|-------|-------|---------|---------|---------|-------|

| WPEN (0) | SNL (0) | X (0) | X (0) | BP1 (0) | BP0 (0) | WEN (0) | RDY   |

Table 3. Status Register Bit Definition

|             | •                        |                                                                                                                                                                            |

|-------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Definition               | Description                                                                                                                                                                |

| Bit 0 (RDY) | Ready                    | Read only bit indicates the ready status of device to perform a memory access. This bit is set to '1' by the device while a STORE or Software RECALL cycle is in progress. |

| Bit 1 (WEN) | Write Enable             | WEN indicates if the device is write enabled. This bit defaults to 0 (disabled) on power-up. WEN = '1'> Write enabled WEN = '0'> Write disabled                            |

| Bit 2 (BP0) | Block Protect bit '0'    | Used for block protection. For details see Table 4 on page 12.                                                                                                             |

| Bit 3 (BP1) | Block Protect bit '1'    | Used for block protection. For details see Table 4 on page 12.                                                                                                             |

| Bit 4-5     | Don't care               | These bits are non-writable and always return '0' upon read.                                                                                                               |

| Bit 6 (SNL) | Serial Number Lock       | Set to '1' for locking serial number                                                                                                                                       |

| Bit 7(WPEN) | Write Protect Enable bit | Used for enabling the function of Write Protect Pin (WP). For details see Table 5 on page 12.                                                                              |

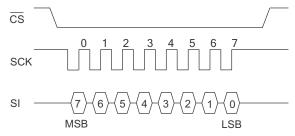

#### Read Status Register (RDSR) Instruction

The Read Status Register instruction provides access to the Status Register at SPI frequency up to 40 MHz. This instruction is used to probe the Write Enable status of the device or the Ready status of the device. RDY bit is set by the device to '1' whenever a STORE or Software RECALL cycle is in progress. The block protection and WPEN bits indicate the extent of protection employed.

This instruction is issued after the falling edge of CS using the opcode for RDSR.

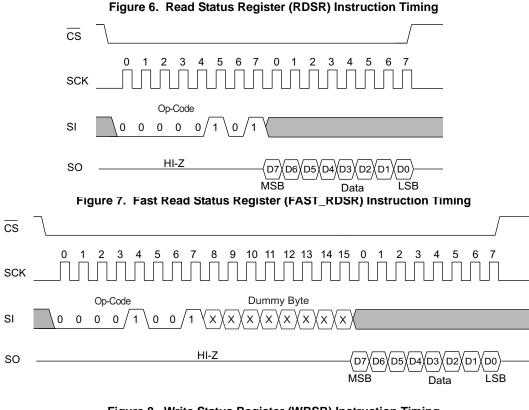

#### Fast Read Status Register (FAST\_RDSR) Instruction

The FAST\_RDSR instruction allows you to read the Status Register at SPI frequency above 40 MHz and up to 104 MHz (max). This instruction is used to probe the Write Enable status of the device or the Ready status of the device. RDY bit is set by the device to '1' whenever a STORE or Software RECALL cycle is in progress. The block protection and WPEN bits indicate the extent of protection employed.

This instruction is issued after the falling edge of  $\overline{\text{CS}}$  using the opcode for RDSR followed by a dummy byte.

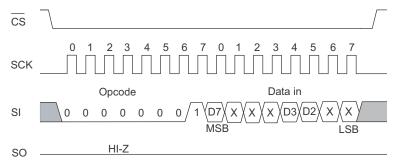

#### Write Status Register (WRSR) Instruction

The WRSR instruction enables the user to write to the Status Register. However, this instruction cannot be used to modify bit 0 (RDY), bit 1 (WEN) and bits 4–5. The BP0 and BP1 bits can be used to select one of four levels of block protection. Further, WPEN bit must be set to '1' to enable the use of Write Protect (WP) pin.

WRSR instruction is a write instruction and needs writes to be enabled (WEN bit set to '1') using the WREN instruction before it is issued. The instruction is issued after the falling edge of CS using the opcode for WRSR followed by eight bits of data to be stored in the Status Register. WRSR instruction can be used to modify only bits 2, 3, 6, and 7 of the Status Register.

**Note** In CY14X101PA, the values written to Status Register are saved to nonvolatile memory only after a STORE operation. If AutoStore is disabled, any modifications to the Status Register must be secured by performing a Software STORE operation.

Figure 8. Write Status Register (WRSR) Instruction Timing

#### Write Protection and Block Protection

CY14X101PA provides features for both software and hardware write protection using WRDI instruction and WP. Additionally, this device also provides block protection mechanism through BP0 and BP1 pins of the Status Register.

The write enable and disable status of the device is indicated by WEN bit of the Status Register. The write instructions (WRSR, WRITE, WRTC and WRSN) and nvSRAM special instruction (STORE, RECALL, ASENB, ASDISB) need the write to be enabled (WEN bit = '1') before they can be issued.

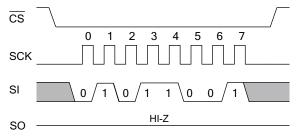

#### Write Enable (WREN) Instruction

On power-up, the device is always in the write disable state. The following WRITE, WRSR, WRTC, WRSN, or nvSRAM special instruction must therefore be preceded by a Write Enable instruction. If the device is not write enabled (WEN = '0'), it ignores the write instructions and returns to the standby state when CS is brought HIGH. A new CS falling edge is required to re-initiate serial communication. The instruction is issued following the falling edge of CS. When this instruction is used, the WEN bit of Status Register is set to '1'. WEN bit defaults to '0' on power-up.

**Note** After completion of a write instruction (WRSR, WRITE, WRTC or WRSN) or nvSRAM special instruction (STORE, RECALL, ASENB, ASDISB), the WEN bit is cleared to '0'. This provides protection from any inadvertent writes. Therefore, the WREN instruction must be used before a new write instruction can be issued.

Figure 9. WREN Instruction

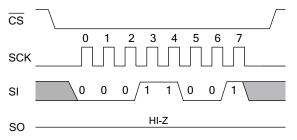

#### Write Disable (WRDI) Instruction

Write Disable instruction disables the write by clearing the WEN bit to '0' to protect the device against inadvertent writes. This instruction is issued following the falling edge of  $\overline{CS}$  followed by opcode for WRDI instruction. The WEN bit is cleared on the rising edge of  $\overline{CS}$  following a WRDI instruction.

Figure 10. WRDI Instruction

#### **Block Protection**

Block protection is provided using the BP0 and BP1 pins of the Status Register. These bits can be set using WRSR instruction and probed using the RDSR instruction. The nvSRAM is divided into four array segments. One-quarter, one-half, or all of the memory segments can be protected. Any data within the protected segment is read only. Table 4 shows the function of Block Protect bits.

Table 4. Block Write Protect Bits

| Level   | Status Register Bits |     | Array Addresses Protected |

|---------|----------------------|-----|---------------------------|

| Level   | BP1                  | BP0 | Array Addresses Protected |

| 0       | 0                    | 0   | None                      |

| 1 (1/4) | 0                    | 1   | 0x18000-0x1FFFF           |

| 2 (1/2) | 1                    | 0   | 0x10000-0x1FFFF           |

| 3 (AII) | 1                    | 1   | 0x00000-0x1FFFF           |

#### **Hardware Write Protection (WP Pin)**

The write <u>protect</u> pin (WP) is used to provide hardware write protection. WP pin enables <u>all normal</u> read and write operations when held HIGH. When the WP pin is brought LOW and WPEN bit is '1', all write operations to the Status Register are inhibited. The hardware write protection function is blocked when the WPEN bit is '0'. This allows you to install the device in a system with the WP pin tied to ground, and still write to the Status Register.

WP pin can be used along with WPEN and Block Protect bits (BP1 and BP0) of the Status Register to inhibit writes to memory. When WP pin is LOW and WPEN is set to '1', any modifications to Status Register are disabled. Therefore, the memory is protected by setting the BP0 and BP1 bits and the WP pin inhibits any modification of the Status Register bits, providing hardware write protection.

**Note** WP going LOW when  $\overline{CS}$  is still LOW has no effect on any of the ongoing write operations to the Status Register.

Table 5 summarizes all the protection features provided in the CY14X101PA.

**Table 5. Write Protection Operation**

| WPEN | WP   | WEN | Protected<br>Blocks | Unprotected Blocks | Status<br>Register |

|------|------|-----|---------------------|--------------------|--------------------|

| Х    | Х    | 0   | Protected           | Protected          | Protected          |

| 0    | Х    | 1   | Protected           | Writable           | Writable           |

| 1    | LOW  | 1   | Protected           | Writable           | Protected          |

| 1    | HIGH | 1   | Protected           | Writable           | Writable           |

#### **Memory Access**

All memory accesses are done using the READ and WRITE instructions. These instructions cannot be used while a STORE or RECALL cycle is in progress. A STORE cycle in progress is indicated by the RDY bit of the Status Register and the HSB pin.

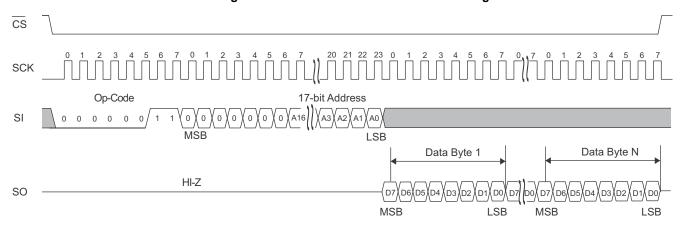

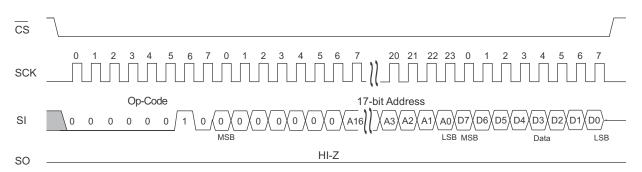

#### Read Sequence (READ) Instruction

The read operations on CY14X101PA are performed by giving the instruction on the SI pin and reading the output on SO pin. The following sequence needs to be followed for a read operation: After the CS line is pulled LOW to select a device, the read opcode is transmitted through the SI line followed by three bytes of address. The most significant address byte contains A16 in bit 0 and other bits as don't cares. Address bits A15 to A0 are sent in the following two address bytes. After the last address bit is transmitted on the SI pin, the data (D7–D0) at the specific address is shifted out on the SO line on the falling edge of SCK starting with D7. Any other data on SI line after the last address bit is ignored.

CY14X101PA allows reads to be performed in bursts through SPI which can be used to read consecutive addresses without issuing a new READ instruction. If only one byte is to be read, the CS line must be driven HIGH after one byte of data comes out. However, the read sequence may be continued by holding the CS line LOW and the address is automatically incremented and data continues to shift out on SO pin. When the last data memory address (0x1FFFF) is reached, the address rolls over to 0x00000 and the device continues to read.

**Note** READ instruction operates up to Max of 40 MHz SPI frequency.

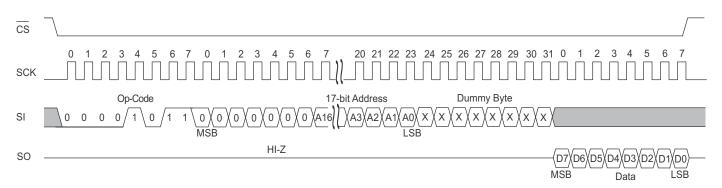

#### Fast Read Sequence (FAST\_READ) Instruction

The FAST\_READ instruction allows you to read memory at SPI frequency above 40 MHz and up to 104 MHz (Max). The host system must first select the device by driving CS LOW, the FAST\_READ instruction is then written to SI, followed by 3 address byte containing the17 bit address (A16–A0) and then a dummy byte.

From the subsequent falling edge of the SCK, the data of the specific address is shifted out serially on the SO line starting with MSB. The first byte specified can be at any location. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single FAST\_READ instruction. When the highest address in the memory array is reached, address counter rolls over to start address 0x00000 and thus allowing the read sequence to continue indefinitely. The FAST\_READ instruction is terminated by driving CS HIGH at any time during data output.

**Note** FAST\_READ instruction operates up to maximum of 104 MHz SPI frequency.

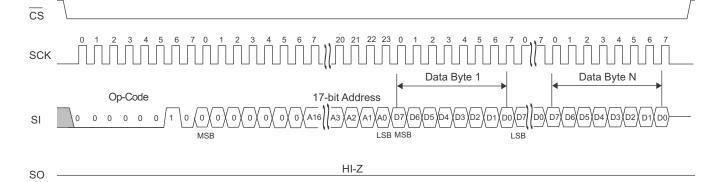

#### Write Sequence (WRITE) Instruction

The write operations on CY14X101PA are performed through the SI pin. To perform a write operation, if the device is write disabled, then the device must first be write enabled through the WREN instruction. When the writes are enabled (WEN  $\underline{=}$  '1'), WRITE instruction is issued after the falling edge of  $\overline{\text{CS}}$ . A WRITE instruction constitutes transmitting the WRITE opcode on SI line followed by 3-bytes of address and the data (D7–D0)

which is to be written. The most significant address byte contains A16 in bit 0 with other bits being don't cares. Address bits A15 to A0 are sent in the following two address bytes.

CY14X101PA allows writes to be performed in bursts through SPI which can be used to write consecutive addresses without issuing a new WRITE instruction. If only one byte is to be written, the CS line must be driven HIGH after the D0 (LSB of data) is transmitted. However, if more bytes are to be written, CS line must be held LOW and address incremented automatically. The following bytes on the SI line are treated as data bytes and written in the successive addresses. When the last data memory address (0x1FFFF) is reached, the address rolls over to 0x00000 and the device continues to write.

The WEN bit is reset to '0' on completion of a WRITE sequence.

**Note** When a burst write reaches a protected block address, it continues the address increment into the protected space but does not write any data to the protected memory. If the address roll over takes the burst write to unprotected space, it resumes writes. The same operation is true if a burst write is initiated within a write protected block.

MSB

Figure 11. Read Instruction Timing

LSB

Data

#### Figure 13. Fast Read Instruction Timing

Figure 14. Write Instruction Timing

Figure 15. Burst Mode Write Instruction Timing

#### RTC Access

CY14X101PA uses 16 registers for RTC. These registers can be read out or written to by accessing all 16 registers in burst mode or accessing each register, one at a time. The RDRTC, FAST\_RDRTC, and WRTC instructions are used to access the RTC.

All the RTC registers can be read in burst mode by issuing the RDRTC and FAST\_RDRTC instruction and reading all 16 bytes without bringing the CS pin HIGH. The 'R' bit must be set while reading the RTC timekeeping registers to ensure that transitional values of time are not read.

Writes to the RTC register are performed using the WRTC instruction. Writing RTC timekeeping registers and control registers, except for the flags register needs the 'W' bit of the flags register to be set to '1'. The internal counters are updated with the new date and time setting when the 'W' bit is cleared to '0'. All the RTC registers can also be written in burst mode using the WRTC instruction.

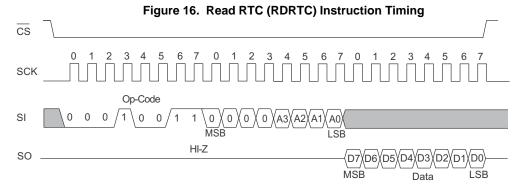

#### **READ RTC (RDRTC) Instruction**

Read RTC (RDRTC) instruction allows you to read the contents of RTC registers at SPI frequency upto 25 MHz. Reading the RTC registers through the SO pin requires the following sequence: After the CS line is pulled LOW to select a device, the RDRTC opcode is transmitted through the SI line followed by eight address bits for selecting the register. Any data on the SI line after the address bits is ignored. The data (D7–D0) at the specified address is then shifted out onto the SO line. RDRTC also allows burst mode read operation. When reading multiple bytes from RTC registers, the address rolls over to 0x00 after the last RTC register address (0x0F) is reached.

The 'R' bit in RTC flags register must be set to '1' before reading RTC time keeping registers to avoid reading transitional data. Modifying the RTC flag registers requires a Write RTC cycle. The R bit must be cleared to '0' after completion of the read operation.

The easiest way to read RTC registers is to perform RDRTC in burst mode. The read may start from the first RTC register (0x00) and the CS must be held LOW to allow the data from all 16 RTC registers to be transmitted through the SO pin.

**Note** RDRTC instruction operates at a maximum clock frequency of 25 MHz. The opcode cycles, address cycles and data out cycles need to run at 25 MHz for the instruction to work properly.

#### Fast Read Sequence (FAST\_RDRTC) Instruction

The FAST\_RDRTC instruction allows you to read memory at a SPI frequency above 25 MHz and up to 104 MHz (Max). The host system must first select the device by driving CS LOW, the FAST\_READ instruction is then written to SI, followed by 8 bit address and a dummy byte.

From the subsequent falling edge of the SCK, the data of the specific address is shifted out serially on the SO line starting with MSB. The first byte specified can be at any location. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single FAST\_RDRTC instruction. When the highest address (0x0F) in the memory array is reached, the address counter rolls over to start address 0x00 and thus allowing the read sequence to continue indefinitely. The FAST\_RDRTC instruction is terminated by driving CS HIGH at any time during data output.

**Note** FAST\_READ instruction operates up to Max of 104 MHz SPI frequency.

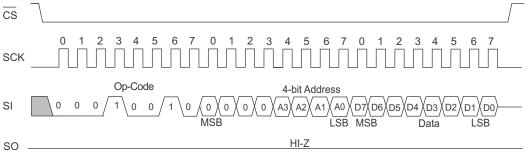

#### WRITE RTC (WRTC) Instruction

WRITE RTC (WRTC) instruction allows you to modify the contents of RTC registers. The WRTC instruction requires the WEN bit to be set to '1' before it can be issued. If WEN bit is '0', a WREN instruction needs to be issued before using WRTC. Writing RTC registers requires the following sequence: After the CS line is pulled LOW to select a device, WRTC opcode is transmitted through the SI line followed by eight address bits identifying the register which is to be written to and one or more

bytes of data. WRTC allows burst mode write operation. When writing more than one registers in burst mode, the address rolls over to 0x00 after the last RTC address (0x0F) is reached.

Note that writing to RTC timekeeping and control registers require the W bit to be set to '1'. The values in these RTC registers take effect only after the 'W' bit is cleared to '0'. Write Enable bit (WEN) is automatically cleared to '0' after completion of the WRTC instruction.

Figure 18. Write RTC (WRTC) Instruction Timing

#### **nvSRAM Special Instructions**

CY14X101PA provides four special instructions that allow access to the nvSRAM specific functions: STORE, RECALL, ASDISB, and ASENB. Table 6 lists these instructions.

Table 6. nvSRAM Special Instructions

| Function Name | Opcode    | Operation         |

|---------------|-----------|-------------------|

| STORE         | 0011 1100 | Software STORE    |

| RECALL        | 0110 0000 | Software RECALL   |

| ASENB         | 0101 1001 | AutoStore Enable  |

| ASDISB        | 0001 1001 | AutoStore Disable |

#### Software STORE (STORE) Instruction

When a STORE instruction is executed, CY14X101PA performs a Software STORE operation. The STORE operation is performed regardless of whether or not a write has taken place since the last STORE or RECALL operation.

Figure 19. Software STORE Operation

To issue this instruction, the device must be write enabled (WEN bit = '1'). The instruction is performed by transmitting the STORE opcode on the SI pin following the falling edge of CS. The WEN

bit is cleared on the positive edge of  $\overline{\text{CS}}$  following the STORE instruction.

#### Software RECALL (RECALL) Instruction

When a RECALL instruction is executed, CY14X101PA performs a Software RECALL operation. To issue this instruction, the device must be write enabled (WEN = '1').

The instruction is performed by transmitting the RECALL opcode on the SI pin following the falling edge of CS. The WEN bit is cleared on the positive edge of CS following the RECALL instruction.

Figure 20. Software RECALL Operation

#### AutoStore Enable (ASENB) Instruction

The AutoStore Enable instruction enables the AutoStore on CY14X101PA. This setting is not nonvolatile and needs to be followed by a STORE sequence if this is desired to survive the power cycle.

To issue this instruction, the device must be write enabled (WEN = '1'). The instruction is performed by transmitting the ASENB opcode on the SI pin following the falling edge of  $\overline{CS}$ . The WEN bit is cleared on the positive edge of  $\overline{CS}$  following the ASENB instruction.

Figure 21. AutoStore Enable Operation

#### AutoStore Disable (ASDISB) Instruction

AutoStore is enabled by default in CY14X101PA. The AutoStore Disable instruction disables the AutoStore on CY14X101PA. This setting is not nonvolatile and needs to be followed by a STORE sequence if this is desired to survive the power cycle.

To issue this instruction, the device must be write enabled (WEN = '1'). The instruction is performed by transmitting the ASDISB opcode on the SI pin following the falling edge of CS. The WEN bit is cleared on the positive edge of CS following the ASDISB instruction.

Figure 22. AutoStore Disable Operation

#### **Special Instructions**

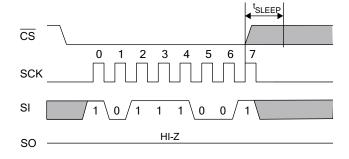

#### **SLEEP Instruction**

SLEEP instruction puts the nvSRAM in sleep mode. When the SLEEP instruction is issued, the nvSRAM takes  $t_{SS}$  time to process the SLEEP request. Once the SLEEP command is successfully registered and processed, the nvSRAM toggles HSB low, performs a STORE operation to secure the data to nonvolatile memory and then enters into SLEEP mode. The device starts consuming  $I_{ZZ}$  current after  $t_{SLEEP}$  time from the instance when SLEEP instruction is registered. The device is not accessible for normal operations after SLEEP instruction is issued. Once in sleep mode, the SCK and SI pins are ignored and SO will be Hi-Z but device continues to monitor the CS pin.

To wake the nvSRAM from the sleep mode, the device must be selected by toggling the  $\overline{\text{CS}}$  pin from HIGH to LOW. The device wakes up and is accessible for normal operations after t<sub>WAKE</sub> duration after a falling edge of  $\overline{\text{CS}}$  pin is detected.

**Note** Whenever nvSRAM enters into sleep mode, it initiates nonvolatile STORE cycle which results in an endurance cycle per sleep command execution. A STORE cycle starts only if a write to the SRAM has been performed since the last STORE or RECALL cycle.

Figure 23. Sleep Mode Entry

#### **Serial Number**

The serial number is an 8-byte programmable memory space provided to you to uniquely identify this device. It typically consists of a two byte Customer ID, followed by five bytes of unique serial number and one byte of CRC check. However, nvSRAM does not calculate the CRC and it is up to the system designer to utilize the eight byte memory space in whatever manner desired. The default value for eight-byte locations are set to '0x00'.

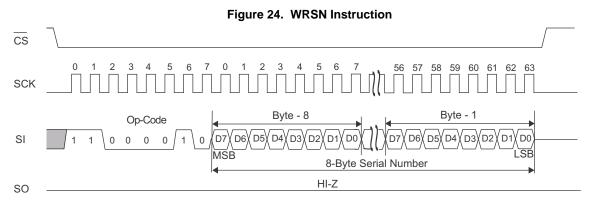

#### **WRSN (Serial Number Write) Instruction**

The serial number can be written using the WRSN instruction. To write serial number the write must be enabled using the WREN instruction. The WRSN instruction can be used in burst mode to write all the 8 bytes of serial number.

The serial number is locked using the SNL bit of the Status Register. Once this bit is set to '1', no modification to the serial number is possible. After the SNL bit is set to '1', using the WRSN instruction has no effect on the serial number.

A STORE operation (AutoStore or Software STORE) is required to store the serial number in nonvolatile memory. If AutoStore is disabled, you must perform a Software STORE operation to secure and lock the serial number. If SNL bit is set to '1' and is not stored (AutoStore disabled), the SNL bit and serial number defaults to '0' at the next power cycle. If SNL bit is set to '1' and is stored, the SNL bit can never be cleared to '0'. This instruction requires the WEN bit to be set before it can be executed. The WEN bit is reset to '0' after completion of this instruction.

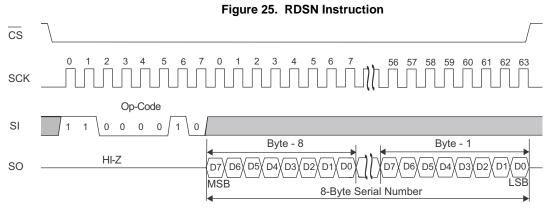

#### **RDSN (Serial Number Read) Instruction**

The serial number is read using RDSN instruction at SPI frequency upto 40 MHz. A serial number read may be performed in burst mode to read all the eight bytes at once. After the last byte of serial number is read, the <u>device</u> does not loop back. RDSN instruction can be issued by shifting the op-code for RDSN in through the SI pin of nvSRAM after CS goes LOW. This is followed by nvSRAM shifting out the eight bytes of serial number through the SO pin.

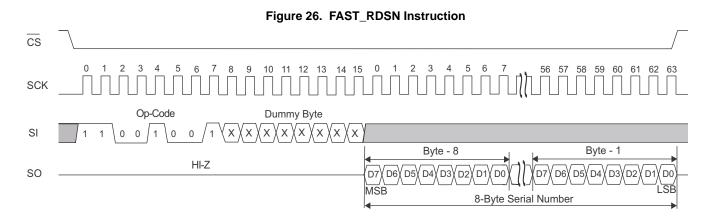

#### FAST RDSN (Fast Serial Number Read) Instruction

The FAST\_RDSN instruction is used to read serial number at SPI frequency above 40 MHz and up to 104 MHz (max). A serial number read may be performed in burst mode to read all the eight bytes at once. After the last byte of serial number is read, the device does not loop back. FAST\_RDSN instruction can be issued by shifting the op-code for FAST\_RDSN in through the SI pin of nvSRAM followed by dummy byte after CS goes LOW. This is followed by nvSRAM shifting out the eight bytes of serial number through the SO pin.

#### **Device ID**

Device ID is a 4-byte read only code identifying a type of product uniquely. This includes the product family code, configuration, and density of the product.

Table 7. Device ID

|            |                        | Device ID Description |                   |                 |                 |  |

|------------|------------------------|-----------------------|-------------------|-----------------|-----------------|--|

| Device     | Device ID<br>(4 bytes) | 31–21<br>(11 bits)    | 20–7<br>(14 bits) | 6–3<br>(4 bits) | 2–0<br>(3 bits) |  |

|            |                        | Manufacturer ID       | Product ID        | Density ID      | Die Rev         |  |

| CY14C101PA | 0x0681C0A0             | 00000110100           | 00001110000001    | 0100            | 000             |  |

| CY14B101PA | 0x0681C8A0             | 00000110100           | 00001110010001    | 0100            | 000             |  |

| CY14E101PA | 0x0681D0A0             | 00000110100           | 00001110100001    | 0100            | 000             |  |

The device ID is divided into four parts as shown in Table 7:

1. Manufacturer ID (11 bits)

This is the JEDEC assigned manufacturer ID for Cypress. JEDEC assigns the manufacturer ID in different banks. The first three bits of the manufacturer ID represent the bank in which ID is assigned. The next eight bits represent the manufacturer ID.

Cypress's manufacturer ID is 0x34 in bank 0. Therefore the manufacturer ID for all Cypress nvSRAM products is:

Cypress ID - 000\_0011\_0100

2. Product ID (14 bits)

The product ID for device is shown in the Table 7.

3. Density ID (4 bits)

The 4-bit density ID is used as shown in Table 7 for indicating the 1Mb density of the product.

4. Die Rev (3 bits)

This is used to represent any major change in the design of the product. The initial setting of this is always 0x0.

#### **RDID (Device ID Read) Instruction**

This instruction is used to read the JEDEC assigned manufacturer ID and product ID of the device at SPI frequency upto 40 MHz. This instruction can be used to identify a device on the bus. RDID instruction can be issued by shifting the op-code for RDID in through the SI pin of nvSRAM after CS goes LOW. This is followed by nvSRAM shifting out the four bytes of device ID through the SO pin.

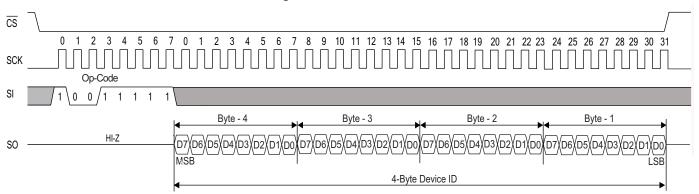

Figure 27. RDID Instruction

#### FAST\_RDID (Fast Device ID Read) Instruction

The FAST\_RDID instruction allows you to read the JEDEC assigned manufacturer ID and product ID at SPI frequency above 40 MHz and up to 104 MHz (Max). FAST\_RDID instruction can be issued by shifting the op-code for FAST\_RDID in through the SI pin of nvSRAM followed by dummy byte after CS goes LOW. This is followed by nvSRAM shifting out the four bytes of device ID through the SO pin.

CS 0 4 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 11 12 3 5 Dummy Byte Op-Code Byte - 4 Byte - 2 Byte - 3 Byte - 1 HI-Z 4-Byte Device ID

Figure 28. FAST\_RDID Instruction

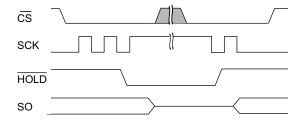

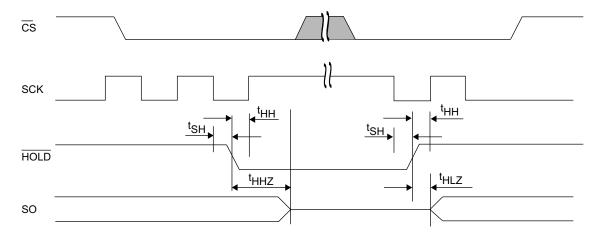

### **HOLD** Pin Operation

The HOLD pin is used to pause the serial communication. When the device is selected and a serial sequence is underway, HOLD is used to pause the serial communication with the master device without resetting the ongoing serial sequence. To pause, the HOLD pin must be brought LOW when the SCK pin is LOW. To resume serial communication, the HOLD pin must be brought HIGH when the SCK pin is LOW (SCK may toggle during HOLD). While the device serial communication is paused, inputs to the SI pin are ignored and the SO pin is in the high-impedance state.

This pin can be used by the master with the  $\overline{\text{CS}}$  pin to pause the serial communication by bringing the pin  $\overline{\text{HOLD}}$  LOW and deselecting an SPI slave to establish communication with another slave device, without the serial communication being reset. The communication may be resumed at a later point by selecting the device and setting the  $\overline{\text{HOLD}}$  pin HIGH.

Figure 29. HOLD Operation

#### **Real Time Clock Operation**

#### nvTIME Operation

The CY14X101PA offers internal registers that contain clock, alarm, watchdog, interrupt, and control functions. The RTC registers occupy a separate address space from nvSRAM and are accessible through the Read RTC register and Write RTC register sequence on register addresses 0x00 to 0x0F. Internal double buffering of the time keeping registers prevents accessing transitional internal clock data during a read or write operation. Double buffering also circumvents disrupting normal timing counts or the clock accuracy of the internal clock when accessing clock data. Clock and alarm registers store data in BCD format.

#### **Clock Operations**

The clock registers maintain time up to 9,999 years in one-second increments. The time can be set to any calendar time and the clock automatically keeps track of days of the week and month, leap years, and century transitions. There are eight registers dedicated to the clock functions, which are used to set time with a write cycle and to read time with a read cycle. These registers contain the time of day in BCD format. Bits defined as '0' are currently not used and are reserved for future use by Cypress.

#### Reading the Clock

The double-buffered RTC register structure reduces the chance of reading incorrect data from the clock. Internal updates to the CY14X101PA time keeping registers are stopped when the read bit 'R' (in the flags register at 0x00) is set to '1' before reading clock data to prevent reading of data in transition. Stopping the register updates does not affect clock accuracy.

When a read sequence of RTC device is initiated, the update of the user timekeeping registers stops and does not restart until a '0' is written to the read bit 'R' (in the flags register at 0x00). After the end of read sequence, all the RTC registers are simultaneously updated within 20 ms.

#### Setting the Clock

A write access to the RTC device stops updates to the time keeping registers and enables the time to be set when the write bit 'W' (in the flags register at 0x00) is set to '1'. The correct day, date, and time is then written into the registers and must be in 24 hour BCD format. The time written is referred to as the "Base Time". This value is stored in nonvolatile registers and used in the calculation of the current time. When the write bit 'W' is cleared by writing '0' to it, the values of timekeeping registers are transferred to the actual clock counters after which the clock resumes normal operation.

If the time written to the timekeeping registers is not in the correct BCD format, each invalid nibble of the RTC registers continue counting to 0xF before rolling over to 0x0 after which RTC resumes normal operation.

**Note** After the 'W' bit is set to '0', values written into the timekeeping, alarm, calibration, and interrupt registers are transferred to the RTC time keeping counters in  $t_{\text{RTCp}}$  time. These counter values must be saved to nonvolatile memory either by initiating a Software/Hardware STORE or AutoStore operation. While working in AutoStore disabled mode, perform a STORE

operation after  $t_{\text{RTCp}}$  time while writing into the RTC registers for the modifications to be correctly recorded.

#### **Backup Power**

The RTC in the CY14X101PA is intended for permanently powered operation. The  $V_{RTCcap}$  or  $V_{RTCbat}$  pin is connected depending on whether a capacitor or battery is chosen for the application. When the primary power,  $V_{CC}$ , fails and drops below  $V_{SWITCH}$  the device switches to the backup power supply.

The clock oscillator uses very little current, which maximizes the backup time available from the backup source. Regardless of the clock operation with the primary source removed, the data stored in the nvSRAM is secure, having been stored in the nonvolatile elements when power was lost.

During backup operation, the CY14X101PA consumes a  $0.45~\mu A$  (Typ) at room temperature. The user must choose capacitor or battery values according to the application.

Backup time values based on maximum current specifications are shown in the following Table 8. Nominal backup times are approximately two times longer.

Table 8. RTC Backup Time

| Capacitor Value | Backup Time<br>(CY14B101PA) |

|-----------------|-----------------------------|

| 0.1 F           | 60 hours                    |

| 0.47 F          | 12 days                     |

| 1.0 F           | 25 days                     |