# SPI Power Controller

SPOC - BTS5460SF

For Advanced Front Light Control

**Data Sheet**

Rev. 1.0, 2010-04-12

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

| 1                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 4                                          |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <b>2</b><br>2.1                             | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| <b>3</b><br>3.1<br>3.2                      | Pin Configuration         Pin Assignment SPOC - BTS5460SF         Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                 | . 8                                          |

| <b>4</b><br>4.1<br>4.2                      | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                           |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4        | Power Supply Power Supply Modes Reset Electrical Characteristics Command Description                                                                                                                                                                                                                                                                                                                                                                                                            | 13<br>14<br>15                               |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Power Stages Output ON-State Resistance Input Circuit Power Stage Output Inverse Current Behavior Electrical Characteristics Command Description                                                                                                                                                                                                                                                                                                                                                | 17<br>17<br>19<br>20<br>21                   |

| 7 7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.8 7.9 7.10  | $\begin{array}{c} \textbf{Protection Functions} \\ \textbf{Over Current Protection} \\ \textbf{Over Current Protection at high } V_{\text{DS}} \\ \textbf{Over Current Protection for Short Circuit Type 2 Protection} \\ \textbf{Over Temperature Protection} \\ \textbf{Reverse Polarity Protection} \\ \textbf{Over Voltage Protection} \\ \textbf{Loss of Ground} \\ \textbf{Loss of } V_{\text{BB}} \\ \textbf{Electrical Characteristics} \\ \textbf{Command Description} \\ \end{array}$ | 26<br>28<br>29<br>31<br>31<br>32<br>32<br>33 |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | Diagnosis  Diagnosis Word at SPI  Load Current Sense Diagnosis  Switch Bypass Diagnosis  Open Load in OFF-State  Electrical Characteristics  Command Description                                                                                                                                                                                                                                                                                                                                | 37<br>37<br>39<br>40<br>41                   |

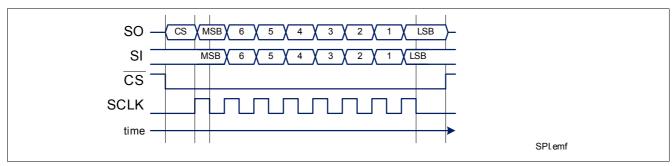

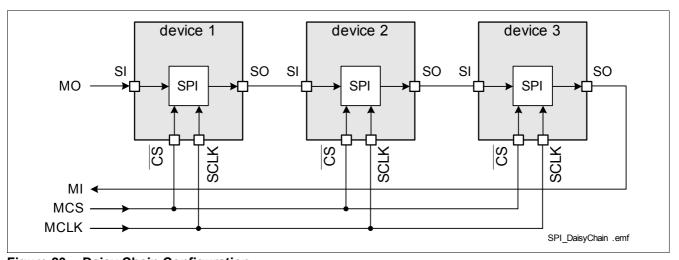

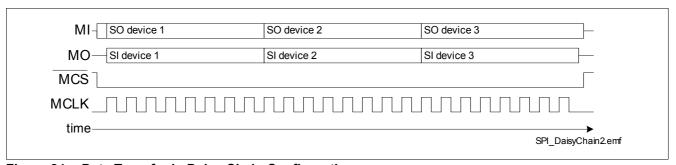

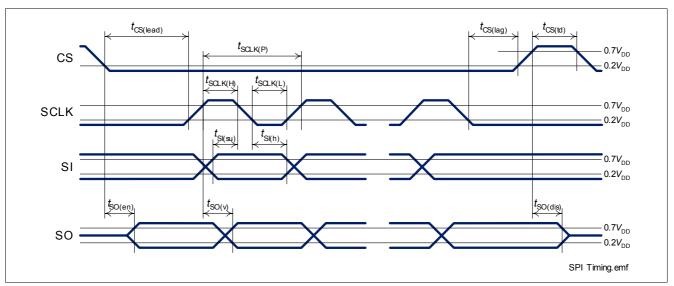

| 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6 | Serial Peripheral Interface (SPI)  SPI Signal Description  Daisy Chain Capability  Timing Diagrams  Electrical Characteristics  SPI Protocol 8 Bit  Register Overview                                                                                                                                                                                                                                                                                                                           | 46<br>47<br>48<br>49                         |

# SPOC - BTS5460SF

|    | Table of Conte                    | nts |

|----|-----------------------------------|-----|

| 10 | Application Description           | 55  |

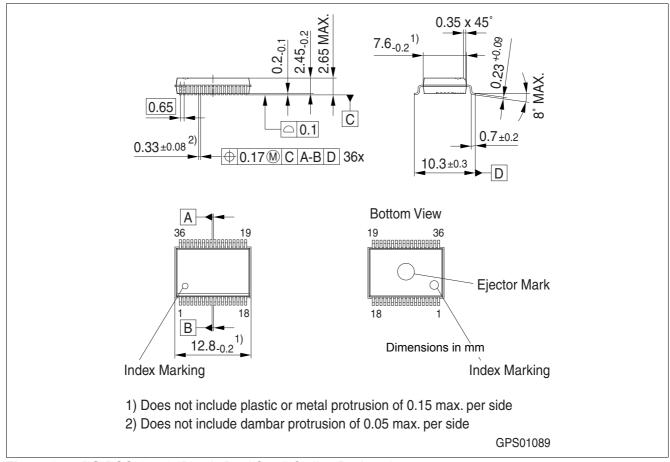

| 11 | Package Outlines SPOC - BTS5460SF | 56  |

| 12 | Revision History                  | 57  |

3 **Data Sheet** Rev. 1.0, 2010-04-12

# For Advanced Front Light Control SPI Power Controller

SPOC - BTS5460SF

### 1 Overview

#### **Features**

- · 8 bit serial peripheral interface for control and diagnosis

- 3.3 V and 5 V compatible logic pins

- · Very low stand-by current

- Enhanced electromagnetic compatibility (EMC) for bulbs as well as LEDs with increased slew rate

- · Stable behavior at under voltage

- Device ground independent from load ground

- · Green Product (RoHS-Compliant)

- AEC Qualified

PG-DSO-36-43

#### **Description**

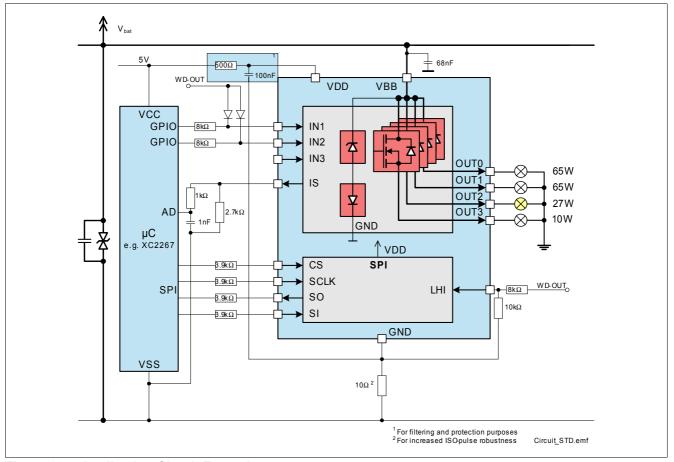

The SPOC - BTS5460SF is a four channel high-side smart power switch in PG-DSO-36-43 package providing embedded protective functions. It is especially designed to control standard exterior lighting in automotive applications. In order to use the same hardware, the device can be configured to bulb or LED mode for channel 2 and channel 3. As a result, both load types are optimized in terms of switching and diagnosis behavior.

It is specially designed to drive exterior lamps up to 65W, 27W and 10W and HIDL.

#### **Product Summary**

| Operating Voltage Power Switch                      |                              | $V_{BB}$                                    | 4.5 28 V                           |

|-----------------------------------------------------|------------------------------|---------------------------------------------|------------------------------------|

| Logic Supply Voltage                                |                              | $V_{DD}$                                    | 3.0 5.5 V                          |

| Supply Voltage for Load Dump Protection             |                              | $V_{BB(LD)}$                                | 40 V                               |

| Maximum Stand-By Current at 25 °C                   |                              | $I_{BB(STB)}$                               | 4.5 μΑ                             |

| Typical On-State Resistance at $T_{\rm j}$ = 25 °C  | channel 0, 1<br>channel 2, 3 | $R_{DS(ON,typ)}$                            | $3.5~\text{m}\Omega$ 11 m $\Omega$ |

| Maximum On-State Resistance at $T_{\rm j}$ = 150 °C | channel 0, 1<br>channel 2, 3 | $R_{\mathrm{DS}(\mathrm{ON},\mathrm{max})}$ | 9 mΩ<br>28 mΩ                      |

| SPI Access Frequency                                |                              | $f_{\sf SCLK(max)}$                         | 5 MHz                              |

| Туре             | Package      | Marking   |

|------------------|--------------|-----------|

| SPOC - BTS5460SF | PG-DSO-36-43 | BTS5460SF |

Data Sheet 4 Rev. 1.0, 2010-04-12

Overview

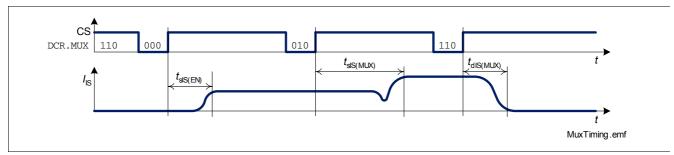

Configuration and status diagnosis are done via SPI. The SPI is daisy chain capable. The device provides a current sense signal per channel that is multiplexed to the diagnosis pin IS. It can be enabled and disabled via SPI commands. An over load and over temperature flag is provided in the SPI diagnosis word. A multiplexed switch bypass monitor provides short-circuit to  $V_{\rm BB}$  diagnosis. In OFF state a current source can be switched to the output of one selected channel in order to detect an open load.

The SPOC - BTS5460SF provides a fail-safe feature via limp home input pin.

The power transistors are built by N-channel vertical power MOSFETs with charge pumps.

#### **Protective Functions**

- · Reverse battery protection with external components

- Reversave<sup>™</sup> Reverse battery protection by self turn on of all channels

- · Short circuit protection

- Over load protection

- Thermal shutdown with latch and dynamic temperature sensor

- · Over current tripping

- Over voltage protection

- · Loss of ground protection

- Electrostatic discharge protection (ESD)

#### **Diagnostic Functions**

- Multiplexed proportional load current sense signal (IS)

- Enable function for current sense signal configurable via SPI

- High accuracy of current sense signal at wide load current range

- Current sense ratio (k<sub>ILIS</sub>) configurable for LEDs or bulbs for channel 2 and 3

- · Very fast diagnosis in LED mode

- · Feedback on over temperature and over load via SPI

- Multiplexed switch bypass monitor provides short circuit to  $V_{\mathrm{BB}}$  detection

- Integrated, in two steps programmable current source for open load in OFF-state detection

#### **Application Specific Functions**

Fail-safe activation via LHI pin

#### **Applications**

- High-side power switch for 12 V grounded loads in automotive applications

- Especially designed for standard exterior lighting like high beam, low beam, indicator, parking light and equivalent LEDs

- · Load type configuration via SPI (bulbs or LEDs) for optimized load control

- Replaces electromechanical relays, fuses and discrete circuits

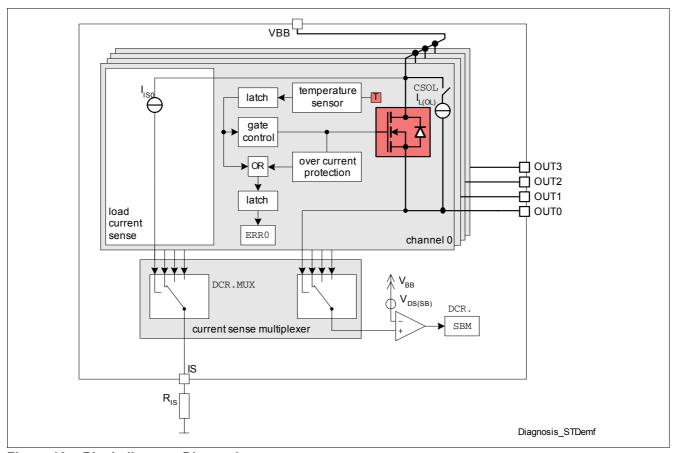

**Block Diagram**

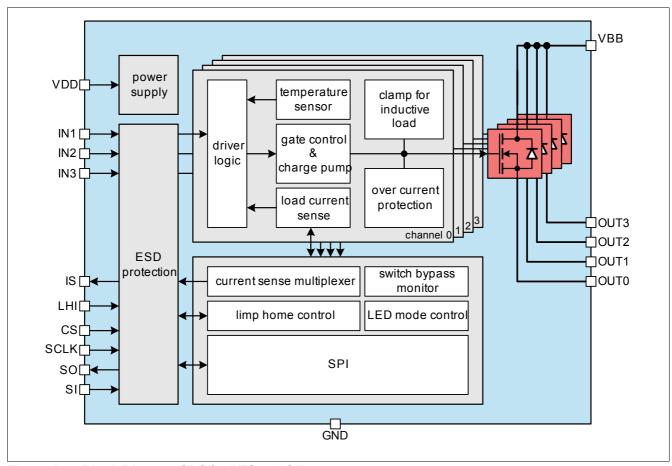

# 2 Block Diagram

Figure 1 Block Diagram SPOC - BTS5460SF

**Block Diagram**

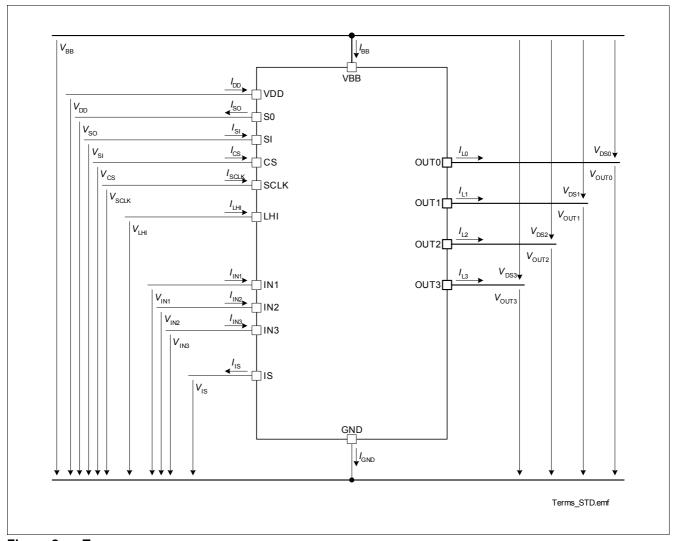

# 2.1 Terms

Figure 2 shows all terms used in this data sheet.

Figure 2 Terms

In all tables of electrical characteristics is valid: Channel related symbols without channel number are valid for each channel separately (e.g.  $V_{\rm DS}$  specification is valid for  $V_{\rm DS0}$  ...  $V_{\rm DS3}$ ).

All SPI register bits are marked as follows: ADDR.PARAMETER (e.g. HWCR.CL). In SPI register description, the values in bold letters (e.g. 0) are default values.

**Pin Configuration**

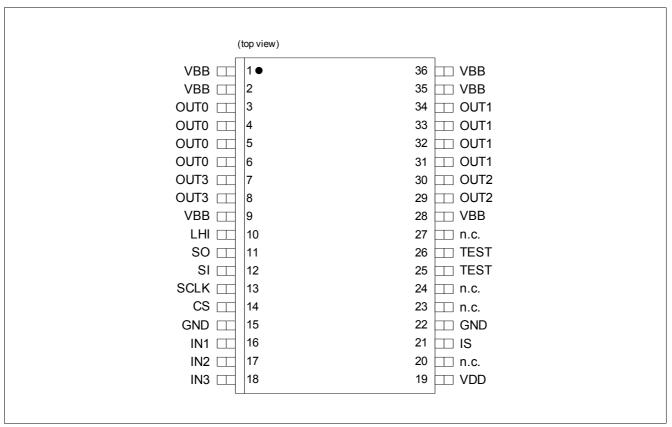

# 3 Pin Configuration

# 3.1 Pin Assignment SPOC - BTS5460SF

Figure 3 Pin Configuration PG-DSO-36-43

**Pin Configuration**

# 3.2 Pin Definitions and Functions

| Pin                               | Symbol         | I/O    | Function                                                      |

|-----------------------------------|----------------|--------|---------------------------------------------------------------|

| Power Supply Pins                 | !              |        |                                                               |

| 1, 2, 9, 28, 35, 36 <sup>1)</sup> | VBB            | _      | Positive power supply for high-side power switch              |

| 19                                | VDD            | _      | Logic supply (5 V)                                            |

| 15, 22                            | GND            | _      | Ground connection                                             |

| Parallel Input Pins (int          | tegrated pull- | down   | , leave unused pins unconnected)                              |

| 16                                | IN1            | I      | Input signal of channel 1 (high active)                       |

| 17                                | IN2            | I      | Input signal of channel 2 (high active)                       |

| 18                                | IN3            | I      | Input signal of channel 3 (high active)                       |

| Power Output Pins                 |                | •      |                                                               |

| 3, 4, 5, 6 <sup>2)</sup>          | OUT0           | 0      | Protected high-side power output of channel 0                 |

| 31, 32, 33, 34 <sup>2)</sup>      | OUT1           | 0      | Protected high-side power output of channel 1                 |

| 29, 30 <sup>2)</sup>              | OUT2           | 0      | Protected high-side power output of channel 2                 |

| 7, 8 <sup>2)</sup>                | OUT3           | 0      | Protected high-side power output of channel 3                 |

| SPI & Diagnosis Pins              |                |        |                                                               |

| 14                                | CS             | I      | Chip select of SPI interface (low active); Integrated pull up |

| 13                                | SCLK           | I      | Serial clock of SPI interface                                 |

| 12                                | SI             | I      | Serial input of SPI interface (high active)                   |

| 11                                | SO             | 0      | Serial output of SPI interface                                |

| 21                                | IS             | 0      | Current sense output signal                                   |

| Limp Home Pin (integ              | rated pull-do  | wn, pı | ull-down resistor recommended)                                |

| 10                                | LHI            | I      | Limp home activation signal (high active)                     |

| Not connected Pins                | 1              | 1      |                                                               |

| 20, 23, 24, 27                    | n.c.           | _      | not connected, internally not bonded                          |

| 25, 26                            | TEST           | -      | Test pins, internally bonded and pulled down, do not connect  |

<sup>1)</sup> All VBB pins have to be connected.

<sup>2)</sup> All outputs pins of each channel have to be connected.

**Electrical Characteristics**

# 4 Electrical Characteristics

# 4.1 Absolute Maximum Ratings

# Absolute Maximum Ratings 1)

$T_{\rm j}$  = -40 to +150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.    | Parameter                                                    | Symbol                 |               | it Values          | Unit | Conditions                                                                 |  |

|---------|--------------------------------------------------------------|------------------------|---------------|--------------------|------|----------------------------------------------------------------------------|--|

|         |                                                              |                        | min.          | max.               |      |                                                                            |  |

| Supply  | y Voltage                                                    |                        |               |                    | *    |                                                                            |  |

| 4.1.1   | Power supply voltage                                         | $V_{BB}$               | -0.3          | 28                 | V    | _                                                                          |  |

| 4.1.2   | Logic supply voltage                                         | $V_{DD}$               | -0.3          | 5.5                | V    | _                                                                          |  |

| 4.1.3   | Reverse polarity voltage according Figure 26                 | -V <sub>bat(rev)</sub> | _             | 16                 | V    | $T_{\text{jStart}}$ = 25 °C $t \le 2 \text{ min.}^{2}$                     |  |

| 4.1.4   | Supply voltage for short circuit protection (single pulse)   | $V_{\mathrm{BB(SC)}}$  |               |                    | V    | $R_{\text{ECU}} = 20 \text{ m}\Omega$<br>$l = 0 \text{ or 5 m}^{3)}$       |  |

|         | channel 0, 1                                                 |                        | 0             | 24                 |      | $R_{\text{Cable}}$ = 6 m $\Omega$ /m $L_{\text{Cable}}$ = 1 $\mu$ H/m      |  |

|         | channel 2, 3                                                 |                        | 0             | 24                 |      | $R_{\mathrm{Cable}}$ = 16 m $\Omega$ /m $L_{\mathrm{Cable}}$ = 1 $\mu$ H/m |  |

| 4.1.5   | Supply voltage for load dump protection with connected loads | $V_{BB(LD)}$           | _             | 40                 | V    | $R_{\rm l} = 2 \ \Omega^{4)}$<br>$t = 400 \ {\rm ms}$                      |  |

| 4.1.6   | Current through ground pin                                   | $I_{GND}$              | _             | 25                 | mA   | <i>t</i> ≤ 2 min.                                                          |  |

| 4.1.7   | Current through VDD pin                                      | $I_{DD}$               | -25           | 12                 | mA   | <i>t</i> ≤ 2 min.                                                          |  |

| Power   | Stages                                                       | *                      |               | <u> </u>           | *    |                                                                            |  |

| 4.1.8   | Load current                                                 | $I_{L}$                | $-I_{L(LIM)}$ | $I_{L(LIM)}$       | Α    | 5)                                                                         |  |

| 4.1.9   | Maximum energy dissipation                                   | $E_{AS}$               |               |                    | mJ   | 6)                                                                         |  |

|         | single pulse                                                 |                        |               |                    |      | $T_{\rm j(0)}$ = 150 °C                                                    |  |

|         | channel 0, 1                                                 |                        | _             | 180                |      | $I_{L(0)} = 5 \text{ A}$                                                   |  |

|         | channel 2, 3                                                 |                        | _             | 45                 |      | $I_{L(0)}$ = 2 A                                                           |  |

| Diagn   | osis Pin                                                     |                        |               |                    |      |                                                                            |  |

| 4.1.10  | Current through sense pin IS                                 | $I_{IS}$               | -8            | 8                  | mA   | $t \le 2 \text{ min.}$                                                     |  |

| Input I | Pins                                                         |                        |               |                    |      |                                                                            |  |

| 4.1.11  | Voltage at input pins                                        | $V_{IN}$               | -0.3          | 5.5                | V    | _                                                                          |  |

| 4.1.12  | Current through input pins                                   | $I_{IN}$               | -0.75         | 0.75               | mA   | _                                                                          |  |

|         |                                                              |                        | -2.0          | 2.0                |      | <i>t</i> ≤ 2 min.                                                          |  |

| SPI Pi  |                                                              | 1                      | 1             |                    | 1    | 1                                                                          |  |

| 4.1.13  | J 1                                                          | $V_{CS}$               | -0.3          | $V_{\rm DD}$ + 0.3 |      | _                                                                          |  |

| 4.1.14  | 3                                                            | $I_{\text{CS}}$        | -2.0          | 2.0                | mA   | <i>t</i> ≤ 2 min.                                                          |  |

| 4.1.15  |                                                              | $V_{SI}$               | -0.3          | $V_{\rm DD}$ + 0.3 | V    | _                                                                          |  |

| 4.1.16  |                                                              | $I_{SI}$               | -2.0          | 2.0                | mA   | <i>t</i> ≤ 2 min.                                                          |  |

| 4.1.17  | ·                                                            | $V_{SCLK}$             | -0.3          | $V_{\rm DD}$ + 0.3 | V    | _                                                                          |  |

| 4.1.18  |                                                              | $I_{SCLK}$             | -2.0          | 2.0                | mA   | <i>t</i> ≤ 2 min.                                                          |  |

| 4.1.19  | Voltage at serial out pin                                    | $V_{SO}$               | -0.3          | $V_{\rm DD}$ + 0.3 | V    | _                                                                          |  |

#### **Electrical Characteristics**

### Absolute Maximum Ratings (cont'd)1)

$T_{\rm j}$  = -40 to +150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                                    | Symbol             | Lim   | it Values | Unit | Conditions        |  |

|--------|----------------------------------------------|--------------------|-------|-----------|------|-------------------|--|

|        |                                              |                    | min.  | max.      |      |                   |  |

| 4.1.20 | Current through serial output pin SO         | $I_{SO}$           | -2.0  | 2.0       | mA   | <i>t</i> ≤ 2 min. |  |

| Limp H | Home Pin                                     |                    |       |           |      |                   |  |

| 4.1.21 | Voltage at limp home input pin               | $V_{LHI}$          | -0.3  | 5.5       | V    | _                 |  |

| 4.1.22 | Current through limp home input pin          | $I_{LHI}$          | -0.75 | 0.75      | mA   | _                 |  |

|        |                                              |                    | -2.0  | 2.0       |      | <i>t</i> ≤ 2 min. |  |

| Tempe  | eratures                                     |                    |       | ·         |      |                   |  |

| 4.1.23 | Junction temperature                         | $T_{\rm j}$        | -40   | 150       | °C   | _                 |  |

| 4.1.24 | Dynamic temperature increase while switching | $\Delta T_{\rm j}$ | _     | 60        | K    | _                 |  |

| 4.1.25 | Storage temperature                          | $T_{\rm stg}$      | -55   | 150       | °C   | _                 |  |

| ESD S  | usceptibility                                |                    |       |           |      | 1                 |  |

| 4.1.26 | ESD susceptibility HBM                       | $V_{ESD}$          |       |           | kV   | HBM <sup>7)</sup> |  |

|        | OUT pins vs. VBE                             |                    | -4    | 4         |      | _                 |  |

|        | other pins incl. OUT vs. GND                 | )                  | -2    | 2         |      | _                 |  |

- 1) Not subject to production test, specified by design.

- 2) Device is mounted on an FR4 2s2p board according to Jedec JESD51-2,-5,-7 at natural convection; The product (chip+package) was simulated on a 76.4 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 μm Cu, 2 x 35 μm Cu). Where applicable, a thermal via array under the package contacted the first inner copper layer.

- 3) In accordance to AEC Q100-012 and AEC Q101-006.

- 4)  $R_1$  is the internal resistance of the load dump pulse generator.

- 5) Over current protection is a protection feature. Operation in over current protection is considered as "outside" normal operating range. Protection features are not designed for continuous repetitive operation.

- 6) Pulse shape represents inductive switch off:  $I_{D(t)} = I_{D}(0) \times (1 t / t_{pulse})$ ;  $0 < t < t_{pulse}$

- 7) ESD resistivity, HBM according to EIA/JESD 22-A 114B (1.5  $k\Omega$ , 100 pF)

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Data Sheet 11 Rev. 1.0, 2010-04-12

**Electrical Characteristics**

# 4.2 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | os. Parameter Symbol           |             | L    | _imit Val | ues  | Unit | Conditions                          |  |

|-------|--------------------------------|-------------|------|-----------|------|------|-------------------------------------|--|

|       |                                |             | Min. | Тур.      | Max. |      |                                     |  |

| 4.2.1 | Junction to Soldering Point 1) | $R_{thJSP}$ | -    | _         | 20   | K/W  | measured to pin 1, 2, 9, 28, 35, 36 |  |

| 4.2.2 | Junction to Ambient 1)         | $R_{thJA}$  | _    | 35        | _    | K/W  | 2)                                  |  |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 12 Rev. 1.0, 2010-04-12

<sup>2)</sup> Specified  $R_{\text{thJA}}$  values is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip+package) was simulated on a 76.4 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70  $\mu$ m Cu, 2 x 35  $\mu$ m Cu). Where applicable, a thermal via array under the package contacted the first inner copper layer.

Power Supply

# 5 Power Supply

The SPOC - BTS5460SF is supplied by two supply voltages  $V_{\rm BB}$  and  $V_{\rm DD}$ . The  $V_{\rm BB}$  supply line is used by the power switches. The  $V_{\rm DD}$  supply line is used by the SPI related circuitry and for driving the SO line. A capacitor between pins VDD and GND is recommended as shown in **Figure 26**.

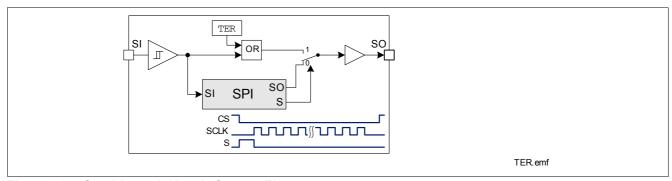

There is a power-on reset function implemented for the  $V_{\rm DD}$  logic power supply. After start-up of the logic power supply, all SPI registers are reset to their default values. The SPI interface including daisy chain function is active as soon as  $V_{\rm DD}$  is provided in the specified range independent of  $V_{\rm BB}$ . First SPI data are the output register values with TER = 1.

Specified parameters are valid for the supply voltage range according  $V_{\rm BB(nor)}$  or otherwise specified. For the extended supply voltage range according  $V_{\rm BB(ext)}$  device functionality (switching, diagnosis and protection functions) are still given, parameter deviations are possible.

### 5.1 Power Supply Modes

The following table shows all possible power supply modes for  $V_{\rm BB},\,V_{\rm DD}$  and the pin LHI.

| Power Supply Modes      | Off | Off | SPI<br>on | Reset | Off    | On via<br>INx          | Limp Home mode         | Normal operation       | Limp Home mode with    |

|-------------------------|-----|-----|-----------|-------|--------|------------------------|------------------------|------------------------|------------------------|

|                         |     |     |           |       |        |                        | without SPI            |                        | SPI 1)                 |

| $V_{BB}$                | 0 V | 0 V | 0 V       | 0 V   | 13.5 V | 13.5 V                 | 13.5 V                 | 13.5 V                 | 13.5 V                 |

| $V_{DD}$                | 0 V | 0 V | 5 V       | 5 V   | 0 V    | 0 V                    | 0 V                    | 5 V                    | 5 V                    |

| LHI                     | 0 V | 5 V | 0 V       | 5 V   | 0 V    | 0 V                    | 5 V                    | 0 V                    | 5 V                    |

| Power stage, protection | _   | _   | _         | _     | _      | <b>√</b> <sup>2)</sup> | <b>√</b> <sup>2)</sup> | ✓                      | <b>√</b> <sup>2)</sup> |

| Limp home               | _   | _   | _         | _     | _      | _                      | 1                      | _                      | 1                      |

| SPI (logic)             | _   | _   | 1         | ✓     | reset  | reset                  | reset                  | 1                      | reset <sup>3)</sup>    |

| Stand-by current        | _   | _   | _         | _     | 1      | <b>✓</b> <sup>4)</sup> | _                      | <b>√</b> <sup>5)</sup> | _                      |

| Idle current            | _   | -   | -         | _     | -      | _                      | _                      | <b>√</b> <sup>6)</sup> | _                      |

| Diagnosis               | _   | -   | _         | _     | -      | _                      | _                      | 1                      | <b>✓</b> <sup>7)</sup> |

- 1) SPI read only

- 2) Channel 1, 2 and/or 3 activated according to the state of INx

- 3) SPI reset only with applied  $V_{\mathrm{BB}}$  voltage

- 4) When INx = low

- 5) When DCR.MUX =  $111_b$  and INx = low

- 6) When all channels are in OFF-state and DCR.MUX  $\neq$  111<sub>b</sub>

- 7) Current sense disabled in limp home mode

#### 5.1.1 Stand-by Mode and Device Wake-up Mechanisms

Stand-by mode is entered as soon as the current sense multiplexer (DCR.MUX) is in default (stand-by) position and all input pins are not set. All error latches are cleared automatically in stand-by mode. As soon as stand-by mode is entered, register HWCR.STB is set. To wake-up the device, the current sense multiplexer (DCR.MUX) is programmed different to default (stand-by) position . The power-on wake up time  $t_{WU(PO)}$  has to be considered.

Idle mode parameters are valid, when all channels are switched off, but the current sense multiplexer is not in default position, and  $V_{\rm DD}$  supply is available.

Note: A transition from operation to stand-by mode does not reset the SPI registers. So, if  $V_{\rm DD}$  is present and SPI is programmed, a changing to  ${\tt MUX}$  = 111 $_{\tt b}$  does not reset the SPI registers. An activation of the channels via the input pin INx will wake up the device with the former SPI register settings.

**Power Supply**

Activating one of the outputs via the input pins (INx = high) will wake-up the device out of stand-by mode. The power stages are working without VDD supply according to the table above. The output turn-on times will be extended by the stand-by channel wake up time  $t_{\text{WU(STCH)}}$  as long as no other channel is active. If one channel is active already before channel turn-on times  $t_{\text{on}}$  (6.5.12) can be considered.

Note: In the operation with  $V_{\rm DD}$  = 0 V and INx = high a switching off of all input signals will turn the device in stand-by mode. In stand-by mode the error latches are cleared.

Limp home (LHI = high) applied for a time longer than  $t_{\rm LH(ac)}$  will wake-up the device out of stand-by mode after the power-on wake up time  $t_{\rm WU(PO)}$  and it is working without VDD supply. Channels 1, 2 and 3 can be activated via the input pins INx. The error latches can be cleared by a low-high transition at the according input pin.

#### 5.2 Reset

There are several reset trigger implemented in the device. They reset the SPI registers including the over temperature latches to their default values. The power stages will switch off, if they are activated via the SPI register OUT.n. If the power stages are activated via the parallel input pins they are not affected by the reset signals. The ERR-flags are cleared by those reset triggers. The over temperature protection and latches are functional after a reset trigger.

Note: During a reset only the channels 1, 2 and 3 can be activated via the according input pins. The input assigned mode is not available during a reset.

The first SPI transmission after any kind of reset contains at pin SO the read information from the standard diagnosis, the transmission error bit TER is set.

#### Power-On Reset

The power-on reset is released, when  $V_{\rm DD}$  voltage level is higher than  $V_{\rm DD(PO)}$ . The SPI interface can be accessed after wake up time  $t_{\rm WU(PO)}$ .

#### **Reset Command**

There is a reset command available to reset all register bits of the register bank and the diagnosis registers. As soon as  $HWCR.RST = 1_b$ , a reset is triggered equivalent to power-on reset. The SPI interface can be accessed after transfer delay time  $t_{CS(td)}$ .

#### **Limp Home Mode**

The limp home mode will be activated as soon as the pin LHI is set to high for a time longer than  $t_{\rm LH(ac)}$ . The SPI write-registers are reset with applied  $V_{\rm BB}$  voltage. The outputs OUTx can be activated via the input pins also during activated limp home mode. The error latches can be cleared by a low-high transition at the according input pin. For application example see **Figure 26**. The SPI interface is operating normally, so the limp home register bit LHI as well as the error flags can be read, but any write command will be ignored.

Data Sheet 14 Rev. 1.0, 2010-04-12

1)

μs

200

**Power Supply**

#### 5.3 Electrical Characteristics

#### **Electrical Characteristics Power Supply**

Unless otherwise specified:  $V_{\rm BB}$  = 8 V to 17 V,  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40 °C to +150 °C

typical values:  $V_{\rm BB}$  = 13.5 V,  $V_{\rm DD}$  = 4.3 V,  $T_{\rm j}$  = 25 °C **Limit Values** Unit | Test Conditions Parameter **Symbol** min. typ. max. 5.3.1 Supply voltage range for normal operation 8 17 ٧  $V_{\rm BB(nor)}$ power switch 28<sup>1)</sup> ٧ Parameter 5.3.2 | Extended supply voltage range for operation  $V_{\mathsf{BB(ext)}}$ 4.5 power switch deviations possible Stand-by current for whole device with loads 5.3.3  $V_{\rm DD}$  = 0 V μΑ  $I_{\rm BB(STB)}$  $V_{\rm LHI}$  = 0 V <sup>1)</sup>  $T_{\rm i}$  = 25 °C 4.5 1)  $T_{i} \le 85 \, {}^{\circ}\text{C}$ 28 7  $V_{\rm DD}$  = 5 V Idle current for whole device with loads, all mΑ  $I_{\mathsf{BB}(\mathsf{idle})}$ channels off DCR.MUX = 1105.3.5 Logic supply voltage  $V_{\mathsf{DD}}$ 3.0 5.5 ٧ 5.3.6 Logic supply current  $V_{\rm CS}$  =  $V_{\rm LHI}$  = 0 V μΑ  $I_{\mathsf{DD}}$  $R_{\rm IS}$  = 2.7 k $\Omega$  $V_{\rm IS}$  = 0 V 140  $f_{SCLK}$  = 0 Hz 280  $f_{SCLK} = 5 \text{ MHz}$ Logic idle current 25  $V_{\rm CS} = V_{\rm DD}$ 5.3.7  $I_{\rm DD(idle)}$ μΑ  $f_{\text{SCLK}} = 0 \text{ Hz}$ Chip in Standby 5.3.8 Operating current for whole device active 25 10 mΑ  $f_{\text{SCLK}} = 0 \text{ Hz}$  $I_{\mathrm{GND}}$ **LHI Input Characteristics** ٧ 5.3.9 L-input level at LHI pin  $V_{\rm LHI(L)}$ 0 8.0 5.3.10 H-input level at LHI pin 1.8 5.5 V  $V_{\mathsf{LHI}(\mathsf{H})}$ 5.3.11 L-input current through LHI pin 3  $^{1)} V_{LHI} = 0.4 \text{ V}$ 12 80 μΑ  $I_{\mathsf{LHI}(\mathsf{L})}$  $V_{\rm I\,HI}$  = 5 V 5.3.12 H-input current through LHI pin 10 40 80 μΑ  $I_{\mathsf{LHI}(\mathsf{H})}$ Reset 5.3.13 Power-On reset threshold voltage  $V_{\rm DD(PO)}$ 2.4 V 1) 5.3.14 Power-On wake up time 200 μs  $t_{WU(PO)}$ 1) 5.3.15 Stand-by channel wake up time 200 μs  $t_{WU(STCH)}$

5.3.16 Limp home acknowledgement time

Note: Characteristics show the deviation of parameter at the given supply voltage and junction temperature.

$t_{\rm LH(ac)}$

<sup>1)</sup> Not subject to production test, specified by design.

**Power Supply**

# 5.4 Command Description

# **HWCR**

# Hardware Configuration Register 1)

| $W/\overline{R}^{2)}$ | RB <sup>2)</sup> | ADDR <sup>2)</sup> |   | 3    | 2    | 1   | 0  |

|-----------------------|------------------|--------------------|---|------|------|-----|----|

| read                  | 1                | 1                  | 0 | LED3 | LED2 | STB | CL |

| write                 | 1                | 1                  | 0 | LED3 | LED2 | RST | CL |

- 1) Shaded cells not mentioned in this chapter.

- 2) W/R Write/Read, RB Register Bank, ADDR Address

| Field | Bits | Type | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| RST   | 1    | W    | Reset Command  0 1) Normal operation  1 Execute reset command |

| STB   | 1    | r    | Stand-by 0 Device is awake 1 Device is in stand-by mode       |

<sup>1)</sup> Bold letters indicate the default values.

# 6 Power Stages

The high-side power stages are built by N-channel vertical power MOSFETs (DMOS) with charge pumps. There are four channels implemented in the device. Channels can be switched on via an input pin (please refer to Section 6.2) or via SPI register OUT.

# 6.1 Output ON-State Resistance

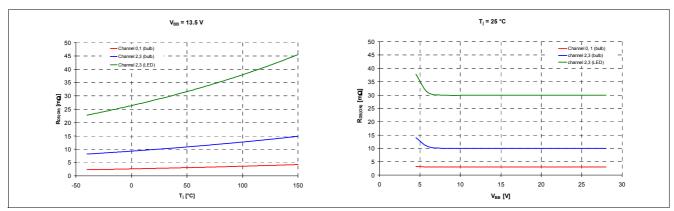

The on-state resistance  $R_{\rm DS(ON)}$  depends on the supply voltage  $V_{\rm BB}$  as well as on the junction temperature  $T_{\rm j}$ . Figure 4 shows those dependencies. The behavior in reverse polarity mode is described in Section 7.5.

Figure 4 Typical On-State Resistance

# 6.2 Input Circuit

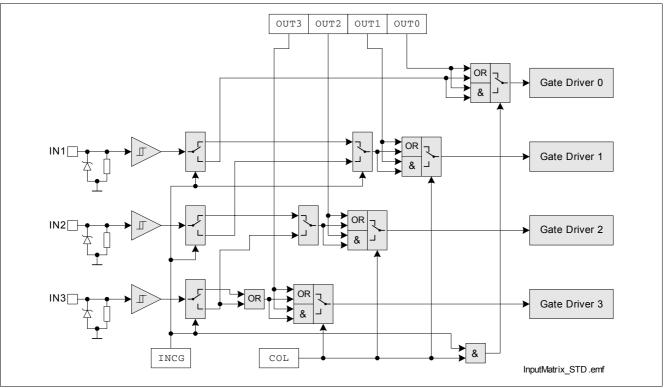

The outputs of the SPOC - BTS5460SF can be activated either via the SPI register <code>OUT.OUTn</code> or via the dedicated input pins. There are two different ways to use the input pins, the direct drive mode and the assigned drive mode. The default setting is the direct drive mode. To activate the assigned drive mode the register bit <code>ICR.INCG</code> needs to be set.

Additionally, there are two ways of using the input pins in combination with the OUT register by programming the ICR.COL parameter.

- ICR.COL = 0<sub>b</sub>: A channel is switched on either by the according OUT register bit or the input pin.

- ICR.COL = 1<sub>b</sub>: A channel is switched on by the according OUT register bit only, when the input pin is high. In this configuration, a PWM signal can be applied to the input pin and the channel is activated by the SPI register OUT.

Data Sheet 17 Rev. 1.0, 2010-04-12

Figure 5 shows the complete input switch matrix.

Figure 5 Input Switch Matrix

The current sink to ground ensures that the input signal is low in case of an open input pin. The zener diode protects the input circuit against ESD pulses.

# 6.2.1 Input Direct Drive

This mode is the default after the device's wake up and reset. The input pins activate the channels during normal operation (with default setting of bit ICR.INCG), stand-by mode and limp home mode. Channel 0 can be activated only via the SPI-bit OUT.OUT0 in direct drive mode. The inputs are linked directly to the channels according to:

Table 1 Direct Drive Mode

| Input Pin | Assigned channel, if ICR.INCG = $0_b$ |

|-----------|---------------------------------------|

| IN1       | Channel 1                             |

| IN2       | Channel 2                             |

| IN3       | Channel 3                             |

# 6.2.2 Input Assigned Drive

To activate the assigned drive function the register bit ICR. INCG needs to be set. In this mode all output channels can be activated via the input pins. Channel 2 and 3 are assigned to only one input pin. The following mapping is used:

Table 2 Assigned Drive Mode

| Input Pin | Assigned channel, if ICR.INCG = 1 <sub>b</sub> |

|-----------|------------------------------------------------|

| IN1       | Channel 0                                      |

| IN2       | Channel 1                                      |

| IN3       | Channel 2, channel 3                           |

# 6.3 Power Stage Output

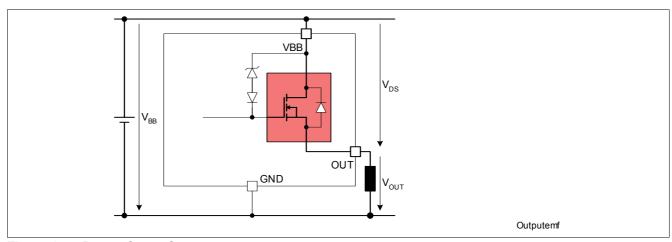

The power stages are built to be used in high side configuration (Figure 6).

Figure 6 Power Stage Output

The power DMOS switches with a dedicated slope, which is optimized in terms of EMC emission. Defined slew rates and edge shaping allow lowest EMC emissions during PWM operation at low switching losses.

#### 6.3.1 Bulb and LED mode

Channel 2 and channel 3 can be configured in bulb and LED mode via the SPI registers HWCR.LEDn. During LED mode following parameters are changed for an optimized functionality with LED loads: On-state resistance  $R_{\rm DS(ON)}$ , switching timings ( $t_{\rm delay(ON)}$ ,  $t_{\rm delay(OFF)}$ ,  $t_{\rm ON}$ ,  $t_{\rm OFF}$ ), slew rates dV/d $t_{\rm ON}$  and dV/d $t_{\rm OFF}$ , current protections  $I_{\rm L(trip)}$  and current sense ratio  $k_{\rm ILIS}$ .

# 6.3.2 Switching Resistive Loads

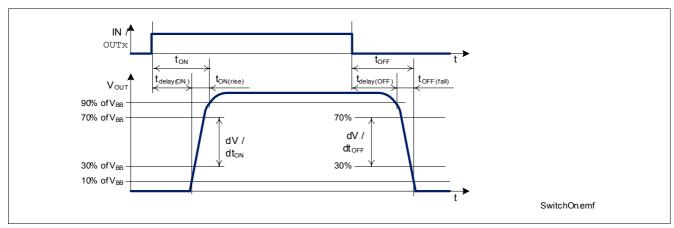

When switching resistive loads the following switching times and slew rates can be considered.

Figure 7 Switching a Load (resistive)

# 6.3.3 Switching Inductive Loads

When switching off inductive loads with high-side switches, the voltage  $V_{\rm OUT}$  drops below ground potential, because the inductance intends to continue driving the current. To prevent the destruction of the device due to high voltages, there is a voltage clamp mechanism implemented, which limits that negative output voltage to a certain level ( $V_{\rm DS(CL)}$  (6.5.2)). See **Figure 6** for details. The device provides SmartClamp functionality. To increase the energy capability, the clamp voltage  $V_{\rm DS(CL)}$  increases with the junction temperature  $T_{\rm j}$  and load current  $I_{\rm L}$ . Please refer also to **Section 7.6**. The maximum allowed load inductance is limited.

#### 6.4 Inverse Current Behavior

During inverse currents ( $V_{\rm OUT} > V_{\rm BB}$ ) the affected channel stays in ON- or in OFF-state. Furthermore, during applied inverse currents no ERR-flag is set.

The functionality of unaffected channels is not influenced by inverse currents applied to other channels (except effects due to junction temperature increase). Influences on the diagnostic function of unaffected channels are possible only for the current sense ratio, please refer to  $\Delta k_{\text{ILIS(IC)}}$  (8.5.3).

Note: No protection mechanism like temperature protection or current protection is active during applied inverse currents. Inverse currents cause power losses inside the DMOS, which increase the overall device temperature, which could lead to a switch off of the unaffected channels due to over temperature.

#### 6.5 **Electrical Characteristics**

# **Electrical Characteristics Power Stages**

| Pos.  | s. Parameter                                    |                                | Lin  | nit Va | lues | Unit      | Test Conditions                                                         |

|-------|-------------------------------------------------|--------------------------------|------|--------|------|-----------|-------------------------------------------------------------------------|

|       |                                                 |                                | min. | typ.   | max. |           |                                                                         |

| Outp  | ut Characteristics                              |                                |      | 1      | 1    |           | I                                                                       |

| 6.5.1 | On-state resistance                             | $R_{\mathrm{DS}(\mathrm{ON})}$ |      |        |      | $m\Omega$ |                                                                         |

|       | channel 0,                                      |                                |      |        |      |           | $I_{\rm L}$ = 7.5 A                                                     |

|       |                                                 |                                | _    | 3.5    | _    |           | $1^{1)} T_{j} = 25  ^{\circ}\text{C}$                                   |

|       |                                                 |                                | -    | 7      | 9    |           | $T_{\rm j}$ = 150 °C                                                    |

|       | channel 2,                                      | 3                              |      |        |      |           | HWCR.LEDn = 0                                                           |

|       |                                                 |                                |      |        |      |           | $I_{\rm L}$ = 2.6 A                                                     |

|       |                                                 |                                | _    | 11     | _    |           | <sup>1)</sup> $T_{\rm j}$ = 25 °C                                       |

|       |                                                 |                                | _    | 22     | 28   |           | $T_{\rm j}$ = 150 °C                                                    |

|       |                                                 |                                |      |        |      |           | HWCR.LEDn = 1                                                           |

|       |                                                 |                                |      | 39     |      |           | $I_{\rm L} = 0.6  {\rm A}$                                              |

|       |                                                 |                                | _    | 78     | 100  |           | $T_{\rm j} = 25  ^{\circ}{\rm C}$<br>$T_{\rm i} = 150  ^{\circ}{\rm C}$ |

| 6.5.2 | Output clamp                                    | V                              |      | 70     | 100  | V         | 1 <sub>j</sub> - 130 0                                                  |

| 0.5.2 |                                                 | $V_{DS(CL)}$                   | 20   |        | 54   | V         | T - 25 °C                                                               |

|       | channel 0,                                      | '                              | 32   | _      | 54   |           | $T_{\rm j}$ = 25 °C<br>$I_{\rm L}$ = 20 mA                              |

|       |                                                 |                                | 40   |        | 55   |           | $\frac{1}{1}T_{\rm j} = 150  ^{\circ}{\rm C}$                           |

|       |                                                 |                                | 70   |        | 33   |           | $I_{L} = 6 \text{ A}$                                                   |

|       | channel 2,                                      | 3                              | 32   | _      | 54   |           | T <sub>i</sub> = 25 °C                                                  |

|       |                                                 |                                |      |        |      |           | $I_{\rm L}$ = 20 mA                                                     |

|       |                                                 |                                | 40   | _      | 55   |           | $T_{\rm j} = 150  ^{\circ}{\rm C}$                                      |

|       |                                                 |                                |      |        |      |           | I <sub>L</sub> = 2 A                                                    |

| 6.5.3 | Output leakage current per channel in           | $I_{L(OFFSTB)}$                |      |        |      | μΑ        | OUT.OUTn = 0                                                            |

|       | stand-by                                        |                                |      |        |      |           | DCR.MUX = 111                                                           |

|       | channel 0,                                      | 1                              | _    | _      | 2    |           | $T_{\rm j}$ = 25 °C                                                     |

|       |                                                 |                                | _    | _      | 10   |           | $\binom{1)^{J}}{T_{j}} = 85  ^{\circ}\text{C}$                          |

|       |                                                 |                                | _    | _      | 50   |           | $T_{j}^{(1)} = 105  ^{\circ}\text{C}$                                   |

|       | channel 2,                                      | 3                              | _    | _      | 1    |           | $T_{\rm j}$ = 25 °C                                                     |

|       |                                                 |                                |      |        | 20   |           | $^{1)'}T_{\rm j}$ = 85 °C<br>$^{1)}T_{\rm i}$ = 105 °C                  |

| 654   | Output loakage current per channel in idle      | I                              | -    |        | 20   | ^         | J                                                                       |

| 6.5.4 | Output leakage current per channel in idle mode | $I_{L(OFFidle)}$               |      |        |      | μΑ        | OUT.OUTn = 0<br>DCR.MUX ≠ 111                                           |

|       | channel 0,                                      | 1                              |      |        | 60   |           | $^{1)} T_{i} = 85  ^{\circ}\text{C}$                                    |

|       | Giaillei 0,                                     | 1                              |      | _      | 80   |           | $T_{\rm j} = 85^{\circ} {\rm C}$<br>$T_{\rm j} = 105^{\circ} {\rm C}$   |

|       |                                                 |                                | _    | _      | 530  |           | $T_{\rm j} = 150 ^{\circ}{\rm C}$                                       |

|       | channel 2,                                      | 3                              | _    | _      | 45   |           | $^{1)}T_{j} = 85 ^{\circ}C$                                             |

|       | Sharifier 2,                                    |                                | _    | _      | 50   |           | $^{1}_{j} = 00^{\circ} \text{C}$                                        |

|       |                                                 |                                | _    | _      | 230  |           | $T_{\rm i} = 150  ^{\circ}{\rm C}$                                      |

|       | I .                                             | 1                              | 1    | 1      | 1    | 1         | 1 -                                                                     |

# **Electrical Characteristics Power Stages** (cont'd)

| Pos.  | Parameter                              | Symbol          | Limit Values |      |      | Unit | <b>Test Conditions</b>                                                                    |  |

|-------|----------------------------------------|-----------------|--------------|------|------|------|-------------------------------------------------------------------------------------------|--|

|       |                                        |                 | min.         | typ. | max. |      |                                                                                           |  |

| 6.5.5 | Inverse current capability per channel | $-I_{L(IC)}$    |              |      |      | Α    | 1) No influences on                                                                       |  |

|       | channel 0, 1                           |                 | 6            | _    | _    |      | switching functionality of                                                                |  |

|       | channel 2, 3                           |                 | 2            | _    | _    |      | unaffected channels, $k_{\rm ILIS}$ influence according $\Delta k_{\rm ILIS(IC)}$ (8.5.3) |  |

| Input | Characteristics                        | !               | +            | •    | -    |      | ,                                                                                         |  |

| 6.5.6 | L-input level                          | $V_{IN(L)}$     | 0            | -    | 8.0  | V    | _                                                                                         |  |

| 6.5.7 | H-input level                          | $V_{\rm IN(H)}$ | 1.8          | _    | 5.5  | V    | _                                                                                         |  |

| 6.5.8 | L-input current                        | $I_{IN(L)}$     | 3            | 12   | 80   | μΑ   | $^{1)} V_{IN} = 0.4 \text{ V}$                                                            |  |

| 6.5.9 | H-input current                        | $I_{IN(H)}$     | 10           | 40   | 80   | μΑ   | V <sub>IN</sub> = 5 V                                                                     |  |

# **Electrical Characteristics Power Stages** (cont'd)

| Pos.    | Parameter                                                  | Symbol                 | Limit Values |      |      | Unit | Test Conditions                        |

|---------|------------------------------------------------------------|------------------------|--------------|------|------|------|----------------------------------------|

|         |                                                            |                        | min.         | typ. | max. |      |                                        |

| Timin   | gs                                                         |                        | •            | •    | *    |      |                                        |

| 6.5.10  | Turn-ON delay to 10% $V_{\rm BB}$                          | $t_{\rm delay(ON)}$    |              |      |      | μs   | $^{1)}$ $V_{\rm BB}$ = 13.5 V          |

|         | channel 0, 1                                               |                        | _            | 25   | _    |      | _                                      |

|         | channel 2, 3                                               |                        | _            | 20   | _    |      | HWCR.LEDn = 0                          |

|         |                                                            |                        | _            | 12   | _    |      | HWCR.LEDn = 1                          |

| 6.5.11  | Turn-OFF delay to 90% $V_{\mathrm{BB}}$                    | $t_{\rm delay(OFF)}$   |              |      |      | μs   | <sup>1)</sup> V <sub>BB</sub> = 13.5 V |

|         | channel 0, 1                                               |                        | _            | 75   | _    |      | _                                      |

|         | channel 2, 3                                               |                        | _            | 50   | _    |      | HWCR.LEDn = 0                          |

|         |                                                            |                        | _            | 20   | _    |      | HWCR.LEDn = 1                          |

| 6.5.12  | Turn-ON time to                                            | $t_{\sf ON}$           |              |      |      | μs   | V <sub>BB</sub> = 13.5 V               |

|         | 90% $V_{\mathrm{BB}}$ including turn-ON delay              |                        |              |      |      |      | DCR.MUX ≠111                           |

|         | channel 0, 1                                               |                        | _            | -    | 100  |      | $R_{L}$ = 2.2 $\Omega$                 |

|         | channel 2, 3                                               |                        | _            | _    | 100  |      | HWCR.LEDn = 0                          |

|         |                                                            |                        |              |      |      |      | $R_{\rm L}$ = 6.8 $\Omega$             |

|         |                                                            |                        | _            | -    | 50   |      | HWCR.LEDn = 1                          |

| 0.5.40  | Town OFF the a to                                          | ,                      |              |      |      | _    | $R_{\rm L} = 33 \Omega$                |

| 6.5.13  | Turn-OFF time to 10% $V_{\rm BB}$ including turn-OFF delay | $t_{OFF}$              |              |      |      | μs   | $V_{\rm BB}$ = 13.5 V                  |

|         | channel 0, 1                                               |                        |              |      | 150  |      | $R_1 = 2.2 \Omega$                     |

|         | channel 2, 3                                               |                        |              | _    | 110  |      | $H_L = 2.2 \Omega$ $HWCR.LEDn = 0$     |

|         | Chamer 2, 3                                                |                        |              | _    | 110  |      | $R_{\rm I} = 6.8 \Omega$               |

|         |                                                            |                        | _            | _    | 50   |      | HWCR.LEDn = 1                          |

|         |                                                            |                        |              |      |      |      | $R_{\rm L}$ = 33 $\Omega$              |

| 6.5.14  | Turn-ON rise time from 10% to                              | t <sub>ON(rise)</sub>  |              |      |      | μs   | V <sub>BB</sub> = 13.5 V               |

|         | 90% V <sub>BB</sub>                                        |                        |              |      |      |      | DCR.MUX ≠111                           |

|         | channel 0, 1                                               |                        | _            | _    | 55   |      | $R_{\rm L}$ = 2.2 $\Omega$             |

|         | channel 2, 3                                               |                        | _            | _    | 55   |      | HWCR.LEDn = 0                          |

|         |                                                            |                        |              |      |      |      | $R_{\rm L}$ = 6.8 $\Omega$             |

|         |                                                            |                        | _            | -    | 11   |      | HWCR.LEDn = 1                          |

| 0 - 4 - | Time OFF fall time a frage 2007 to                         |                        |              |      |      |      | $R_{\rm L} = 33 \Omega$                |

| 6.5.15  | Turn-OFF fall time from 90% to 10% $V_{\rm BB}$            | t <sub>OFF(fall)</sub> |              |      |      | μs   | $V_{\rm BB}$ = 13.5 V                  |

|         | channel 0, 1                                               |                        | _            | _    | 55   |      | $R_{\rm L}$ = 2.2 $\Omega$             |

|         | channel 2, 3                                               |                        | _            | _    | 55   |      | HWCR.LEDn = 0                          |

|         | ,                                                          |                        |              |      |      |      | $R_{\rm L}$ = 6.8 $\Omega$             |

|         |                                                            |                        | _            | _    | 11   |      | HWCR.LEDn = 1                          |

|         |                                                            |                        |              |      |      |      | $R_{\rm L}$ = 33 $\Omega$              |

# **Electrical Characteristics Power Stages** (cont'd)

| Pos.   | Parameter                                  |              | Symbol                             | Limit Values |      |      | Unit | Test Conditions                         |  |

|--------|--------------------------------------------|--------------|------------------------------------|--------------|------|------|------|-----------------------------------------|--|

|        |                                            |              |                                    | min.         | typ. | max. |      |                                         |  |

| 6.5.16 | Turn-ON/OFF matching                       |              | $ t_{\text{ON}} - t_{\text{OFF}} $ |              |      |      | μs   | V <sub>BB</sub> = 13.5 V                |  |

|        |                                            | channel 0, 1 |                                    | _            | _    | 90   |      | $R_{L}$ = 2.2 $\Omega$                  |  |

|        |                                            | channel 2, 3 |                                    | _            | _    | 70   |      | HWCR.LEDn = 0 $R_1 = 6.8 \Omega$        |  |

|        |                                            |              |                                    | _            | _    | 50   |      | HWCR.LEDn = 1 $R_{\rm L}$ = 33 $\Omega$ |  |

| 6.5.17 | Turn-ON slew rate 30% to 70% $V_{\rm BB}$  |              | $dV/dt_{ON}$                       |              |      |      | V/µs | V <sub>BB</sub> = 13.5 V                |  |

|        |                                            | channel 0, 1 |                                    | 0.2          | 0.7  | 2.0  |      | $R_{\rm L}$ = 2.2 $\Omega$              |  |

|        |                                            | channel 2, 3 |                                    | 0.2          | 0.9  | 2.5  |      | HWCR.LEDn = 0 $R_1 = 6.8 \Omega$        |  |

|        |                                            |              |                                    | 0.6          | 2.5  | 6.0  |      | HWCR.LEDn = 1 $R_{\rm L} = 33 \Omega$   |  |

| 6.5.18 | Turn-OFF slew rate 70% to 30% $V_{\rm BB}$ |              | $-dV/$ $dt_{OFF}$                  |              |      |      | V/µs | V <sub>BB</sub> = 13.5 V                |  |

|        |                                            | channel 0, 1 |                                    | 0.2          | 0.7  | 2.0  |      | $R_{L}$ = 2.2 $\Omega$                  |  |

|        |                                            | channel 2, 3 |                                    | 0.2          | 0.9  | 2.5  |      | HWCR.LEDn = 0 $R_L = 6.8 \Omega$        |  |

|        |                                            |              |                                    | 0.6          | 2.5  | 6.0  |      | HWCR.LEDn = 1 $R_L = 33 \Omega$         |  |

<sup>1)</sup> Not subject to production test, specified by design.

# 6.6 Command Description

# OUT

# **Output Configuration Registers**

| $W/\overline{R}$ | RB | 5 | 4 | 3    | 2    | 1    | 0    |

|------------------|----|---|---|------|------|------|------|

| read/write       | 0  | 0 | 0 | ОПТЗ | OUT2 | OUT1 | OUT0 |

| Field        | Bits | Туре | Description                   |

|--------------|------|------|-------------------------------|

| OUTn         | n    | rw   | Set Output Mode for Channel n |

| n = 3  to  0 |      |      | Channel n is switched off     |

|              |      |      | 1 Channel n is switched on    |

#### **HWCR**

# **Hardware Configuration Register**

| $W/\overline{R}$ | RB | AD | DR | 3    | 2    | 1   | 0  |

|------------------|----|----|----|------|------|-----|----|

| read/write       | 1  | 1  | 0  | LED3 | LED2 | RST | CL |

| Field      | Bits | Туре | Description                 |

|------------|------|------|-----------------------------|

| LEDn       | n    | rw   | Set LED Mode for Channel n  |

| n = 3 to 2 |      |      | 0 Channel n is in bulb mode |

|            |      |      | 1 Channel n is in LED mode  |

# **ICR**

# **Input and Current Source Configuration Register**

| W/R        | RB | AD | DR | 3   | 2    | 1   | 0 |

|------------|----|----|----|-----|------|-----|---|

| read/write | 1  | 0  | 1  | COL | INCG | CSL | 0 |

| Field | Bits | Type | Description                                                       |

|-------|------|------|-------------------------------------------------------------------|

| INCG  | 2    | rw   | Input Drive Configuration                                         |

|       |      |      | Direct drive mode                                                 |

|       |      |      | 1 Assigned drive mode                                             |

| COL   | 3    | rw   | Input Combinatorial Logic Configuration                           |

|       |      |      | <b>0</b> Input signal OR-combined with according OUT register bit |

|       |      |      | 1 Input signal AND-combined with according OUT register bit       |

# 7 Protection Functions

The device provides embedded protective functions, which are designed to prevent IC destruction under fault conditions described in this data sheet. Fault conditions are considered as "outside" normal operating range. Protective functions are neither designed for continuous nor for repetitive operation.

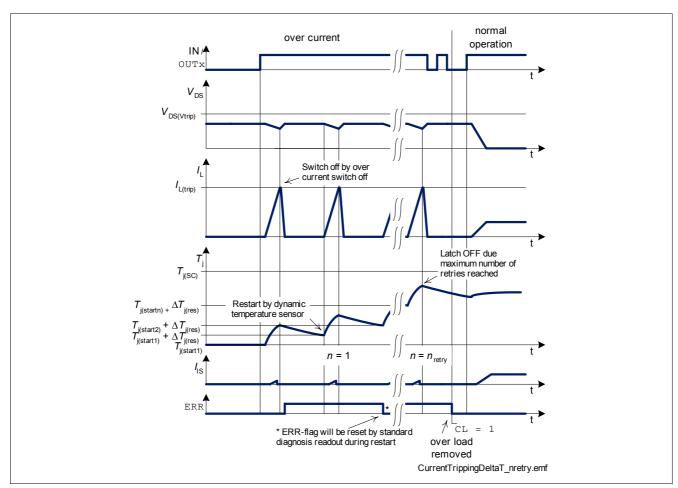

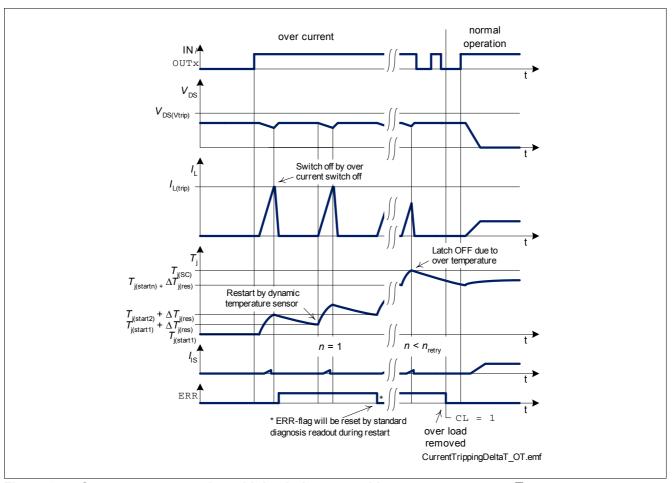

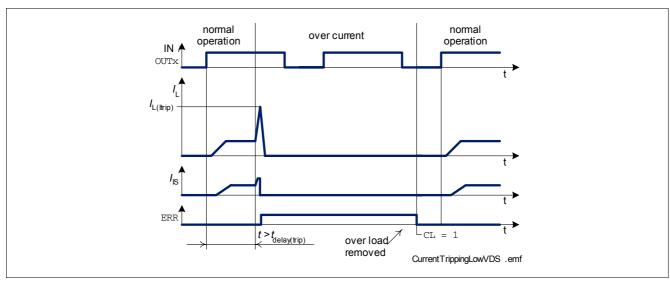

# 7.1 Over Current Protection

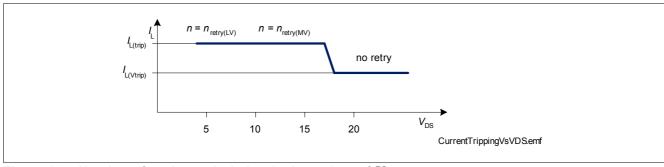

The maximum load current  $I_{\rm L}$  is switched off in case of exceeding the over current trip level  $I_{\rm L(trip)}$  by the device itself. Depending on the total short circuit impedance higher current over shoots may occur. A limited auto-restart function is implemented. The number of restarts is dependent of the  $V_{\rm DS}$  voltage. Please refer to following figures for details.

Figure 8 Over current protection with latch due to reaching maximum number of retries  $n_{\text{retry}}$

Figure 9 Over current protection with latch due to reaching over temperature  $T_{i(SC)}$

The ERR-flag will be set during over current shut down. It can be reset by reading the ERR-flag. If the channel is still in over current shut down, the ERR-flag will be set again. During the automatic restart of the channel the ERR-flag can be cleared by reading the ERR-flag. It will be set again as soon as the over current protection is activated again.

The number of restarts  $n_{\text{retry}}$  is depending on the  $V_{\text{DS}}$  voltage according to the following figure and Chapter 7.2.

Figure 10 Number of retries and trip levels dependent of  $V_{

m DS}$

The retry latch or over temperature latch is cleared by SPI command  $HWCR.CL = 1_b$ . If the input pin or the bit in the SPI register OUT is still set, the channel will be turned on immediately after the command  $HWCR.CL = 1_b$ .

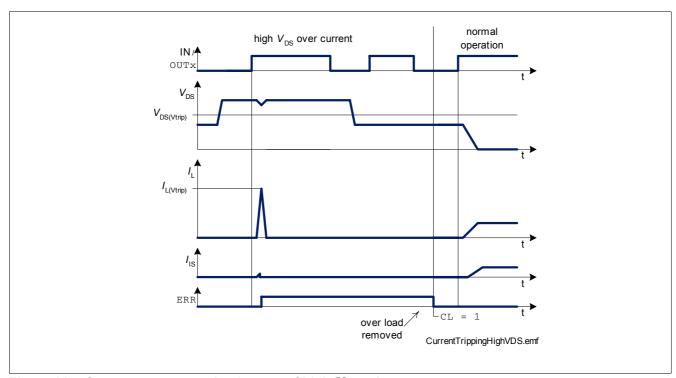

# 7.2 Over Current Protection at high $V_{DS}$

The SPOC - BTS5460SF provides an over current protection for  $V_{\rm DS} > V_{\rm DS(Vtrip)}$  (7.9.5). For  $V_{\rm DS} > V_{\rm DS(Vtrip)}$  and  $I_{\rm L} > I_{\rm L(Vtrip)}$  during turn on the channel switches off and latches immediately. For details please refer to parameter  $I_{\rm L(VTRIP)}$  (7.9.4).

The current trip level  $I_{\text{L(Vtrip)}}$  is below the current trip level  $I_{\text{L(trip)}}$  at  $V_{\text{DS}}$  = 7V. The ratio between  $I_{\text{L(trip)}}$  and  $I_{\text{L(Vtrip)}}$  is defined by the parameter  $\Delta k_{\text{TR}}$  (7.9.6).

The over current latch is cleared by SPI command  $HWCR.CL = 1_b$ . If the input pin or the bit in the SPI register OUT is still set, the channel will be turned on immediately after the command  $HWCR.CL = 1_b$ .

Figure 11 Over current protection in case of high  $V_{

m DS}$  voltages

# 7.3 Over Current Protection for Short Circuit Type 2 Protection

After activation of the channels without over temperature shutdown and after the delay time  $t_{\rm delay(trip)}$  (7.9.2) the over current protection threshold  $I_{\rm L(trip)}$  is reduced to  $I_{\rm L(ltrip)}$ . The delay time  $t_{\rm delay(trip)}$  is reset by an dynamic temperature sensor or over current shutdown and any INor OUTx. In case of a short circuit to GND event with  $I_{\rm L} > I_{\rm L(ltrip)}$  (7.9.3), which occurs in the on state, the channel is switched off and latched immediately. For more details, please refer to the figure Figure 12.

The current trip level  $I_{\text{L(Itrip)}}$  is below the current trip level  $I_{\text{L(trip)}}$  at  $V_{\text{DS}}$  = 7V. The ratio between  $I_{\text{L(trip)}}$  and  $I_{\text{L(Itrip)}}$  is defined by the parameter  $\Delta k_{\text{TR}}$  (7.9.6).

The over current latch is cleared by SPI command  $HWCR.CL = 1_b$ . If the input pin or the bit in the SPI register OUT is still set, the channel will be turned on immediately after the command  $HWCR.CL = 1_b$ .

Figure 12 Shut Down by Over Current due to Short Circuit Type 2

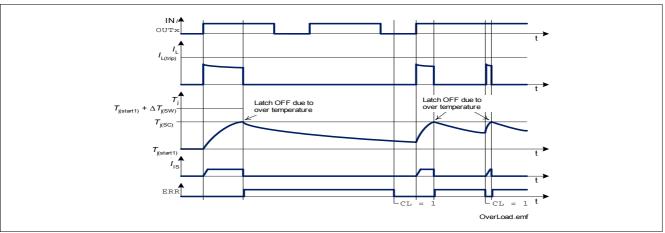

#### 7.4 Over Temperature Protection

Each channel has its own temperature sensor. If the temperature at the channel exceeds the thermal shutdown temperature  $T_{\rm j(SC)}$ , the channel will switch off and latch to prevent destruction (also in case of  $V_{\rm DD}$  = 0V). In order to reactivate the channel, the temperature at the output must drop by at least the thermal hysteresis  $\Delta T_{\rm j}$  and the over temperature latch must be cleared by SPI command  ${\rm HWCR.CL} = 1_{\rm b}$ . If the input pin or the bit in the SPI register OUT is still set, the channel will be turned on immediately after the command  ${\rm HWCR.CL} = 1_{\rm b}$ .

Figure 13 Shut Down by Over Temperature

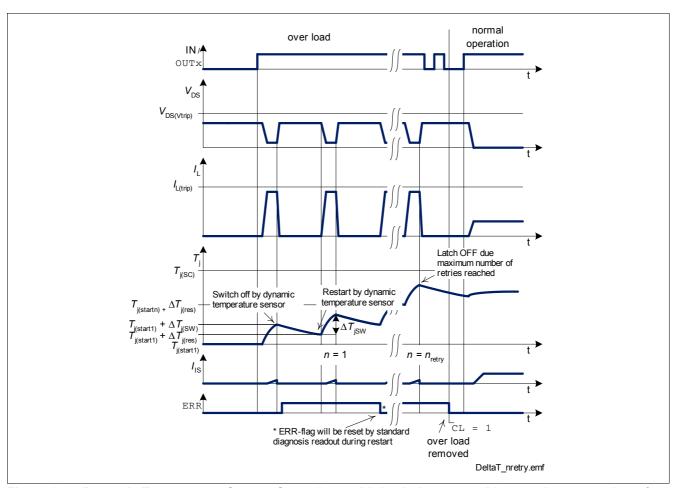

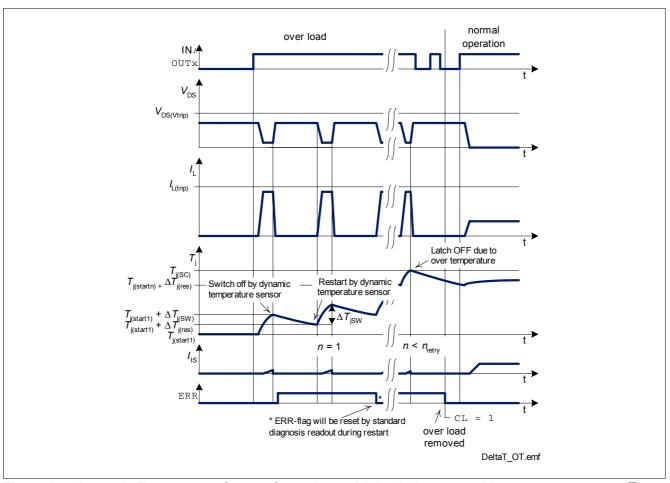

# 7.4.1 Dynamic Temperature Sensor Protection

Additionally, each channel has its own dynamic temperature sensor. The dynamic temperature sensor improves short circuit robustness by limiting sudden increases in the junction temperature. The dynamic temperature sensor turns off the channel if its sudden temperature increase exceeds the dynamic temperature sensor threshold  $\Delta T_{\rm j(SW)}$ . The number of automatic reactivations is limited by  $n_{\rm retry}$  (7.9.7). If this number of retries is exceeded the channel turns off and latches. The retry latch is cleared by SPI command  ${\rm HWCR.CL} = 1_{\rm b}$ . If the input pin or the bit in the SPI register  ${\rm OUT}$  is still set, the channel will be turned on immediately after the command  ${\rm HWCR.CL} = 1_{\rm b}$ . For the condition  $n < n_{\rm retry}$  the counter of automatic reactivations will be reset by every low to high transition on the input pin or the bit in SPI register  ${\rm OUT}$ .

Please refer to Figure 12 for details.

Figure 14 Dynamic Temperature Sensor Operations with latch due to reaching maximum number of retries  $n_{\rm retry}$

Figure 15 Dynamic Temperature Sensor Operations with latch due to reaching over temperature  $T_{i(SC)}$

The ERR-flag will be set during dynamic temperature sensor shut down. It can be reset by reading the ERR-flag. If the channel is still in dynamic temperature sensor shut down, the ERR-flag will be set again. During the automatic restart of the channel the ERR-flag can be cleared by reading the ERR-flag. It will be set again as soon as the dynamic temperature sensor is activated again.

#### 7.5 Reverse Polarity Protection

In reverse polarity mode, power dissipation is caused by the intrinsic body diode of each DMOS channel as well as each ESD diode of the logic pins. The reverse current through the channels has to be limited by the connected loads. The current through the ground pin, sense pin IS, the logic power supply pin VDD, the SPI pins, input pins and the limp home input pin has to be limited as well (please refer to the maximum ratings listed on Page 10).

For reducing the power loss during reverse polarity Reversave<sup>TM</sup> functionality is implemented for all channels. They are turned on to almost forward condition in reverse polarity condition, see parameter  $R_{DS(REV)}$ .

Note: No protection mechanism like temperature protection or current protection is active during reverse polarity.

# 7.6 Over Voltage Protection

In the case of supply voltages between  $V_{\rm BB(SC)\,max}$  and  $V_{\rm BB(CL)}$  the output transistors are still operational and follow the input or the OUT register. Parameters are not warranted and lifetime is reduced compared to normal mode.

In addition to the output clamp for inductive loads as described in **Section 6.3**, there is a clamp mechanism available for over voltage protection for the logic and all channels.

# 7.7 Loss of Ground

In case of complete loss of the device ground connections, but connected load ground, the SPOC - BTS5460SF securely changes to or stays in OFF-state.

# 7.8 Loss of $V_{\rm BB}$

In case of loss of  $V_{\rm BB}$  connection in on-state, all inductances of the loads have to be demagnetized through the ground connection or through an additional path from VBB to ground. For example, a suppressor diode is recommended between VBB and GND.

# 7.9 Electrical Characteristics

# **Electrical Characteristics Protection Functions**

| Pos.  | Parameter                                                   | er Symbol Limit Values   |      |      | ues  | Unit | Test Conditions                              |

|-------|-------------------------------------------------------------|--------------------------|------|------|------|------|----------------------------------------------|

|       |                                                             |                          | min. | typ. | max. |      |                                              |

| Over  | Load Protection                                             |                          |      |      |      |      |                                              |

| 7.9.1 | Load current trip level                                     | $I_{L(trip)}$            |      |      |      | Α    | $V_{\rm DS}$ < 7 V                           |

|       | channel 0, 1                                                |                          | 71   | _    | 120  |      | $T_{\rm j} = -40  ^{\circ}{\rm C}$           |

|       |                                                             |                          | _    | 90   | _    |      | $T_{i} = 25  ^{\circ}\text{C}$               |

|       |                                                             |                          | 67   | -    | 100  |      | $T_{\rm j}$ = 150 °C                         |

|       | channel 2, 3                                                |                          |      |      |      |      | HWCR.LEDn = 0                                |

|       |                                                             |                          | 29   | _    | 44   |      | $T_{\rm j}$ = -40 °C                         |

|       |                                                             |                          | _    | 30   | _    |      | $T_{\rm j} = 25  ^{\circ}{\rm C}$            |

|       |                                                             |                          | 23   | -    | 39   |      | $T_{\rm j}$ = 150 °C                         |

|       |                                                             |                          |      |      |      |      | HWCR.LEDn = 1                                |

|       |                                                             |                          | 7    | -    | 12   |      | $T_{\rm j} = -40  ^{\circ}{\rm C}$           |

|       |                                                             |                          |      | 8.5  | -    |      | $T_{\rm j} = 25  ^{\circ}{\rm C}$            |

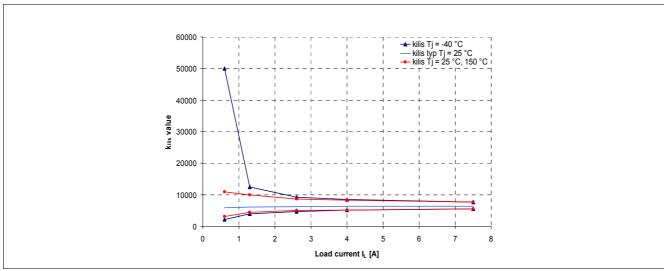

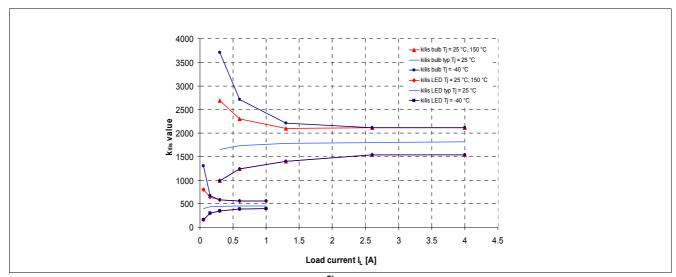

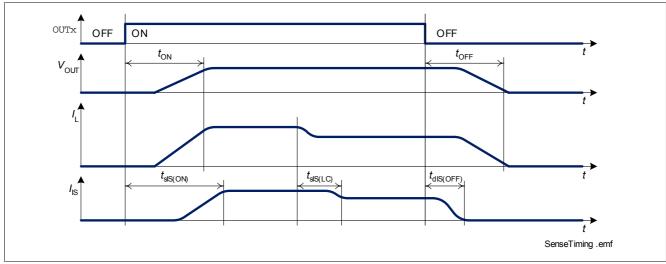

|       |                                                             |                          | 5.5  | _    | 11   |      | $T_{\rm j}$ = 150 °C                         |