# Data Sheet

# 5-Port SPoE PSE Controller

#### **FEATURES**

- ▶ IEEE 802.3cg-compliant SPoE PSE

- ▶ Five independent PSE ports

- Wide input-supply operating range: 6 V to 60 V

- Adjustable source and return electronic circuit breakers

- 52 µA (typical) and 51 µA (typical) input supply current in sleep and disabled states, respectively

- Charge pump enhances the external, high-side, N-channel MOS-FETs

- Supports SCCP with external microcontroller

- SPI bus interface with PEC

- Voltage, current, and temperature telemetry

- Per port power-good comparators

- ▶ PD sleep, wake-up, and wake-up forwarding support

- ► Available in 48-lead, 7 mm × 7 mm, QFN package

#### **APPLICATIONS**

- Operational technology (OT) systems

- Building and factory automation systems

- ► Field instruments and switches

- Security systems

- Traffic control systems

#### **GENERAL DESCRIPTION**

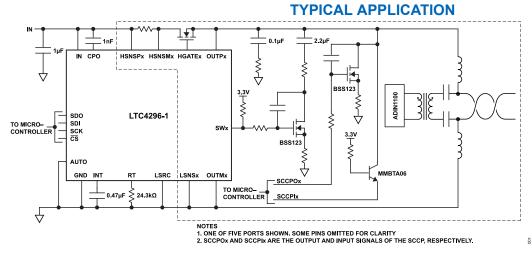

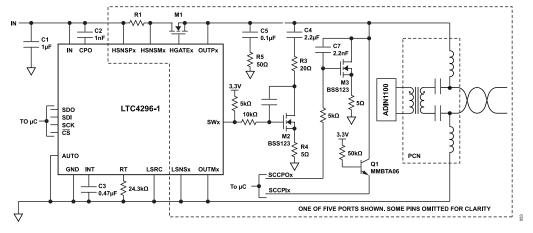

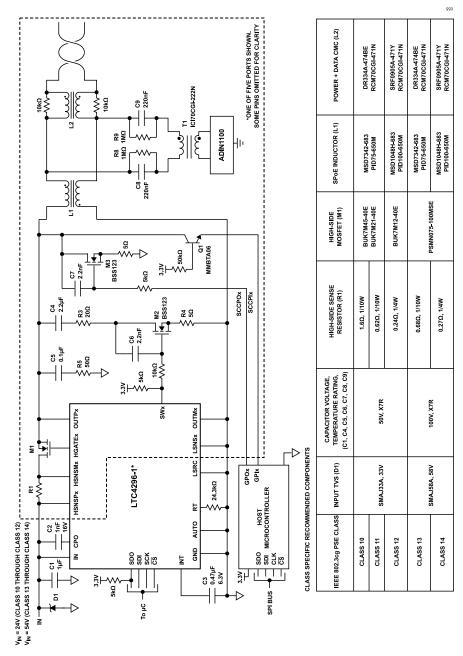

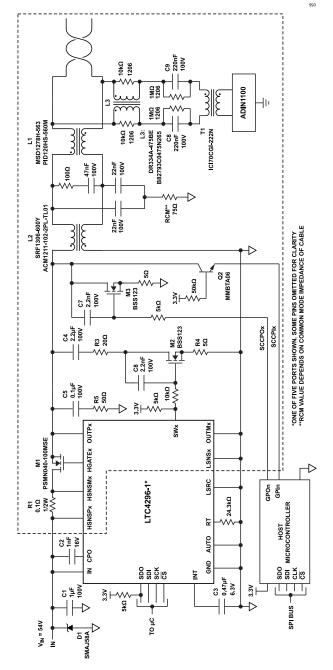

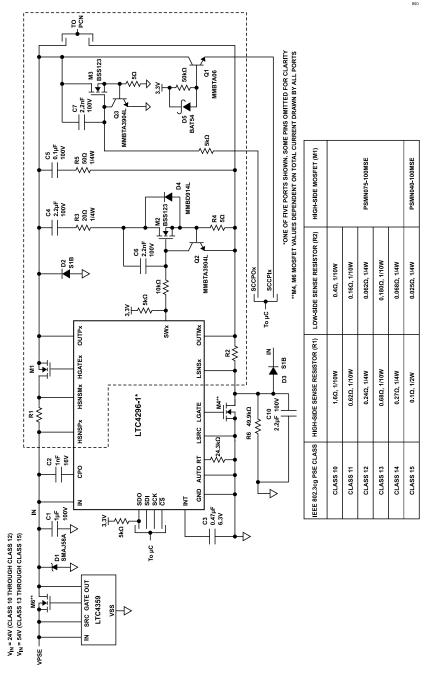

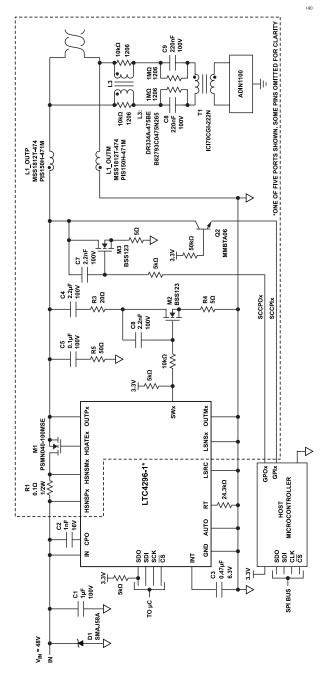

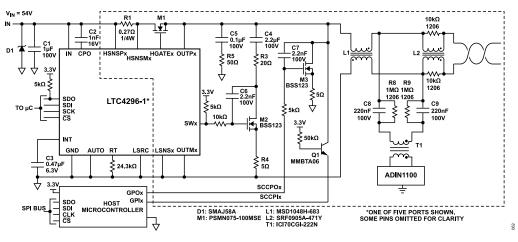

The LTC4296-1 is an IEEE 802.3cg-compliant, five port, single-pair power over Ethernet (SPoE), power sourcing equipment (PSE) controller. SPoE simplifies system design and installation with standardized power and Ethernet data over a single-pair cable. The LTC4296-1 is designed for interoperability with 802.3cg powered devices (PDs) in 24 V or 54 V systems. The LTC4296-1 delivers power using external, low drain-to-source on resistance (R<sub>DS(ON)</sub>), N-channel metal-oxide semiconductor field-effect transistors (MOS-FETs), which minimize voltage drop and ensure application rugged-ness.

High-side circuit breakers with foldback, analog current limit (ACL) provide controlled inrush and short-circuit protection. An optional low-side circuit breaker protects the negative output against back-feed faults, and ground faults in nonisolated applications. PD classification via the serial communication classification protocol (SCCP) and maintain full voltage signature (MFVS) ensure that the full operating voltage is only applied to the cable when a PD is present. The SWx pins disconnect port power snubbers during detection and classification. PD initiated sleep and wake-up are supported. The WAKEUP pin supports wake-up forwarding. Telemetry, status, and software control features are accessed via a serial peripheral interface (SPI) bus interface with packet error code (PEC) protection.

The LTC4296-1 provides a versatile SPoE, PSE solution for 10BASE-T1L controllers and switches and can easily be integrated with the Analog Devices, Inc., 10BASE-T1L transceiver portfolio, such as the ADIN1100 (physical layer, PHY), ADIN1110 (MAC-PHY), and ADIN2111 (2-port switch).

Figure 1. IEEE 802.3cg-Compliant, SPoE PSE

Rev. 0

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features1                                      |

|------------------------------------------------|

| Applications1                                  |

| General Description1                           |

| Typical Application1                           |

| Electrical Characteristics                     |

| Timing Diagram6                                |

| Absolute Maximum Ratings7                      |

| Thermal Resistance7                            |

| ESD Caution7                                   |

| Pin Configuration and Functional Descriptions8 |

| Typical Performance Characteristics10          |

| Theory of Operation17                          |

| Overview17                                     |

| Usage Cases20                                  |

| Port State Descriptions21                      |

| Host Serial Interface23                        |

| Sample Code25                                  |

| Register Map27                                 |

| Global Events28                                |

| Global Status29                                |

| Global Command29                               |

#### **REVISION HISTORY**

1/2023—Revision 0: Initial Version

| Configuration                | 29   |

|------------------------------|------|

| Global ADC                   |      |

| Port x Events                | 31   |

| Port x Status                | 31   |

| Port x Configuration         | 31   |

| Port x Diagnosis             |      |

| Applications Information     |      |

| Överview                     |      |

| Power Supply                 | 35   |

| External Component Selection |      |

| MDI Fault Tolerance          |      |

| Layout Guidelines            | 41   |

| Data Converters              |      |

| Isolation Considerations     | 42   |

| Low-Droop Applications       | 43   |

| Class 14 Typical Application | 44   |

| Related Parts                | 44   |

| Outline Dimensions           | . 45 |

| Ordering Guide               | 45   |

| Evaluation Boards            |      |

|                              |      |

Specifications apply over the full operating temperature range, and the input supply voltage ( $V_{IN}$ ) = 6 V and 60 V, unless otherwise noted. Pin voltages are referred to as  $V_{PIN}$ , and pin currents are referred to as  $I_{PIN}$ , where PIN is the name of pin. All currents into the device pins are positive, and all currents out of the device pins are negative. All voltages are referenced to GND, unless otherwise specified.

| Table 1. | Electrical | Characteristics |

|----------|------------|-----------------|

|----------|------------|-----------------|

| Parameter                                                                      | Test Conditions/Comments                                                                                                                           | Min                   | Тур   | Max             | Unit |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------|------|

| IN                                                                             |                                                                                                                                                    |                       |       |                 |      |

| Input Supply Operating Range, V <sub>IN</sub>                                  |                                                                                                                                                    | 6                     |       | 60              | V    |

| Input Supply Current, I <sub>IN</sub>                                          | All ports in power-on state                                                                                                                        |                       | 6.5   | 10              | mA   |

|                                                                                | All ports in sleep state, serial bus idle                                                                                                          |                       | 52    | 140             | μA   |

|                                                                                | All ports in disabled state, serial bus idle                                                                                                       |                       | 51    | 135             | μA   |

|                                                                                | All ports in detection state                                                                                                                       |                       | 80    | 90              | mA   |

| INT                                                                            |                                                                                                                                                    |                       |       |                 |      |

| INT Voltage, V <sub>INT</sub>                                                  | I <sub>INT</sub> = 0 μA or −100 μA                                                                                                                 | 4.1                   | 4.3   | 4.5             | V    |

| HSNSPx and HSNSMx                                                              |                                                                                                                                                    |                       |       |                 |      |

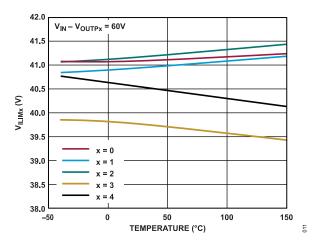

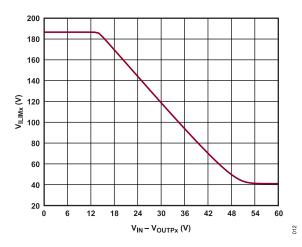

| Analog Foldback Current-Limit Threshold, $V_{\text{ILIMx}}$                    | V <sub>ILIMx</sub> = V <sub>HSNSPx</sub> - V <sub>HSNSMx</sub> , V <sub>IN</sub> - V <sub>OUTPx</sub> < 12 V, V <sub>HSNSPx</sub> = 6<br>V or 60 V | 177                   | 186   | 193             | mV   |

|                                                                                | V <sub>IN</sub> – V <sub>OUTPx</sub> = 60 V, V <sub>HSNSPx</sub> = 60 V                                                                            | 37                    | 41    | 46              | mV   |

| HSNSPx Input Current, IIN_HSNSPx                                               | $V_{IN} = V_{HSNSPx} = V_{HSNSMx} = 60 V$                                                                                                          |                       | 95    | 190             | μA   |

| HSNSMx Input Current, I <sub>IN HSNSMx</sub>                                   | $V_{IN} = V_{HSNSPx} = V_{HSNSMx} = 60 V$                                                                                                          |                       | 66    | 128             | μA   |

| LSNS0                                                                          |                                                                                                                                                    |                       |       | -               |      |

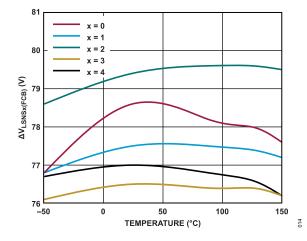

| Port 0 Forward Circuit Breaker Threshold, ΔV <sub>LSNS0(FCB)</sub>             | $\Delta V_{\text{LSNS0(FCB)}} = V_{\text{OUTM0}} - V_{\text{LSNS0}}$                                                                               | 60                    | 76    | 90              | mV   |

| Port 0 Reverse Circuit Breaker Threshold, $\Delta V_{LSNS0(RCB)}$              | $\Delta V_{\text{LSNS0}(\text{FCB})} = V_{\text{OUTM0}} = V_{\text{LSNS0}}$                                                                        | 60                    | 76    | 90              | mV   |

| Deep Sleep Return Path Reverse Fault Threshold, AvLSNS0(RCB)                   | All ports in sleep and disabled state, serial bus idle, $V_{SLP(RCB)} =$                                                                           | -1.2                  | -0.87 | -0.25           | V    |

| V <sub>SLP(RCB)</sub>                                                          | All ports in sleep and disabled state, senar bus idle, $v_{SLP(RCB)} = V_{LSNS0}$                                                                  | -1.2                  | -0.07 | -0.20           | v    |

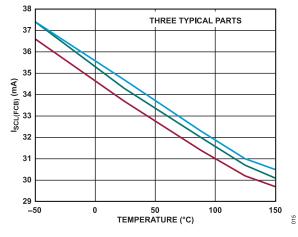

| V SLP(RCB)<br>Deep Sleep Return Path Forward Fault Threshold,                  | All ports in sleep and disabled state, serial bus idle                                                                                             | 15                    | 34    | 45              | mA   |

| I <sub>SLP(FCB)</sub>                                                          |                                                                                                                                                    |                       | υT    | 10              |      |

| Deep Sleep Return Path Short Circuit Current, I <sub>SLP_LSNS0</sub>           | All ports in sleep and disabled state, serial bus idle, $V_{LSNS0}$ = 2.5 V                                                                        | 40                    | 79    | 110             | mA   |

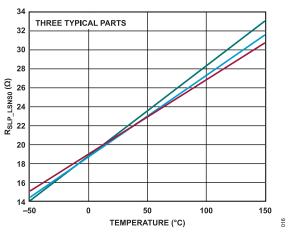

| Deep Sleep Return Path Impedance, $R_{SLP\_LSNS0}$                             | All ports in sleep and disabled state, serial bus idle, $I_{LSNS0} = 10$ mA                                                                        | 17                    | 22    | 45              | Ω    |

| LSNS1/SNS2 and LSNS3/LSNS4                                                     |                                                                                                                                                    |                       |       |                 |      |

| Forward Circuit Breaker Threshold, $\Delta V_{LSNSx(FCB)}$                     | $\Delta V_{\text{LSNSx(FCB)}} = V_{\text{OUTMx}} - V_{\text{LSNSx}}$                                                                               | 60                    | 76    | 90              | mV   |

| Reverse Circuit Breaker Threshold, $\Delta V_{LSNSx(RCB)}$                     | $\Delta V_{\text{LSNSx}(\text{RCB})} = V_{\text{LSNSx}} - V_{\text{OUTMx}}$                                                                        | 60                    | 76    | 90              | mV   |

| Input Current, I <sub>LSNSx</sub>                                              | $V_{LSNSx} = -0.1 \text{ V or } +0.1 \text{ V},  \text{T}_{\text{A}} = 25^{\circ}\text{C}$                                                         |                       | -2.5  |                 | μA   |

| HGATEX                                                                         |                                                                                                                                                    |                       |       |                 |      |

| External Port Source Path N-Channel MOSFET Gate<br>Drive, ΔV <sub>HGATEx</sub> | AUTO high, $\Delta V_{HGATEx} = V_{HGATEx} - V_{OUTPx}$ , $I_{HGATEx} = 0 \ \mu A \text{ or } -1 \ \mu A$                                          | 9.3                   | 10.2  | 10.6            | V    |

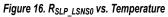

| HGATEx Pull-Up Current, I <sub>HGATEx UP</sub>                                 | Power-on state, $\Delta V_{HGATEx} = 3 V$                                                                                                          | -45                   | -34   | -28             | μA   |

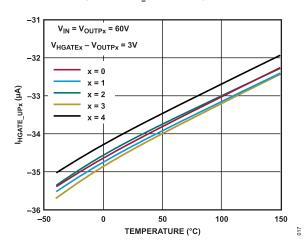

| HGATEX Fast Pull-Down Current, I <sub>HGATEX FAST</sub>                        | Power-on state, $V_{HSNSPx} - V_{HSNSMx} = 0.3 V$ , $\Delta V_{HGATEx} = 3 V$                                                                      | 40                    | 72    | 150             | mA   |

| HGATEX Slow Pull-Down Current, I <sub>HGATEX_SLOW</sub>                        | Disabled state, $\Delta V_{HGATEx} = 1.5 V$ , $V_{OUTPx} = 0 V$                                                                                    | 8                     | 16    | 24              | mA   |

|                                                                                | Disabled state, $\Delta V_{HGATEX} = 1.5 \text{ V}$ , $V_{OUTPX} = 0.7 \text{ V}$                                                                  | 40                    | 110   | 185             | μA   |

| HGATEx Fast Pull-Down Dropout Voltage,                                         | Power-on state, $V_{OUTPx} = 0.V$ , $I_{HGATEx} = 1.3 v$ , $V_{OUTPx} = -2 v$                                                                      | то                    | 1.1   | 1.4             | V    |

| VPULLDOWN_FASTx                                                                | $V_{\text{HSNSMx}} = 0.3 \text{ V}$                                                                                                                |                       | 1.1   | 1.7             | , v  |

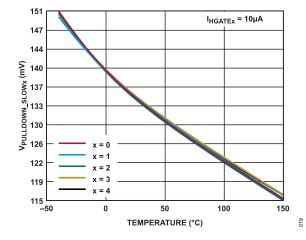

| HGATEx Slow Pull-Down Dropout Voltage,                                         | Disabled state, $V_{OUTPx} = 0$ V, $I_{HGATEx} = 10 \ \mu A$                                                                                       |                       | 0.14  | 0.3             | V    |

| VPULLDOWN_SLOWX                                                                | - HOAIEX TO PIT                                                                                                                                    |                       | 0.71  | 0.0             |      |

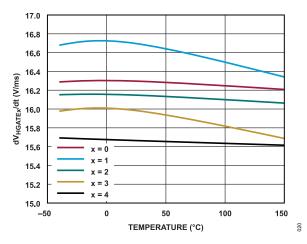

| HGATEX Inrush Slew Rate, dV <sub>HGATEX</sub> /dt                              | Power-on state, V <sub>HSNSPx</sub> – V <sub>HSNSMx</sub> < 30 mV                                                                                  | 14                    | 16.5  | 19              | V/ms |

| -GATE                                                                          |                                                                                                                                                    |                       |       | -               |      |

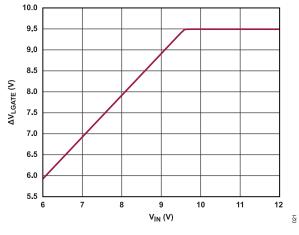

| External Return Path N-Channel Gate Drive, $\Delta V_{LGATE}$                  | Power-on state, 6 V < $V_{IN}$ < 8.6 V, $I_{LGATE}$ = 0 $\mu$ A or –1 $\mu$ A                                                                      | V <sub>IN</sub> – 0.2 |       | V <sub>IN</sub> | V    |

|                                                                                | Power-on state, $V_{IN} \ge 8.6$ V, $I_{LGATE} = 0$ mA or $-1$ mA                                                                                  | 8.25                  | 9.5   | 9.8             | v    |

| LGATE Pull-Up Current, ILGATE(UP)                                              | AUTO high, $V_{LGATE} - V_{LSRC} = 3 V$                                                                                                            | -3.3                  | -2.2  | -0.6            | mA   |

| ()                                                                             |                                                                                                                                                    |                       |       |                 |      |

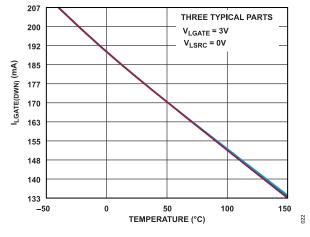

| LGATE Pull-Down Current, I <sub>LGATE(DWN)</sub>                               | LGATE disabled, $V_{LGATE}$ = 3 V, $V_{LSRC}$ = 0 V                                                                                                | 70                    | 180   | 270             | mA   |

#### Table 1. Electrical Characteristics (Continued)

| Parameter                                                                                   | Test Conditions/Comments                                            | Min  | Тур   | Max  | Unit   |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-------|------|--------|

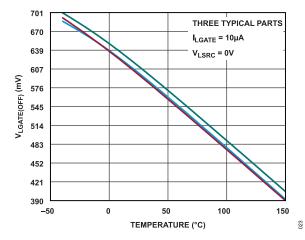

| LGATE Pull-Down Voltage, V <sub>LGATE(OFF)</sub>                                            | LGATE disabled, I <sub>LGATE</sub> = 10 µA, V <sub>LSRC</sub> = 0 V |      | 0.6   | 1    | V      |

| AUTO                                                                                        |                                                                     |      |       |      |        |

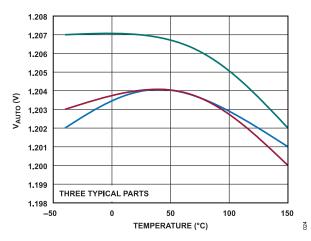

| Input Threshold Voltage, V <sub>AUTO</sub>                                                  | V <sub>AUTO</sub> rising                                            | 1.15 | 1.205 | 1.25 | V      |

| Input Hysteresis                                                                            | $V_{AUTO}$ falling, $T_A = 25^{\circ}C$                             |      | 11    |      | mV     |

| Input Current, I <sub>AUTO</sub>                                                            | V <sub>AUTO</sub> = 5.5 V                                           | -100 |       | +100 | nA     |

| Pulse Width of Spike Suppressed, t <sub>SP AUTO</sub>                                       | Positive going spike, T <sub>A</sub> = 25°C                         |      | 28    |      | μs     |

| -                                                                                           | Negative going spike, $T_A = 25^{\circ}C$                           |      | 7     |      | μs     |

| PORT SOURCE CURRENT READBACK ANALOG-TO-<br>DIGITAL CONVERTER (ADC)                          |                                                                     |      |       |      |        |

| Resolution <sup>1</sup>                                                                     | T <sub>A</sub> = 25°C                                               |      | 11    |      | Bits   |

| Full-Scale                                                                                  | T <sub>A</sub> = 25°C                                               |      | 204.8 |      | mV     |

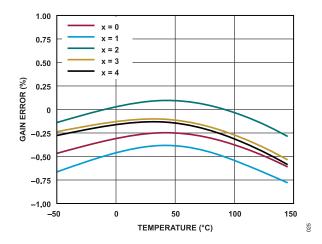

| Gain Error <sup>2</sup>                                                                     | V <sub>HSNSPx</sub> – V <sub>HSNSMx</sub> < 200 mV                  |      |       | ±2.5 | %      |

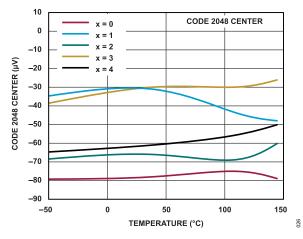

| Offset <sup>2</sup>                                                                         | Code 2048 center                                                    | -250 | -50   | 150  | μV     |

| Integral Nonlinearity (INL) <sup>2</sup>                                                    |                                                                     |      |       | ±1   | LSB    |

| Conversion Time <sup>3</sup>                                                                |                                                                     | 3.3  | 3.6   | 4    | ms     |

| V <sub>IN</sub> , PORT OUTPUT VOLTAGE, AND PORT RETURN<br>CURRENT READBACK ADC (GLOBAL ADC) |                                                                     |      |       |      |        |

| Resolution <sup>1</sup>                                                                     | T <sub>A</sub> = 25°C                                               |      | 11    |      | Bits   |

| Voltage Readback Full-Scale                                                                 | $V_{OUTPx} - V_{OUTMx}$ , $V_{IN}$ , low gain, $T_A = 25^{\circ}C$  |      | 72.09 |      | V      |

|                                                                                             | $V_{OUTPx} - V_{OUTMx}$ , $V_{IN}$ , high gain, $T_A = 25^{\circ}C$ |      | 36.04 |      | V      |

| Current Readback Full-Scale                                                                 | $V_{OUTMx} - V_{LSNSx}, T_A = 25^{\circ}C$                          |      | 204.8 |      | mV     |

| Full-Scale Gain Error                                                                       | T <sub>A</sub> = 25°C                                               |      | ±2.5  |      | %      |

| Offset                                                                                      | Code 2048 center, $T_A = 25^{\circ}C$                               |      | ±1    |      | LSB    |

| INL                                                                                         | T <sub>A</sub> = 25°C                                               |      | ±1    |      | LSB    |

| Conversion Time <sup>3</sup>                                                                |                                                                     | 3.3  | 3.6   | 4    | ms     |

| NTERNAL CHECK VOLTAGE REFERENCE                                                             |                                                                     |      |       |      |        |

| ACCESSIBLE THROUGH THE GLOBAL ADC)                                                          |                                                                     |      |       |      |        |

| Code                                                                                        | T <sub>A</sub> = 25°C                                               |      | 3548  |      | LSB    |

| Tolerance                                                                                   |                                                                     |      |       | ±3.5 | %      |

| Conversion Time <sup>3</sup>                                                                |                                                                     | 3.3  | 3.6   | 4    | ms     |

| NTERNAL TEMPERATURE SENSOR (ACCESSIBLE<br>THROUGH THE GLOBAL ADC)                           |                                                                     |      |       |      |        |

| Weight                                                                                      | T <sub>A</sub> = 25°C                                               |      | 0.25  |      | °C/LSE |

| Error                                                                                       | T <sub>A</sub> = 25°C                                               |      | ±5    |      | °C     |

| Conversion Time <sup>3</sup>                                                                |                                                                     | 3.3  | 3.6   | 4    | ms     |

| SDI, SCK, and CS                                                                            |                                                                     |      |       |      |        |

| Digital Input Low Voltage, V <sub>ILD</sub>                                                 |                                                                     |      |       | 0.8  | V      |

| Digital Input High Voltage, V <sub>IHD</sub>                                                |                                                                     | 2    |       |      | V      |

| Input Current, I <sub>SPI</sub>                                                             | $V_{SDI}$ , $V_{SCK}$ , and $V_{CS}$ = 5.5 V                        | -1   |       | +1   | μA     |

| SDO and SWx                                                                                 |                                                                     |      |       |      |        |

| Output Low Voltage, V <sub>OL</sub>                                                         | I <sub>SDO</sub> , I <sub>SWX</sub> = 3 mA                          |      |       | 0.4  | V      |

| Output Leakage Current, ILEAK                                                               | $V_{\text{PIN}}$ = 5.5 V, where PIN denotes SDO or SWx              | -1   |       | +1   | μA     |

| THERMAL SHUTDOWN INTERNAL TEMPERATURE                                                       | T <sub>A</sub> = 25°C                                               |      |       |      |        |

| Junction, T <sub>SHUTDOWN</sub>                                                             |                                                                     |      | 175   |      | °C     |

| Junction Hysteresis, T <sub>SHUTDOWN(HYST)</sub>                                            |                                                                     |      | 30    |      | °C     |

| OUTPx and OUTMx                                                                             |                                                                     |      |       |      |        |

| Open-Circuit Detection Voltage, V <sub>OC</sub> <sup>2</sup>                                | Detection state, $I_{OUTPx} = 0 \ \mu A$                            | 5.05 | 5.2   | 5.5  | V      |

| Invalid PD Signature Voltage High Range, V <sub>BAD HI PSE</sub> <sup>2</sup>               | Detection state, invalid signature high threshold                   | 4.7  |       | 5    | V      |

| Invalid PD Signature Voltage Low Range, V <sub>BAD LO PSE</sub> <sup>2</sup>                | Detection state, invalid signature low threshold                    | 3.7  |       | 4.05 | V      |

#### Table 1. Electrical Characteristics (Continued)

| Parameter                                                                                 | Test Conditions/Comments                                                               | Min   | Тур   | Мах   | Unit |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|------|

| Sleep State Output Voltage, V <sub>SLEEP</sub> <sup>2</sup>                               | Sleep state, I <sub>OUTPx</sub> = 0 mA, -1.85 mA, or 100 µA                            | 3.15  | 3.4   | 3.575 | V    |

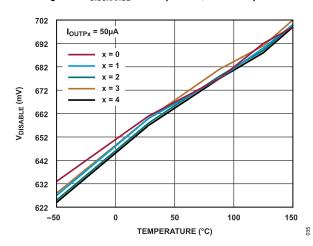

| Port Disabled Voltage at OUTPx, V <sub>DISABLE</sub> <sup>2</sup>                         | Port disabled, I <sub>OUTPx</sub> = 50 μA                                              |       |       | 1     | V    |

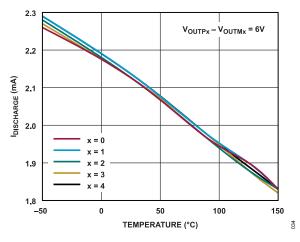

| OUTPx Discharge Current During Settle-Sleep State,<br>I <sub>DISCHARGE</sub> <sup>2</sup> | Settle-sleep state, I <sub>OUTPx</sub> , V <sub>OUTPx</sub> - V <sub>OUTMx</sub> = 6 V | 1.2   | 2.1   | 3.6   | mA   |

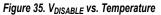

| Short-Circuit Current, I <sub>SC</sub> <sup>2</sup>                                       | Sleep state, I <sub>OUTPx</sub> , V <sub>OUTPx</sub> - V <sub>OUTMx</sub> = 0 V        | -6.8  | -5.5  | -4.25 | mA   |

| Valid Wake-Up Current Input Range, I <sub>WAKEUP</sub> <sup>2</sup>                       | Sleep state, I <sub>OUTPx</sub>                                                        | -1.85 |       | -1.25 | mA   |

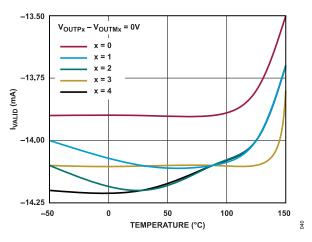

| Detection Probe Current Range, $I_{VAI ID}^2$                                             | Detection state, $V_{OUTPx} - V_{OUTMx} = 0 V$                                         | -16   | -14   | -12   | mA   |

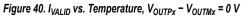

|                                                                                           | Detection state, $V_{OUTPx} - V_{OUTMx} = 4.7 V$                                       | -16   | -13   | -11   | mA   |

| High-Side Power-Good Threshold Voltage,                                                   | Portenabled, $\Delta V_{OUTPx} + V_{OUTPx} - V_{IN}$ , $V_{OUTMx} = 0 V$ ,             | 390   | 440   | 510   | mV   |

| $\Delta V_{OUTPx PWRGD}$                                                                  | V <sub>OUTPx</sub> rising                                                              | 000   | 110   | 010   |      |

| High-Side Power-Good Threshold Voltage Hysteresis,                                        | Port enabled, $V_{OUTPx}$ falling, $T_A = 25^{\circ}C$                                 |       | 22    |       | mV   |

| ΔV <sub>OUTPx_PWRGD(HYST)</sub>                                                           |                                                                                        |       |       |       |      |

| Low-Side Power-Good Threshold Voltage,                                                    | Port enabled, $\Delta V_{OUTMx_PWRGD} = V_{OUTMx}$ , $\Delta V_{OUTPx_PWRGD} = 0 V$    | 150   | 200   | 250   | mV   |

| ΔV <sub>OUTMx_PWRGD</sub>                                                                 |                                                                                        |       |       |       |      |

| <br>/AKEUP                                                                                |                                                                                        |       |       |       |      |

| Internal Pull-Up Current, I <sub>PU</sub>                                                 | V <sub>WAKEUP</sub> = 1.2 V                                                            | -125  | -100  | -75   | μA   |

| Internal Pull-Down Resistance, R <sub>PD</sub>                                            | $V_{WAKEUP} = 5.5 V$                                                                   | 0.4   | 1.2   | 2.25  | ΜΩ   |

| Internal Pull-Up Voltage, V <sub>OH</sub>                                                 | $I_{WAKEUP} = 0 \ \mu A \text{ or } 50 \ \mu A$                                        | 3.25  | 3.8   | 4.5   | V    |

| Input Threshold Voltage, V <sub>ITH</sub>                                                 | V <sub>WAKEUP</sub> rising                                                             | 1.15  | 1.205 | 1.25  | V    |

| Input Threshold Voltage Hysteresis, V <sub>ITH(HYST)</sub>                                | $V_{WAKEUP}$ falling, $T_A = 25^{\circ}C$                                              |       | 10    |       | mV   |

| Pulse Width of Spike Suppressed, t <sub>SP WAKEUP</sub>                                   | Positive going spike, $T_A = 25^{\circ}C$                                              |       | 30    |       | μs   |

| Tales Than of Chine Capp. Coost, SP_WAREDP                                                | Negative going spike, $T_A = 25^{\circ}C$                                              |       | 6     |       | μs   |

| ORT TIMING CHARACTERISTICS                                                                |                                                                                        |       | •     |       |      |

| Detection State Timeout, t <sub>DET</sub>                                                 | Detection state, invalid signature                                                     | 2.55  |       | 3.11  | ms   |

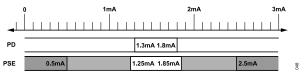

| Detection Signature Hold Time, t <sub>SIG HOLD</sub>                                      | Detection state, valid signature                                                       | 1     |       | 1.22  | ms   |

| Power-Up State Timeout Tolerance, t <sub>INRUSH TOL</sub>                                 | Power-up state, short-circuit, programmable                                            |       |       | ±7    | %    |

| Port Source Circuit Breaker Overload Fault Delay Time                                     | Programmable, $V_{HSNSPx} - V_{HSNSMx} > V_{ILIMx}$                                    |       |       | ±7    | %    |

| Tolerance, t <sub>LIM_TOL</sub>                                                           |                                                                                        |       |       |       |      |

| Port Return Circuit Breaker Delay Time, $t_{\mbox{LSNS}\_\mbox{FAULT}}$                   | $V_{LSNSx} = 1.2 V$                                                                    | 1.3   | 1.8   | 2.4   | μs   |

|                                                                                           | $V_{LSNSx} = -0.1 V$                                                                   | 2     | 4     | 6.3   | μs   |

| Overload Delay Tolerance, t <sub>OD_TOL</sub>                                             | Overload state, programmable                                                           |       |       | ±7    | %    |

| Port MFVS Valid Hold Time, t <sub>MFVS</sub>                                              | $V_{HSNSPx} - V_{HSNSMx} > V_{MFVS}$ , $V_{MFVS}$ programmable                         | 4     | 5     | 6     | ms   |

| Port MFVS Dropout Time, t <sub>MFVDO</sub>                                                | V <sub>HSNSPx</sub> - V <sub>HSNSMx</sub> < V <sub>MFVS</sub>                          | 300   | 350   | 400   | ms   |

| OUTPx Sleep Regulator Overload Fault Delay Time Tolerance, $t_{LIM\_SLEEP\_TOL}$          | Idle or sleep states, programmable                                                     |       |       | ±20   | %    |

| Restart Delay Tolerance, t <sub>RESTART TOL</sub>                                         | Restart state, programmable                                                            |       |       | ±7    | %    |

| Wake-Up Deglitch Time, t <sub>WAKEUP</sub>                                                |                                                                                        | 0.05  |       | 0.1   | ms   |

| Turn Off Time, t <sub>OFF</sub>                                                           | Settle-sleep to overload, V <sub>OUTPx</sub> = 5 V                                     | 409   |       | 500   | ms   |

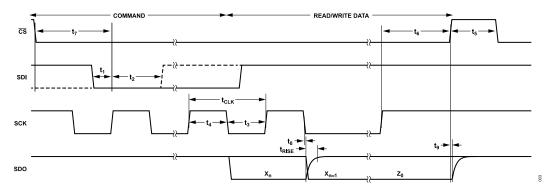

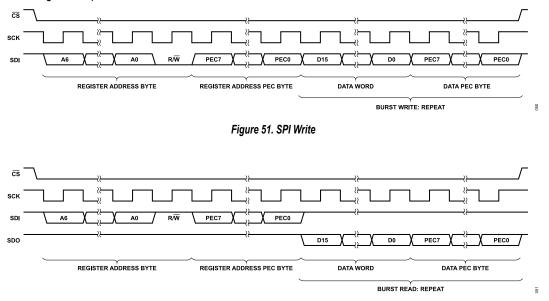

| PI BUS TIMING                                                                             |                                                                                        |       |       |       |      |

| SCK Frequency, 1/t <sub>CLK</sub>                                                         |                                                                                        |       |       | 1     | MHz  |

| SDI Setup Time Before SCK Rising Edge, t <sub>1</sub>                                     |                                                                                        | 26    |       |       | ns   |

| SDI Hold Time After SCK Rising Edge, t <sub>2</sub>                                       |                                                                                        | 25    |       |       | ns   |

| SCK Low, t <sub>3</sub>                                                                   |                                                                                        | 200   |       |       | ns   |

| SCK High, t <sub>4</sub>                                                                  |                                                                                        | 200   |       |       | ns   |

| $\overline{CS}$ Rising Edge to $\overline{CS}$ Falling Edge, t <sub>5</sub>               |                                                                                        | 650   |       |       | ns   |

| SCK Rising Edge to $\overline{CS}$ Rising Edge, t <sub>6</sub>                            |                                                                                        | 800   |       |       | ns   |

| $\overline{CS}$ Falling Edge to SCK Rising, t <sub>7</sub>                                |                                                                                        | 1     |       |       | μs   |

| SCK Falling Edge to SDO Valid, t <sub>8</sub> <sup>4</sup>                                |                                                                                        |       |       | 100   | ns   |

|                                                                                           |                                                                                        |       |       | 100   | 1113 |

- <sup>1</sup> Both port and global ADCs have a bipolar input range that is spanned by 11 bits plus a sign bit.

- $^2$  This specification is tested at V\_{IN} = 6 V. The operation at V\_{IN} = 60 V is guaranteed by design.

- <sup>3</sup> This specification is guaranteed by design.

- <sup>4</sup> This specification does not include the rise or fall time of the SDO. While the fall time (typically 5 ns due to the internal pull-down transistor) is not a concern, the rising-edge transition time, t<sub>RISE</sub>, is dependent on the pull-up resistance and load capacitance on the SDO pin.

# TIMING DIAGRAM

Figure 2. SPI Bus Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature is exceeded when this protection is active. Continuous operation more than the specified absolute maximum operating junction temperature can impair device reliability or permanently damage the device.

#### Table 2. Absolute Maximum Ratings

| Parameter                             | Rating          |

|---------------------------------------|-----------------|

| Supply Voltage                        |                 |

| IN                                    | –0.3 V to +80 V |

| INT                                   | –0.3 V to +6 V  |

| Input Voltages                        |                 |

| SDI, SCK, CS, AUTO, and RT            | –0.3 V to +6 V  |

| HSNSPx and HSNSMx                     | –0.3 V to +80 V |

| HSNSPx to HSNSMx                      | –5 V to +10 V   |

| OUTMx                                 | –5.5 V to +80 V |

| LSNSx                                 | –5.5 V to +80 V |

| OUTPx                                 | –5.5 V to +80 V |

| Output Voltages                       |                 |

| SDO, WAKEUP, and SWx                  | –0.3 V to +6 V  |

| LGATE to LSRC <sup>1</sup>            | –0.3 V to +15 V |

| LSRC                                  | –5.5 V to +4 V  |

| CPO to IN <sup>1</sup>                | –0.3 V to +15 V |

| HGATEx to OUTPx <sup>1</sup>          | –0.3 V to +15 V |

| Output Currents                       |                 |

| SDO and SWx                           | ±5 mA           |

| RT                                    | -10 mA to +1 mA |

| Temperature                           |                 |

| Operating Junction Range <sup>2</sup> | –40 to +125°C   |

| Storage Range                         | –65°C to +150°C |

| Lead (Soldering, 10 sec)              | 300°C           |

<sup>1</sup> Externally forced voltage absolute maximums. The LTC4296-1 can exceed these during normal operation.

<sup>2</sup> The LTC4296-1 is tested under pulsed load conditions such that T<sub>J</sub> ≈ T<sub>A</sub>. The LTC4296-1 is guaranteed over the –40°C to 125°C operating junction temperature range.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction-to-case thermal resistance.

#### Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| 05-08-7073   | 18              | 2.5             | °C/W |

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

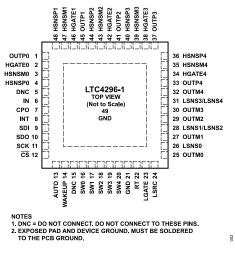

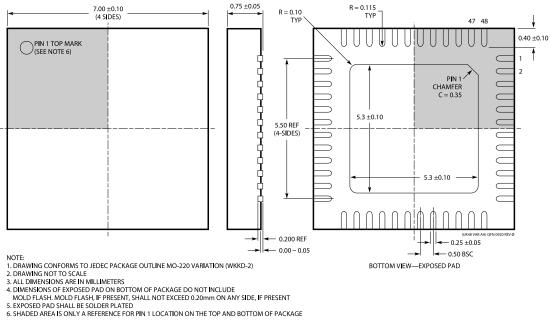

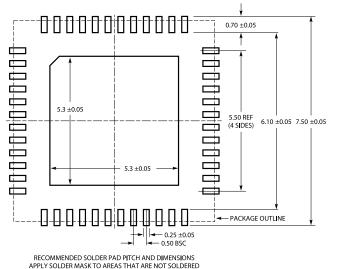

#### PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

Figure 3. Pin Configuration

#### Table 4. Pin Function Descriptions

| Pin No.           | Mnemonic <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 33, 37, 41, 45 | OUTPx                 | Port x Positive Output. Connect the OUTPx pin to the source of the Port x, top-side, external N-channel MOSFET. Do not connect the OUTPx pin if Port x is unused.                                                                                                                                                                                                                           |

| 2, 34, 38, 42, 46 | HGATEx                | Port x High-Side Gate Drive. Connect the HGATEx pin to the gate of the Port x, top-side, external N-channel MOSFET. Do not connect the HGATEx pin if Port x is unused.                                                                                                                                                                                                                      |

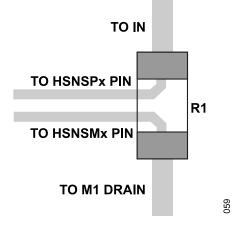

| 3, 35, 39, 43, 47 | HSNSMx                | Port x High-Side Kelvin Sense Negative Input. Connect the HSNSMx pin directly to the negative terminal of the Port x, top-side, current-sense resistor. Connect the sense-resistor negative terminal to the drain of the Port x, top-side, external N-channel MOSFET. If Port x is unused, connect the HSNSMx pin to the HSNSPx pin.                                                        |

| 4, 36, 40, 44, 48 | HSNSPx                | Port x High-Side Kelvin Sense Positive Input. Connect the HSNSPx pins directly to the positive terminal of the Port x, top-side, current-sense resistor. If Port x is unused, connect to IN.                                                                                                                                                                                                |

| 5, 15             | DNC                   | Do Not Connect. Do not connect to these pins.                                                                                                                                                                                                                                                                                                                                               |

| 6                 | IN                    | Supply Voltage Input.                                                                                                                                                                                                                                                                                                                                                                       |

| 7                 | CPO                   | Charge-Pump Output. Connect a 1 nF, 16 V capacitor from CPO to IN.                                                                                                                                                                                                                                                                                                                          |

| 8                 | INT                   | Internal 4.3 V Regulator Bypass. Connect a 470 nF bypass capacitor from INT to GND.                                                                                                                                                                                                                                                                                                         |

| 9                 | SDI                   | SPI Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                      |

| 10                | SDO                   | SPI Serial Data Open-Drain Output. Connect SDO to logic high through a pull-up resistor.                                                                                                                                                                                                                                                                                                    |

| 11                | SCK                   | SPI Serial Clock Input.                                                                                                                                                                                                                                                                                                                                                                     |

| 12                | CS                    | SPI Chip Select Input, Active Low.                                                                                                                                                                                                                                                                                                                                                          |

| 13                | AUTO                  | Auto Mode Enable for All Ports, Active High. Tie AUTO low to configure the LTC4296-1 in manual mode<br>for performing microcontroller assisted PD classification. Tie AUTO high for applications that support<br>physical detection. See the Autonomous Mode section for additional uses for the AUTO pin.                                                                                  |

| 14                | WAKEUP                | Bidirectional Wake-Up. During a PD initiated wake-up event on a port, the WAKEUP pin is pulled high to $3.75 \text{ V}$ with an internal 100 $\mu$ A pull-up current. The WAKEUP pin is pulled down to GND by an internal $1.2 \text{ M}\Omega$ resistor. The WAKEUP pin can also be pulled to logic high externally to wake up one or more ports. Do not connect the WAKEUP Pin if unused. |

| 16 to 20          | SWx                   | Open-Drain Snubber Switch Output for Port x, Active High. SWx drives an external N-channel MOSFET to disconnect the power snubber during classification. See the Classification State section for additional information. Do not connect SWx if unused.                                                                                                                                     |

| 21                | GND                   | Device Ground.                                                                                                                                                                                                                                                                                                                                                                              |

| 22                | RT                    | Internal Oscillator Frequency Program Pin. Connect a 24.3 k $\Omega$ resistor between the RT pin and GND to set the internal oscillator frequency.                                                                                                                                                                                                                                          |

#### PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

#### Table 4. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                           |

|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

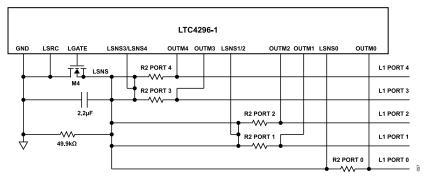

| 23      | LGATE                 | Low-Side Gate Drive. If a low-side, external N-channel MOSFET is present, connect LGATE to the<br>MOSFET gate. Do not connect LGATE if a low-side, external MOSFET is not present.                                                                                                                                                                    |

| 24      | LSRC                  | Low-Side External MOSFET Source Connection. Connect LSRC to GND.                                                                                                                                                                                                                                                                                      |

| 25      | OUTM0                 | Port 0, Negative Output, and Low-Side Kelvin Sense Positive Input. Connect OUTM0 directly to the positive terminal of the Port 0, low-side, current-sense resistor. Connect to LSNS0 if Port 0 is unused.                                                                                                                                             |

| 26      | LSNS0                 | Port 0, Low-Side, Kelvin Sense Negative Input. Connect LSNS0 directly to the negative terminal of the Port 0, low-side, current-sense resistor. If a low-side, external N-channel MOSFET is present, connect LSNS0 to the MOSFET drain. If a low-side external MOSFET is not present, connect LSNS0 to GND.                                           |

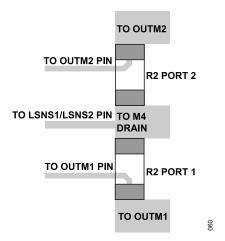

| 27      | OUTM1                 | Port 1, Negative Output, and Low-Side Kelvin Sense Positive Input. Connect OUTM1 directly to the positive terminal of the Port 1, low-side, current-sense resistor. Connect to LSNS1/LSNS2 if Port 1 is unused.                                                                                                                                       |

| 28      | LSNS1/LSNS2           | Port 1 and Port 2, Low-Side, Kelvin Sense Negative Input. Connect LSNS1/LSNS2 directly to the negative terminals of the Port 0 and Port 1, Iow-side, current-sense resistors. If a low-side, external N-channel MOSFET is present, connect LSNS1/LSNS2 to the MOSFET drain. If a low-side external MOSFET is not present, connect LSNS1/LSNS2 to GND. |

| 29      | OUTM2                 | Port 2, Negative Output, and Low-Side Kelvin Sense Positive Input. Connect OUTM2 directly to the positive terminal of the Port 2, low-side, current-sense resistor. Connect OUTM2 to LSNS1/LSNS2 if Port 2 is unused.                                                                                                                                 |

| 30      | OUTM3                 | Port 3, Negative Output, and Low-Side Kelvin Sense Positive Input. Connect OUTM3 directly to the positive terminal of the Port 3, low-side, current-sense resistor. Connect OUTM3 to LSNS3/LSNS4 if Port 3 is unused.                                                                                                                                 |

| 31      | LSNS3/LSNS4           | Port 3 and Port 4, Low-Side, Kelvin Sense Negative Input. Connect LSNS3/LSNS4 directly to the negative terminals of the Port 3 and Port 4, low-side current-sense resistors. If a low-side, external N-channel MOSFET is present, connect LSNS3/LSNS4 to the MOSFET drain. If a low-side external MOSFET is not present, connect LSNS3/LSNS4 to GND.  |

| 32      | OUTM4                 | Port 4, Negative Output, and Low-Side Kelvin Sense Positive Input. Connect OUTM4 directly to the positive terminal of the Port 4, low-side, current-sense resistor. Connect OUTM4 to LSNS3/LSNS4 if Port 4 is unused.                                                                                                                                 |

| 49      | GND                   | Exposed Pad and Device Ground. Must be soldered to the printed circuit board (PCB) ground.                                                                                                                                                                                                                                                            |

<sup>1</sup> Where x is to 0 through 4.

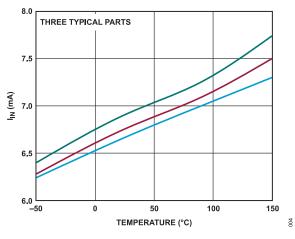

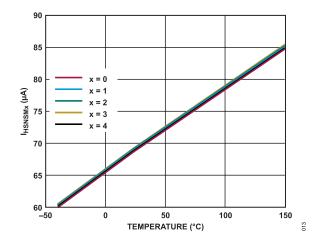

All tests were performed with  $V_{IN} = V_{HSNSPx} = V_{HSNSMx} = 60$  V at room temperature, unless otherwise noted.

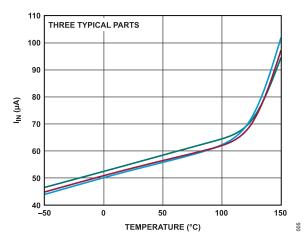

Figure 4. I<sub>IN</sub> vs. Temperature, All Ports in Power-On State

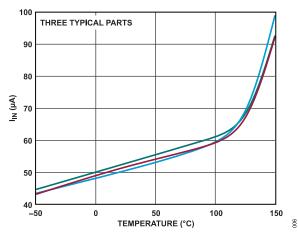

Figure 5. IIN vs. Temperature, All Ports in Sleep State

Figure 6. I<sub>IN</sub> vs. Temperature, All Ports in Disabled State

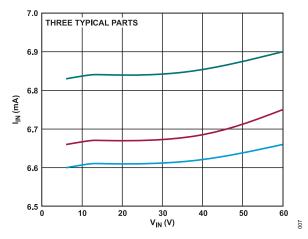

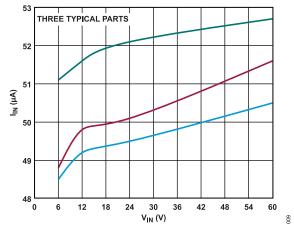

Figure 7. IIN vs. VIN, All Ports in Power-On State

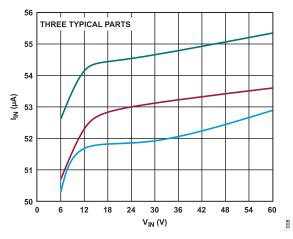

Figure 8. IIN vs. VIN, All Ports in Sleep State

Figure 9. IIN vs. VIN, All Ports in Disabled State

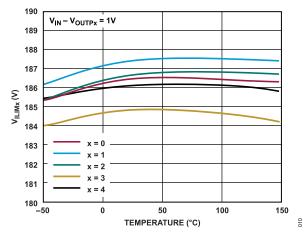

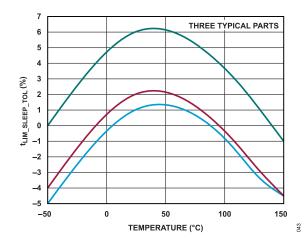

Figure 10. V<sub>ILIMx</sub> vs. Temperature, V<sub>IN</sub> – V<sub>OUTPx</sub> = 1 V

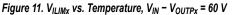

Figure 12. V<sub>ILIMx</sub> vs. V<sub>IN</sub> - V<sub>OUTPx</sub>

Figure 13. IHSNSMX vs. Temperature, Port in Power-On State

Figure 14.  $\Delta V_{LSNSx(FCB)}$  vs. Temperature

Figure 15. I<sub>SLP(FCB)</sub> vs. Temperature

Figure 17. I<sub>HGATE\_UPx</sub> vs. Temperature

Figure 18. I<sub>HGATE\_FASTx</sub> vs. Temperature

Figure 19. V<sub>PULLDOWN\_SLOWx</sub> vs. Temperature

Figure 20. dV<sub>HGATEx</sub>/dt vs. Temperature

Figure 21. ΔV<sub>LGATE</sub> vs. V<sub>IN</sub>

Figure 22. I<sub>LGATE(DWN)</sub> vs. Temperature, LGATE Disabled

Figure 24. V<sub>AUTO</sub> vs. Temperature, Rising Edge

Figure 25. Port Source Current Readback ADC Gain Error vs. Temperature

Figure 26. Port Source Current Readback ADC Offset vs. Temperature

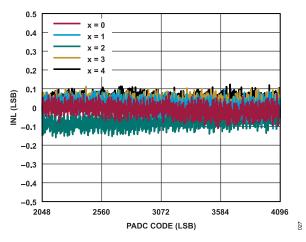

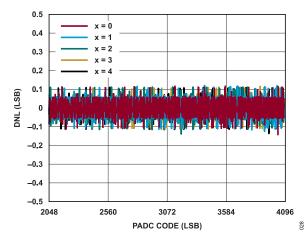

Figure 27. Port Source Current Readback ADC INL

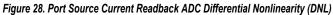

Figure 29. Internal Temperature Sensor Error vs. Temperature

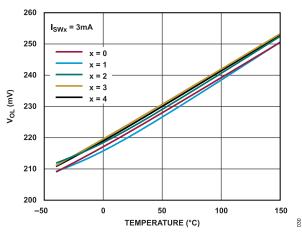

Figure 30. SWx VoL vs. Temperature

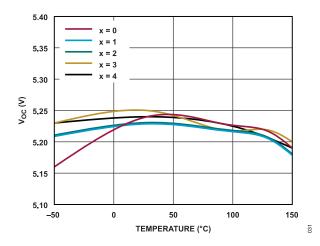

Figure 31. V<sub>OC</sub> vs. Temperature

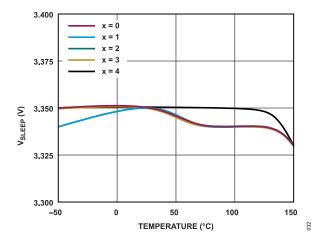

Figure 32. V<sub>SLEEP</sub> vs. Temperature

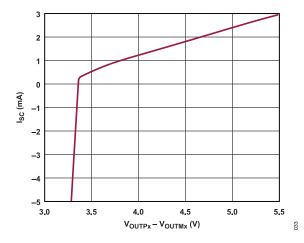

Figure 33. ISC vs. VOUTPx - VOUTMx, Sleep State

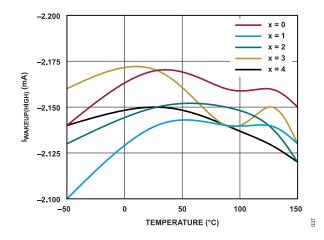

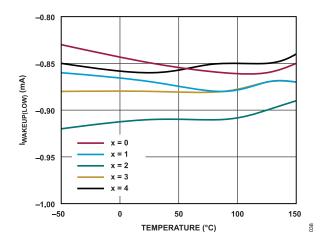

Figure 34. I<sub>DISCHARGE</sub> vs. Temperature, Settle-Sleep State

Figure 36. I<sub>SC</sub> vs. Temperature, Sleep State

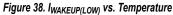

Figure 39. IVALID vs. VOUTPx - VOUTMX

Figure 41. I<sub>VALID</sub> vs. Temperature, V<sub>OUTPx</sub> - V<sub>OUTMx</sub> = 4.7 V

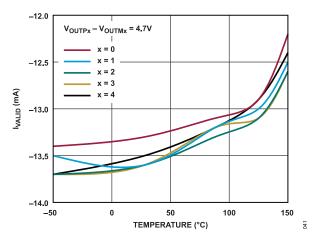

Figure 42. Timer Tolerance vs. Temperature ( $t_{INRUSH_TOL}$ ,  $t_{LIM_TOL}$ ,  $t_{OD_TOL}$ , and  $t_{RESTART_TOL}$ )

Figure 43. t<sub>LIM\_SLEEP\_TOL</sub> vs. Temperature

#### **OVERVIEW**

The LTC4296-1 is an IEEE 802.3cg-compliant, SPoE, PSE controller that controls and monitors power delivery for up to five PDs. The complementary data protocol for SPoE is 10BASE-T1L.

With a host microcontroller, the LTC4296-1 provides the circuitry required to implement an IEEE 802.3cg-compliant PSE design. Additional required components include a per port external, N-channel MOSFET and a sense resistor to implement high-side electronic circuit breakers with foldback ACL. An optional low-side, N-channel MOSFET, combined with per port, low-side sense resistors can be used to implement a low-side electronic circuit breaker. The LTC4296-1 application circuit provides the fault tolerance mandated by IEEE 802.3cg, increases system reliability, and minimizes power losses compared to designs with on-board MOSFETs.

The source and return circuit breakers offer protection against the following output faults at the connector:

- A short between the two conductors

- A short on one conductor or both conductors to an external positive voltage

- A short on the positive conductor to ground

The host microcontroller is used to configure the LTC4296-1 for PD classification by writing to the configuration registers using the SPI. The host microcontroller can also communicate with the LTC4296-1 via the SPI to read telemetry, such as port status, port voltages, and currents. The data integrity of the SPI is verified with the PEC feature.

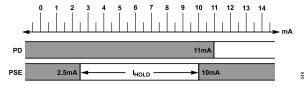

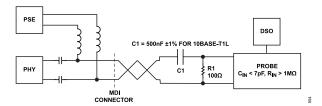

#### SPoE

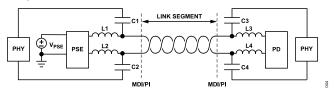

SPoE is a standard protocol for sending power over 2-wire Ethernet data cables. SPoE is similar in concept to traditional power over Ethernet (PoE) but differs significantly in definition and implementation. The differences stem mainly from the unique power coupling techniques used in a 2-wire circuit, as opposed to 4-wire and 8-wire, pair-oriented powering techniques of PoE. SPoE enables the simultaneous transmission of power and data over a single conductor pair, for example, balanced twisted pair or coaxial cable (Figure 44).

Single pair Ethernet (SPE) data connections consist of a single pair of wires, AC-coupled at each end to avoid ground loops. Unlike

PoE systems that transmit power common mode to the data, SPoE systems, diplex power and data over a single pair of conductors.

IEEE 802.3cg (SPoE) is an extension of 802.3bu power over data lines (PoDL). The IEEE Standards Association ratified PoDL in 2016. Multiple complementary data standards are already ratified or in development, ranging from 10 Mbps to 10 Gbps and higher. PoDL defines protocols for detecting, classifying, powering, disconnecting, and standby power operation. IEEE 802.3cg was ratified in 2019 to add features targeting long reach protocols, such as 10BASE-T1L, with cable lengths of up to 1 km.

SPoE was tailored to meet building and factory automation market requirements. SPoE also defines the classification-based power delivery protocol for the PSE and PD. Classification ensures PSE and PD compatibility and avoids applying power into a short-circuit or an open-circuit. The PSE performs detection, followed by classification, of the PD before applying the full operating voltage. During classification, the PSE requests information such as class, type, and cable resistance measurement (CRM) support from the PD.

If the PSE determines that the PD is compatible, it applies the full operating voltage to the PD at the medium dependent interface/power interface (MDI/PI). If CRM is supported, the PSE and PD can negotiate allocation of surplus power to the PD. The PSE can skip classification and power up a PD that provides a valid detection signature. A PD providing an invalid detection signature, however, must undergo classification before being powered. A PD is required to present a valid MFVS to remain fully powered. If the PD is disconnected or goes to sleep, the PSE detects the absence of the MFVS and removes the full operating voltage. The PSE removes the output voltage entirely in the event of a fault or short-circuit.

After removing the full operating voltage in the absence of the MFVS, the PSE enters a low power sleep state and provides  $V_{SLEEP}$  (3.4 V typical) at the port.

Wake-up functions from sleep are flexible and can flow either upstream (PD initiated) or downstream (PSE initiated). The PD can request restoration of the full operating voltage by presenting a wake-up current signature to the PSE. The PSE can also initiate a wake-up of the PD by providing the full operating voltage after successful classification.

Figure 44. Basic SPoE Architecture

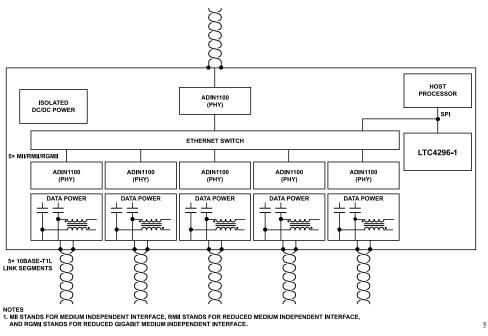

# 10BASE-T1L Field Switch PSE

The LTC4296-1 provides a solution for 10BASE-T1L field switches that require a PSE at each port.

Classification of the PD connected to each link segment ensures that the overall power provided to the switch is appropriately distributed across the subsystems. An example of a 10BASE-T1L field switch is shown in Figure 45. The field switch host processor manages the 5× port Ethernet switch (integrated MAC) and the LTC4296-1 over a SPI.

Figure 45. 10BASE-T1L Field Switch PSE

#### **Classification for Discoverable Systems**

The SPoE class defines the PSE output voltage range and maximum power sourced or consumed in the system. PoDL comprises Class 0 through Class 15. Class 10 through Class 15 are defined by IEEE 802.3cg for discoverable systems as shown in Table 5 and Table 6. Class 10 through Class 12 provide a 24 V nominal PSE output voltage, as required by many industrial, factory automation, legacy building automation, and wet locations. Each of the three 24 V classes represents a different cabling definition and accompanying maximum power transfer. Class 13 through Class 15 provide a 54 V nominal PSE output voltage, to maximize power transfer without exceeding the safety extra low voltage (SELV). Compatible SPoE, PSE and PD class pairs are shown in Table 7. PoDL defines the SCCP for classifying a PD. The SCCP uses three basic symbols: initialization, read-slot, and write-slot. Classification is performed in the detection state by the host microcontroller using the SCCP. Refer to the EVAL-SPoE-KIT-AZ Evaluation Kit User Guide (the LTC4296-1 demonstration board) for additional information on how to implement the SCCP with the host microcontroller.

IEEE 802.3cg also supports an optional CRM feature as part of the SCCP. CRM allows a PSE to allocate additional power otherwise allocated for cable loss to a PD when connected through less than the maximum allowed cable resistance.

#### Table 5. IEEE 802.3cg Class Power Requirements Matrix for PSE and PDs

| Class Symbol and Unit         | Class Description  | Class 10 | Class 11 | Class 12 | Class 13 | Class 14 | Class 15 |

|-------------------------------|--------------------|----------|----------|----------|----------|----------|----------|

| V <sub>PSE</sub> (V)          | PSE output voltage |          | 20 to 30 |          |          | 50 to 58 |          |

| I <sub>PI(MAX)</sub> (mA)     | Cable current      | 92       | 240      | 632      | 231      | 600      | 1579     |

| P <sub>CLASS(MIN)</sub> (W)   | PSE output power   | 1.85     | 4.8      | 12.63    | 11.54    | 30       | 79       |

| V <sub>PD(MIN)</sub> (V)      | PD input voltage   |          | 14       |          |          | 35       |          |

| P <sub>PD(MAX)</sub> (W)      | PD power           | 1.23     | 3.2      | 8.4      | 7.7      | 20       | 52       |

| $R_{LINK\_SEG\_LOOP}(\Omega)$ | Cable resistance   | 65       | 25       | 9.5      | 65       | 25       | 9.5      |

Table 6. IEEE 802.3cg Class Power Requirements Matrix Example Link Segment Maximum Distances

|                       |                   | Maximum Lengths (m) |          |                   |          |          |  |

|-----------------------|-------------------|---------------------|----------|-------------------|----------|----------|--|

| Example Cable         | Class 10          | Class 11            | Class 12 | Class 13          | Class 14 | Class 15 |  |

| 14AWG, 14 Gauge Cable | 1000 <sup>1</sup> | 1000                | 400      | 1000 <sup>1</sup> | 1000     | 400      |  |

| 18AWG, 18 Gauge Cable | 1000              | 400                 | 158      | 1000              | 400      | 158      |  |

| 24AWG, 24 Gauge Cable | 300               | 100                 | 40       | 300               | 100      | 40       |  |

<sup>1</sup> IEEE 802.3cg limits cable length to 1000 m.

#### Table 7. PSE and PD Class Compatibility Matrix

|          | PSE Class |     |     |     |     |     |

|----------|-----------|-----|-----|-----|-----|-----|

| PD Class | 10        | 11  | 12  | 13  | 14  | 15  |

| 10       | Yes       | Yes | Yes | No  | No  | No  |

| 11       | No        | Yes | Yes | No  | No  | No  |

| 12       | No        | No  | Yes | No  | No  | No  |

| 13       | No        | No  | No  | Yes | Yes | Yes |

| 14       | No        | No  | No  | No  | Yes | Yes |

| 15       | No        | No  | No  | No  | No  | Yes |

#### **USAGE CASES**

#### 802.3cg-Compliant PSE

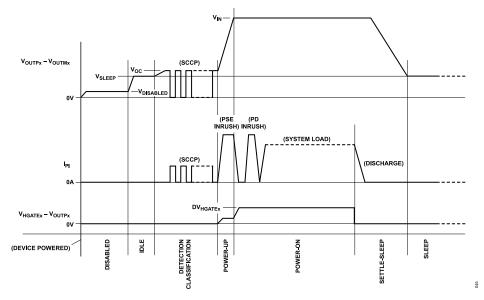

The primary usage case for the LTC4296-1 is an 802.3cg-compliant PSE. With this case, the LTC4296-1 AUTO pin is pulled low and a host operates the LTC4296-1 ports semimanually through the states shown in Figure 46. In each state, the LTC4296-1 controls the port output voltage accordingly.

From a system power-up or device reset, the LTC4296-1 starts in the disabled state. An LTC4296-1 port is enabled by the host and moves on to the idle state. The LTC4296-1 then awaits a command from the host to move on to the next state.

When ready, the host configures the LTC4296-1 port to enter the detection state. Note that the LTC4296-1 checks the port current status before moving on to detection.

When the port is in the detection state, the host sets the LTC4296-1 to the classification state and performs the SCCP with a valid PD. Once the host microcontroller determines that the class of the PD is compatible, it can then command the port to enter the power-up state.

During the power-up state, the LTC4296-1 controls inrush and monitors the port output voltage to determine when inrush is complete.

After a successful power-up, the port enters the power-on state and remains there until the LTC4296-1 detects a current overload fault or an MFVS timeout, or the device is instructed by the host to exit power-on when power is no longer available.

If the LTC4296-1 removes power to the port due to an invalid MFVS, it monitors the port voltage discharge in the settle-sleep state.

The LTC4296-1 enters the low power, sleep state after a successful port discharge. In this state, the LTC4296-1 waits for the user, host, or PD to initiate a wake-up before returning to the detection state.

While in the idle, power-on, settle-sleep, or sleep states, the LTC4296-1 monitors the port for current overload fault conditions. If a fault occurs, the LTC4296-1 turns off the port and waits a set time in the overload state before entering the idle state.

A port that fails to exit either the detection or power-up states successfully before the maximum allotted time enters the restart state. The port then waits a set time before re-entering the idle state.

Figure 46. Simplified 802.3cg-Compliant PSE State Sequence (Not to Scale)

#### Autonomous Mode

For applications that do not require classification, the LTC4296-1 can operate in an autonomous mode without a host controller when the AUTO pin is pulled high. In autonomous mode, the LTC4296-1 powers up any port when a PD presents a valid detection signature. This mode is ideal for applications that only require a basic detection. Power-up can be forced, regardless of the detection signature, by setting the signature override good bit (Register PxCFG1, Bit 0, SIG OVERRIDE GOOD).

#### PORT STATE DESCRIPTIONS

#### Overview

Every port in the LTC4296-1 implements the PSE state described in the usage cases (see the 802.3cg-Compliant PSE section and the Autonomous Mode section). A detailed description of each state is provided in the subsequent sections.

#### **Disabled State**

A port starts in the disabled state after a power-on or software reset event. In this state, the high-side MOSFET is turned off, and the port voltage is discharged to less than  $V_{\text{DISABLED}}$  with an internal pull-down. The port remains in this state until it is enabled by the software enable bit (Register PxCFG0, Bit 0, SW\_EN) or if the AUTO pin is high and not masked (Register PxCFG0, Bit 1, HW\_EN\_MASK). Once enabled, the port enters the idle state.

#### **Idle State**

In the Idle state, the port output is biased by the LTC4296-1 to  $V_{SLEEP}$ . If the output voltage is in the  $V_{SLEEP}$  range, the output current is less than the I<sub>WAKEUP</sub> maximum, and the AUTO pin is high or the software PSE ready is asserted (Register PxCFG0, Bit 6, SW\_PSE\_READY), the port proceeds to the detection state. If the port current exceeds I<sub>WAKEUP</sub> for t<sub>LIM\_SLEEP</sub>, the port enters the overload state.

#### **Detection State**

PD detection is performed in the detection state. During detection, a probing current,  $I_{VALID}$ , is sourced and the port searches for a PD. A

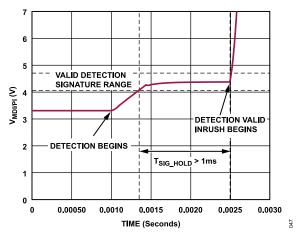

PD not requiring classification presents a valid detection signature voltage in the range of 4.05 V to 4.55 V when the PSE sources  $I_{VALID}$ . Figure 47 shows a typical valid PD detection sequence.

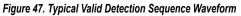

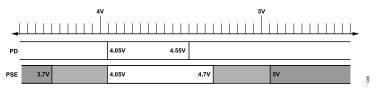

The PSE must accept a PD detection signature as valid when a valid detection signature voltage is present for at least  $t_{SIG_HOLD}$  and must reject voltages less than  $V_{BAD_LO_PSE}$  (3.7 V) or greater than  $V_{BAD_HI_PSE}$  (5 V), dark shaded regions in Figure 48. The PSE can accept or reject voltages in the undefined ranges between the must-reject and must-accept limits (light shaded regions).

A port exits the detection state after  $t_{DET}$  unless the detection timer is disabled (PxCFG0, Bit 11, TDET\_DISABLE). If the  $t_{DET}$  timer expires without detecting a valid PD signature, the port enters the restart state and then returns to the idle state.

For use cases not requiring classification, the following conditions must be met to proceed to the power-up state:

- A valid detection signature is found (or Register PxCFG1, Bit 0, SIG\_OVERRIDE\_GOOD, is set).

- The global software power-good bit is set (Register GCFG, Bit 0, SW\_VIN\_PGOOD).

- The port software power available bit is set (Register PxCFG0, Bit 5, SW\_POWER\_AVAILABLE). If the port software power available bit is not set, the port goes to the restart state after exiting the detection state.

Figure 48. IEEE 802.3bu Signature Voltage Range

# **Classification State**

Classification is performed in the detection state by the host microcontroller using the SCCP. Refer to the EVAL-SPoE-KIT-AZ Evaluation Kit User Guide (the LTC4296-1 demonstration board) for additional information on how to implement the SCCP with the host microcontroller.

Classification is configured by setting the software PSE ready bit (PxCFG0, Bit6, SW\_PSE\_READY) and setting the classification mode bit (PXCFG0, Bit 13, SET\_CLASSIFICATION\_MODE) before entering the detection state. When the classification mode bit is asserted while in the detection state, the port SWx pin pulls low to disable the external, snubber switch MOSFET (M2) of the port.

If the microcontroller determines that a valid PD with a compatible class is present, the port can proceed to the power-up state by setting the port software power available bit (Register PxCFG0, Bit 5, SW\_POWER\_AVAILABLE) and the end classification bit (Register PxCFG0, Bit 14, END\_CLASSIFICATION).

If a PD with a valid signature or a PD with a compatible class is not present, the port can be returned to the idle state via the restart state by clearing the port software power available bit and setting Register PxCFG0, Bit 14, END\_CLASSIFICATION.

# **Power-Up State**

In the power-up state, the port ramps up the HGATEx voltage in a controlled manner to limit inrush current. Under normal power-up circumstances, the HGATEx voltage increases until the port reaches  $V_{ILIMx}$ , or until the maximum HGATEx inrush slew rate,  $dV_{HGATEx}/dt$ , is reached. The inrush time ( $t_{INRUSH}$ ) timer is initiated upon entry of the power-up state.

When the port output voltage has ramped up, the port current decreases, and the HGATEx pin voltage continues rising to fully enhance the external MOSFET. The final gate-to-source voltage for the MOSFET is  $\Delta V_{HGATEx}$ . Power-up is complete when the voltage between the IN pin and the port OUTPx pin drops to less than the high-side, power-good threshold voltage,  $\Delta V_{OUTPx\ PWRGD}$ .

If inrush is not complete within  $t_{\text{INRUSH}}$ , the port enters the restart state, and the  $t_{\text{INRUSH}}$  timer done bit of the port is set (Register PxEV, Bit 3, TINRUSH\_TIMER\_DONE). The  $t_{\text{INRUSH}}$  timer limit is programmable (PxCFG1, Bits[3:2], TINRUSH\_TIMER). If the inrush completes within  $t_{\text{INRUSH}}$ , the port proceeds to the power-on state.

# **Power-On State**

During operation in the power-on state, the high-side output current is continuously monitored and limited by the port current sense ADC and an electronic circuit breaker with foldback ACL, respectively. If the PD does not present a valid MFVS for more than  $t_{MFVDO}$ , the port goes to the settle-sleep state and starts discharging the port output voltage to the  $V_{SLEEP}$  range. If the host decides power is not available, it can deassert the port software power

available bit (Register PxCFG0, Bit 5, SW\_POWER\_AVAILABLE), and the port goes into the restart state.

# Settle-Sleep State

In the settle-sleep state, the port output is discharged to V<sub>SLEEP</sub> by the pull-down current I<sub>DISCHARGE</sub>. If the output voltage discharges to V<sub>SLEEP</sub> within t<sub>OFF</sub>, the port goes to the sleep state. A port enters the overload state from the settle-sleep state if it is unable to discharge the port output to V<sub>SLEEP</sub> within t<sub>OFF</sub>.

# Sleep State

In the sleep state, the port output is maintained at V<sub>SLEEP</sub> and monitored for a wake-up signature current, I<sub>WAKEUP</sub>, from the PD. The PSE enters the detection state after a valid wake-up signature is detected for at least t<sub>WAKEUP</sub>. A wake-up event can also be initiated by the PSE application host microcontroller via the SPI or the WAKEUP pin.