# 8-Bit, 165 MSPS TxDAC® D/A Converter

# **Preliminary Technical Data**

AD9748\*

#### **FEATURES**

High-Performance Member of Pin-Compatible TxDAC Product Family

Excellent Spurious-Free Dynamic Range and Noise Performance

Two's Complement or Straight Binary Data Format

Differential Current Outputs: 2 mA to 20 mA

Power Dissipation: 135 mW @ 3.3 V Power-Down Mode: 15 mW @ 3.3 V

On-Chip 1.20 V Reference

CMOS-Compatible Digital Interface

Package: 32-Lead Leadframe Chip Scale Package

(LFCSP)

**Edge-Triggered Latches**

#### **APPLICATIONS**

Wideband Communication Transmit Channel:

Direct IF

Base Stations

Wireless Local Loop

Digital Radio Link

Direct Digital Synthesis (DDS)

Instrumentation

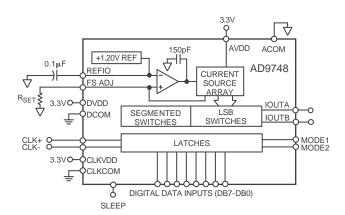

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT DESCRIPTION

The AD9748 is a 8-bit resolution, wideband, third generation member of the TxDAC series of high-performance, low power CMOS digital-to-analog converters (DACs). The TxDAC family, consisting of pin-compatible 8-, 10-, 12-, and 14-bit DACs, is specifically optimized for the transmit signal path of communication systems. All of the devices share the same interface options, small outline package, and pinout, providing an upward or downward component selection path based on performance, resolution, and cost. The AD9748 offers exceptional ac and dc performance while supporting update rates up to 165 MSPS.

The AD9748's low power dissipation makes it well suited for portable and low power applications. Its power dissipation can be further reduced to a mere 60 mW with a slight degradation in performance by lowering the full-scale current output. Also, a power-down mode reduces the standby power dissipation to approximately 15 mW. A segmented current source architecture is combined with a proprietary switching technique to reduce spurious components and enhance dynamic performance. Edgetriggered input latches and a 1.2 V temperature compensated

TxDAC is a registered trademark of Analog Devices, Inc. \*Protected by U.S. Patent Numbers 5568145, 5689257, and 5703519.

#### REV. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

band gap reference have been integrated to provide a complete monolithic DAC solution. The digital inputs support 3 V CMOS logic families.

#### PRODUCT HIGHLIGHTS

- 1. New 32-lead LFCSP package.

- 2. The AD9748 is the 8-bit member of the pin-compatible TxDAC family that offers excellent INL and DNL performance.

- 3. Differential or single-ended clock input (LVPECL or CMOS).

- 4. Data input supports two's complement or straight binary data coding.

- 5. High-speed, single-ended CMOS clock input supports 165 MSPS conversion rate.

- 6. Low power: Complete CMOS DAC function operates on 135 mW from a 3.0 V to 3.6 V single supply. The DAC full-scale current can be reduced for lower power operation, and a sleep mode is provided for low power idle periods.

- 7. On-chip voltage reference: The AD9748 includes a 1.2 V temperature-compensated band gap voltage reference.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# **AD9748-SPECIFICATIONS**

$DC \ SPECIFICATIONS \quad (T_{MIN} \ to \ T_{MAX}, \ AVDD = 3.3 \ V, \ DVDD = 3.3 \ V, \ I_{OUTFS} = 20 \ mA, \ unless \ otherwise \ noted.)$

| Parameter                                                | Min   | Тур   | Max   | Unit          |

|----------------------------------------------------------|-------|-------|-------|---------------|

| RESOLUTION                                               | 8     |       |       | Bits          |

| DC ACCURACY <sup>1</sup>                                 |       |       |       |               |

| Integral Linearity Error (INL)                           | TBD   | ±0.25 | TBD   | LSB           |

| Differential Nonlinearity (DNL)                          | TBD   | ±0.25 | TBD   | LSB           |

| ANALOG OUTPUT                                            |       |       |       |               |

| Offset Error                                             | -0.02 |       | +0.02 | % of FSR      |

| Gain Error (Without Internal Reference)                  | -0.5  | ±0.1  | +0.5  | % of FSR      |

| Gain Error (With Internal Reference)                     | -0.5  | ±0.1  | +0.5  | % of FSR      |

| Full-Scale Output Current <sup>2</sup>                   | 2.0   |       | 20.0  | mA            |

| Output Compliance Range                                  | -1.0  |       | +1.25 | V             |

| Output Resistance                                        |       | 100   |       | kΩ            |

| Output Capacitance                                       |       | 5     |       | pF            |

| REFERENCE OUTPUT                                         |       | ·     | ·     |               |

| Reference Voltage                                        | 1.14  | 1.20  | 1.26  | V             |

| Reference Output Current <sup>3</sup>                    |       | 100   |       | nA            |

| REFERENCE INPUT                                          |       |       |       |               |

| Input Compliance Range                                   | 0.1   |       | 1.25  | V             |

| Reference Input Resistance (Ext. Ref)                    |       | 1     |       | ΜΩ            |

| Small Signal Bandwidth                                   |       | 0.5   |       | MHz           |

| TEMPERATURE COEFFICIENTS                                 |       |       |       |               |

| Offset Drift                                             |       | 0     |       | ppm of FSR/°C |

| Gain Drift (Without Internal Reference)                  |       | ±50   |       | ppm of FSR/°C |

| Gain Drift (With Internal Reference)                     |       | ±100  |       | ppm of FSR/°C |

| Reference Voltage Drift                                  |       | ±50   |       | ppm/°C        |

| POWER SUPPLY                                             |       |       |       |               |

| Supply Voltages                                          |       |       |       |               |

| AVDD                                                     | 3.0   | 3.3   | 3.6   | V             |

| DVDD                                                     | 3.0   | 3.3   | 3.6   | V             |

| Analog Supply Current (I <sub>AVDD</sub> )               |       | 33    | 36    | mA            |

| Digital Supply Current (I <sub>DVDD</sub> ) <sup>4</sup> |       | 8     | TBD   | mA            |

| Supply Current Sleep Mode (I <sub>AVDD</sub> )           |       | 5     | 6     | mA            |

| Power Dissipation <sup>4</sup>                           |       | 135   | 145   | mW            |

| Power Dissipation <sup>5</sup>                           |       | 145   |       | mW            |

| Power Supply Rejection Ratio—AVDD <sup>6</sup>           | -1    |       | +1    | % of FSR/V    |

| Power Supply Rejection Ratio—DVDD <sup>6</sup>           | -0.04 |       | +0.04 | % of FSR/V    |

| OPERATING RANGE                                          | -40   |       | +85   | °C            |

| NOTES                                                    |       |       |       | I             |

Specifications subject to change without notice.

REV. PrA -2-

<sup>&</sup>lt;sup>1</sup>Measured at IOUTA, driving a virtual ground.

<sup>&</sup>lt;sup>2</sup>Nominal full-scale current,  $I_{OUTFS}$ , is 32 times the  $I_{REF}$  current.

<sup>3</sup>An external buffer amplifier with input bias current <100 nA should be used to drive any external load.

<sup>4</sup>Measured at  $f_{CLOCK}$  = 25 MSPS and  $f_{OUT}$  = 1.0 MHz.

<sup>5</sup>Measured as unbuffered voltage output with  $I_{OUTFS}$  = 20 mA and 50  $\Omega$   $R_{LOAD}$  at IOUTA and IOUTB,  $f_{CLOCK}$  = 100 MSPS and  $f_{OUT}$  = 40 MHz.

<sup>6±5%</sup> Power supply variation.

**AD9748**

# DYNAMIC SPECIFICATIONS

(T<sub>MIN</sub> to T<sub>MAX</sub> , AVDD = 3.3 V, DVDD = 3.3 V, I<sub>OUTFS</sub> = 20 mA, Differential Transformer Coupled Output, 50  $\Omega$  Doubly Terminated, unless otherwise noted.)

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min | Тур                                           | Max | Unit                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------|-----|----------------------------------------------------|

| DYNAMIC PERFORMANCE  Maximum Output Update Rate $(f_{CLOCK})$ Output Settling Time $(t_{ST})$ (to $0.1\%$ ) <sup>1</sup> Output Propagation Delay $(t_{PD})$ Glitch Impulse Output Rise Time $(10\% \text{ to } 90\%)^1$ Output Fall Time $(10\% \text{ to } 90\%)^1$ Output Noise $(I_{OUTFS} = 20 \text{ mA})^2$ Output Noise $(I_{OUTFS} = 2 \text{ mA})^2$ Noise Spectral Density <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 165 | 11<br>1<br>5<br>2.5<br>2.5<br>50<br>30<br>TBD |     | MSPS  ns  ns  pV-s  ns  ns  pA/√Hz  pA/√Hz  dBm/Hz |

| AC LINEARITY  Spurious-Free Dynamic Range to Nyquist  f <sub>CLOCK</sub> = 25 MSPS; f <sub>OUT</sub> = 1.00 MHz  0 dBFS Output  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 1.00 MHz  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 2.51 MHz  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 10 MHz  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 15 MHz  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 25 MHz  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 21 MHz  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 41 MHz  Total Harmonic Distortion  f <sub>CLOCK</sub> = 25 MSPS; f <sub>OUT</sub> = 1.00 MHz  f <sub>CLOCK</sub> = 50 MSPS; f <sub>OUT</sub> = 2.00 MHz  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 2.00 MHz  Signal-to-Noise Ratio  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 20 mA  f <sub>CLOCK</sub> = 65 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 20 mA  f <sub>CLOCK</sub> = 125 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 20 mA  f <sub>CLOCK</sub> = 125 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA  f <sub>CLOCK</sub> = 165 MSPS; f <sub>OUT</sub> = 5 MHz; I <sub>OUTFS</sub> = 5 mA | TBD | TBD       | TBD | dBc            |

#### NOTES

REV. PrA –3–

<sup>&</sup>lt;sup>1</sup>Measured single-ended into 50 ý load.

<sup>&</sup>lt;sup>2</sup>Output noise is measured with a full-scale output set to 20 mA with no conversion activity. It is a measure of the thermal noise only.

<sup>&</sup>lt;sup>3</sup>Noise spectral density is the average noise power normalized to a 1 Hz bandwidth, with the DAC converting and producing an output tone.

Specifications subject to change without notice.

### AD9748

# DIGITAL SPECIFICATIONS

( $T_{MIN}$  to  $T_{MAX}$ , AVDD = 3.3 V, DVDD = 3.3 V,  $I_{OUTFS}$  = 20 mA, unless otherwise noted.)

| Parameter                            | Min | Typ | Max | Unit |  |

|--------------------------------------|-----|-----|-----|------|--|

| DIGITAL INPUTS                       |     |     |     |      |  |

| Logic "1" Voltage                    | 2.1 | 3   |     | V    |  |

| Logic "0" Voltage                    |     | 0   | 0.9 | V    |  |

| Logic "1" Current                    | -10 |     | +10 | μA   |  |

| Logic "0" Current                    | -10 |     | +10 | μA   |  |

| Input Capacitance                    |     | 5   |     | pF   |  |

| Input Setup Time (t <sub>S</sub> )   | 2.0 |     |     | ns   |  |

| Input Hold Time (t <sub>H</sub> )    | 1.5 |     |     | ns   |  |

| Latch Pulsewidth (t <sub>LPW</sub> ) | 1.5 |     |     | ns   |  |

Figure 1. Timing Diagram

#### ABSOLUTE MAXIMUM RATINGS\*

|                           | With       |      |            |      |

|---------------------------|------------|------|------------|------|

| Parameter                 | Respect to | Min  | Max        | Unit |

| AVDD                      | ACOM       | -0.3 | +3.9       | V    |

| DVDD                      | DCOM       | -0.3 | +3.9       | V    |

| ACOM                      | DCOM       | -0.3 | +0.3       | V    |

| AVDD                      | DVDD       | -3.9 | +3.9       | V    |

| CLOCK, SLEEP              | DCOM       | -0.3 | DVDD + 0.3 | V    |

| Digital Inputs            | DCOM       | -0.3 | DVDD + 0.3 | V    |

| IOUTA, IOUTB              | ACOM       | -1.0 | AVDD + 0.3 | V    |

| REFIO, REFLO, FSADJ       | ACOM       | -0.3 | AVDD + 0.3 | V    |

| Junction Temperature      |            |      | 150        | °C   |

| Storage Temperature       |            | -65  | +150       | °C   |

| Lead Temperature (10 sec) |            |      | 300        | °C   |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause perma nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

#### ORDERING GUIDE

| Model     | Temperature<br>Range |               | Package<br>Options* |

|-----------|----------------------|---------------|---------------------|

| AD9748XCP | -40°C to +85°C       | 32-Lead LFCSP | CP-32               |

<sup>\*</sup>CP = Leadframe Chip Scale Package

THERMAL CHARACTERISTICS Thermal Resistance 32-Lead LFCSP  $\theta_{JA}$ = TBD°C/W

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9748 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4- REV. PrA

# **AD9748**

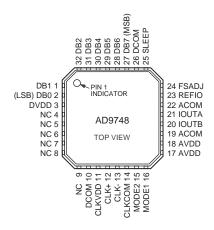

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No.  | Mnemonic | Description                                                                                                                                                                                                                                                                      |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27       | DB7      | Most Significant Data Bit (MSB)                                                                                                                                                                                                                                                  |

| 28-32, 1 | DB6-DB1  | Data Bits 6-1                                                                                                                                                                                                                                                                    |

| 2        | DB0      | Least Significant Data Bit (LSB)                                                                                                                                                                                                                                                 |

| 25       | SLEEP    | Power-Down Control Input. Active high. Contains active pull-down circuit; it may be left unterminated if not used.                                                                                                                                                               |

| 23       | REFIO    | Reference Input/Output. Serves as reference input when internal reference disabled (i.e., tie REFLO to AVDD). Serves as 1.2 V reference output when internal reference activated (i.e., tie REFLO to AGND). Requires 0.1 μF capacitor to AGND when internal reference activated. |

| 24       | FS ADJ   | Full-Scale Current Output Adjust                                                                                                                                                                                                                                                 |

| 4-9      | NC       | No Internal Connection                                                                                                                                                                                                                                                           |

| 19, 22   | ACOM     | Analog Common                                                                                                                                                                                                                                                                    |

| 20       | IOUTB    | Complementary DAC Current Output. Full-scale current when all data bits are 0s.                                                                                                                                                                                                  |

| 21       | IOUTA    | DAC Current Output. Full-scale current when all data bits are 1s.                                                                                                                                                                                                                |

| 17, 18   | AVDD     | Analog Supply Voltage (3.3 V)                                                                                                                                                                                                                                                    |

| 15       | MODE2    | Selects Input Data Format. Connect to CLKGND for straight binary, CLKVDD for two's complement.                                                                                                                                                                                   |

| 16       | MODE1    | Clock Mode Selection. Connect to CLKGND for single ended clock receiver (drive clk+ and float clk-). Connect to CLKVDD for differential receiver. Float for PECL receiver (terminations on-chip).                                                                                |

| 10, 26   | DCOM     | Digital Common                                                                                                                                                                                                                                                                   |

| 3        | DVDD     | Digital Supply Voltage (3.3 V)                                                                                                                                                                                                                                                   |

| 12       | CLK+     | Differential Clock Input.                                                                                                                                                                                                                                                        |

| 13       | CLK-     | Differential Clock Input.                                                                                                                                                                                                                                                        |

| 11       | CLKVDD   | Clock Supply Voltage (3.3 V)                                                                                                                                                                                                                                                     |

| 14       | CLKCOM   | Clock Common                                                                                                                                                                                                                                                                     |

REV. PrA –5–

### AD9748

#### **DEFINITIONS OF SPECIFICATIONS**

Linearity Error (Also Called Integral Nonlinearity or INL) Linearity error is defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero to full scale.

#### Differential Nonlinearity (or DNL)

DNL is the measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### Monotonicity

A D/A converter is monotonic if the output either increases or remains constant as the digital input increases.

#### Offset Error

The deviation of the output current from the ideal of zero is called the offset error. For IOUTA, 0 mA output is expected when the inputs are all 0s. For IOUTB, 0 mA output is expected when all inputs are set to 1s.

#### Gain Error

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1s minus the output when all inputs are set to 0s.

#### Output Compliance Range

The range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown resulting in nonlinear performance.

#### Temperature Drift

Temperature drift is specified as the maximum change from the ambient (25°C) value to the value at either  $T_{MIN}$  or  $T_{MAX}$ . For offset and gain drift, the drift is reported in ppm of full-scale

range (FSR) per °C. For reference drift, the drift is reported in ppm per °C.

#### Power Supply Rejection

The maximum change in the full-scale output as the supplies are varied from nominal to minimum and maximum specified voltages.

#### Settling Time

The time required for the output to reach and remain within a specified error band about its final value, measured from the start of the output transition.

#### Glitch Impulse

Asymmetrical switching times in a DAC give rise to undesired output transients that are quantified by a glitch impulse. It is specified as the net area of the glitch in pV-s.

#### Spurious-Free Dynamic Range

The difference, in dB, between the rms amplitude of the output signal and the peak spurious signal over the specified bandwidth.

#### Total Harmonic Distortion

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal. It is expressed as a percentage or in decibels (dB).

#### Multitone Power Ratio

The spurious free dynamic range containing multiple carrier tones of equal amplitude. It is measures as the difference between the rms amplitude of a carrier tone to the peak spurious signal in the region of a removed tone.

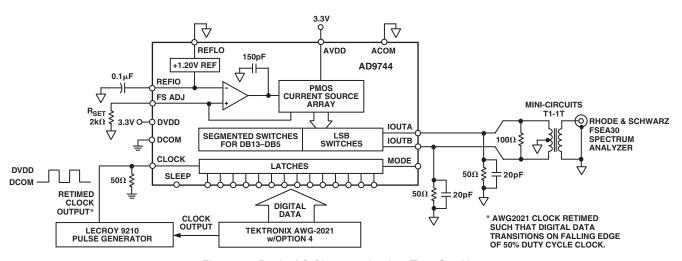

Figure 2. Basic AC Characterization Test Set-Up

-6- REV. PrA

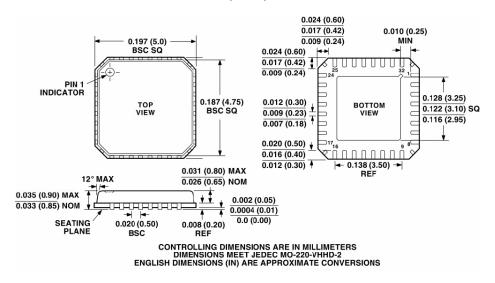

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm)

32-Lead Leadframe Chip Scale Package (LFCSP) (CP-28)

REV. PrA -7-