Sample &

Buv

TUSB320LAI, TUSB320HAI

SLLSEQ8B-OCTOBER 2015-REVISED SEPTEMBER 2016

# TUSB320LAI, TUSB320HAI USB Type-C Configuration Channel Logic and Port Control

Technical

Documents

#### 1 Features

- USB Type-C<sup>™</sup> Specification 1.1

- Backward Compatible with USB Type-C Specification 1.0

- Supports Up to 3 A of Current Advertisement and Detection

- Mode Configuration

- Host Only DFP (Source)

- Device Only UFP (Sink)

- Dual Role Port DRP

- Supports both Try.SRC and Try.SNK

- Channel Configuration (CC)

- Attach of USB Port Detection

- Cable Orientation Detection

- Role Detection

- Type-C Current Mode (Default, Medium, High)

- V<sub>BUS</sub> Detection

- I<sup>2</sup>C or GPIO Control

- Supports up to 400 kHz I<sup>2</sup>C

- Role Configuration Control through I<sup>2</sup>C

- Supply Voltage: 2.7 V to 5 V

- Low Current Consumption

- Industrial Temperature Range of -40 to 85°C

#### 2 Applications

- Host, Device, Dual Role Port Applications

- Mobile Phones

- Tablets and Notebooks

- **USB** Peripherals

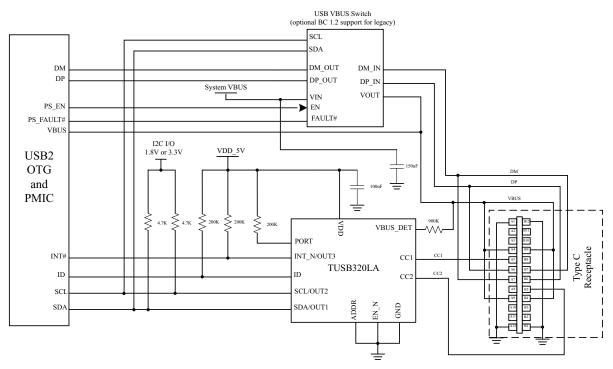

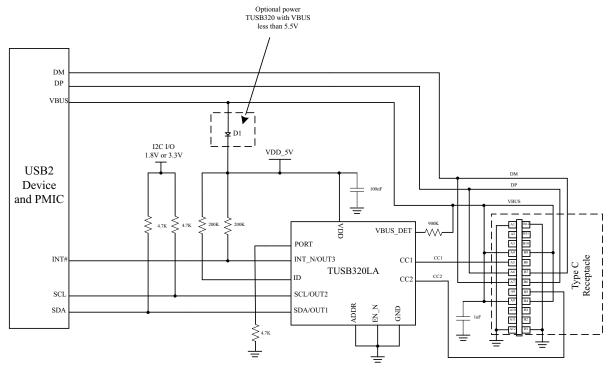

# Simplified Schematic

# 3 Description

Tools &

Software

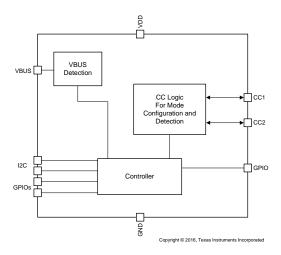

The TUSB320LA and TUSB320HA devices, hereafter called TUSB320 unless otherwise noted, are Texas Instrument's third generation Type-C configuration channel logic and port controller. The TUSB320 devices use the CC pins to determine port attach and detach, cable orientation, role detection, and port control for Type-C current mode. The TUSB320 devices can be configured as a downstream facing port (DFP), upstream facing port (UFP) or a dual role port (DRP) making them ideal for any application.

Support &

Community

The TUSB320 devices have an alternate configuration as a DFP or UFP according to the Type-C specifications. The CC logic block monitors the CC1 and CC2 pins for pullup or pulldown resistances to determine when a USB port has been attached, the orientation of the cable, and the role detected. The CC logic detects the Type-C current mode as default, medium, or high depending on the role detected. V<sub>BUS</sub> detection is implemented to determine a successful attach in UFP and DRP modes.

The devices operate over a wide supply range and have low-power consumption. The TUSB320 is available in two versions of enable: Active low enable called TUSB320LA and active high enable called TUSB320HA. The TUSB320 family of devices are available in industrial temperature ranges.

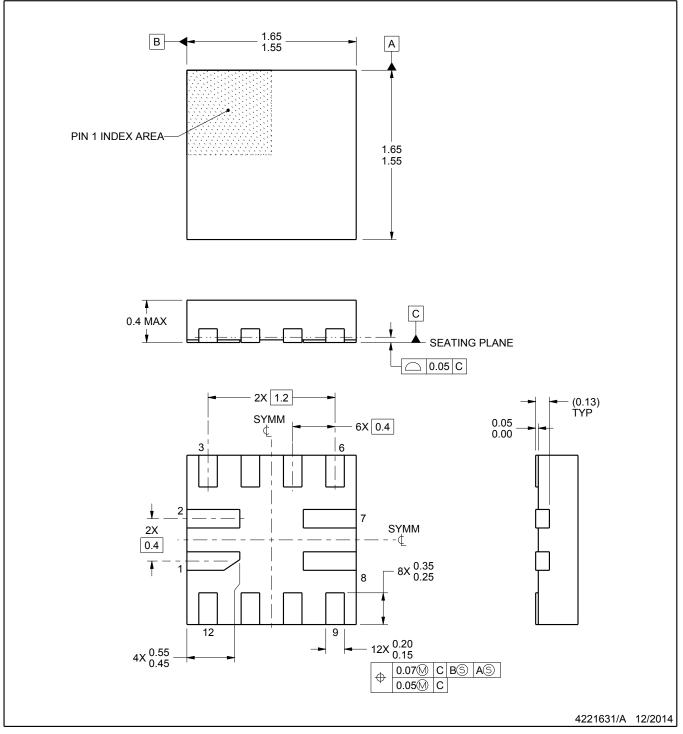

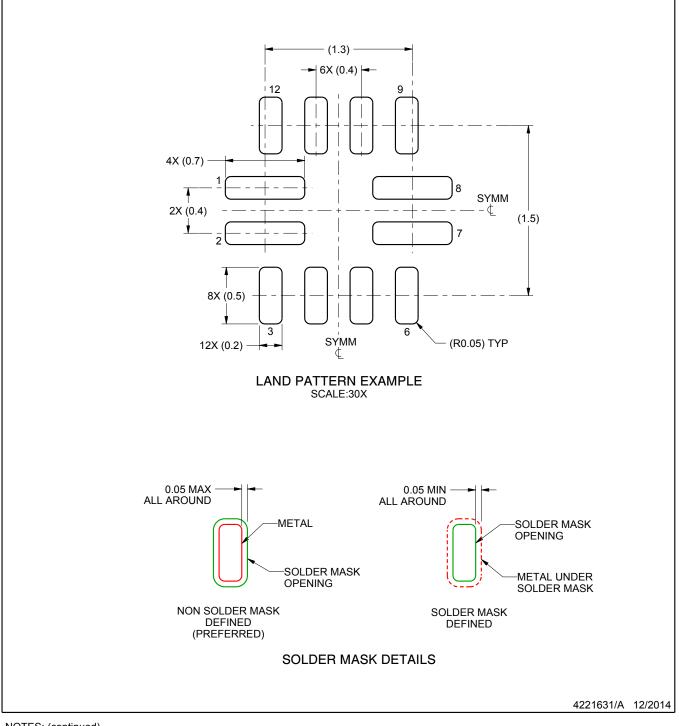

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |  |  |  |

|-------------|------------|-------------------|--|--|--|--|--|

| TUSB320LAI  | X2QFN (12) | 1.60 mm × 1.60 mm |  |  |  |  |  |

| TUSB320HAI  | X2QFN (12) | 1.60 mm × 1.60 mm |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

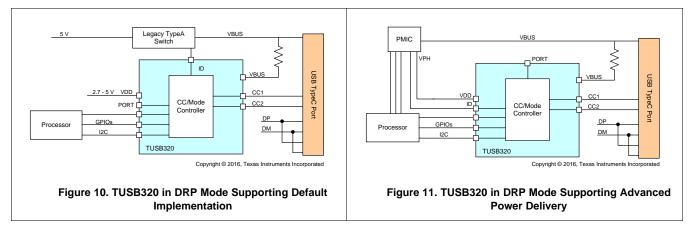

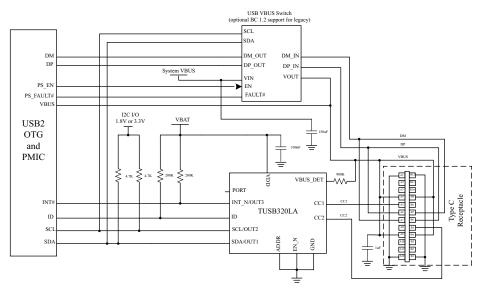

### Sample Applications

2

# **Table of Contents**

7.5

11.2

11.3

8

9

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications1                         |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Timing Requirements 6              |

|   | 6.7  | Switching Characteristics 6        |

| 7 | Deta | ailed Description 8                |

|   | 7.1  | Overview                           |

|   | 7.2  | Feature Description9               |

|   | 7.3  | Device Functional Modes 13         |

|   |      |                                    |

#### Revision History 4

-

| С | hanges from Revision A (March 2016) to Revision B                                                                            | Page |

|---|------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed pins CC1 and CC2 values From: MIN = -0.3 MAX = VDD + 0.3 To: MIN -0.3 MAX = 6 in the <i>Absolute Maximum Ratings</i> | 4    |

| с | hanges from Original (October 2015) to Revision A                                                                            | Page |

| A |   |

|---|---|

|   | A |

| • | Added Note 1 and 2 to the Pin Functions table                                            | . 3 |

|---|------------------------------------------------------------------------------------------|-----|

| • | Changed the DESCRIPTION of pin EN_N pin in the Pin Functions table                       | 3   |

| • | Changed the DESCRIPTION of pin EN pin in the Pin Functions table                         | 3   |

| • | Changed the DESCRIPTION of pin V <sub>DD</sub> in the <i>Pin Functions</i> table         | . 3 |

| • | Added Note 2 to the Electrical Characteristics table                                     | . 5 |

| • | Added Test Condition "See Figure 1" to VBUS_THR in the <i>Electrical Characteristics</i> | 6   |

| • | Changed the last sentence of the <i>Debug Accessory</i> section                          | 12  |

| • | Added Note: "SW must make sure" to the Description of INTERRUPT_STATUS in Table 9        | 18  |

| • | Added text to list item 2 in the TUSB320LA Initialization Procedure section              | 28  |

| • | Added text to list item 2 in the TUSB320HA Initialization Procedure section              | 28  |

|   |                                                                                          |     |

STRUMENTS

EXAS

7.4 Programming..... 15

8.1 Application Information...... 21

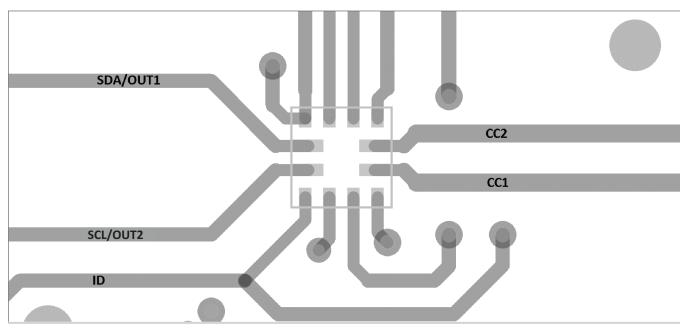

10.1 Layout Guidelines ..... 29 10.2 Layout Example ..... 29 11 Device and Documentation Support ...... 30 11.1 Related Links ...... 30

Register Maps ..... 16 Application and Implementation ...... 21

Trademarks ...... 30

11.5 Glossary ...... 30

12 Mechanical, Packaging, and Orderable

# Dago

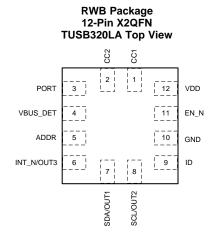

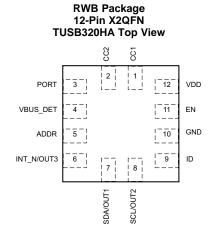

#### Pin Configuration and Functions 5

#### **Pin Functions**

| PIN                        |           | TYPE      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------------------------|-----------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                       | TUSB320LA | TUSB320HA | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CC1                        | 1         | 1         | I/O  | Type-C configuration channel signal 1                                                                                                                                                                                                                                                                                                                                                                                               |  |

| CC2                        | 2         | 2         | I/O  | Type-C configuration channel signal 2                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PORT <sup>(1)</sup>        | 3         | 3         | I    | Tri-level input pin to indicate port mode. The state of this pin is sampled when EN_N is asserted low in the TUSB320L device, EN is asserted high in the TUSB320H device, and VDD is active. This pin is also sampled following a I2C_SOFT_RESET.<br>H - DFP (Pull-up to V <sub>DD</sub> if DFP mode is desired)<br>NC - DRP (Leave unconnected if DRP mode is desired)<br>L - UFP (Pull-down or tie to GND if UFP mode is desired) |  |

| VBUS_DET <sup>(1)</sup>    | 4         | 4         | I    | 5-V to 28-V V <sub>BUS</sub> input voltage. V <sub>BUS</sub> detection determines UFP attachment. One 900-k $\Omega$ external resistor required between system V <sub>BUS</sub> and VBUS_DET pin.                                                                                                                                                                                                                                   |  |

| ADDR <sup>(1)</sup>        | 5         | 5         | I    | Tri-level input pin to indicate I <sup>2</sup> C address or GPIO mode:<br>H — I <sup>2</sup> C is enabled and I <sup>2</sup> C 7-bit address is 0x67.<br>NC — GPIO mode (I <sup>2</sup> C is disabled)<br>L — I <sup>2</sup> C is enabled and I <sup>2</sup> C 7-bit address is 0x47.<br>ADDR pin should be pulled up to V <sub>DD</sub> if high configuration is desired                                                           |  |

| INT_N/OUT3 <sup>(1)</sup>  | 6         | 6         | Ο    | The INT_N/OUT3 is a dual-function pin. When used as the INT_N, the pin is an open drain output in I <sup>2</sup> C control mode and is an active low interrupt signal for indicating changes in I <sup>2</sup> C registers. When used as OUT3, the pin is in audio accessory detect in GPIO mode: no detection (H), audio accessory connection detected (L).                                                                        |  |

| SDA/OUT1 <sup>(1)(2)</sup> | 7         | 7         | I/O  | The SDA/OUT1 is a dual-function pin. When I <sup>2</sup> C is enabled (ADDR pin is high or low), this pin is the I <sup>2</sup> C communication data signal. When in GPIO mode (ADDR pin is NC), this pin is an open drain output for communicating Type-C current mode detect when the device is in UFP mode: default current mode detected (H); medium or high current mode detected (L).                                         |  |

| SCL/OUT2 <sup>(1)(2)</sup> | 8         | 8         | I/O  | The SCL/OUT2 is a dual function pin. When I <sup>2</sup> C is enabled (ADDR pin is high or low), this pin is the I <sup>2</sup> C communication clock signal. When in GPIO mode (ADDR pin is NC), this pin is an open drain output for communicating Type-C current mode detect when the device is in UFP mode: default or medium current mode detected (H); high current mode detected (L).                                        |  |

| ID                         | 9         | 9         | 0    | Open drain output; asserted low when the CC pins detect device attachment when port is a source (DFP), or dual-role (DRP) acting as source (DFP).                                                                                                                                                                                                                                                                                   |  |

| GND                        | 10        | 10        | G    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| EN_N                       | 11        | _         | I    | Enable signal; active low. Pulled up to $V_{DD}$ internally to disable the TUSB320L device. If controlled externally, must be held low at least for 50 ms after VDD has reached its valid voltage level.                                                                                                                                                                                                                            |  |

| EN                         | -         | 11        | I    | Enable signal; active high. Pulled down to GND internally to disable the TUSB320H device. If controlled externally, must be held low at least for 50 ms after VDD has reached its valid voltage level.                                                                                                                                                                                                                              |  |

| V <sub>DD</sub>            | 12        | 12        | Р    | Positive supply voltage. V <sub>DD</sub> must ramp within 25 ms or less                                                                                                                                                                                                                                                                                                                                                             |  |

(1) When V<sub>DD</sub> is off, the TUSB320 non-failsafe pins (VBUS\_DET, ADDR, PORT, OUT[3:1] pins) could back-drive the TUSB320 device if not handled properly. When necessary to pull these pins up, it is recommended to pullup PORT, ADDR, and INT\_N/OUT3 to the device V<sub>DD</sub> supply. The VBUS\_DET must be pulled up to VBUS through a 900-k $\Omega$  resistor. When using the 3.3 V supply for I<sup>2</sup>C, the end user must ensure that the V<sub>DD</sub> is 3 V and above. Otherwise the I<sup>2</sup>C may back power the

(2)device.

Copyright © 2015–2016, Texas Instruments Incorporated

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                 |                                  | MIN  | MAX                   | UNIT |

|-----------------|----------------------------------|------|-----------------------|------|

| Supply voltage  | V <sub>DD</sub>                  | -0.3 | 6                     | V    |

|                 | PORT, ADDR, ID, EN_N, INT_N/OUT3 | -0.3 | V <sub>DD</sub> + 0.3 |      |

| Control pipe    | CC1, CC2                         | -0.3 | 6                     | V    |

| Control pins    | SDA/OUT1, SCL/OUT2               | -0.3 | V <sub>DD</sub> + 0.3 |      |

|                 | VBUS_DET , EN                    | -0.3 | 4                     |      |

| Storage tempera | iture, T <sub>stg</sub>          | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                   | MIN | NOM | MAX | UNIT |

|------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>DD</sub>  | Supply voltage range                                              | 2.7 |     | 5   | V    |

| V <sub>BUS</sub> | System V <sub>BUS</sub> voltage                                   | 4   | 5   | 28  | V    |

| T <sub>A</sub>   | TUSB320HAI and TUSB320LAI Operating free air temperature<br>range | -40 | 25  | 85  | °C   |

### 6.4 Thermal Information

|                       |                                              | TUSB320     |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RWB (X2QFN) | UNIT |

|                       |                                              | 12 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 169.3       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 68.1        | °C/W |

| $R_{\thetaJB}$        | Junction-to-board thermal resistance         | 83.4        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 2.2         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 83.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and C Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                                | PARAMETER                                                                                                                                                                      | TEST<br>CONDITIONS        | MIN                    | TYP  | MAX                    | UNIT |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|------|------------------------|------|

| POWER CONSUM                   | IPTION                                                                                                                                                                         |                           |                        |      |                        |      |

| IUNATTACHED_UFP                | Current consumption in unattached mode when port is unconnected and waiting for connection. [ $V_{DD}$ = 4.5 V, EN_N (TUSB320LA) = L, EN (TUSB320HA) = H, ADDR = NC, PORT = L] |                           |                        | 70   |                        | μΑ   |

| I <sub>ACTIVE_UFP</sub>        | Current consumption in active mode. [ $V_{DD} = 4.5 V$ , EN_N<br>(TUSB320LA) = L, EN (TUSB320HA) = H, ADDR = NC,<br>PORT = L]                                                  |                           |                        | 70   |                        | μΑ   |

| I <sub>SHUTDOWN</sub>          | Leakage current when $V_{DD}$ is supplied, but the TUSB320 device is not enabled. [ $V_{DD}$ = 4.5 V, EN_N (TUSB320LA) = H, EN (TUSB320HA) = L]                                |                           |                        | 0.04 |                        | μA   |

| CC1 AND CC2 PI                 | NS                                                                                                                                                                             | ł                         | l                      |      |                        |      |

| R <sub>CC_DB</sub>             | Pulldown resistor when in dead-battery mode.                                                                                                                                   |                           | 4.1                    | 5.1  | 6.1                    | kΩ   |

| R <sub>CC_D</sub>              | Pulldown resistor when in UFP or DRP mode.                                                                                                                                     |                           | 4.6                    | 5.1  | 5.6                    | kΩ   |

| V <sub>UFP_CC_USB</sub>        | Voltage level range for detecting a DFP attach when<br>configured as a UFP and DFP is advertising default current<br>source capability.                                        |                           | 0.25                   |      | 0.61                   | V    |

| V <sub>UFP_CC_MED</sub>        | Voltage level range for detecting a DFP attach when configured as a UFP and DFP is advertising medium (1.5-A) current source capability.                                       |                           | 0.7                    |      | 1.16                   | V    |

| V <sub>UFP_CC_HIGH</sub>       | Voltage level range for detecting a DFP attach when<br>configured as a UFP and DFP is advertising high (3-A)<br>current source capability.                                     |                           | 1.31                   |      | 2.04                   | V    |

| V <sub>TH_DFP_CC_USB</sub>     | Voltage threshold for detecting a UFP attach when<br>configured as a DFP and advertising default current source<br>capability.                                                 |                           | 1.51                   | 1.6  | 1.64                   | V    |

| V <sub>TH_DFP_CC_MED</sub>     | Voltage threshold for detecting a UFP attach when configured as a DFP and advertising medium current (1.5-A) source capability.                                                |                           | 1.51                   | 1.6  | 1.64                   | V    |

| V <sub>TH_DFP_CC_HIGH</sub>    | Voltage threshold for detecting a UFP attach when<br>configured as a DFP and advertising high current (3.0-A)<br>source capability.                                            |                           | 2.46                   | 2.6  | 2.74                   | V    |

| I <sub>CC_DEFAULT_P</sub>      | Default mode pullup current source when operating in DFP or DRP mode.                                                                                                          |                           | 64                     | 80   | 96                     | μA   |

| I <sub>CC_MED_P</sub>          | Medium (1.5-A) mode pullup current source when<br>operating in DFP or DRP mode.                                                                                                |                           | 166                    | 180  | 194                    | μA   |

| I <sub>CC_HIGH_P</sub>         | High (3-A) mode pullup current source when operating in DFP or DRP mode. $^{(1)}$                                                                                              |                           | 304                    | 330  | 356                    | μΑ   |

| CONTROL PINS:                  | PORT, ADDR, INT/OUT3, EN_N, EN, ID                                                                                                                                             |                           | 1                      |      |                        |      |

| V <sub>IL</sub>                | Low-level control signal input voltage (PORT, ADDR, EN_N, EN)                                                                                                                  |                           |                        |      | 0.4                    | V    |

| V <sub>IM</sub>                | Mid-level control signal input voltage (PORT, ADDR)                                                                                                                            |                           | 0.28 × V <sub>DD</sub> | (    | 0.56 × V <sub>DD</sub> | V    |

| V <sub>IH</sub>                | High-level control signal input voltage (PORT, ADDR, EN_N)                                                                                                                     |                           | V <sub>DD</sub> - 0.3  |      | $V_{DD}$               | V    |

| V <sub>IH_EN</sub>             | High-Level control signal input voltage for EN for TUSB320HA                                                                                                                   |                           | 1.05                   |      | 3.65                   | V    |

| I <sub>IH</sub>                | High-level input current                                                                                                                                                       |                           | -20                    |      | 20                     | μA   |

| IIL                            | Low-level input current                                                                                                                                                        |                           | -10                    |      | 10                     | μA   |

| I <sub>ID_LEAKAGE</sub>        | Current Leakage on ID pin                                                                                                                                                      | $V_{DD} = 0 V; ID = 5 V$  |                        |      | 10                     | μA   |

| R <sub>EN_N</sub>              | Internal pullup resistance for EN_N for TUSB320LA                                                                                                                              |                           |                        | 1.1  |                        | MΩ   |

| R <sub>EN</sub>                | Internal pulldown resistance for EN for TUSB320HA                                                                                                                              |                           |                        | 500  |                        | kΩ   |

| R <sub>pu</sub> <sup>(2)</sup> | Internal pullup resistance (PORT, ADDR)                                                                                                                                        |                           |                        | 588  |                        | kΩ   |

| R <sub>pd</sub> <sup>(2)</sup> | Internal pulldown resistance (PORT, ADDR)                                                                                                                                      |                           |                        | 1.1  |                        | MΩ   |

| V <sub>OL</sub>                | Low-level signal output voltage (open-drain) (INT_N/OUT3, ID)                                                                                                                  | I <sub>OL</sub> = -1.6 mA |                        |      | 0.4                    | V    |

(1) V<sub>DD</sub> must be 3.5 V or greater to advertise 3 A current.

(2) Internal pullup and pulldown for PORT and ADDR are removed after the device has sampled EN = high or EN\_N = low.

SLLSEQ8B-OCTOBER 2015-REVISED SEPTEMBER 2016

STRUMENTS www.ti.com

EXAS

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                          | TEST<br>CONDITIONS        | MIN  | ТҮР | МАХ | UNIT |

|----------------------------|--------------------------------------------------------------------|---------------------------|------|-----|-----|------|

| R <sub>p_ODext</sub>       | External pullup resistor on open drain IOs (INT_N/OUT3, ID)        |                           |      | 200 |     | kΩ   |

| R <sub>p_TLext</sub>       | Tri-level input external pullup resistor (PORT, ADDR)              |                           |      | 4.7 |     | kΩ   |

| I <sup>2</sup> C - SDA/OUT | Г1, SCL/OUT2 CAN OPERATE FROM 1.8 V OR 3.3 V (±10%) <sup>(3)</sup> |                           |      |     |     |      |

| V <sub>DD_I2C</sub>        | Supply range for I <sup>2</sup> C (SDA/OUT1, SCL/OUT2)             |                           | 1.65 | 1.8 | 3.6 | V    |

| V <sub>IH</sub>            | High-level signal voltage                                          |                           | 1.05 |     | 3.6 | V    |

| V <sub>IL</sub>            | Low-level signal voltage                                           |                           |      |     | 0.4 | V    |

| V <sub>OL</sub>            | Low-level signal output voltage (open drain)                       | I <sub>OL</sub> = -1.6 mA |      |     | 0.4 | V    |

| VBUS_DET IC                | PINS (CONNECTED TO SYSTEM V <sub>BUS</sub> SIGNAL)                 |                           |      |     |     |      |

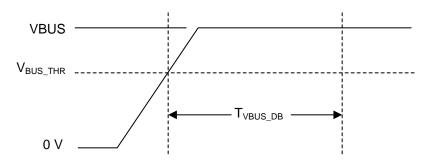

| V <sub>BUS_THR</sub>       | V <sub>BUS</sub> threshold range                                   | See Figure 1              | 2.95 | 3.3 | 3.8 | V    |

| R <sub>VBUS</sub>          | External resistor between $V_{BUS}$ and $VBUS\_DET$ pin            |                           | 891  | 900 | 909 | KΩ   |

| R <sub>VBUS_PD</sub>       | Internal pulldown resistance for VBUS_DET                          |                           |      | 95  |     | KΩ   |

(3) When using 3.3 V for  $I^2C,$  customer must ensure  $V_{DD}$  is above 3.0 V at all times.

## 6.6 Timing Requirements

|                           |                                                                               | MIN | NOM MAX | UNIT |

|---------------------------|-------------------------------------------------------------------------------|-----|---------|------|

| I <sup>2</sup> C (SDA, SC | CL)                                                                           |     |         |      |

| t <sub>SU:DAT</sub>       | Data setup time                                                               | 100 |         | ns   |

| t <sub>HD;DAT</sub>       | Data hold time                                                                | 10  |         | ns   |

| t <sub>SU:STA</sub>       | Set-up time, SCL to start condition                                           | 0.6 |         | μs   |

| t <sub>HD:STA</sub>       | Hold time (repeated), start condition to SCL                                  | 0.6 |         | μs   |

| t <sub>SU:STO</sub>       | Set up time for stop condition                                                | 0.6 |         | μs   |

| t <sub>BUF</sub>          | Bus free time between a stop and start condition                              | 1.3 |         | μs   |

| t <sub>VD;DAT</sub>       | Data valid time                                                               |     | 0.9     | μs   |

| t <sub>VD;ACK</sub>       | Data valid acknowledge time                                                   |     | 0.9     | μs   |

| f <sub>SCL</sub>          | SCL clock frequency; I <sup>2</sup> C mode for local I <sup>2</sup> C control |     | 400     | kHz  |

| t <sub>r</sub>            | Rise time of both SDA and SCL signals                                         |     | 300     | ns   |

| t <sub>f</sub>            | Fall time of both SDA and SCL signals                                         |     | 300     | ns   |

| C <sub>BUS_100KHZ</sub>   | Total capacitive load for each bus line when operating at $\leq$ 100 kHz      |     | 400     | pF   |

| C <sub>BUS_400KHz</sub>   | Total capacitive load for each bus line when operating at 400 kHz             |     | 100     | pF   |

# 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                                                                         | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|------|

| tCCCB_DEFAULT           | Power on default of CC1 and CC2 voltage debounce time                                                             | DEBOUCE<br>register = 2'b00        |     | 168 |     | ms   |

| t <sub>VBUS_DB</sub>    | Debounce of VBUS_DET pin after valid $V_{BUS_{THR}}$                                                              |                                    |     | 2   |     | ms   |

| tDRP_DUTY_CYCLE         | Power-on default of percentage of time DRP advertises DFP during a t <sub>DRP</sub>                               | DRP_DUTY_CYCLE<br>register = 2'b00 |     | 30% |     |      |

| t <sub>DRP</sub>        | The period during which the TUSB320HA or the TUSB320LA in DFP mode completes a DFP to UFP and back advertisement. |                                    | 50  | 75  | 100 | ms   |

| t <sub>I2C_EN</sub>     | Time from TUSB320LA EN_N low or TUSB320HA EN high and $V_{\text{DD}}$ active to $I^2\text{C}$ access available    |                                    |     |     | 100 | ms   |

| t <sub>SOFT_RESET</sub> | Soft reset duration                                                                                               |                                    | 26  | 49  | 95  | ms   |

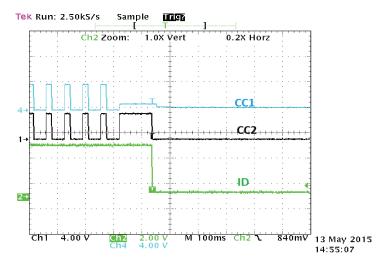

Figure 1. VBUS Detect and Debounce

# 7 Detailed Description

### 7.1 Overview

The USB Type-C ecosystem operates around a small form factor connector and cable that is flippable and reversible. Because of the nature of the connector, a scheme is required to determine the connector orientation. Additional schemes are required to determine when a USB port is attached and what the acting role of the USB port (DFP, UFP, DRP) is, as well as to communicate Type-C current capabilities. These schemes are implemented over the CC pins according to the USB Type-C pecification. The TUSB320 devices provide Configuration Channel (CC) logic for determining USB port attach and detach, role detection, cable orientation, and Type-C current mode. The TUSB320 devices also contains several features such as mode configuration and low standby current which make these devices ideal for source or sinks in USB2.0 applications.

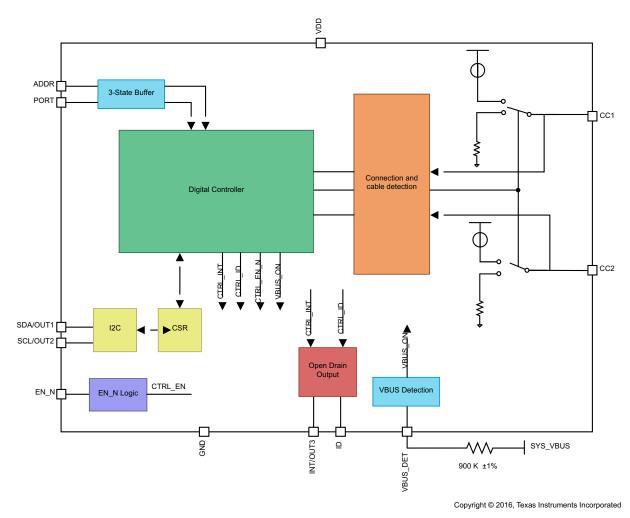

Figure 2. Functional Block Diagram of TUSB320

### 7.1.1 Cables, Adapters, and Direct Connect Devices

Type-C specification defines several cables, plugs, and receptacles to be used to attach ports. The TUSB320 devices support all cables, receptacles, and plugs. The TUSB320 devices do not support any USB Type-C feature which requires USB power delivery communication over CC lines like e-marking or alternate mode.

### 7.1.1.1 USB Type-C Receptacles and Plugs

Below is list of Type-C receptacles and plugs supported by the TUSB320 devices:

• USB Type-C receptacle for USB2.0 platforms and devices

#### TUSB320LAI, TUSB320HAI SLLSEQ8B-OCTOBER 2015-REVISED SEPTEMBER 2016

## **Overview (continued)**

- USB full-featured Type-C plug

- USB2.0 Type-C plug

# 7.1.1.2 USB Type-C Cables

Below is a list of Type-C cables types supported by the TUSB320 devices:

- USB full-featured Type-C cable

- USB2.0 Type-C cable with USB2.0 plug

- Captive cable on remote device with either a USB full-featured plug or USB2.0 plug

# 7.1.1.3 Legacy Cables and Adapters

The TUSB320 devices support legacy cable adapters as defined by the Type-C specification. The cable adapter must correspond to the mode configuration of a TUSB320 device.

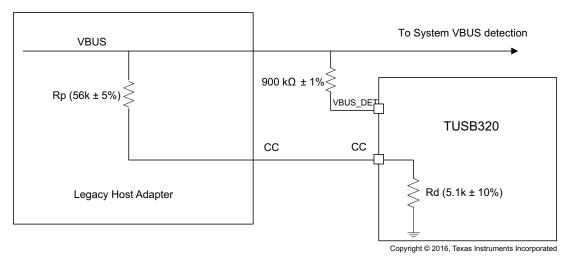

Figure 3 displays the TUSB320 Legacy Adapter Implementation Circuit.

Figure 3. Legacy Adapter Implementation Circuit

# 7.1.1.4 Direct Connect Devices

The TUSB320 devices support the attaching and detaching of a direct-connect device.

### 7.1.1.5 Audio Adapters

Additionally, the TUSB320 devices support audio adapters for audio accessory mode, including:

- Passive Audio Adapter

- Charge Through Audio Adapter

# 7.2 Feature Description

### 7.2.1 Port Role Configuration

The TUSB320 devices can be configured as a downstream facing port (DFP), upstream facing port (UFP), or dual-role port (DRP) using the tri-level PORT pin. The PORT pin should be pulled high to  $V_{DD}$  using a pullup resistance, low to GND or left as floated on the PCB to achieve the desired mode. This flexibility allows a TUSB320 device to be used in a variety of applications. A TUSB320 device samples the PORT pin after reset and maintains the desired mode until the TUSB320 device is reset again. The port role can also be selected through I<sup>2</sup>C registers. Table 1 lists the supported features in each mode:

Copyright © 2015–2016, Texas Instruments Incorporated

### Feature Description (continued)

| Table 1. Supported | Features for the | e TUSB320 Device | by Mode |

|--------------------|------------------|------------------|---------|

|--------------------|------------------|------------------|---------|

| PORT PIN                                     | PORT PIN           |                   |             |  |  |  |  |  |  |

|----------------------------------------------|--------------------|-------------------|-------------|--|--|--|--|--|--|

| SUPPORTED<br>FEATURES                        | HIGH<br>(DFP ONLY) | LOW<br>(UFP ONLY) | NC<br>(DRP) |  |  |  |  |  |  |

| Port attach and detach                       | Yes                | Yes               | Yes         |  |  |  |  |  |  |

| Cable orientation (through I <sup>2</sup> C) | Yes                | Yes               | Yes         |  |  |  |  |  |  |

| Current advertisement                        | Yes                | -                 | Yes (DFP)   |  |  |  |  |  |  |

| Current detection                            | -                  | Yes               | Yes (UFP)   |  |  |  |  |  |  |

| Accessory modes<br>(audio and debug)         | Yes                | Yes               | Yes         |  |  |  |  |  |  |

| Try.SRC                                      | -                  | -                 | Yes         |  |  |  |  |  |  |

| Try.SNK                                      | -                  | -                 | Yes         |  |  |  |  |  |  |

| Active cable detection                       | Yes                | -                 | Yes (DFP)   |  |  |  |  |  |  |

| I <sup>2</sup> C / GPIO                      | Yes                | Yes               | Yes         |  |  |  |  |  |  |

| Legacy cables                                | Yes                | Yes               | Yes         |  |  |  |  |  |  |

| V <sub>BUS</sub> detection                   | -                  | Yes               | Yes (UFP)   |  |  |  |  |  |  |

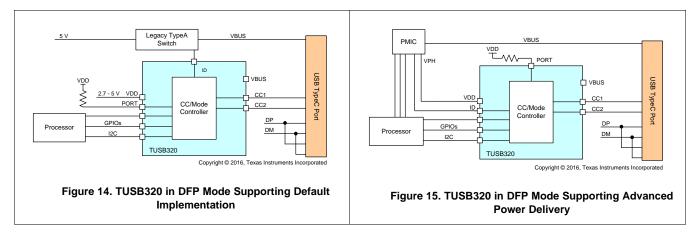

#### 7.2.1.1 Downstream Facing Port (DFP) - Source

The TUSB320 device can be configured as a DFP-only by pulling the PORT pin high through a resistance to  $V_{DD}$  or by changing the MODE\_SELECT register. In DFP-only mode, the TUSB320 device constantly presents Rps on both CC. In DFP-only mode, the TUSB320 device initially advertises default USB Type-C current. The Type-C current can be adjusted through I<sup>2</sup>C if the system requires to increase the amount advertised. The TUSB320 device only advertises default Type-C current. In GPIO mode, the TUSB320 device only advertises default Type-C current.

When configured as a DFP, the TUSB320 device can operate with older USB Type-C 1.0 devices except for a USB Type-C 1.0 DRP device. A USB Type-C 1.1 compliant DFP can not connect to a Type-C 1.0 DRP. Because the TUSB320 device is compliant to Type-C 1.1, the TUSB320 device can not operate with a USB Type-C 1.0 DRP device. This limitation is a result of a backwards compatibility problem between USB Type-C 1.1 DFP and a USB Type-C 1.0 DRP.

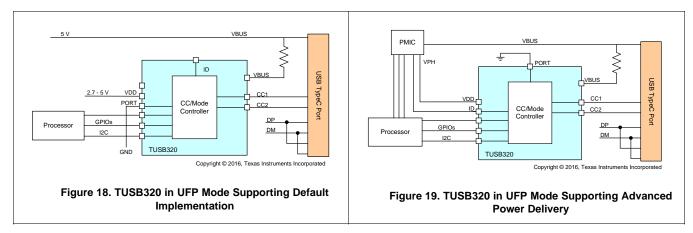

### 7.2.1.2 Upstream Facing Port (UFP) - Sink

The TUSB320 device can be configured as a UFP only by pulling the PORT pin low to GND. In UFP mode, the TUSB320 device constantly presents pulldown resistors (Rd) on both CC pins. The TUSB320 device monitors the CC pins for the voltage level corresponding to the Type-C mode current advertisement by the connected DFP. The TUSB320 device debounces the CC pins and wait for  $V_{BUS}$  detection before successfully attaching. As a UFP, the TUSB320 device detects and communicates the advertised current level of the DFP to the system through the OUT1 and OUT2 GPIOs (if in GPIO mode) or through the I<sup>2</sup>C CURRENT\_MODE\_DETECT register one time in the Attached.SNK state.

### 7.2.1.3 Dual Role Port (DRP)

The TUSB320 device can be configured to operate as a DRP when the PORT pin is left floated on the PCB. In DRP mode, the TUSB320 device toggles between operating as a DFP and a UFP. When functioning as a DFP in DRP mode, the TUSB320 device complies with all operations as defined for a DFP according to the Type-C specification. When presenting as a UFP in DRP mode, the TUSB320 device operates as defined for a UFP according to the Type-C specification.

The TUSB320 supports two optional Type-C DRP features called Try.SRC and Try.SNK. Products supporting dual-role functionality may have a requirement to be a source (DFP) or a sink (UFP) when connected to another dual-role capable product. For example, a dual-role capable notebook can be a source when connected to a tablet, or a cell phone can be a sink when connected to a notebook or tablet. When standard DRP products (products which don't support either Try.SRC or Try.SNK) are connected together, the role (UFP or DFP) outcome is not predetermined. These two optional DRP features provide a means for dual-role capable products to connect to another dual-role capable product in the role desired. Try.SRC and Try.SNK are only available when TUSB320 is configured in I2C mode. When operating in GPIO mode, the TUSB320 will always operate as a standard DRP.

The Try.SRC feature of the TUSB320 device provides a means for a DRP product to connect as a DFP when connected to another DRP product that doesn't implement Try.SRC. When two products which implement Try.SRC are connected together, the role outcome of either UFP or DFP is the same as a standard DRP. Try.SRC is enabled by changing I2C register SOURCE\_PREF to 2'b11. Once this register is changed to 2'b11, the TUSB320 will always attempt to connect as a DFP when attached to another DRP capable device.

The Try.SNK feature of the TUSB320 device provides a method for a DRP product to connect as a UFP when connected to another DRP product that doesn't implement Try.SNK. When two products which implement Try.SNK are connected together, the role outcome of either UFP or DFP is the same as a standard DRP. Try.SNK is enabled by changing I2C register SOURCE\_PREF to 2'b01. Once this register is changed to 2'b01, the TUSB320 will always attempt to connect as a UFP when attached to another DRP capable device.

### 7.2.2 Type-C Current Mode

When a valid cable detection and attach have been completed, the DFP has the option to advertise the level of Type-C current a UFP can sink. The default current advertisement for the TUSB320 device is max of 500 mA (for USB2.0) or max of 900 mA (for USB3.1). If a higher level of current is available, the I<sup>2</sup>C registers can be written to provide medium current at 1.5 A or high current at 3 A. When the CURRENT\_MODE\_ADVERTISE register has been written to advertise higher than default current, the DFP adjusts the Rps for the specified current level. If a DFP advertises 3 A, system designer must ensure that the V<sub>DD</sub> of the TUSB320 device is 3.5 V or greater. Table 2 lists the Type-C current advertisements in GPIO an I<sup>2</sup>C modes.

| TYPE-C CURRENT                           |                                                        | GPIO MODE (AI                                    | DDR PIN IN NC)     | I <sup>2</sup> C MODE (ADDR PIN H, L)                   |                                                                        |  |

|------------------------------------------|--------------------------------------------------------|--------------------------------------------------|--------------------|---------------------------------------------------------|------------------------------------------------------------------------|--|

| TTPE-C                                   | CURRENT                                                | UFP (PORT PIN L) DFP (PORT PIN H)                |                    | UFP                                                     | DFP                                                                    |  |

| Default                                  | max of 500<br>mA (USB2.0)<br>max of 900<br>mA (USB3.1) | Current mode detected<br>and output through OUT1 | Only advertisement | Current mode detected and read through I <sup>2</sup> C | I <sup>2</sup> C register default is 500<br>or 900 mA (max)            |  |

| Medium - 1.5 A (max)<br>High - 3 A (max) |                                                        | / OUT2                                           | N/A                | register                                                | Advertisement selected<br>through writing I <sup>2</sup> C<br>register |  |

Table 2. Type-C Current Advertisement for GPIO and I<sup>2</sup>C Modes

### 7.2.3 Accessory Support

The TUSB320 device supports audio and debug accessories in UFP, DFP mode and DRP mode. Audio and debug accessory support is provided through reading of I<sup>2</sup>C registers. Audio accessory is also supported through GPIO mode with INT\_N/OUT3 pin (audio accessory is detected when INT\_N/OUT3 pin is low).

### 7.2.3.1 Audio Accessory

Audio accessory mode is supported through two types of adapters. First, the passive audio adapter can be used to convert the Type-C connector into an audio port. To effectively detect the passive audio adapter, the TUSB320 device must detect a resistance < Ra on both of the CC pins.

Secondly, a charge through audio adapter can be used. The primary difference between a passive and charge through adapter is that the charge through adapter supplies 500 mA of current over VBUS. The charge through adapter contains a receptacle and a plug. The plug acts as a DFP and supply  $V_{BUS}$  when the plug detects a connection.

When the TUSB320 device is configured in GPIO mode, OUT3 pin determines if an audio accessory is connected. When an audio accessory is detected, the OUT3 pin is pulled low.

Copyright © 2015–2016, Texas Instruments Incorporated

#### 7.2.3.2 Debug Accessory

Debug is an additional state supported by USB Type-C. The specification does not define a specific user scenario for this state, but the specification is important because the end user could use debug accessory mode to enter a test state for production specific to the application. The TUBS320 device will detect a debug accessory if  $R_d$  or  $R_p$  is detected on both CC1 and CC2.

#### 7.2.4 I<sup>2</sup>C and GPIO Control

The TUSB320 device can be configured for I<sup>2</sup>C communication or GPIO outputs using the ADDR pin. The ADDR pin is a tri-level control pin. When the ADDR pin is left floating (NC), the TUSB320 device is in GPIO output mode. When the ADDR pin is pulled high or pulled low, the TUSB320 device is in I<sup>2</sup>C mode.

All outputs for the TUSB320 device are open drain configuration.

The OUT1 and OUT2 pins are used to output the Type-C current mode when in GPIO mode. Additionally, the OUT3 pin is used to communicate the audio accessory mode in GPIO mode. Table 3 lists the output pin settings. See the *Pin Configuration and Functions* section for more information.

#### Table 3. Simplified Operation for OUT1 and OUT2

| OUT1 | OUT2 | ADVERTISEMENT                            |

|------|------|------------------------------------------|

| Н    | Н    | Default Current in Unattached State      |

| Н    | L    | Default Current in Attached State        |

| L    | Н    | Medium Current (1.5 A) in Attached State |

| L    | L    | High Current (3.0 A) in Attached State   |

When operating in  $I^2C$  mode, the TUSB320 device uses the SCL and SDA lines for clock and data and the INT\_N pin to communicate a change in  $I^2C$  registers, or an interrupt, to the system. The INT\_N pin is pulled low when the TUSB320 device updates the registers with new information. The INT\_N pin is open drain. The INTERRUPT\_STATUS register will be set when the INT\_N pin is pulled low. To clear the INTERRUPT\_STATUS register, the end user writes to  $I^2C$ .

When operating in GPIO mode, the OUT3 pin is used in place of the INT\_N pin to determine if an audio accessory is detected and attached. The OUT3 pin is pulled low when an audio accessory is detected.

#### NOTE

When using the 3.3 V supply for  $I^2C$ , the end user must ensure that the V<sub>DD</sub> is 3 V and above. Otherwise the  $I^2C$  can back power the device.

#### 7.2.5 V<sub>BUS</sub> Detection

The TUSB320 device supports  $V_{BUS}$  detection according to the Type-C specification.  $V_{BUS}$  detection is used to determine the attachment and detachment of a UFP and to determine the entering and exiting of accessary modes.  $V_{BUS}$  detection is also used to successfully resolve the role in DRP mode.

The system  $V_{BUS}$  voltage must be routed through a 900-k $\Omega$  resistor to the VBUS\_DET pin on the TUSB320 device if the PORT pin is configured as a DRP or a UFP. If the TUSB320 device is configured as a DFP and only ever used in DFP mode, the VBUS\_DET pin can be left unconnected.

#### 7.3 Device Functional Modes

The TUSB320 device has four functional modes. Table 4 lists these modes:

| MODES        | GENERAL BEHAVIOR                                                                | PORT PIN    | STATES <sup>(1)</sup>                              |

|--------------|---------------------------------------------------------------------------------|-------------|----------------------------------------------------|

|              |                                                                                 |             | Unattached.SNK                                     |

|              |                                                                                 | UFP         | Unattached.Accessory                               |

|              |                                                                                 | UFF         | AttachWait.Accessory                               |

| Unattached   | USB port unattached. ID, PORT operational. I <sup>2</sup> C on. CC pins         |             | AttachWait.SNK                                     |

| Unallacheu   | configure according to PORT pin.                                                | DRP         | Toggle Unattached.SNK $\rightarrow$ Unattached.SRC |

|              |                                                                                 | DKP         | AttachedWait.SRC or AttachedWait.SNK               |

|              |                                                                                 | DFP         | Unattached.SRC                                     |

|              |                                                                                 | DFF         | AttachWait.SRC                                     |

|              | USB port attached. All GPIOs operational. I <sup>2</sup> C on.                  |             | Attached.SNK                                       |

|              |                                                                                 | UFP         | Audio accessory                                    |

|              |                                                                                 |             | Debug accessory.SNK                                |

|              |                                                                                 |             | Attached.SNK                                       |

| Active       |                                                                                 | DRP         | Attached.SRC                                       |

| Active       |                                                                                 | DKF         | Audio accessory                                    |

|              |                                                                                 |             | Debug accessory.SNK or Debug accessory.SRC         |

|              |                                                                                 |             | Attached.SRC                                       |

|              |                                                                                 | DFP         | Audio accessory                                    |

|              |                                                                                 |             | Debug accessory.SRC                                |

| Dead battery | No operation.<br>V <sub>DD</sub> not available.                                 | UFP/DRP/DFP | Default device state to UFP/SNK with Rd.           |

| Shutdown     | V <sub>DD</sub> available.<br>TUSB320LA EN_N pin high.<br>TUSB320HA EN pin low. | UFP/DRP/DFP | Default device state to UFP/SNK with Rd.           |

#### Table 4. USB Type-C States According to TUSB320 Functional Modes

(1) Required; not in sequential order.

#### 7.3.1 Unattached Mode

Unattached mode is the primary mode of operation for the TUSB320 device, because a USB port can be unattached for a lengthy period of time. In unattached mode,  $V_{DD}$  is available, and all IOs and I<sup>2</sup>C are operational. After the TUSB320 device is powered up, the part enters unattached mode until a successful attach has been determined. Initially, right after power up, the TUSB320 device comes up as an Unattached.SNK. The TUSB320 device checks the PORT pin and operates according to the mode configuration. The TUSB320 device toggles between the UFP and the DFP if configured as a DRP. In unattached mode, I<sup>2</sup>C can be used to change the mode configuration or port role if the board configuration of the PORT pin is not the desired mode. Writing to the I<sup>2</sup>C MODE\_SELECT register can override the PORT pin in unattached mode. The PORT pin is only sampled at reset (EN\_N high to low transition for the TUSB320LA device or the EN low to high transition for theTUSB320HA device), after I2C\_SOFT\_RESET, or power up. I<sup>2</sup>C must be used after reset to change the device mode configuration.

#### 7.3.2 Active Mode

Active mode is defined as the port being attached. In active mode, all GPIOs are operational, and I<sup>2</sup>C is read / write (R/W). When in active mode, the TUSB320 device communicates to the AP that the USB port is attached. This communication happens through the ID pin if TUSB320 is configured as a DFP or DRP connect as source. If TUSB320 is configured as a UFP or a DRP connected as a sink, the OUT1/OUT2 and INT\_N/OUT3 pins are used. The TUSB320 device exits active mode under the following conditions:

- Cable unplug

- V<sub>BUS</sub> removal if attached as a UFP

- Dead battery; system battery or supply is removed

- TUSB320LA EN\_N pin floated or pulled high

- TUSB320HA EN pin floated or pulled low.

During active mode,  $I^2C$  be used to change the mode configuration following the sequence below. This same sequence is valid when TUSB320 is in unattached mode.

- Set the DISABLE\_TERM register (address 0x0A bit 0) to a 1'b1.

- Change the MODE\_SELECT register (address 0x0A bits 5:4) to desired mode of operation.

- Wait 5 ms.

- Clear the DISABLE\_TERM register (address 0x0A bit 0) to 1'b0.

#### 7.3.3 Dead Battery Mode

During dead battery mode,  $V_{DD}$  is not available. CC pins always default to pulldown resistors in dead battery mode. Dead battery mode means:

- TUSB320 in UFP with 5.1-k $\Omega$  ± 20% Rd; cable connected and providing charge

- TUSB320 in UFP with 5.1-kΩ ± 20% Rd; nothing connected (application could be off or have a discharged battery)

#### NOTE

When V<sub>DD</sub> is off, the TUSB320 non-failsafe pins (VBUS\_DET, ADDR, PORT, OUT[3:1] pins) could back-drive the TUSB320 device if not handled properly. When necessary to pull these pins up, TI recommendeds pulling up PORT, ADDR, and INT\_N/OUT3 to the device's V<sub>DD</sub> supply. The VBUS\_DET must be pulled up to V<sub>BUS</sub> through a 900-k $\Omega$  resistor.

#### 7.3.4 Shutdown Mode

Shutdown mode for TUSB320LA device is defined as follows:

- Supply voltage available and EN\_N pin is pulled high or floating.

- EN\_N pin has internal pullup resistor.

- The TUSB320LA device is off, but still maintains the Rd on the CC pins

Shutdown mode for TUSB320HA device is defined as follows:

- Supply voltage available and EN pin is pulled low or floating.

- EN pin has internal pulldown resistor.

- The TUSB320HA device is off, but still maintains the Rd on the CC pins

#### 7.4 Programming

For further programmability, the TUSB320 device can be controlled using I<sup>2</sup>C. The TUSB320 device local I<sup>2</sup>C interface is available for reading/writing after  $T_{I2C_{EN}}$  when the device is powered up. The SCL and SDA terminals are used for I<sup>2</sup>C clock and I<sup>2</sup>C data respectively. If I<sup>2</sup>C is the preferred method of control, the ADDR pin must be set accordingly.

|          | TUSB320 I <sup>2</sup> C Target Address |       |       |       |       |       |       |             |  |

|----------|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------------|--|

| ADDR pin | Bit 7 (MSB)                             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (W/R) |  |

| Н        | 1                                       | 1     | 0     | 0     | 1     | 1     | 1     | 0/1         |  |

| L        | 1                                       | 0     | 0     | 0     | 1     | 1     | 1     | 0/1         |  |

#### Table 5. TUSB320 I<sup>2</sup>C Addresses

The following procedure should be followed to write to TUSB320 I<sup>2</sup>C registers:

- 1. The master initiates a write operation by generating a start condition (S), followed by the TUSB320 7-bit address and a zero-value R/W bit to indicate a write cycle.

- 2. The TUSB320 device acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within the TUSB320 device) to be written, consisting of one byte of data, MSB-first.

- 4. The TUSB320 device acknowledges the sub-address cycle.

- 5. The master presents the first byte of data to be written to the  $l^2C$  register.

- 6. The TUSB320 device acknowledges the byte transfer.

- 7. The master can continue presenting additional bytes of data to be written, with each byte transfer completing with an acknowledge from the TUSB320 device.

- 8. The master terminates the write operation by generating a stop condition (P).

The following procedure should be followed to read the TUSB320 I<sup>2</sup>C registers:

- 1. The master initiates a read operation by generating a start condition (S), followed by the TUSB320 7-bit address and a one-value R/W bit to indicate a read cycle.

- 2. The TUSB320 device acknowledges the address cycle.

- The TUSB320 device transmits the contents of the memory registers MSB-first starting at register 00h or last read sub-address+1. If a write to the T I<sup>2</sup>C register occurred prior to the read, then the TUSB320 device starts at the sub-address specified in the write.

- The TUSB320 device waits for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master after each byte transfer; the I<sup>2</sup>C master acknowledges reception of each data byte transfer.

- 5. If an ACK is received, the TUSB320 device transmits the next byte of data.

- 6. The master terminates the read operation by generating a stop condition (P).

The following procedure should be followed for setting a starting sub-address for  $I^2C$  reads:

- 1. The master initiates a write operation by generating a start condition (S), followed by the TUSB320 7-bit address and a zero-value R/W bit to indicate a read cycle.

- 2. The TUSB320 device acknowledges the address cycle.

- 3. The master presents the sub-address (I<sup>2</sup>C register within the TUSB320 device) to be read, consisting of one byte of data, MSB-first.

- 4. The TUSB320 device acknowledges the sub-address cycle.

- 5. The master terminates the read operation by generating a stop condition (P).

#### NOTE

If no sub-addressing is included for the read procedure, then the reads start at register offset 00h and continue byte-by-byte through the registers until the  $I^2C$  master terminates the read operation. If a  $I^2C$  address write occurred prior to the read, then the reads start at the sub-address specified by the address write.

Copyright © 2015–2016, Texas Instruments Incorporated

TEXAS INSTRUMENTS

www.ti.com

# 7.5 Register Maps

#### Table 6. CSR Registers

| ACCESS<br>TAG | NAME      | MEANING                                                                                  |

|---------------|-----------|------------------------------------------------------------------------------------------|

| R             | Read      | The field can be read by software.                                                       |

| W             | Write     | The field can be written by software.                                                    |

| S             | Set       | The field can be set by a write of one. Writes of zeros to the field have no effect.     |

| С             | Clear     | The field can be cleared by a write of one. Writes of zeros to the field have no effect. |

| U             | Update    | Hardware can autonomously update this field.                                             |

| NA            | No Access | Not accessible or not applicable.                                                        |

### 7.5.1 CSR Registers (address = 0x00 - 0x07)

#### Figure 4. CSR Registers (address = 0x00 - 0x07)

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---|---|---|---|---|---|---|

| DEVICE_ID |   |   |   |   |   |   |   |

| R         |   |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 7. CSR Registers (address = 0x00 - 0x07)

| Bit | Field     | Туре | Reset | Description                                                                                                                                                    |

|-----|-----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DEVICE_ID | R    |       | For the TUSB320 device these fields return a string of ASCII characters returning TUSB320<br>Addresses 0x07 - 0x00 = {0x00 0x54 0x55 0x53 0x42 0x33 0x32 0x30} |

### 7.5.2 CSR Registers (address = 0x08)

# Figure 5. CSR Registers (address = 0x08)

| 7           | 6           | 5          | 4          | 3    | 2           | 1    | 0                          |

|-------------|-------------|------------|------------|------|-------------|------|----------------------------|

| CURRENT_MOD | E_ADVERTISE | CURRENT_MC | DDE_DETECT | ACCE | SSORY_CONNE | CTED | ACTIVE_CABLE_<br>DETECTION |

| RW          | 1           | RI         | U          |      | RU          |      | RU                         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 8. CSR Registers (address = 0x08)

| Bit | Field                  | Туре | Reset | Description                                                                                                                                     |

|-----|------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                        |      |       | These bits are programmed by the application to raise the current advertisement from default.                                                   |

|     |                        |      |       | 00 - Default (500 mA / 900 mA) initial value at startup                                                                                         |

| 7:6 | CURRENT_MODE_ADVERTISE | RW   | 00    | 01 – Mid (1.5 A)                                                                                                                                |

|     |                        |      |       | 10 – High (3 A)                                                                                                                                 |

|     |                        |      |       | 11 – Reserved                                                                                                                                   |

|     |                        |      |       | These bits are set when a UFP determines the Type-C Current mode.                                                                               |

|     | AUDDENT MODE DETENT    |      |       | 00 – Default (value at start up)                                                                                                                |

| 5:4 | CURRENT_MODE_DETECT    | RU   | 00    | 01 – Medium                                                                                                                                     |

|     |                        |      |       | 10 – Audio Charged through accessory – 500 mA                                                                                                   |

|     |                        |      |       | 11 – High                                                                                                                                       |

|     |                        |      |       | These bits are read by the application to determine if an accessory was attached.                                                               |

|     |                        |      |       | 000 - No accessory attached (default)                                                                                                           |

|     |                        |      |       | 001 – Reserved                                                                                                                                  |

|     |                        |      |       | 010 – Reserved                                                                                                                                  |

| 3:1 | ACCESSORY CONNECTED    | RU   | 000   | 011 – Reserved                                                                                                                                  |

| 0.1 |                        | NO   |       | 100 – Audio accessory                                                                                                                           |

|     |                        |      |       | 101 – Audio charged thru accessory                                                                                                              |

|     |                        |      |       | 110 – Debug accessory when the TUSB320 device is connected as a DFP.                                                                            |

|     |                        |      |       | 111 – Debug accessory when the TUSB320 device is connected as a UFP.                                                                            |

| 0   | ACTIVE_CABLE_DETECTION | RU   | 0     | This flag indicates that an active cable has been plugged into<br>the Type-C connector. When this field is set, an active cable is<br>detected. |

#### TUSB320LAI, TUSB320HAI SLLSEQ8B-OCTOBER 2015-REVISED SEPTEMBER 2016

www.ti.com

**STRUMENTS**

EXAS

# 7.5.3 CSR Registers (address = 0x09)

# Figure 6. CSR Registers (address = 0x09)

| 7          | 6    | 5         | 4                | 3 | 2       | 1       | 0                         |

|------------|------|-----------|------------------|---|---------|---------|---------------------------|

| ATTACHED_S | TATE | CABLE_DIR | INTERRUPT_STATUS | _ | DRP_DUT | Y_CYCLE | DISABLE_UFP_<br>ACCESSORY |

| RU         |      | RU        | RCU              | R | R       | W       | RW                        |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 9. CSR Registers (address = 0x09)

| Bit | Field                 | Туре | Reset             | Description                                                                                                                                                                                                             |

|-----|-----------------------|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                       |      |                   | This is an additional method to communicate attach other than<br>the ID pin. These bits can be read by the application to<br>determine what was attached.                                                               |

| 7:6 | ATTACHED_STATE        | RU   | 00                | 00 – Not attached (default)                                                                                                                                                                                             |

|     | _                     | 110  |                   | 01 – Attached.SRC (DFP)                                                                                                                                                                                                 |

|     |                       |      |                   | 10 – Attached.SNK (UFP)                                                                                                                                                                                                 |

|     |                       |      |                   | 11 – Attached to an accessory                                                                                                                                                                                           |

|     |                       |      | 4                 | Cable orientation. The application can read these bits for cable orientation information.                                                                                                                               |

| 5   | CABLE_DIR             | RU   | 1                 | 0 – CC1                                                                                                                                                                                                                 |

|     |                       |      | 1 – CC2 (default) |                                                                                                                                                                                                                         |

|     | INTERRUPT_STATUS      | RCU  | 0                 | The INT pin is pulled low whenever a CSR with RU in Access field changes. When a CSR change has occurred this bit should be held at 1 until the application clears it. A write of 1'b1 is required to clear this field. |

| 4   |                       |      |                   | 0 – Clear                                                                                                                                                                                                               |

|     |                       |      |                   | 1 – Interrupt (When $INT_N$ is pulled low, this bit will be 1.)                                                                                                                                                         |

|     |                       |      |                   | Note: SW must make sure the INTERRUPT_STATUS has been cleared to zero. Rewrites to this register are needed for the INT_N to be correctly asserted for all interrupt events.                                            |

| 3   | Reserved              | R    | 0                 | Reserved                                                                                                                                                                                                                |

|     |                       |      |                   | Percentage of time that a DRP advertises DFP during tDRP                                                                                                                                                                |

|     |                       |      |                   | 00 – 30% (default)                                                                                                                                                                                                      |

| 2:1 | DRP_DUTY_CYCLE        | RW   | 00                | 01 – 40%                                                                                                                                                                                                                |

|     |                       |      |                   | 10 – 50%                                                                                                                                                                                                                |

|     |                       |      |                   | 11 – 60%                                                                                                                                                                                                                |

|     |                       |      |                   | Settings this field will disable UFP accessory support.                                                                                                                                                                 |

| 0   | DISABLE_UFP_ACCESSORY | RW   | 0                 | 0 – UFP accessory support enabled (Default)                                                                                                                                                                             |

|     |                       |      |                   | 1 – UFP accessory support disabled                                                                                                                                                                                      |

### 7.5.4 CSR Registers (address = 0x0A)

#### Figure 7. CSR Registers (address = 0x0A)

| 7    | 6    | 5      | 4      | 3                           | 2     | 1      | 0            |

|------|------|--------|--------|-----------------------------|-------|--------|--------------|

| DEBO | UNCE | MODE_S | SELECT | I <sup>2</sup> C_SOFT_RESET | SOURC | E_PREF | DISABLE_TERM |

| R    | W    | R      | N      | RSU                         | R     | W      | RW           |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 10. CSR Registers (address = 0x0A)

| Bit | Field                       | Туре | Reset                                                                                                                                                                                                                 | Description                                                                                                                                             |