SCDS358B-NOVEMBER 2014-REVISED FEBRUARY 2015

**TS3A227E**

# TS3A227E Autonomous Audio Accessory Detection and Configuration Switch

#### **Features**

- Supple Range of 2.5 V to 4.5 V

- Accessory Insertion/Removal Detection with Adjustable De-bounce Timings

- Accessory Configuration Detection:

- Stereo 3-pole Headphone

- 4-pole Standard Headset with MIC on Sleeve

- 4-pole OMTP Headset with MIC on Ring2

- Key Press Detection for Up to 4 Keys

- Ultra Low Ground FET  $R_{ON}$  of 60 m $\Omega$

- Power Off Noise Removal

- Isolation of MICBIAS From Audio Jack to Remove Click/Pop Noise

- Integrated Codec Sense Line

- Manual I<sup>2</sup>C Control

- FM Transmission Capability

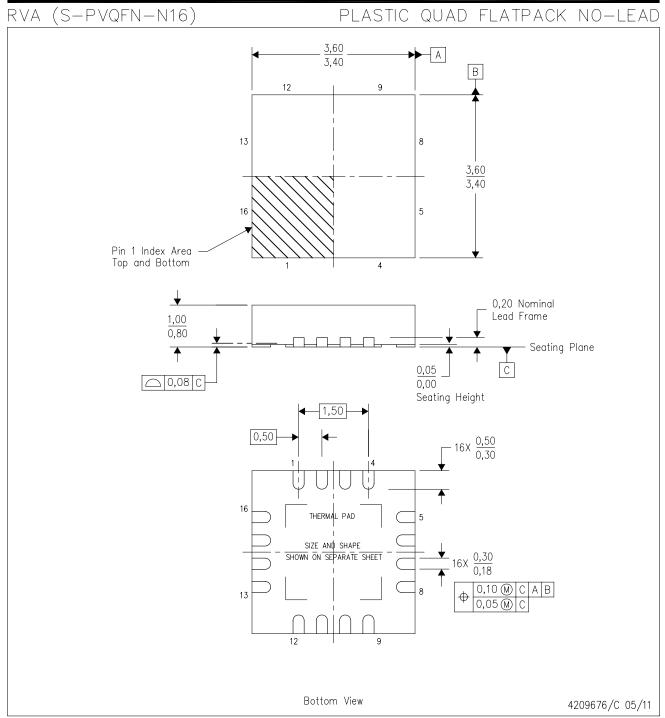

- **Dual Small Package Options**

- 16 Pin DSBGA

- 16 Pin QFN

#### Applications

- Mobile Phones

- **Tablets**

- Notebooks and Ultrabooks

- Anywhere a 3.5 mm Audio Jack is Used

#### 3 Description

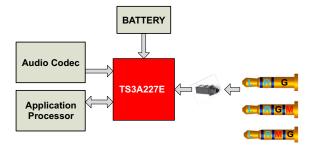

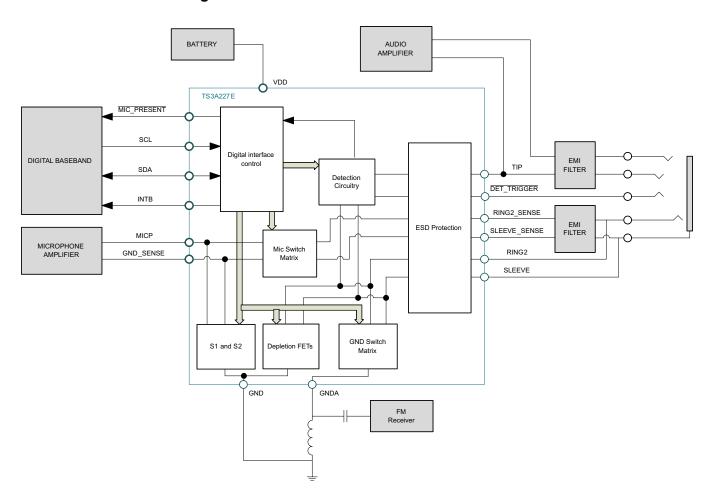

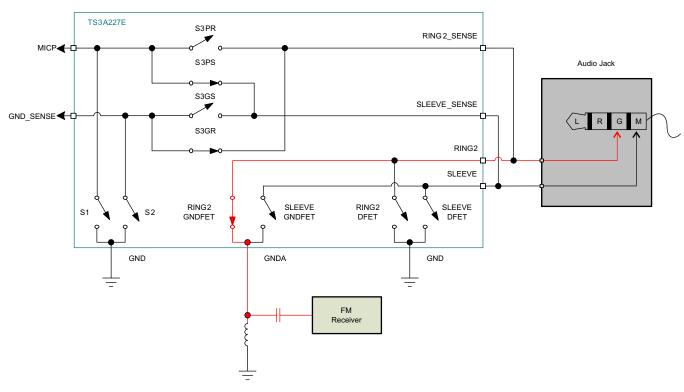

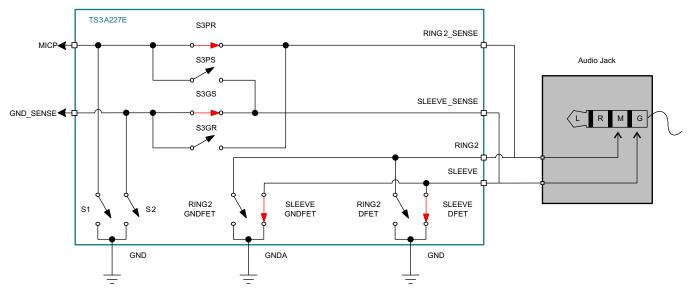

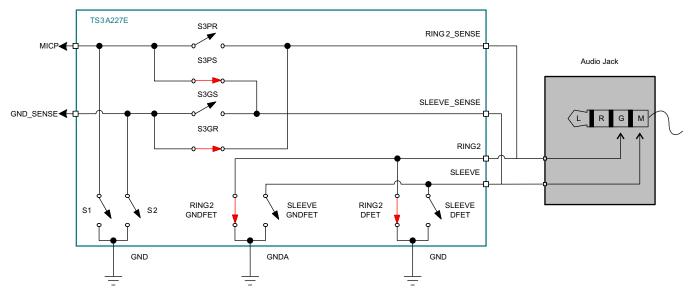

The TS3A227E is an autonomous audio accessory detection and configuration switch that detects 3-pole or 4-pole audio accessories and configures internal switches to route the signals accordingly.

The internal ground FETS of the TS3A227E have an ultra-low  $R_{\text{ON}}$  of 60 m $\Omega$  to minimize crosstalk impact. The ground FETs are also designed to pass FM signals, making it possible to use the ground line of the accessory as an FM antenna in mobile audio applications.

Internal isolation switches allow the TS3A227E to remove the click/pop noise that can be generated during and insertion or removal of an audio accessory. In addition depletion FETs prevent a floating ground while the device is unpowered, removing the humming noise present when leaving accessories plugged into an unpowered system.

A low-power sleep mode is provided which shuts down internal circuitry to achieve very low quiescent current draw when no headset is inserted.

The TS3A227E features integrated key press detection for detecting up to 4 keys with press and release support.

Manual I2C control allows the TS3A227E to adapt to application needs by providing control over debounce settings and switch states.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| T024227F    | QFN (16)   | 3.50 mm × 3.50 mm |

| TS3A227E    | DSBGA (16) | 1.79 mm × 1.79 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

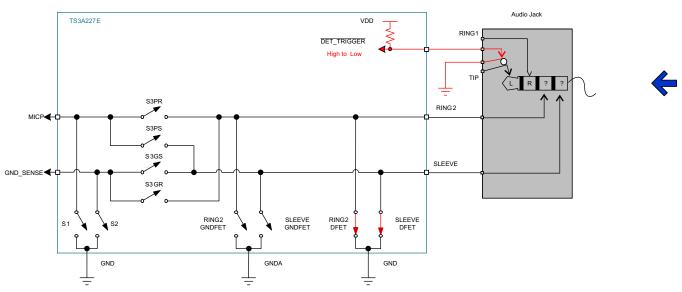

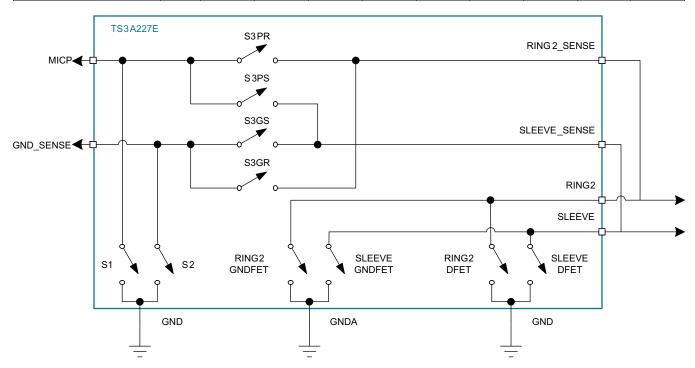

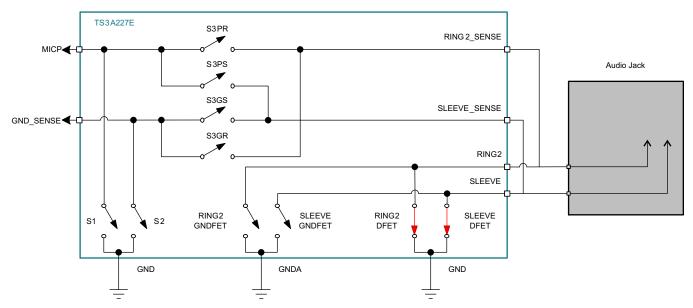

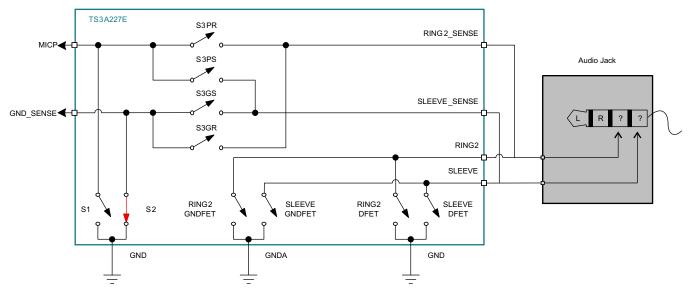

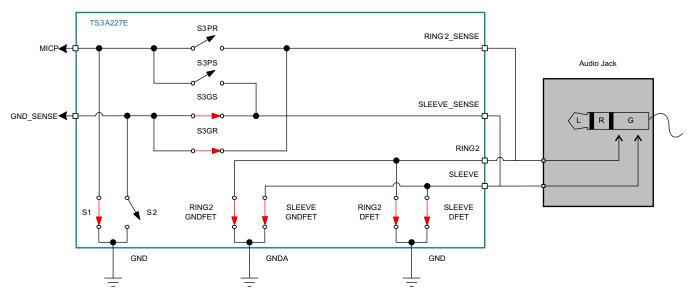

# Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                            |    | 9.2 Functional Block Diagram         | 18 |

|---|-------------------------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                                        |    | 9.3 Feature Description              | 19 |

| 3 | Description 1                                         |    | 9.4 Device Functional Modes          | 20 |

| 4 | Simplified Schematic 1                                |    | 9.5 Register Maps                    | 24 |

| 5 | Revision History                                      |    | 9.6 Register Field Descriptions      | 24 |

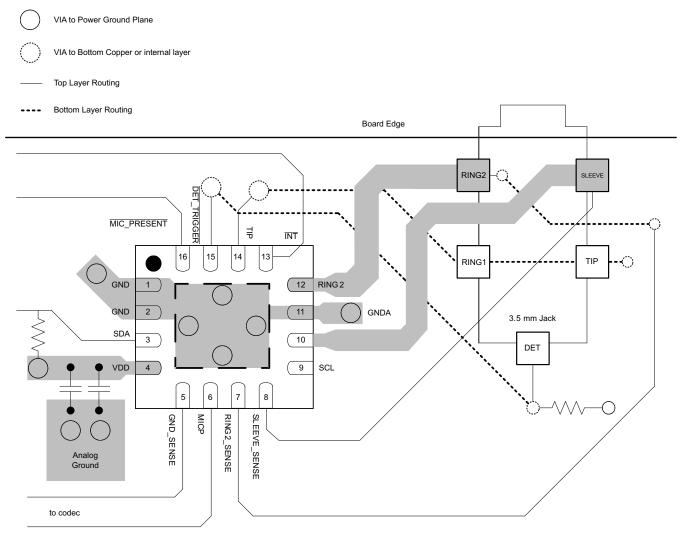

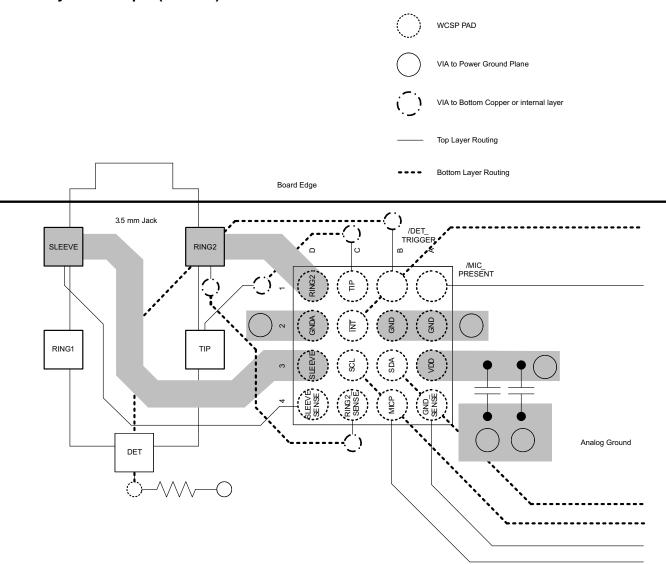

| 6 | Pin Configuration and Functions                       | 10 | Application and Implementation       | 33 |

| - | _                                                     |    | 10.1 Application Information         | 33 |

| 7 | Specifications                                        |    | 10.2 Typical Application             | 33 |

|   | 7.1 Absolute Maximum Ratings                          | 11 | Power Supply Recommendations         | 47 |

|   | 7.2 ESD Ratings                                       | 12 | Layout                               |    |

|   | 7.3 Recommended Operating Conditions                  |    | 12.1 Layout Guidelines               |    |

|   | 7.4 Thermal Information                               |    | 12.2 Layout Example (QFN)            |    |

|   | 7.5 Electrical Characteristics                        |    | 12.3 Layout Example (DSBGA)          |    |

|   | 7.6 I <sup>2</sup> C Interface Timing Characteristics | 13 | Device and Documentation Support     |    |

|   | 7.7 Timing Diagrams                                   | .0 | 13.1 Trademarks                      |    |

| _ | 7.8 Typical Characteristics                           |    | 13.2 Electrostatic Discharge Caution |    |

| 8 | Parameter Measurement Information 12                  |    | 13.3 Glossary                        |    |

| 9 | Detailed Description 17                               | 14 |                                      | 50 |

|   | 9.1 Overview 17                                       | 14 | Information                          | 50 |

|   |                                                       |    |                                      |    |

# 5 Revision History

| Changes from Revision A (December 2014) to Revision B | Page |

|-------------------------------------------------------|------|

| Added DSBGA package to the Thermal Information table  | 5    |

| Updated SWITCH RESISTANCE for the DSBGA package.      | 6    |

| Changes from Original (July 2014) to Revision A       | Page |

| Initial release of full version document              | 1    |

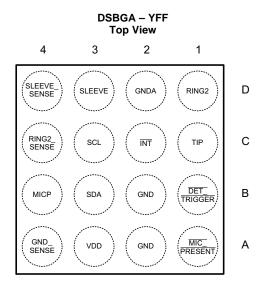

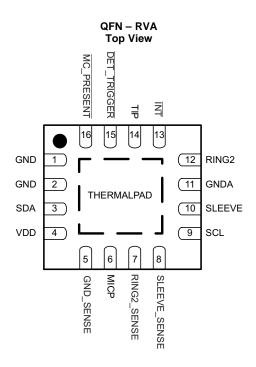

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PII          | N            |        |      |                                                                                                                                                                                                                     |  |  |  |

|--------------|--------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME         | IAME RVA YFF |        | TYPE | DESCRIPTION                                                                                                                                                                                                         |  |  |  |

| DET_TRIGGER  | 15           | B1     | I/O  | A falling edge from high to low on this pin triggers accessory detection. This pin can be connected the headset jack to allow automatic pull-down to ground after headset insertion to initialize detection.        |  |  |  |

| GND          | 1, 2         | A2, B2 | GND  | Primary ground connection for the TS3A227E. Must be connected to system ground.                                                                                                                                     |  |  |  |

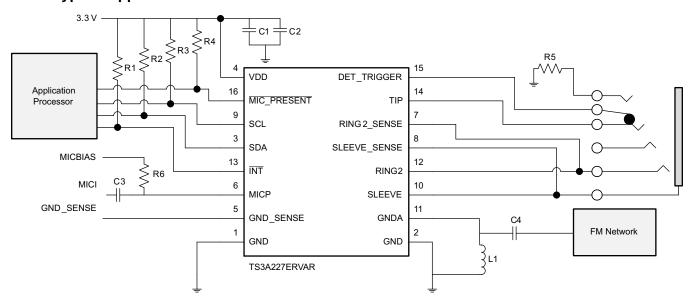

| GNDA         | 11           | D2     | I/O  | Ground connection for the internal ground FETs of the TS3A227E. If FM is being supported connect this pin to the FM matching network. If FM is not being support connect this pin to system ground.                 |  |  |  |

| GND_SENSE    | 5            | A4     | I/O  | Ground sense line for the codec.                                                                                                                                                                                    |  |  |  |

| ĪNT          | 13           | C2     | GND  | Open drain interrupt output from the TS3A227E to notify the host that an event has occurred. If I <sup>2</sup> C is not used this pin must be grounded.                                                             |  |  |  |

| MIC_PRESENT  | 16           | A1     | I/O  | Open drain output to indicate to the host that a headset with a microphone is inserted                                                                                                                              |  |  |  |

| MICP         | 6            | B4     | I/O  | Microphone signal connection to the codec. Microphone bias is applied to this pin.                                                                                                                                  |  |  |  |

| RING2        | 12           | D1     | 0    | Headset current return path if RING2 is ground for the headset. Connect to 3.5 mm jack RING2 connection with low DC resistance trace.                                                                               |  |  |  |

| RING2_SENSE  | 7            | C4     | GND  | Connected to the RING2 pin of the 3.5 mm jack. If RING2 pin on plug in is MIC signal, this is connected to MICP. If not, this is connected to GND_SENSE and becomes the ground sensing feedback for the accessory   |  |  |  |

| SCL          | 9            | СЗ     | I    | Clock from I <sup>2</sup> C bus. This can be connected to VDD if I2C is not used.                                                                                                                                   |  |  |  |

| SDA          | 3            | В3     | I/O  | Bidirectional data from/to I <sup>2</sup> C bus. This can be connected to VDD if I <sup>2</sup> C is not used.                                                                                                      |  |  |  |

| SLEEVE       | 10           | D3     | 0    | Headset current return path if SLEEVE is GND for headset. Connect to 3.5 mm jack SLEEVE connection with low DC resistance trace.                                                                                    |  |  |  |

| SLEEVE_SENSE | 8            | D4     | GND  | Connected to the SLEEVE pin of the 3.5 mm jack. If SLEEVE pin on plug in is MIC signal, this is connected to MICP. If not, this is connected to GND_SENSE and becomes the ground sensing feedback for the accessory |  |  |  |

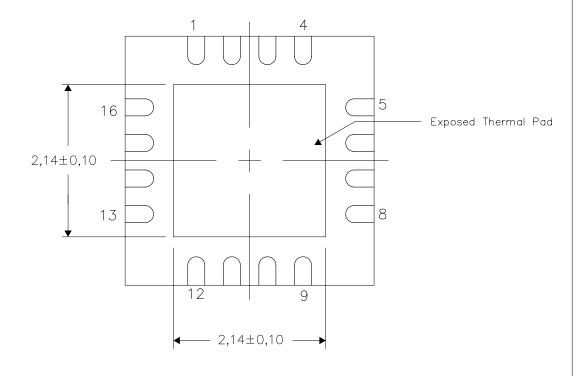

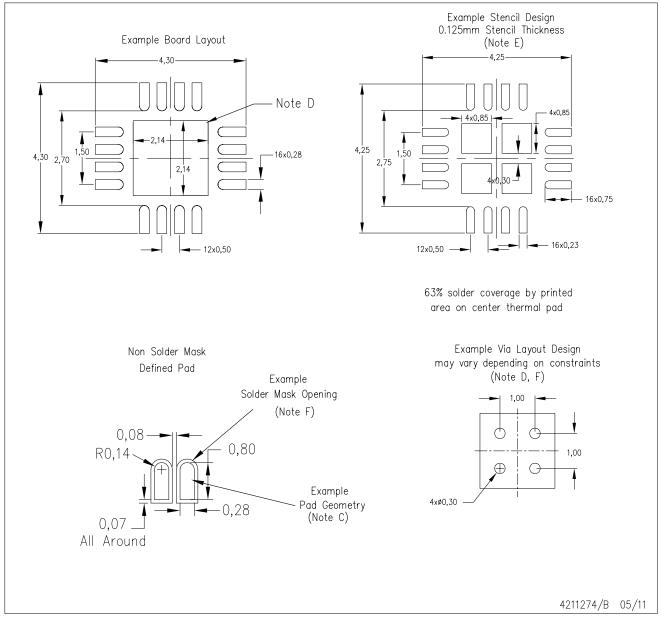

| THERMAL PAD  |              |        | GND  | The THERMAL PAD of the RVA – QFN package must be connected to any internal PCB ground plane using multiple vias for best thermal performance.                                                                       |  |  |  |

| TIP          | 14           | C1     | I/O  | Connect to the TIP pin of the 3.5 mm jack.                                                                                                                                                                          |  |  |  |

| VDD          | 4            | А3     | PWR  | Power input to the TS3A227E. External de-coupling capacitors are required on this pin.                                                                                                                              |  |  |  |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range referenced with respect to GND (unless otherwise noted)(1)

|                  |                                                                 | MIN  | MAX                                                                                                                                                                    | UNIT |

|------------------|-----------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Input Voltage    | VDD                                                             | -0.3 | 5                                                                                                                                                                      | V    |

|                  | SDA, SCL, INT, MIC_PRESENT                                      | -0.3 | V <sub>DD</sub> + 0.5                                                                                                                                                  | V    |

|                  | TIP                                                             | -3.3 | V <sub>DD</sub> + 0.5                                                                                                                                                  | V    |

|                  | DET_TRIGGER                                                     | -2.2 | V <sub>DD</sub> + 0.5                                                                                                                                                  | V    |

|                  | GND_SENSE, RING2, SLEEVE, RING2_SENSE, SLEEVE_SENSE, MICP, GNDA | -0.3 | 5<br>V <sub>DD</sub> + 0.5<br>V <sub>DD</sub> + 0.5                                                                                                                    | V    |

| ON-state switch  | Combined continuous current through R2GNDFET and SLV GNDFET     |      | 500                                                                                                                                                                    | mA   |

| current          | Continuous current through R2DFET and SLV DFET                  |      | 50                                                                                                                                                                     |      |

|                  | Continuous current through S1                                   |      | 20                                                                                                                                                                     |      |

|                  | Continuous current through S2                                   |      | 20                                                                                                                                                                     |      |

|                  | Continuous current through S3PR                                 |      | 50                                                                                                                                                                     |      |

|                  | Continuous current through S3PS                                 |      | 0.3 5 0.3 V <sub>DD</sub> + 0.5 3.3 V <sub>DD</sub> + 0.5 2.2 V <sub>DD</sub> + 0.5 0.3 3.6 <sup>(2)</sup> and V <sub>DD</sub> + 0.5 500 20 20 20 50 50 100 100 -40 85 |      |

|                  | Continuous current through S3GR                                 |      | 100                                                                                                                                                                    |      |

|                  | Continuous current through S3GS                                 |      | 100                                                                                                                                                                    |      |

| Operating ambien | t temperature range                                             | -40  | 85                                                                                                                                                                     | °C   |

| T <sub>stg</sub> | Storage temperature range                                       | -65  | 150                                                                                                                                                                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|             |                         |                                                                                                                               | VALUE | UNIT |

|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), ESD stress voltagenew note #1 to the ESD Ratings table and combined MIN MAX column to VALUE (1) (2)   | ±2000 | V    |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), ESD stress voltage (1) (3)                                                                        | ±500  | V    |

|             |                         | Contact discharge model (IEC) ESD stress voltage on TIP, DET_TRIGGER, RING2_SENSE, SLEEVE_SENSE, RING2, SLEEVE <sup>(1)</sup> | ±8000 | V    |

<sup>(1)</sup> Electrostatic Discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device

(2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> This rating is exclusive and the voltage on the pins must not exceed either 3.6 and V<sub>DD</sub>. E.g. if V<sub>DD</sub> = 4.5 V the voltage on the pin must not exceed 3.6 V and if V<sub>DD</sub> is = 2.5 V the voltage on the pin must not exceed 3.0 V.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                              |                                                           | MIN                    | MAX                        | UNIT |

|-----------------|------------------------------|-----------------------------------------------------------|------------------------|----------------------------|------|

| VDD             | Power supply voltage range   |                                                           | 2.5                    | 4.5                        | V    |

| \/              | Digital input valtage range  | SDA, SCL                                                  | 0                      | $V_{DD}$                   | V    |

| V <sub>I</sub>  | Digital input voltage range  | DET_TRIGGER                                               | 2.5 4.5                | V                          |      |

| V <sub>IO</sub> | Input/output voltage range   | RING2_SENSE, SLEEVE_SENSE, RING2, SLEEVE, GND_SENSE, MICP | 0                      | 3.3 <sup>(1)</sup> and VDD | V    |

| .0              |                              | TIP                                                       | -3                     | $V_{DD}$                   |      |

| Vo              | Output voltage range         | INT, MIC_PRESENT                                          | 0                      | $V_{DD}$                   | V    |

| \/              | Input logic high             | SDA, SCL                                                  | 1.2                    | $V_{DD}$                   | V    |

| $V_{IH}$        | Input logic high             | DET_TRIGGER                                               | 0.65 × V <sub>DD</sub> | $V_{DD}$                   | V    |

|                 | lament lamin lavo            | SDA, SCL                                                  | 0                      | 0.4                        | V    |

| $V_{IL}$        | Input logic low              | DET_TRIGGER                                               | 0                      | $0.4 \times V_{DD}$        | V    |

| T <sub>A</sub>  | Operating ambient temperatur | re                                                        | -40                    | 85                         | °C   |

<sup>(1)</sup> This rating is exclusive and the voltage on the pins must not exceed either 3.3 and  $V_{DD}$ . E.g. if  $V_{DD} = 4.5 \text{ V}$  the voltage on the pin must not exceed 3.3 V and if  $V_{DD}$  is = 2.5 V the voltage on the pin must not exceed 2.5 V.

#### 7.4 Thermal Information

|                       |                                              | TS3A227E | TS3A227E |        |

|-----------------------|----------------------------------------------|----------|----------|--------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE      | YFF      | UNIT   |

|                       |                                              | 16 PINS  | 16 PINS  |        |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 45.9     | 77.9     |        |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 52.6     | 0.6      |        |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 21.2     | 12.5     | °C/W   |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.9      | 2.3      | - C/VV |

| ΨЈВ                   | Junction-to-board characterization parameter | 21.2     | 12.5     |        |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.3      | -        |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics

Unless otherwise noted the specification applies over the VDD and ambient operating temperature range

|                       | PARAMETER                                                  | TEST CONDITIONS                                                                                                                      | MIN   | TYP | MAX | UNIT |

|-----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| SUPPLY VO             | DLTAGE                                                     |                                                                                                                                      |       |     |     |      |

| VDD                   | Supply voltage                                             |                                                                                                                                      | 2.5   | 3.3 | 4.5 | V    |

|                       |                                                            | No accessory inserted. I <sup>2</sup> C bus inactive <sup>(1)</sup><br>V <sub>DD</sub> = 2.5 V to 4.5 V                              |       | 0.5 | 10  | μΑ   |

|                       |                                                            | Manual switch control = '1' , I <sup>2</sup> C bus inactive, (1) V <sub>DD</sub> = 2.5 V to 4.5 V, Depletion FETs on                 |       | 7   | 15  | μΑ   |

|                       |                                                            | Manual switch control = '1' , $I^2C$ bus inactive, $V_{DD} = 2.5 \text{ V}$ to $4.5 \text{ V}$ Depletion FETs off                    |       | 20  | 40  | μA   |

| I <sub>DD</sub>       | Quiescent current                                          | 3-pole accessory inserted.  I <sup>2</sup> C bus inactive <sup>(1)</sup> , FM Support = '0'  V <sub>DD</sub> = 2.5 V to 4.5 V        |       | 11  | 20  | μΑ   |

|                       |                                                            | 3-pole accessory inserted. I <sup>2</sup> C bus inactive, $^{(1)}$ FM Support = '1' $V_{DD} = 2.5$ V to 4.5 V                        |       | 25  | 45  | μΑ   |

|                       |                                                            | 4-pole Accessory inserted.<br>I <sup>2</sup> C bus inactive, <sup>(1)</sup> V <sub>DD</sub> = 2.5 V to 4.5 V                         |       | 25  | 40  | μΑ   |

|                       |                                                            | 4-pole Accessory inserted.<br>KP detection enabled<br>I <sup>2</sup> C bus inactive, <sup>(1)</sup> V <sub>DD</sub> = 2.5 V to 4.5 V |       | 30  | 45  | μА   |

| I <sub>DD_1.8</sub>   | Quiescent current addition from using a 1.8 V I2C bus. (2) | No accessory inserted.<br>I <sup>2</sup> C bus inactive at 1.8 V, <sup>(3)</sup><br>V <sub>DD</sub> = 2.5 V to 4.5 V                 |       | 1   | 8   | μΑ   |

| SWITCH RE             | SISTANCE                                                   |                                                                                                                                      | ·     |     |     |      |

| D                     | RING2 GNDFET on resistance (DSBGA Package)                 | $V_{DD} = 3.3 \text{ V}, V_{GND} = 0 \text{V},$ $I_{GNDA} = 75 \text{ mA}$                                                           |       | 40  | 85  | mΩ   |

| R <sub>R2GNDFT</sub>  | RING2 GNDFET on resistance (QFN Package)                   |                                                                                                                                      |       | 60  | 95  |      |

| Rausaura              | SLEEVE GNDFET on resistance (DSBGA Package)                |                                                                                                                                      |       | 40  | 85  |      |

| R <sub>SLVGNDFT</sub> | SLEEVE GNDFET on resistance (QFN Package)                  |                                                                                                                                      |       | 60  | 95  |      |

| R <sub>S3PS</sub>     | S3PS on resistance                                         | $V_{DD} = 3.3 \text{ V},$                                                                                                            | ·     | 3   | 6.5 | 0    |

| R <sub>S3PR</sub>     | S3PR on resistance                                         | $V_{SLEEVE\_SENSE/RING2\_SENSE} = 0 \text{ V to } 2.7 \text{ V},$ $I_{MICP} = \pm 10 \text{ mA}$                                     |       | 3   | 6.5 | Ω    |

| R <sub>S3GS</sub>     | S3GS on resistance                                         | V <sub>DD</sub> = 3.3 V,                                                                                                             |       | 0.5 | 1   |      |

| R <sub>S3GR</sub>     | S3GR on resistance                                         | V <sub>SLEEVE_SENSE/RING2_SENSE</sub> = 0 V to 2.7 V,<br>I <sub>GND_SENSE</sub> = ±75 mA                                             |       | 0.5 | 1   | Ω    |

| R <sub>S1</sub>       | Switch 1 on resistance                                     | GNG_GENGE                                                                                                                            |       | 15  | 30  |      |

| R <sub>S2</sub>       | Switch 2 on resistance                                     |                                                                                                                                      |       | 15  | 30  | Ω    |

| R <sub>R2DFET</sub>   | RING2 depletion FET on resistance                          | $V_{DD} = 3.3 \text{ V}, I_{GND} = 10 \text{ mA}$                                                                                    |       | 75  | 150 |      |

| R <sub>SLVDFET</sub>  | SLEEVE depletion FET on resistance                         |                                                                                                                                      | -     | 75  | 150 | Ω    |

|                       | AKAGE CURRENT                                              |                                                                                                                                      |       |     |     |      |

|                       | RING2 pin off leakage                                      |                                                                                                                                      |       |     | 1   |      |

|                       | SLEEVE pin off leakage                                     |                                                                                                                                      |       |     | 1   |      |

|                       | RING2_SENSE pin off leakage                                | V = 0.V to 2.2.V V = 2.2.V                                                                                                           |       |     | 1   | ^    |

| OFF                   | SLEEVE_SENSE pin off leakage                               | $V_{IN} = 0 \text{ V to } 3.3 \text{ V}, V_{DD} = 3.3 \text{ V}$                                                                     |       |     | 1   | μA   |

|                       | MICP pin off leakage                                       |                                                                                                                                      | · · · |     | 1   |      |

|                       | GND_SENSE pin off leakage                                  |                                                                                                                                      |       |     | 1   |      |

| I <sub>ON</sub>       | S2PS, S3PR, S3GS, S3GR on leakage                          | V <sub>SLEEVE/RING2</sub> = 0V, V <sub>DD</sub> = 3.3 V                                                                              |       |     | 1   | μA   |

The  $I^2C$  bus is inactive if both the SDA and SCL lines are tied to  $V_{DD}$ . If the  $I^2C$  bus is operating at 1.8 V the  $I_{DD\_1.8}$  current number will be in addition to the other current consumption numbers specified. The  $I^2C$  bus is inactive if both the SDA and SCL lines are tied to 1.8 V.

# **Electrical Characteristics (continued)**

Unless otherwise noted the specification applies over the VDD and ambient operating temperature range.

|                    | PARAMETER                                                          | TEST CONDITIONS                                                                                                                                                                                                                                                                     | MIN                    | TYP | MAX                   | UNIT |

|--------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------------|------|

| SWITCH 1           | TIMING                                                             |                                                                                                                                                                                                                                                                                     | ·                      |     | -                     |      |

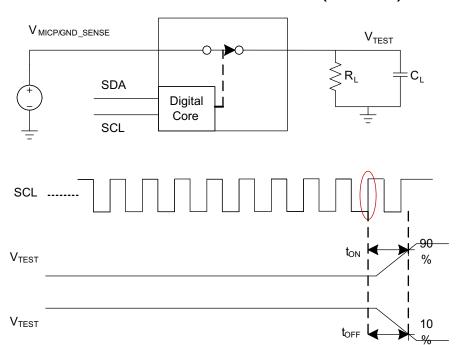

|                    | Turn off time for S3PS, S3PR, S3GS, S3GR                           | $\begin{split} &V_{DD} = 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V}, \\ &R_L = 300  \Omega,  C_L = 50  \text{pF} \\ &V_{SLEEVE\_SENSE,RING2\_SENSE} = 2.5  \text{V}  (V_{DD} = 2.5  \text{V}), \\ &3.3  \text{V}  (V_{DD} = 3.3  \text{V},  V_{DD} = 4.5  \text{V}) \end{split}$ |                        |     | 5                     | μs   |

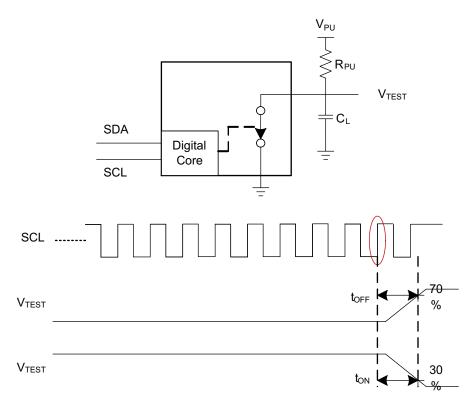

| t <sub>OFF</sub>   | Turn off time for S1, S2, RING2 GNDFET, SLEEVE GNDFET              | $\begin{split} V_{DD} &= 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V} \\ R_{PU} &= 1500  \Omega,  C_L = 50 \text{ pF} \\ V_{PU} &= 2.5 \text{ V}  (V_{DD} = 2.5 \text{ V}), \\ 3.3 \text{ V}  (V_{DD} = 3.3 \text{ V},  V_{DD} = 4.5 \text{ V}) \end{split}$                       |                        |     | 5                     | μs   |

|                    | Turn off time for RING2 DFET and SLEEVE DFET                       | $\begin{split} V_{DD} &= 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V} \\ R_{PU} &= 1500  \Omega,  C_L = 50 \text{ pF} \\ V_{PU} &= 2.5 \text{ V}  (V_{DD} = 2.5 \text{ V}), \\ 3.3 \text{ V}  (V_{DD} = 3.3 \text{ V},  V_{DD} = 4.5 \text{ V}) \end{split}$                       |                        |     | 500                   | μs   |

| t <sub>ON</sub>    | Turn on time for S3PS, S3PR, S3GS, S3GR                            | $\begin{split} &V_{DD} = 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V} \\ &R_L = 300  \Omega,  C_L = 50 \text{ pF} \\ &V_{SLEEVE\_SENSE/RING2\_SENSE} = 2.5 \text{ V}  (V_{DD} = 2.5 \text{ V}), \\ &3.3 \text{ V}  (V_{DD} = 3.3 \text{ V},  V_{DD} = 4.5 \text{ V}) \end{split}$  |                        |     | 1                     | μs   |

|                    | Turn on time for S1, S2, RING2 GNDFET, SLEEVE GNDFET               | $\begin{split} V_{DD} &= 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V} \\ R_{PU} &= 1500  \Omega,  C_L = 50 \text{ pF} \\ V_{PU} &= 2.5 \text{ V}  (V_{DD} = 2.5 \text{ V}), \\ 3.3 \text{ V}  (V_{DD} = 3.3 \text{ V},  V_{DD} = 4.5 \text{ V}) \end{split}$                       |                        |     | 35                    | μs   |

|                    | Turn on time for RING2 DFET and SLEEVE DFET                        | $\begin{split} V_{DD} &= 2.5 \text{ V},  3.3 \text{ V},  4.5 \text{ V} \\ R_{PU} &= 1500  \Omega,  C_L = 50 \text{ pF} \\ V_{PU} &= 2.5 \text{ V}  (V_{DD} = 2.5 \text{ V}), \\ 3.3 \text{ V}  (V_{DD} = 3.3 \text{ V},  V_{DD} = 4.5 \text{ V}) \end{split}$                       |                        |     | 1                     | μs   |

| DIGITAL I          | 1/O                                                                |                                                                                                                                                                                                                                                                                     |                        |     |                       |      |

| $V_{OL}$           | MIC_PRESENT low level output voltage  INT low level output voltage | V <sub>DD</sub> = 3.3 V, I <sub>OL</sub> = 10 mA                                                                                                                                                                                                                                    | 0                      |     | 0.4                   | V    |

|                    | SDA low level output voltage                                       | $V_{DD} = 3.3 \text{ V}, I_{OLMAX} = 3 \text{ mA}$                                                                                                                                                                                                                                  | 0                      |     | 0.4                   |      |

|                    |                                                                    | SDA, SCL                                                                                                                                                                                                                                                                            | 1.2                    | ·   | $V_{DD}$              |      |

| V <sub>IH</sub>    | Input logic high                                                   | DET_TRIGGER                                                                                                                                                                                                                                                                         | V <sub>DD</sub> x 0.65 |     | $V_{DD}$              | V    |

| $V_{IL}$           | Input logic low                                                    | SDA, SCL                                                                                                                                                                                                                                                                            | 0                      |     | 0.4                   |      |

| * IL               | input logic low                                                    | DET_TRIGGER                                                                                                                                                                                                                                                                         | 0                      |     | V <sub>DD</sub> x 0.4 |      |

| R <sub>PU/DT</sub> | Internal DET_TRIGGER pull-up resistance                            | $V_{DD} = 3.3 \text{ V}, I_{/DET\_TRIGGER} = 1  \mu\text{A}$                                                                                                                                                                                                                        | 0.5                    | 1   | 1.85                  | МΩ   |

#### **Electrical Characteristics (continued)**

Unless otherwise noted the specification applies over the VDD and ambient operating temperature range.

|                       | PARAMETER                                                 | TEST CONDITIONS                                                                                                                | MIN | TYP     | MAX | UNIT |

|-----------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| DYNAMIC               | CHARACTERISTICS                                           |                                                                                                                                |     |         |     |      |

| PSR <sub>217</sub>    |                                                           | $V_{DD}$ = 3.3 V ± 200 mV <sub>PP</sub> , f = 217 Hz, R <sub>L</sub> at RING2= 50 $\Omega$                                     | -95 | -120    |     |      |

| PSR <sub>1k</sub>     | Power supply rejection                                    | $V_{DD}$ = 3.3 V ± 200 mV <sub>PP</sub> , f = 1 kHz, R <sub>L</sub> at RING2= 50 $\Omega$                                      | -85 | -110    |     | dB   |

| PSR <sub>20k</sub>    |                                                           | $V_{DD}$ = 3.3 V ± 200 mV <sub>PP</sub> , f = 20 kHz, R <sub>L</sub> at RING2= 50 $\Omega$                                     | -70 | -90     |     |      |

| ISO <sub>S3</sub>     | SLEEVE_SENSE or RING2_SENSE to MICP Isolation             | $V_{IN} = 200 \text{ mV}_{PP}, f = 20 \text{ Hz} - 20 \text{ kHz}, R_L = 50 \Omega$                                            |     | -90     |     | dB   |

| SEP <sub>S3</sub>     | SLEEVE_SENSE to RING2_SENSE<br>Separation                 | $V_{IN} = 200 \text{ mV}_{PP}, f = 20 \text{ Hz} - 20 \text{ kHz}, R_L = 50 \Omega$                                            |     | -75     |     | dB   |

| BW                    | Bandwidth through GNDFETs                                 | $V_{IN} = 60 \text{ mV}_{PP}, I_{BIAS} = 10 \text{ mA}$                                                                        | 120 | 150     |     | MHz  |

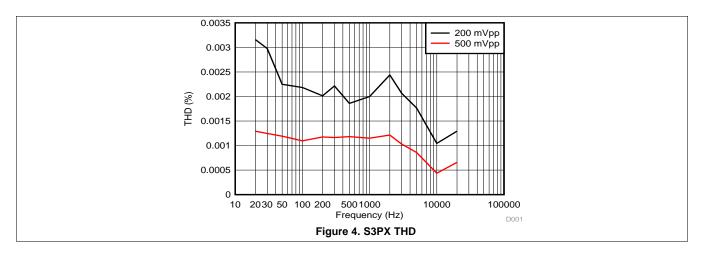

| THD <sub>200</sub>    | MICP to RING2_SENSE or                                    | $V_{IN} = 1.5 \text{ V} + 200 \text{ mV}_{PP}, f = 20 \text{ Hz} - 20 \text{ kHz}, \\ R_S = 600 \Omega, R_L = 600 \Omega$      |     | 0.003 % |     |      |

| THD <sub>500</sub>    | SLEEVE_SENSE total harmonic distortion                    | $V_{IN}$ = 1.5 V + 500 mV <sub>PP</sub> , f = 20 Hz – 20 kHz,<br>R <sub>S</sub> = 600 $\Omega$ , R <sub>L</sub> = 600 $\Omega$ |     | 0.002%  |     |      |

| SNR                   | MICP to RING2_SENSE or SLEEVE_SENSE signal to noise ratio | $V_{IN} = 1 \ V_{RMS}, f = 20 \ Hz - 20 \ kHz, \\ R_S = 600 \ \Omega, \ R_L = 600 \ \Omega$                                    | -90 | -110    |     | dB   |

| t <sub>DET</sub>      | Detection sequence duration                               | Time between DET_TRIGGER transition from high to low and INT transition from high to low. Default 90 ms insertion debounce.    |     | 175     | 210 | ms   |

| T <sub>power-up</sub> | Power up time Power-up time                               | Time from $V_{DD} > 2.5 \text{ V}$ till $I^2C$ communication is ready                                                          |     | 20      | 25  | ms   |

| t <sub>REMOVAL</sub>  | Removal wait period                                       | Time between DET_TRIGGER transition from low to high and RING2/SLEEVE DFETs turning on                                         |     | 50      | 65  | ms   |

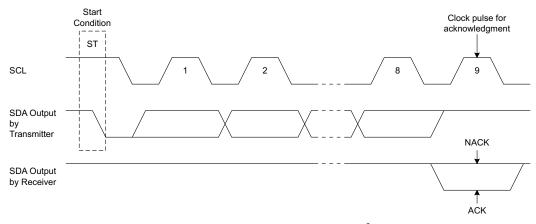

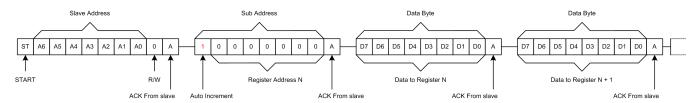

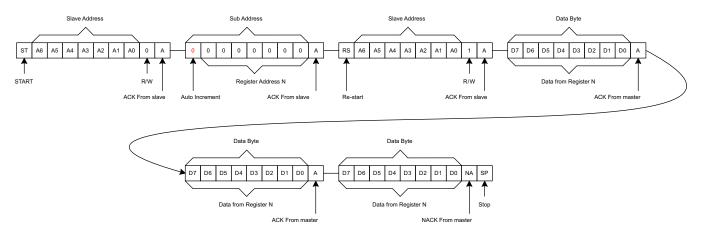

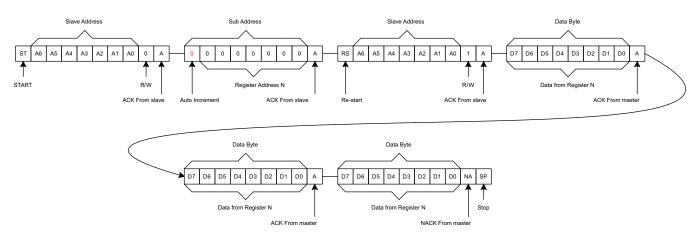

# 7.6 I<sup>2</sup>C Interface Timing Characteristics

Unless otherwise noted the specification applies over the VDD and ambient operating temperature range

|                       | PARAMETER                                                                  | STANDARD<br>I <sup>2</sup> C BU |      | FAST MODE I <sup>2</sup> C<br>BUS |     | UNIT |

|-----------------------|----------------------------------------------------------------------------|---------------------------------|------|-----------------------------------|-----|------|

|                       |                                                                            | MIN                             | MAX  | MIN                               | MAX |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                                           | 0                               | 100  | 0                                 | 400 | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                                           | 4                               |      | 0.6                               |     | μs   |

| t <sub>scl</sub>      | I2C clock low time                                                         | 4.7                             |      | 1.3                               |     | μs   |

| t <sub>sp</sub>       | I2C spike time                                                             |                                 | 50   |                                   | 50  | ns   |

| t <sub>sds</sub>      | I2C serial data setup time                                                 | 250                             |      | 100                               |     | ns   |

| t <sub>sdh</sub>      | I2C serial data hold time                                                  | 0                               |      | 0                                 |     | ns   |

| t <sub>icr</sub>      | I2C input rise time                                                        |                                 | 1000 | 21                                | 300 | ns   |

| t <sub>icf</sub>      | I2C input fall time                                                        |                                 | 300  | 21                                | 300 | ns   |

| t <sub>ocf</sub>      | I2C output fall time; 10 pF to 400 pF bus                                  |                                 | 300  | 20 + 0.1<br>Cb                    | 300 | μs   |

| t <sub>buf</sub>      | I2C bus free time between Stop and Start                                   | 4.7                             |      | 1.3                               |     | μs   |

| t <sub>sts</sub>      | I2C Start or repeater Start condition setup time                           | 4.7                             |      | 0.6                               |     | μs   |

| t <sub>sth</sub>      | I2C Start or repeater Start condition hold time                            | 4                               |      | 0.6                               |     | μs   |

| t <sub>sps</sub>      | I2C Stop condition setup time                                              | 4                               |      | 0.6                               |     | μs   |

| t <sub>vd(data)</sub> | Valid data time; SCL low to SDA output valid                               |                                 | 3.45 | 0.3                               | 0.9 | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition; ACK signal from SCL low to SDA (out) low |                                 | 3.45 | 0.3                               | 0.9 | μs   |

| C <sub>b</sub>        | I2C bus capacitive loading                                                 | 0                               | 400  | 0                                 | 400 | pF   |

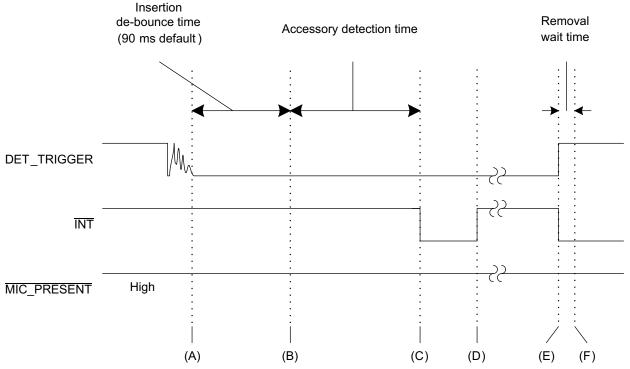

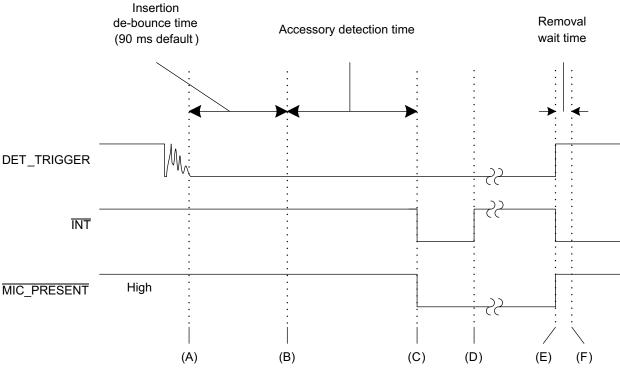

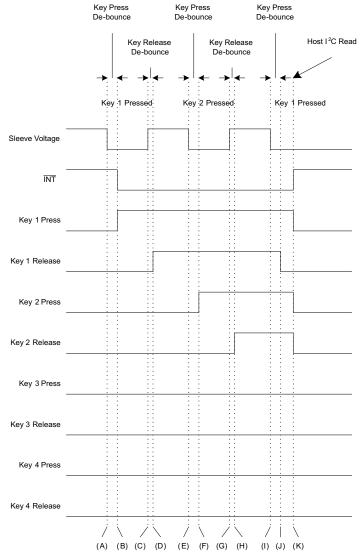

#### 7.7 Timing Diagrams

- A. (This is the point that DET\_TRIGGER has stopped glitching and is fully low. The de-bounce time of 90 ms starts from the point that the pin is constantly below the V<sub>IL</sub> level. Any time the DET\_TRIGGER pin cross the V<sub>IH</sub> level the debounce timer will restart.

- B. Point B is the end of the insertion de-bounce time and the beginning of accessory detection.

- C. Detection has completed at this point. The switches will be routed before the  $\overline{\text{INT}}$  pin is pulled low.

- D. INT is cleared after the host reads the interrupt register.

- E. The headset is removed here. The switch states will change immediately and  $\overline{\text{INT}}$  will be pulled low.

- F. After a 50 ms removal de-bounce timer the TS3A227E will go back into sleep mode if manual switch control is not enabled

Figure 1. 3-Pole Accessory

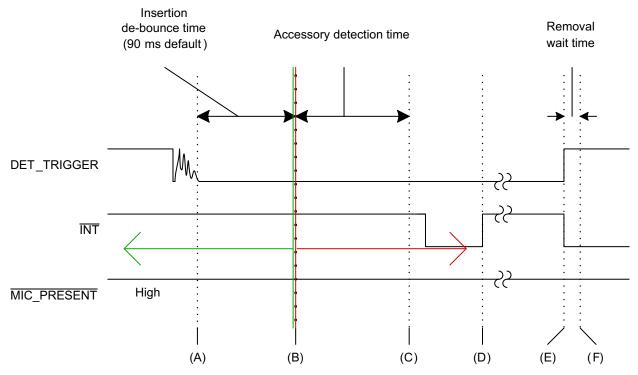

#### **Timing Diagrams (continued)**

- A. This is the point that DET\_TRIGGER has stopped glitching and is fully low. The de-bounce time of 90 ms starts from the point that the pin is constantly below the V<sub>IL</sub> level. Any time the DET\_TRIGGER pin cross the VIH level the debounce timer will restart.

- B. Point B is the end of the insertion de-bounce time and the beginning of accessory detection.

- C. Detection has completed at this point. The switches will be routed before the INT and MIC\_PRESENT pins are pulled low.

- D. INT is cleared after the host reads the interrupt register.

- E. The headset is removed here. The switch states will change immediately and  $\overline{\text{INT}}$  will be pulled low. The MIC\_PRESENT pin will be released.

- F. After a 50 ms removal de-bounce timer the TS3A227E will go back into sleep mode if manual switch control is not enabled

Figure 2. 4-Pole Accessory

# **Timing Diagrams (continued)**

#### 7.7.1 Removal

A removal event will interrupt any on-going process in the TS3A227E. The following diagram depicts how the device "jumps" during a removal.

If the removal event occurs during the insertion de-bounce period the TS3A227E will jump to the (A) point of the diagram depicted by the green arrow and line.

Any time after point (B) has been reached and the accessory is removed the device jumps to point (E), which includes key press detection. Under Manual Switch Control the switch states will not change.

Figure 3. Removal Timing During Insertion

# TEXAS INSTRUMENTS

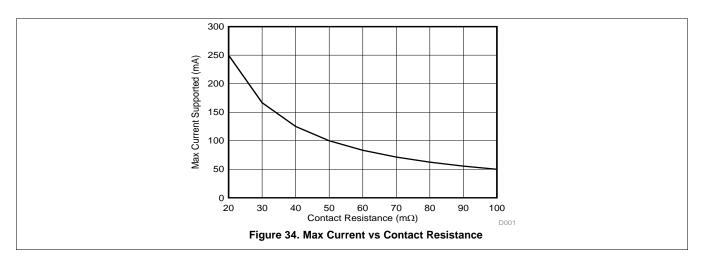

#### 7.8 Typical Characteristics

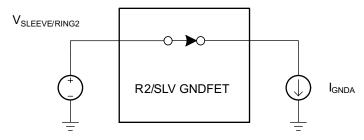

#### 8 Parameter Measurement Information

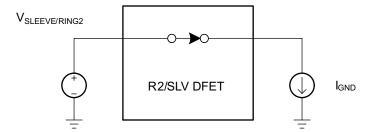

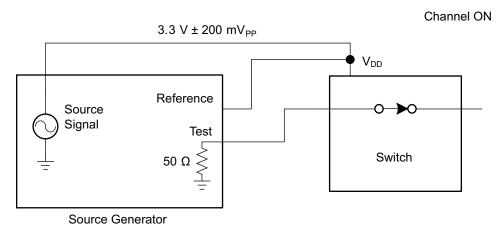

Channel ON  $R_{ON} = V_{SLEEVE/RING2} / I_{GNDA}$

Figure 5. RING2/SLEEVE GNDFET On Resistance Measurement

Channel ON R<sub>ON</sub> = V<sub>SLEEVE/RING2</sub> / I<sub>GND</sub>

Figure 6. RING2/SLEEVE DFET On Resistance Measurement

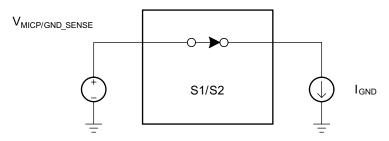

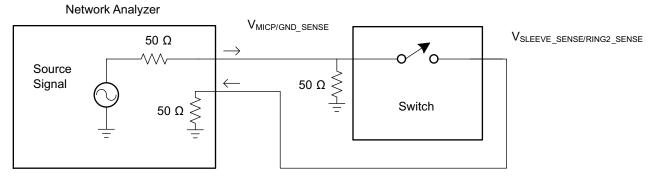

Channel ON  $R_{ON} = V_{MICP/GND\_SENSE} / I_{GND}$

Figure 7. S1/S2 On Resistance Measurement

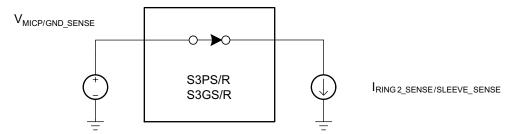

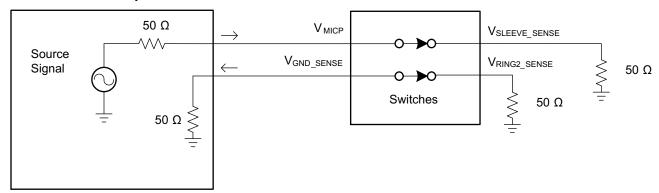

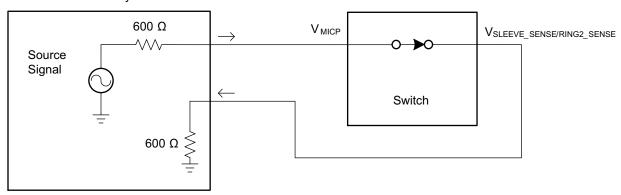

Channel ON  $R_{ON} = V_{MICP/GND\_SENSE} / I_{RING2\_SENSE/SLEEVE\_SENSE}$

Figure 8. S3PS, S3PR, S3GS, S3GR On Resistance Measurement

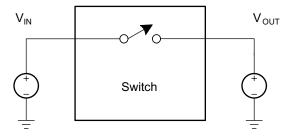

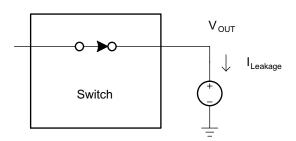

**Channel OFF**

Figure 9. Switch Off Leakage Current

Channel ON

Figure 10. Switch On Leakage Current

Figure 11. Power Supply Rejection Ratio (PSRR)

**Channel Off**

Figure 12. Switch Off Isolation

#### Network Analyzer

Figure 13. Channel Separation

#### Audio Analyzer

Figure 14. Total Harmonic Distortion (THD) and SNR

Figure 15. S3  $t_{OFF}/t_{O}N$

Figure 16. S1, S2, GNDFET and DFET t<sub>ON</sub>/t<sub>OFF</sub>

#### 9 Detailed Description

#### 9.1 Overview

The TS3A227E is an autonomous audio accessory switch with adjustable de-bounce settings, ultra-low RON ground FETs, depletion FETs and manual I<sup>2</sup>C control.

The detection sequence is initiated via the external  $\overline{\text{DET\_TRIGGER}}$  pin or via I2C command. The device incorporates internal de-bounce timings that remove the need for external RC circuits, reducing cost and overall PCB footprint. Additionally all switches of the TS3A227E and the internal de-bounce timings can be controlled through I<sup>2</sup>C.

Before an insertion, TS3A227E isolates the MICBIAS voltage output from the audio jack to remove click/pop noise that can be created during an insertion event. In addition the device also includes depletion FETs to ground the accessory SLEEVE and RING2 pins when VDD is not powered. This removes the humming noise that can be created when plugging an accessory into and unpowered system.

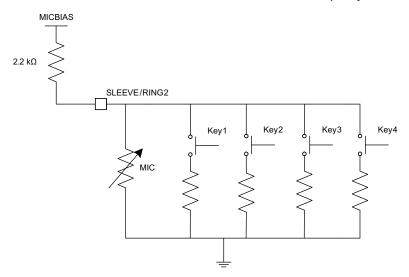

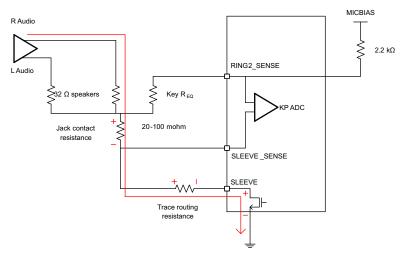

The TS3A227E detects the presence and configuration of the microphone in an attached headset upon insertion. Upon detection of a microphone the TS3A227E automatically connects a system analog microphone pin (MICP) to the appropriate audio jack connection. The device also automatically routes the device GNDA pin to the headset ground. After a 4-pole headset insertion the host can enable the Key Press detection feature of the TS3A227E.

The device also features an ultra-low power sleep mode to conserve battery life when an accessory is not inserted.

For FM transmission the ground FETs of the device can be used as an FM transmission path by placing the FM receiver and matching network on the GNDA pin. The FM support bit must be set to '1' through I<sup>2</sup>C for FM transmission to pass.

# 9.2 Functional Block Diagram

#### 9.3 Feature Description

#### 9.3.1 Accessory Configuration Detection

There are currently two difference configurations for headsets with microphones as shown in Table 1. Many codecs requires that the system designer make a tough decision via a hardware connection which headset they would like to support. This is done by directly connecting the microphone bias and the ground connections to the sleeve and ring2 pins of the audio jack. For the end user this leaves a headset standard as fully unsupported.

PHYSICAL CONNECTOR INTERNAL IMPEDANCE NETWORK PIN NAME **CONFIGURATION** Tip Sleeve Tip Audio Left Ring R G Ring Audio Right **TRS**  $16-2 k\Omega$ Sleeve Ground 16-2 kΩ 3-pole TRS 600-4kΩ Tip Audio Left  $\bigvee\bigvee$ Ring1 Audio Right Ring2 Ground R G Ring1 Tip Ring2 Sleeve Sleeve Microphone Standard  $16-2 k\Omega$ 16-2 kΩ 600-4kΩ Tip Audio Left Ring1 Audio Right Ring2 Microphone 4-pole TRRS R G Sleeve Ground **OMTP** 16-2 kΩ 16-2 kΩ

**Table 1. Two Difference Configurations for Headsets**

The TS3A227E fills this system gap by detecting the presence and location of the microphone and automatically routing the MICBIAS and ground lines to support each headset. This enhances the overall user experience by allowing headsets from all manufacturers.

#### 9.3.2 Optional Manual I<sup>2</sup>C Control

The TS3227E also features optional manual I<sup>2</sup>C control for enhanced system flexibility. This allows the system designer to manually control the switches and de-bounce settings at their discretion enabling the TS3A227E to adapt to unique use cases.

This is an optional feature that does not need to be used for the device to operate autonomously.

#### 9.3.3 Adjustable De-bounce Timings

The TS3A227E features manual control of the insertion de-bounce timer with selectable values. The default insertion de-bounce timer is 90 ms.

This eliminates the need for external RC components which reduces BOM cost, the PCB footprint of the external RC components. Further information on how to select an appropriate de-bounce timer can be found in the application and implementation section.

#### 9.3.4 Key Press Detection

After a headset is inserted, the host can enable Key Press detection through the I<sup>2</sup>C registers. This will configure the TS3A227E to detect up to 4 different keys and report when the key is pressed and released.

#### 9.3.5 Click Pop Noise Reduction

During an accessory insertion and removal event the TS3A227E use special techniques to remove the click/pop noise that can occur with a traditional implementation creating a better user experience.

#### 9.3.6 Power off Noise Removal

In a system that intends to support both headset types, the end user can place the system into sleep mode and leave a headset/speaker plugged into the audio jack. If the audio jack switch is turned off to conserve power in the sleep mode this would typically mean the headset/speaker ground would not be connected because there is no power to turn on the ground FETs. This creates an audible humming noise at the speaker/headset output that can be discomforting to listen to.

By utilizing always on depletion FETs this issue can be removed and the headset/speaker can be connected to ground even with the device unpowered.

#### 9.3.7 Sleep Mode

The TS3A227E will automatically enter a low power sleep when no accessory is inserted and manual switch control is not enabled. After an accessory is inserted the device will wake, run detection, and configure the switches as necessary.

#### 9.3.8 Codec Sense Line

In the complex systems of today, there is an increasing amount of ICs on any given board. The issue this creates is that a codec can be far away from the audio jack and there is a potential difference between the grounding of the codec and the grounding of the headset.

By incorporating a ground sense line into the TS3A227E the codec can compensate for this offset and create a higher quality audio experience.

#### 9.3.9 FM Support

FM can be picked up using the headset ground line and passed through the ground FETs of the TS3A227E. By having a bandwidth of 200 MHz the full FM band can be passed through these FETs to a FM matching network and the FM receiver.

#### 9.4 Device Functional Modes

#### 9.4.1 Sleep Mode

The device will realize a sleep mode of 1 µA if the following are true:

- · No accessory is inserted

- Manual Switch Control = '0'

The TS3A227E will respond to I2C communication and insertion events while in sleep mode. The user can set the de-bounce settings and device configuration as desired while in the sleep mode. If the user sets the Manual Switch Control bit to '1' the device will turn on all blocks and come out of sleep mode.

If there is no accessory inserted and the users exits manual switch control, the switches will revert to the noinsertion state and all unnecessary blocks of the TS3A227E will turn off and enter the sleep mode.

Product Folder Links: TS3A227E

Copyright © 2014-2015, Texas Instruments Incorporated

#### **Device Functional Modes (continued)**

#### 9.4.2 Manual Switch Control

The TS3A227E supports manual switch control that can be utilized by setting Bit6 of the Device Settings 1 register to '1'.

Key operational characteristics of manual switch control are below.

- 1. Enabling the manual switch control does not disable automatic insertion and accessory type detection.

- 2. Manual Switch Control is blocked during accessory type detection which includes an automatic detection sequence or a manual SW triggered detection sequence. Any changes to the switch control registers, or setting the device to manual switch control will not update the switches until after the accessory type detection has completed.

- 3. Manual Switch Control is also blocked during de-bounce periods.

- 4. Excluding items 2 and 3 above, immediately after the system enables manual switch control the switch states will change to reflect the switch control registers. It is advised to set the desired state of the switches before enabling manual switch control.

- 5. Turning off the depletion FETs of the device will result in increased power consumption as defined in the electrical characteristics table.

- 6. Immediately upon setting Manual Switch Control = '0' the device will automatically configure the switches to the latest detection state. If an accessory is inserted but the TS3A227E has not run detection due to Auto Det EN = '0', the switch status will revert to the no insertion state.

- 7. The device cannot be in sleep mode and utilize manual switch control at the same time.

#### 9.4.3 Manual Switch Control Use Cases

The table below captures what occurs after a 3-pole insertion with the Manual Switch Control, Auto DET Enable, and DET Trigger bits set to the following before an insertion.

| MANUAL<br>SWITCH<br>CONTROL | AUTO DET<br>EN | DET TRIGGER<br>(SW) | DOES TYPE<br>DETECTION<br>RUN | SWITCH STATUS AFTER INSERTION | DET TRIGGER (SW) AFTER INSERTION |

|-----------------------------|----------------|---------------------|-------------------------------|-------------------------------|----------------------------------|

| 0                           | 0              | 0                   | no                            | No-insertion                  | 0                                |

| 0                           | 0              | 1                   | yes                           | 3-pole config                 | 0                                |

| 0                           | 1              | 0                   | yes                           | 3-pole config                 | 0                                |

| 0                           | 1              | 1                   | yes                           | 3-pole config                 | 0                                |

| 1                           | 0              | 0                   | no                            | Switch control registers      | 0                                |

| 1                           | 0              | 1                   | yes                           | Switch control registers      | 0                                |

| 1                           | 1              | 0                   | yes                           | Switch control registers      | 0                                |

| 1                           | 1              | 1                   | yes                           | Switch control registers      | 0                                |

The table below captures the switch and relevant register outputs for sequence 1.

| EVENT<br>NO. | EVENT DESCRIPTION                           | SWITCH STATUS     | 3-POLE<br>BIT | 4-POLE<br>STANDARD BIT | 4-POLE<br>OMTP BIT |

|--------------|---------------------------------------------|-------------------|---------------|------------------------|--------------------|

| 1            | Device powers up                            | No-insertion      | 0             | 0                      | 0                  |

| 2            | User sets Auto DET Enable = '0'             | No-insertion      | 0             | 0                      | 0                  |

| 3            | 3-pole accessory is inserted                | No-insertion      | 0             | 0                      | 0                  |

| 4            | System sets Manual Switch Control = '1'     | System controlled | 0             | 0                      | 0                  |

| 5            | System sets switch control registers = 0xFF | System controlled | 0             | 0                      | 0                  |

| 6            | System sets Manual Switch Control = '0'     | No-insertion      | 0             | 0                      | 0                  |

In sequence 1 at event 3 the switch status does not change because the system set the Auto DET Enable = '0'. When the accessory is inserted we will not run detection and not change the switches because of this.

At event 6 the system turns off manual switch control, the switch state reverts back to the No-insertion state because the TS3A227E has not ran detection.

The table below captures the switch and relevant register outputs for sequence 2.

| EVENT<br>NO. | EVENT DESCRIPTION                           |  | SWITCH STATUS<br>AFTER EVENT | 3-POLE<br>BIT | 4-POLE<br>STANDARD BIT | 4-POLE<br>OMTP BIT |

|--------------|---------------------------------------------|--|------------------------------|---------------|------------------------|--------------------|

| 1            | Device powers up                            |  | No-insertion                 | 0             | 0                      | 0                  |

| 2            | User sets Auto DET Enable = '0'             |  | No-insertion                 | 0             | 0                      | 0                  |

| 3            | 3-pole accessory is inserted                |  | No-insertion                 | 0             | 0                      | 0                  |

| 4            | System sets Manual Switch Control = '1'     |  | System controlled            | 0             | 0                      | 0                  |

| 5            | System sets switch control registers = 0xFF |  | System controlled            | 0             | 0                      | 0                  |

| 6            | System sets DET Trigger = '1'               |  | System controlled            | 1             | 0                      | 0                  |

| 7            | System sets Manual Switch Control = '0'     |  | 3-pole configuration         | 1             | 0                      | 0                  |

In sequence 2 at event 3 the switch status does not change because the system set the Auto DET Enable = '0'. When the accessory is inserted we will not run detection and not change the switches because of this.

At event 6 the system turns triggers a manual type detection and the TS3A227E detects a 3-pole accessory. The switch state will remain in the system controlled state.

At event 7 the system exits manual switch control. The switch status will then change back to the last detection state. Because detection was ran at event 6 and a 3-pole was detected, the switch state will reflect that of the 3-pole switch configuration.

#### 9.4.4 FM Support Mode

FM support mode needs to be entered via I2C through the Device Settings register. This will turn off the depletion switches when an accessory is inserted, eliminating the extra ground path. The ground line of the headset/headphone is used for FM transmission. This signal must pass through the TS3A227E ground FETs as shown in Figure 17 where the red line indicates the transmission path.

Figure 17. FM Support Transmission Path

#### **NOTE**

FM support should be enabled before an accessory is inserted. Toggling the FM support bit after a headset is inserted can cause a pop noise to be heard by the end user.

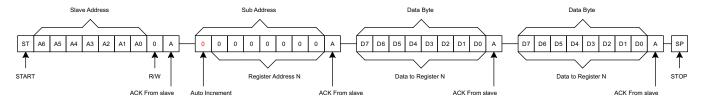

#### 9.5 Register Maps

The I<sup>2</sup>C address of the TS3A227E is b'0111011X or 77h read and 76h write.

| Addr<br>(xxh) | Name                    | Туре | Reset | Bit7                                          | Bit6                     | Bit5               | Bit4            | Bit3           | Bit2                             | Bit1              | Bit0                         |

|---------------|-------------------------|------|-------|-----------------------------------------------|--------------------------|--------------------|-----------------|----------------|----------------------------------|-------------------|------------------------------|

| 00h           | Device ID               | R    | 11h   | 0                                             | 0                        | 0                  | 1               | 0              | 0                                | 0                 | 1                            |

| 01h           | Interrupt               | R    | 00h   |                                               |                          | Reserved           |                 |                | ADC<br>Conversion                | DC                | Ins/Rem Event                |

| 02h           | Key Press<br>Interrupts | R    | 00h   | Key 4<br>Release                              | Key 4 Press              | Key 3 Release      | Key 3 Press     | Key 2 Release  | Key 2 Press                      | Key 1 Release     | Key 1 Press                  |

| 03h           | Interrupt Disable       | R/W  | 08h   |                                               | Reserved                 |                    |                 |                | ADC<br>Conversion<br>INT Disable | DC INT<br>Disable | Ins/Rem Event<br>INT Disable |

| 04h           | Device Settings         | R/W  | 23h   | Reset                                         | Manual Switch<br>Control | Auto DET<br>Enable | DET Trigger     | FM Support     | Inse                             | rtion De-bounce   | Time                         |

| 05h           | Device Setting 1        | R/W  | 00h   |                                               |                          | Reserved           |                 |                | Key Press<br>Enable              | Raw Data En       | ADC Trigger                  |

| 06h           | Device Setting 2        | R/W  | 0Eh   | Res                                           | served                   | MICBIAS Setting    |                 |                | Key Release<br>De-bounce         | Key Press         | De-bounce                    |

| 07h           | Switch Control 1        | R/W  | 00h   | Res                                           | served                   | SLEEVE<br>GNDFET   | RING2<br>GNDFET | SLEEVE<br>DFET | RING2 DFET                       | Switch 2          | Switch 1                     |

| 08h           | Switch Control 2        | R/W  | 00h   |                                               | Res                      | erved              |                 | S3PS           | S3PR                             | S3GS              | S3GR                         |

| 09h           | Switch Status 1         | R    | 0Ch   | Res                                           | served                   | SLEEVE<br>GNDFET   | RING2<br>GNDFET | SLEEVE<br>DFET | RING2 DFET                       | Switch 2          | Switch 1                     |

| 0Ah           | Switch Status 2         | R    | 00h   |                                               | Res                      | erved              |                 | S3PS           | S3PR                             | S3GS              | S3GR                         |

| 0Bh           | Accessory<br>Status     | R    | 00h   | Reserved Insertion Status Standard 4-pole OMT |                          |                    |                 |                |                                  |                   | 3-pole                       |

| 0Ch           | ADC Output              | R    | 00h   | ADC                                           |                          |                    |                 |                |                                  |                   |                              |

| 0Dh           | Threshold 1             | R/W  | 20h   | KP Threshold 1                                |                          |                    |                 |                |                                  |                   |                              |

| 0Eh           | Threshold 2             | R/W  | 40h   |                                               |                          |                    | KP Th           | reshold 2      |                                  |                   |                              |

| 0Fh           | Threshold 3             | R/W  | 68h   |                                               |                          |                    | KP Th           | reshold 3      |                                  |                   |                              |

#### Interrupt and Key Press Interrupt register notes:

- The device will continue to automatically run type detection and key press detection even if the host has not serviced the interrupts.

- Consecutive reads of an interrupt register at 400 kHz will not allow time for the internal registers to clear and will appear. The internal digital core requires 200 µs to clear the register after it has been read.

#### 9.6 Register Field Descriptions

#### 9.6.1 Device ID Register Field Descriptions (Address 00h)

Figure 18. Device ID Register Field Descriptions (Address 00h)

| Bit | Field     | Туре | Reset | Description            |

|-----|-----------|------|-------|------------------------|

| 7-0 | Device ID | R    | 11h   | Unique Revision number |

#### 9.6.2 Interrupt Register Field Descriptions (Address 01h)

Table 2. Interrupt Register Field Descriptions (Address 01h)

| Bit | Field          | Туре | Reset | Description                                                                                                                                                                                              |

|-----|----------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 | Reserved       | R    | 0h    |                                                                                                                                                                                                          |

| 2   | ADC Conversion | R    | 0h    | ADC Conversion complete Interrupt. Flagged after a manual ADC conversion is complete.                                                                                                                    |

|     |                |      |       | Interrupt bit is cleared after being read through I2C or after a removal event.                                                                                                                          |

|     |                |      |       | 0h = Default state<br>1h = ADC Conversion Complete                                                                                                                                                       |

| 1   | DC             | R    | 0h    | Detection Complete interrupt. Flagged after detection is completed for an insertion sequence. This bit is also flagged after completion of a manually triggered detection.                               |

|     |                |      |       | Interrupt bit is cleared after being read through I2C or after a removal event.                                                                                                                          |

|     |                |      |       | 0h = Default state<br>1h = Detection Completed                                                                                                                                                           |

| 0   | Ins/Rem Event  | R    | 0h    | Insertion or removal interrupt indicator. This bit is set if there is an insertion or removal event. The Insertion status bit of the Accessory Status register (0Bh) must be checked if this bit is set. |

|     |                |      |       | Interrupt bit is cleared after being read through I2C                                                                                                                                                    |

|     |                |      |       | 0h = Default state                                                                                                                                                                                       |

|     |                |      |       | 1h = Accessory has been inserted or removed                                                                                                                                                              |

#### 9.6.3 Key Press Interrupt Register Field Descriptions (Address 02h)

Table 3. Key Press Interrupt Register Field Descriptions (Address 02h)

| Bit | Field         | Туре | Reset | Description                                                                                                                              |

|-----|---------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Key 4 Release | R    | 0h    | This interrupt bit is set after the user has released key 4 on the accessory for a duration longer than the Key Release De-bounce timer. |

|     |               |      |       | This bit will auto-clear on the following conditions:                                                                                    |

|     |               |      |       | <ul> <li>Host reads the register through I<sup>2</sup>C</li> </ul>                                                                       |

|     |               |      |       | The KP Enable bit is set to '0'                                                                                                          |

|     |               |      |       | <ul> <li>The KP Enable bit is set to '0' automatically after a removal</li> </ul>                                                        |

|     |               |      |       | The Key 4 press bit is set ot '1'                                                                                                        |

|     |               |      |       | 0h = Default State                                                                                                                       |

|     |               |      |       | 1h = Key 4 was released                                                                                                                  |

| 6   | Key 4 Press   | R    | 0h    | This interrupt bit is set after the user has pressed key 4 on the accessory for a duration longer than the Key Press De-bounce timer.    |

|     |               |      |       | This bit will auto-clear on the following conditions:                                                                                    |

|     |               |      |       | <ul> <li>Host reads the register through I<sup>2</sup>C</li> </ul>                                                                       |

|     |               |      |       | The KP Enable bit is set to '0'                                                                                                          |

|     |               |      |       | <ul> <li>The KP Enable bit is set to '0' automatically after a removal</li> </ul>                                                        |

|     |               |      |       | 0h = Default State                                                                                                                       |

|     |               |      |       | 1h = Key 4 was released                                                                                                                  |

| 5   | Key 3 Release | R    | 0h    | This interrupt bit is set after the user has pressed Key 3 on the accessory for a duration longer than the Key Release De-bounce timer.  |

|     |               |      |       | This bit will auto-clear on the following conditions:                                                                                    |

|     |               |      |       | <ul> <li>Host reads the register through I<sup>2</sup>C</li> </ul>                                                                       |

|     |               |      |       | The KP Enable bit is set to '0'                                                                                                          |

|     |               |      |       | <ul> <li>The KP Enable bit is set to '0' automatically after a removal</li> </ul>                                                        |

|     |               |      |       | The Key 3 Press bit is set to '1'                                                                                                        |

|     |               |      |       | 0h = Default State                                                                                                                       |

|     |               |      |       | 1h = Key 3 was released                                                                                                                  |

# Table 3. Key Press Interrupt Register Field Descriptions (Address 02h) (continued)

| Bit | Field           | Туре | Reset | Description                                                                                                                                                                           |

|-----|-----------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Key 3 Press     | R    | 0h    | This interrupt bit is set after the user has pressed Key 3 on the accessory for a duration longer than the Key Press De-bounce timer.                                                 |