# Advance Information Intelligent Power Module (IPM) 600 V, 3 A

The STK5C4U332J-E is a fully-integrated inverter power stage consisting of a high-voltage driver, six IGBT's and a thermistor, suitable for driving permanent magnet synchronous (PMSM) motors, brushless-DC (BLDC) motors and AC asynchronous motors. The IGBT's are configured in a 3phase bridge with separate emitter connections for the lower legs for maximum flexibility in the choice of control algorithm.

The power stage has a full range of protection functions including crossconduction protection, external shutdown and under-voltage lockout functions. An internal comparator and reference connected to the overcurrent protection circuit allows the designer to set the over-current protection level.

#### Features

- Three-phase 3 A / 600 V IGBT module with integrated drivers

- Typical values :  $V_{CE}(sat) = 1.3 V$ ,  $V_F = 1.3 V$ ,  $E_{SW} = 115 \mu J$  at 1.5 A

- Compact 29.6 mm × 18.2 mm dual in-line package

- Cross-conduction protection

- Adjustable over-current protection level

- Integrated bootstrap diodes and resistors

- Enable pin

#### Certification

• UL1557 (File number : E339285)

#### **Typical Applications**

- Industrial Pumps

- Industrial Fans

- Industrial Automation

- Home Appliances

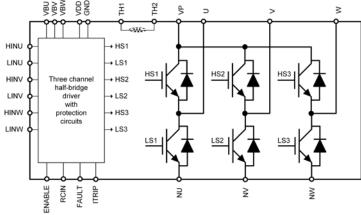

Figure 1. Functional Diagram

### **ON Semiconductor®**

www.onsemi.com

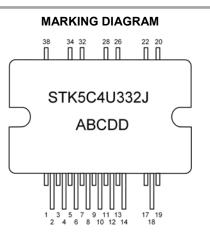

PACKAGE PICTURE

MODULE 29.6x18.2 DIP S

STK5C4U332J = Specific Device Code A = Year

- B = Month

- C = Production Site

- DD = Factory Lot Code

Device marking is on package underside

#### **ORDERING INFORMATION**

| Device        | Package                                | Shipping<br>(Qty / Packing) |  |

|---------------|----------------------------------------|-----------------------------|--|

| STK5C4U332J-E | MODULE<br>29.6x18.2 DIP S<br>(Pb-Free) | 16 / Tube                   |  |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

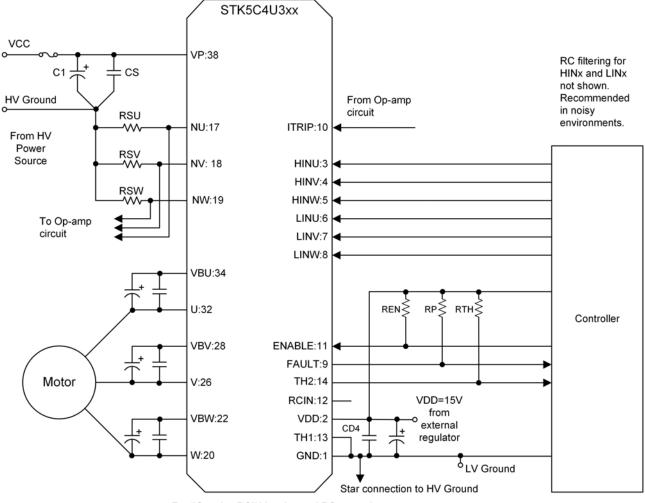

For 5C series RCIN has internal RC network

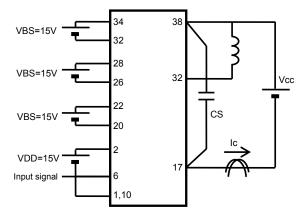

Figure 2. Application Schematic

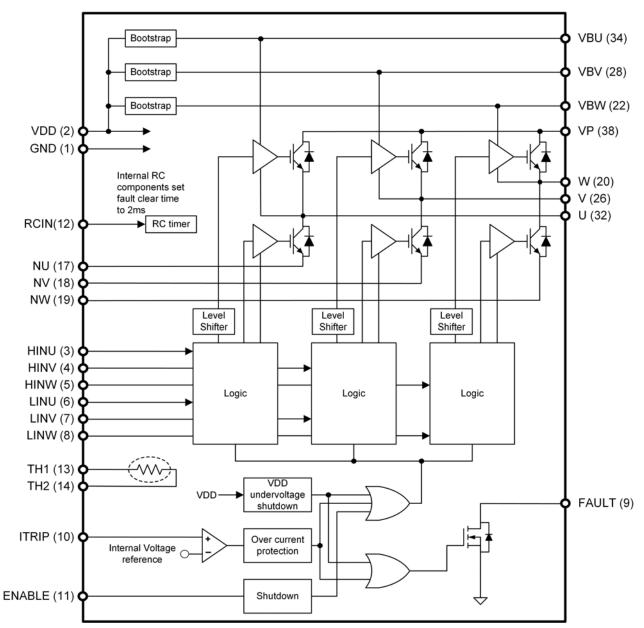

Figure 3. Simplified Block Diagram

#### **PIN FUNCTION DESCRIPTION**

| Pin | Name   | Description                                                             |  |  |  |

|-----|--------|-------------------------------------------------------------------------|--|--|--|

| 1   | GND    | Negative Main Supply                                                    |  |  |  |

| 2   | VDD    | +15 V Main Supply                                                       |  |  |  |

| 3   | HINU   | ogic Input High Side Gate Driver - Phase U                              |  |  |  |

| 4   | HINV   | Logic Input High Side Gate Driver - Phase V                             |  |  |  |

| 5   | HINW   | Logic Input High Side Gate Driver - Phase W                             |  |  |  |

| 6   | LINU   | Logic Input Low Side Gate Driver - Phase U                              |  |  |  |

| 7   | LINV   | Logic Input Low Side Gate Driver - Phase V                              |  |  |  |

| 8   | LINW   | Logic Input Low Side Gate Driver - Phase W                              |  |  |  |

| 9   | FAULT  | Fault output                                                            |  |  |  |

| 10  | ITRIP  | Current protection pin                                                  |  |  |  |

| 11  | ENABLE | Enable input                                                            |  |  |  |

| 12  | RCIN   | R,C connection terminal for setting FAULT clear time                    |  |  |  |

| 13  | TH1    | Thermistor output 1                                                     |  |  |  |

| 14  | TH2    | Thermistor output 2                                                     |  |  |  |

| 17  | NU     | Low Side Emitter Connection - Phase U                                   |  |  |  |

| 18  | NV     | Low Side Emitter Connection - Phase V                                   |  |  |  |

| 19  | NW     | Low Side Emitter Connection - Phase W                                   |  |  |  |

| 20  | W      | W phase output. Internally connected to W phase high side driver ground |  |  |  |

| 22  | VBW    | High Side Floating Supply Voltage for W phase                           |  |  |  |

| 26  | V      | V phase output. Internally connected to V phase high side driver ground |  |  |  |

| 28  | VBV    | High Side Floating Supply voltage for V phase                           |  |  |  |

| 32  | U      | U phase output. Internally connected to U phase high side driver ground |  |  |  |

| 34  | VBU    | High Side Floating Supply voltage for U phase                           |  |  |  |

| 38  | VP     | Positive Bus Input Voltage                                              |  |  |  |

Note : Pins 15, 16, 21, 23, 24, 25, 27, 29, 30, 31, 33, 35, 36, 37 are not present

### **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

| Rating                      | Symbol              | Conditions                                                       | Value                   | Unit |

|-----------------------------|---------------------|------------------------------------------------------------------|-------------------------|------|

| Supply voltage              | V <sub>CC</sub>     | VP to NU,NV,NW, surge < 500 V (Note 3)                           | 450                     | V    |

| Collector-emitter voltage   | V <sub>CE</sub> max | VP to U,V,W; U to NU; V to NV; W to NW                           | 600                     | V    |

|                             |                     | VP,U,V,W,NU,NV,NW terminal current                               | ±3                      | A    |

| Output current              | lo                  | VP,U,V,W,NU,NV,NW terminal current,<br>Tc = 100°C                | ±1.5                    | А    |

| Output peak current         | Іор                 | VP,U,V,W,NU,NV,NW terminal current,<br>pulse width 1ms           | ±6                      | А    |

| Gate driver supply voltages | VBS                 | VBU to U, VBV to V, VBW to W, V <sub>DD</sub> to GND<br>(Note 4) | -0.3 to +20.0           | V    |

| Input signal voltage        | VIN                 | HINU, HINV, HINW, LINU, LINV, LINW                               | -0.3 to V <sub>DD</sub> | V    |

| FAULT terminal voltage      | VFAULT              | FAULT terminal                                                   | -0.3 to V <sub>DD</sub> | V    |

| RCIN terminal voltage       | VRCIN               | RCIN terminal                                                    | -0.3 to V <sub>DD</sub> | V    |

| ITRIP terminal voltage      | VITRIP              | ITRIP terminal                                                   | -0.3 to +10.0           | V    |

| ENABLE terminal voltage     | VENABLE             | ENABLE terminal                                                  | -0.3 to V <sub>DD</sub> | V    |

| Maximum power dissipation   | Pd                  | IGBT per 1 channel                                               | 11.3                    | W    |

| Junction temperature        | Тј                  | IGBT, Gate driver IC                                             | 150                     | °C   |

| Storage temperature         | Tstg                |                                                                  | -40 to +125             | °C   |

| Operating case temperature  | Тс                  | IPM case temperature                                             | -20 to +100             | °C   |

| Package mounting torque     |                     | Case mounting screw                                              | 0.6                     | Nm   |

| Isolation voltage           | Vis                 | 50 Hz sine wave AC 1 minute (Note 5)                             | 2000                    | Vrms |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for 1.

2. Safe Operating parameters. This surge voltage developed by the switching operation due to the wiring inductance between VP and NU,NV,NW terminals. VBS=VBU to U, VBV to V, VBW to W. Test conditions : AC 2500 V, 1 s.

3.

4.

5.

#### **RECOMMENDED OPERATING RANGES** (Note 6)

| Rating                      | Symbol          |                                    | Min  | Тур | Max             | Unit |

|-----------------------------|-----------------|------------------------------------|------|-----|-----------------|------|

| Supply voltage              | V <sub>CC</sub> | VP to NU,NV,NW                     | 0    | 280 | 450             | V    |

|                             | VBS             | VBU to U, VBV to V, VBW to W       | 12.5 | 15  | 17.5            | V    |

| Gate driver supply voltage  | V <sub>DD</sub> | V <sub>DD</sub> to GND (Note 4)    | 13.5 | 15  | 16.5            | V    |

| ON-state input voltage      | VIN(ON)         |                                    | 2.5  |     | V <sub>DD</sub> | V    |

| OFF-state input voltage     | VIN(OFF)        | HINU, HINV, HINW, LINU, LINV, LINW | 0    |     | 0.8             |      |

| PWM frequency               | fPWM            |                                    | 1    |     | 20              | kHz  |

| Dead time                   | DT              | Turn-off to turn-on (external)     | 1.3  |     |                 | μs   |

| Allowable input pulse width | PWIN            | ON and OFF                         | 1    |     |                 | μs   |

| Package mounting torque     |                 | 'M3' type screw                    | 0.4  |     | 0.6             | Nm   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to 6. stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### ELECTRICAL CHARACTERISTICS at Tc = 25°C (Note 7)

| Parameter                                                                                  | Test Conditions                                 | Symbol                                   | Min            | Тур  | Мах  | Unit |

|--------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------|----------------|------|------|------|

| Power output section                                                                       |                                                 | 1                                        |                |      |      |      |

| Collector-emitter leakage current                                                          | V <sub>CE</sub> = 600 V                         | ICE                                      |                |      | 100  | μA   |

| Bootstrap diode reverse current                                                            | VR(BD) = 600 V                                  | IR(BD)                                   |                |      | 100  | μA   |

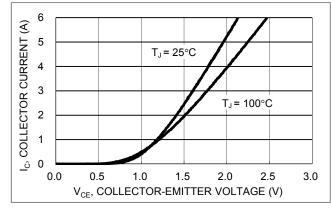

|                                                                                            | lc = 3 A, Tj = 25°C                             | V <sub>CE</sub> (SAT)                    |                | 1.6  | 2.4  | V    |

| Collector to emitter saturation voltage                                                    | lc = 1.5 A, Tj = 100°C                          |                                          |                | 1.3  | -    | V    |

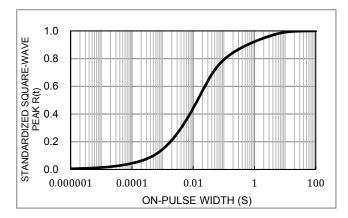

|                                                                                            | IF = 3 A, Tj = 25°C                             | VF                                       |                | 1.5  | 2.3  | V    |

| Diode forward voltage                                                                      | IF = 1.5 A, Tj = 100°C                          |                                          |                | 1.3  | -    | V    |

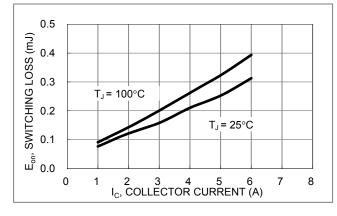

| Junction to case thermal resistance                                                        | Reverse conducting IGBT                         | θj-c(T)                                  | -              | -    | 11   | °C/W |

|                                                                                            |                                                 | t <sub>on</sub>                          | -              | 0.5  | 1.2  | μs   |

| Switching time                                                                             | lc = 3 A, V <sub>CC</sub> = 300 V, Tj = 25°C    | t <sub>OFF</sub>                         | -              | 0.6  | 1.4  | μs   |

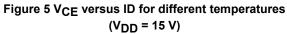

| Turn-on switching loss                                                                     |                                                 | E <sub>ON</sub>                          | -              | 100  | -    | μJ   |

| Turn-off switching loss                                                                    | lc = 1.5 A, V <sub>CC</sub> = 300 V, Tj = 25°C  | E <sub>OFF</sub>                         | -              | 15   | -    | μJ   |

| Total switching loss                                                                       | 1                                               | E <sub>TOT</sub>                         | -              | 115  | -    | μJ   |

| Turn-on switching loss                                                                     |                                                 | E <sub>ON</sub>                          | -              | 120  | -    | μJ   |

| Turn-off switching loss                                                                    | lc = 1.5 A, V <sub>CC</sub> = 300 V, Tj = 100°C | E <sub>OFF</sub>                         | -              | 20   | -    | μJ   |

| Total switching loss                                                                       | 1                                               | Етот                                     | -              | 140  | -    | μJ   |

| Diode reverse recovery energy                                                              | lc = 1.5 A, V <sub>CC</sub> = 300 V, Tj = 100°C | E <sub>REC</sub>                         | -              | 35   | -    | μJ   |

| Diode reverse recovery time                                                                | (di/dt set by internal driver)                  | trr                                      | -              | 150  | -    | ns   |

| Reverse bias safe operating area                                                           | Ic = 6 A, V <sub>CE</sub> = 450 V               | RBSOA                                    | Full<br>Square | -    |      |      |

| Short circuit safe operating area                                                          | V <sub>CE</sub> = 400 V                         | SCSOA                                    | 3              | -    | -    | μs   |

| Allowable offset voltage slew rate                                                         | U to UN, V to VN, W to WN                       | dv/dt                                    | -50            | -    | 50   | V/ns |

| Driver Section                                                                             | •                                               |                                          |                |      |      |      |

|                                                                                            | V <sub>BS</sub> = 15 V (Note 4), per driver     | ID                                       | -              | 0.1  | 0.2  | mA   |

| Gate driver consumption current                                                            | V <sub>DD</sub> = 15 V, total                   | ID                                       | -              | 1.3  | 2.6  | mA   |

| High level Input voltage                                                                   | HINU, HINV, HINW, LINU, LINV, LINW              | Vin H                                    | 2.5            | -    | -    | V    |

| Low level Input voltage                                                                    | to GND                                          | Vin L                                    | -              | -    | 0.8  | V    |

| Logic 1 input current                                                                      | VIN = +3.3 V                                    | I <sub>IN+</sub>                         | -              | 100  | 143  | μA   |

| Logic 0 input current                                                                      | VIN = 0 V                                       | I <sub>IN-</sub>                         | -              | -    | 2    | μA   |

| Bootstrap ON Resistance                                                                    | IB = 1 mA                                       | RB                                       | -              | 110  | 300  | Ω    |

| FAULT terminal sink current                                                                | FAULT : ON / VFAULT = 0.1 V                     | loSD                                     | -              | 2    | -    | mA   |

| FAULT clearance delay time                                                                 |                                                 | FLTCLR                                   | 1              | 2    | 3    | ms   |

|                                                                                            | VEN ON-state voltage                            | VEN +                                    | 2.5            | -    | -    | V    |

| ENABLE ON/OFF voltage                                                                      | VEN OFF-state voltage                           | VEN –                                    | -              | -    | 0.8  | V    |

| ITRIP threshold voltage                                                                    | ITRIP to GND                                    | VITRIP                                   | 0.44           | 0.49 | 0.54 | V    |

| ITRIP to shutdown propagation delay                                                        |                                                 | t <sub>ITRIP</sub>                       | -              | 550  | -    | ns   |

| ITRIP blanking time                                                                        |                                                 | t <sub>ITRIPBL</sub>                     | 100            | 350  | -    | ns   |

| V <sub>DD</sub> and V <sub>BS</sub> supply undervoltage positive going input threshold     |                                                 | V <sub>DDUV+</sub><br>V <sub>BSUV+</sub> | 10.5           | 11.1 | 11.7 | V    |

| V <sub>DD</sub> and V <sub>BS</sub> supply undervoltage negative going input threshold     |                                                 | V <sub>DDUV-</sub><br>V <sub>BSUV-</sub> | 10.3           | 10.9 | 11.5 | V    |

| V <sub>DD</sub> and V <sub>BS</sub> supply undervoltage I <sub>lockout</sub><br>hysteresis |                                                 | V <sub>DDUVH</sub><br>V <sub>BSUVH</sub> | 0.14           | 0.2  | -    | V    |

7. Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

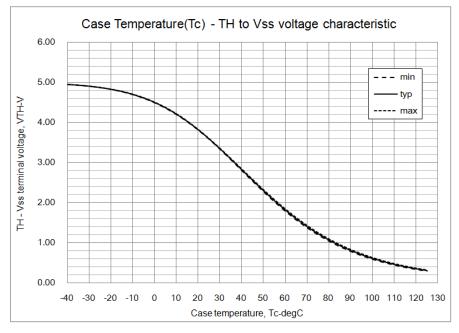

### **TYPICAL CHARACTERISTICS**

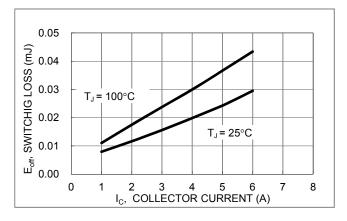

Figure 8 EON versus ID for different temperatures

Figure 6 Thermal impedance plot

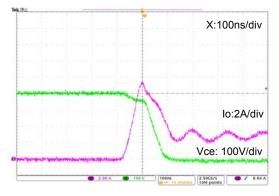

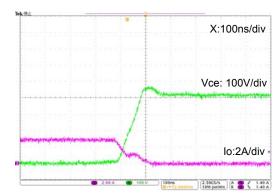

Figure 9 Turn-on waveform Tj = 100°C, V<sub>CC</sub> = 400 V

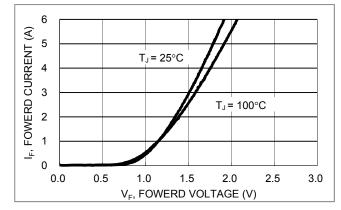

Figure 4 VF versus ID for different temperatures

Figure 7 EOFF versus ID for different temperatures

### **APPLICATIONS INFORMATION**

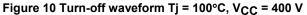

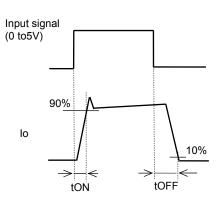

#### Input / Output Timing Chart

Figure 11. Input/Output Timing Chart

#### Notes

- 1. This section of the timing diagram shows the effect of cross-conduction prevention.

- This section of the timing diagram shows that when the voltage on V<sub>DD</sub> decreases sufficiently all gate output signals will go low, switching off all six IGBTs. When the voltage on V<sub>DD</sub> rises sufficiently, normal operation will resume.

- This section shows that when the bootstrap voltage V<sub>BS</sub> drops, the corresponding high side output (U or V or W) is switched off. When V<sub>BS</sub> rises sufficiently, normal operation will resume.

- 4. This section shows that when the voltage on ITRIP exceeds the threshold, all IGBT's are turned off. Normal operation resumes later after the over-current condition is removed.

- 5. After V<sub>DD</sub> has risen above the threshold to enable normal operation, the driver waits to receive an input signal on the LIN input before enabling the driver for the HIN signal.

### Input / Output Logic Table

|     | II  | IPUT  |        | OUTPUT            |                  |                |       |  |  |

|-----|-----|-------|--------|-------------------|------------------|----------------|-------|--|--|

| HIN | LIN | ltrip | Enable | High side<br>IGBT | Low side<br>IGBT | U,V,W          | FAULT |  |  |

| Н   | L   | L     | Н      | ON (Note 5)       | OFF              | VP             | OFF   |  |  |

| L   | н   | L     | н      | OFF               | ON               | NU,NV,NW       | OFF   |  |  |

| L   | L   | L     | н      | OFF               | OFF              | High Impedance | OFF   |  |  |

| Н   | Н   | L     | Н      | OFF               | OFF              | High Impedance | OFF   |  |  |

| х   | х   | Н     | Н      | OFF               | OFF              | High Impedance | ON    |  |  |

| х   | х   | х     | L      | OFF               | OFF              | High Impedance | OFF   |  |  |

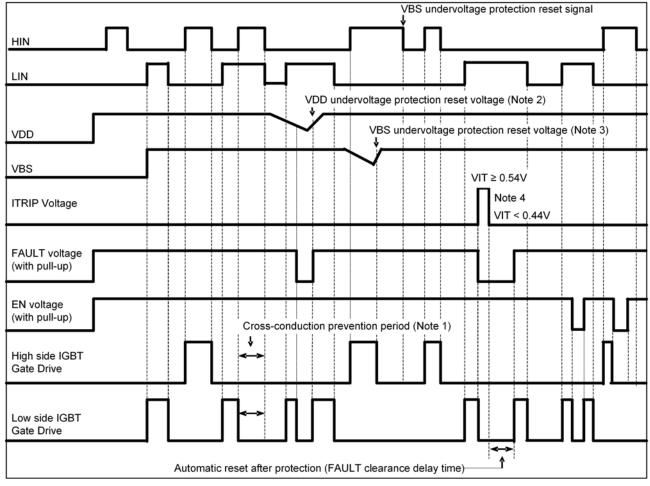

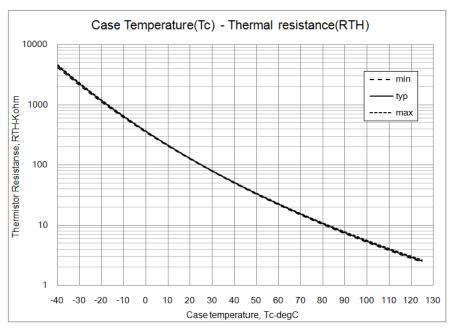

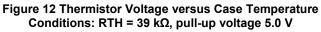

#### **Thermistor characteristics**

| Parameter               | Symbol           | Condition  | Min  | Тур  | Max  | Unit |

|-------------------------|------------------|------------|------|------|------|------|

| Resistance              | R <sub>25</sub>  | Tc = 25°C  | 99   | 100  | 101  | kΩ   |

|                         | R <sub>100</sub> | Tc = 100°C | 5.18 | 5.38 | 5.60 | kΩ   |

| B-Constant (25 to 50°C) | В                |            | 4208 | 4250 | 4293 | К    |

| Temperature Range       |                  |            | -40  |      | +125 | °C   |

Figure 9 Thermistor Resistance versus Case Temperature

(see Figure 2)

#### Fault output

The FAULT output is an open drain output requiring a pull-up resistor. If the pull-up voltage is 5 V, use a pull-up resistor with a value of 6.8 k $\Omega$  or higher. If the pull-up voltage is 15 V, use a pull-up resistor with a value of 20 k $\Omega$  or higher. The FAULT output is triggered if there is a V<sub>DD</sub> undervoltage or an overcurrent condition.

#### Undervoltage lockout protection

If  $V_{DD}$  goes below the  $V_{DD}$  supply undervoltage lockout falling threshold, the FAULT output is switched on. The FAULT output stays on until  $V_{DD}$  rises above the  $V_{DD}$  supply undervoltage lockout rising threshold. After  $V_{DD}$  has risen above the threshold to enable normal operation, the driver waits to receive an input signal on the LIN input before enabling the driver for the HIN signal.

#### **Overcurrent protection**

An over-current condition is detected if the voltage on the ITRIP pin is larger than the reference voltage. There is a blanking time of typically 350 ns to improve noise immunity. After a shutdown propagation delay of typically 0.55  $\mu$ s, the FAULT output is switched on. The FAULT output is held on for a time determined by the resistor and capacitor connected to the RCIN pin. If RCIN pin is unconnected, the internal RC components set fault clear time to 2 ms (typical).

The over-current protection threshold should be set to be equal or lower to 2 times the module rated current (IO).

An additional fuse is recommended to protect against system level or abnormal over-current fault conditions.

#### Capacitors on High Voltage and VDD supplies

Both the high voltage and  $V_{DD}$  supplies require an electrolytic capacitor and an additional high frequency capacitor.

#### Enable pin

The ENABLE terminal pin is used to enable or shut down the built-in driver. If the voltage on the ENABLE pin rises above the ENABLE ON-state voltage, the output drivers are enabled. If the voltage on the ENABLE pin falls below the ENABLE OFF-state voltage, the drivers are disabled.

#### Minimum input pulse width

When input pulse width is less than 1  $\mu$ s, an output may not react to the pulse. (Both ON signal and OFF signal)

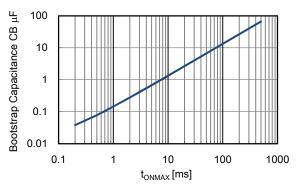

#### Calculation of bootstrap capacitor value

The bootstrap capacitor value CB is calculated using the following approach. The following parameters influence the choice of bootstrap capacitor:

- VBS: Bootstrap power supply. 15 V is recommended.

- QG: Total gate charge of IGBT at VBS = 15 V. 34 nC

- UVLO: Falling threshold for UVLO. Specified as 12 V.

- ID<sub>MAX</sub>: High side drive consumption current. Specified as 0.4 mA

- t<sub>ONMAX</sub>: Maximum ON pulse width of high side IGBT.

Capacitance calculation formula:

$$CB = (QG + ID_{MAX} * t_{ONMAX}) / (VBS - UVLO)$$

CB is recommended to be approximately 3 times the value calculated above. The recommended value of CB is in the range of 1 to 47  $\mu$ F, however, the value needs to be verified prior to production. When not using the bootstrap circuit, each high side driver power supply requires an external independent power supply.

The internal bootstrap circuit uses a MOSFET. The turn on time of this MOSFET is synchronized with the turn on of the low side IGBT. The bootstrap capacitor is charged by turning on the low side IGBT.

If the low side IGBT is held on for a long period of time (more than one second for example), the bootstrap voltage on the high side MOSFET will slowly discharge.

Figure 13: Bootstrap capacitance versus tonmax

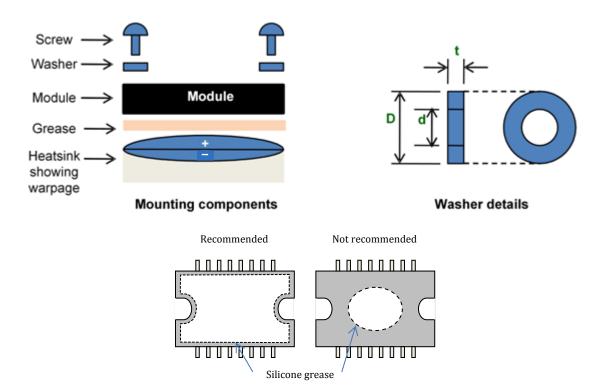

### **Mounting Instructions**

| Item      | Recommended Condition                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pitch     | 26.0 ±0.1 mm (Please refer to Package Outline Diagram)                                                                                                                                                                                                        |

| Screw     | Diameter : M3<br>Screw head types : pan head, truss head, binding head                                                                                                                                                                                        |

| Washer    | Plane washer dimensions (Figure 14)<br>D = 7 mm, d = $3.2$ mm and t = $0.5$ mm JIS B 1256                                                                                                                                                                     |

| Heat sink | Material: Aluminum or Copper<br>Warpage (the surface that contacts IPM ) : -50 to 50 μm<br>Screw holes must be countersunk.<br>No contamination on the heat sink surface that contacts IPM.                                                                   |

| Torque    | Temporary tightening : 50 to 60% of final tightening on first screw<br>Temporary tightening : 50 to 60% of final tightening on second screw<br>Final tightening : 0.4 to 0.6 Nm on first screw<br>Final tightening : 0.4 to 0.6 Nm on second screw            |

| Grease    | Silicone grease.<br>Thickness : 50 to 100 μm<br>Uniformly apply silicone grease to whole back.<br>Thermal foils are only recommended after careful evaluation. Thickness, stiffness and<br>compressibility parameters have a strong influence on performance. |

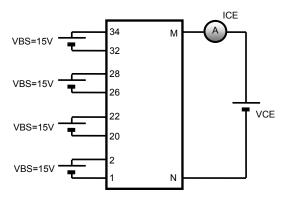

## **TEST CIRCUITS**

■ ICE

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| М | 38 | 38 | 38 | 32 | 26 | 20 |

| Ν | 32 | 26 | 20 | 17 | 18 | 19 |

U+,V+,W+ : High side phase U-,V-,W- : Low side phase

Figure 15 Test Circuit for ICE

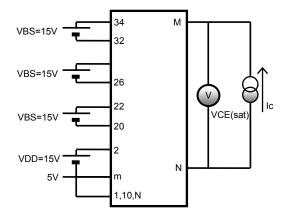

■ V<sub>CE</sub>(sat) (Test by pulse)

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| М | 38 | 38 | 38 | 32 | 26 | 20 |

| Ν | 32 | 26 | 20 | 17 | 18 | 19 |

| m | 3  | 4  | 5  | 6  | 7  | 8  |

Figure 16 Test circuit for V<sub>CE</sub>(sat)

Figure 17 Test circuit for VF

■ VF (Test by pulse)

|   | U+ | V+ | W+ | U- | V- | W- |

|---|----|----|----|----|----|----|

| М | 38 | 38 | 38 | 32 | 26 | 20 |

| Ν | 32 | 26 | 20 | 17 | 18 | 19 |

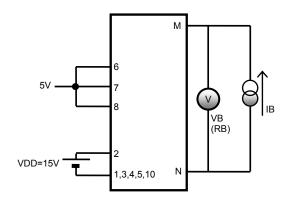

### ■ RB (Test by pulse)

|   | U+ | V+ | W+ |  |

|---|----|----|----|--|

| М | 2  | 2  | 2  |  |

| N | 34 | 28 | 22 |  |

Figure 18 Test circuit for RB

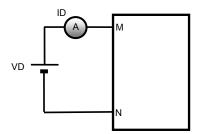

∎ ID

|   | VBS U+ | VBS V+ | VBS W+ | V <sub>DD</sub> |

|---|--------|--------|--------|-----------------|

| М | 34     | 28     | 22     | 2               |

| N | 32     | 26     | 20     | 1               |

Figure 19 Test circuit for ID

Switching time (The circuit is a representative example of the low side U phase.)

Figure 20 Switching time test circuit

#### PACKAGE DIMENSIONS unit : mm

missing pin : 15,16,21,23,24,25,27,  $\infty$ 29,30,31,33,35,36,37 പ  $\infty$ 1 29.6 26.4±0.1 26±0.1(Screw pitch) 38 20 Π П П П Ŕ STK5C4U332J  $\sim$ (21.1) I8.2 20 6 1 19  $0.5^{+0.2}_{-0.05}$ 1 3.4 18×1.0=18 1  $\infty$ Ο  $\infty$  $\sim$ Ъ. 4

The tolerances of length are +/-0.5 mm unless otherwise specified.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor and to vary in different application in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly or use for any such unintended or unauthorized with such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers,