LP5562

SNVS820A - APRIL 2013-REVISED SEPTEMBER 2015

# LP5562 Four-Channel LED Driver With Programmable Lighting Sequences

Technical

Documents

Sample &

Buy

#### **1** Features

- Four Independently Programmable LED Outputs With 8-Bit Current Setting (From 0 mA to 25.5 mA With 100-µA Steps) and 8-Bit PWM Control

- Typical LED Output Saturation Voltage 60 mV and Current Matching 1%

- Flexible PWM Control for LED Outputs

- Automatic Power-Save Mode With External Clock

- Three Program Execution Engines With Flexible

Instruction Set

- Autonomous Operation With Program Execution Engines

- SRAM Program Memory for Lighting Pattern

Programs

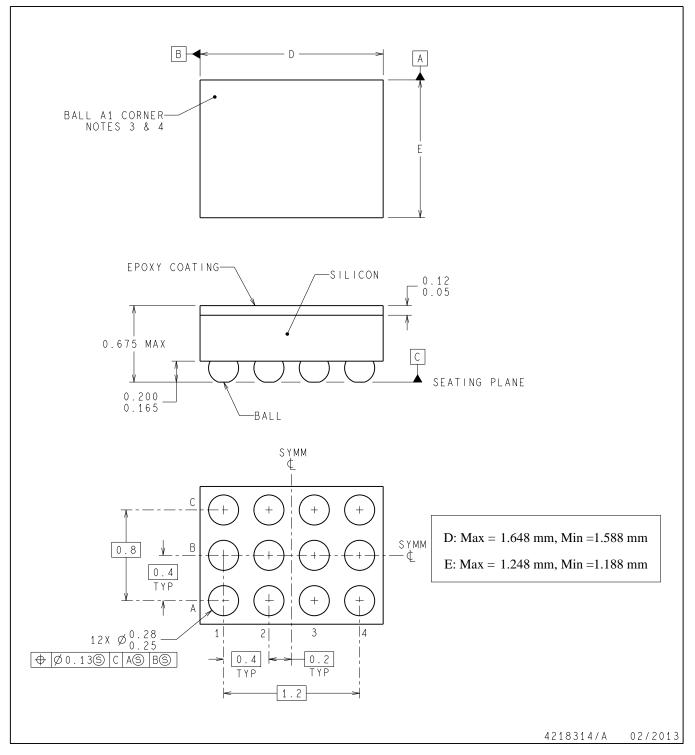

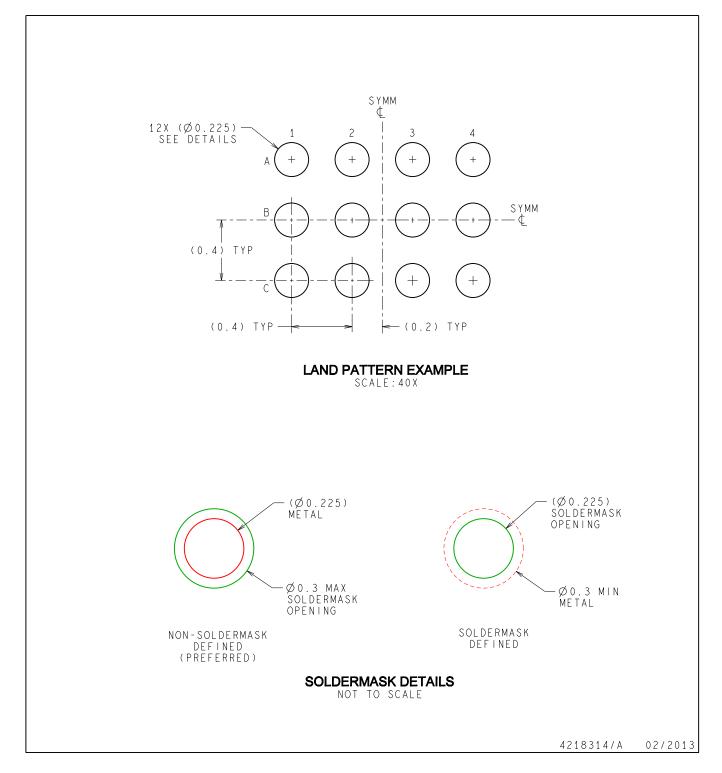

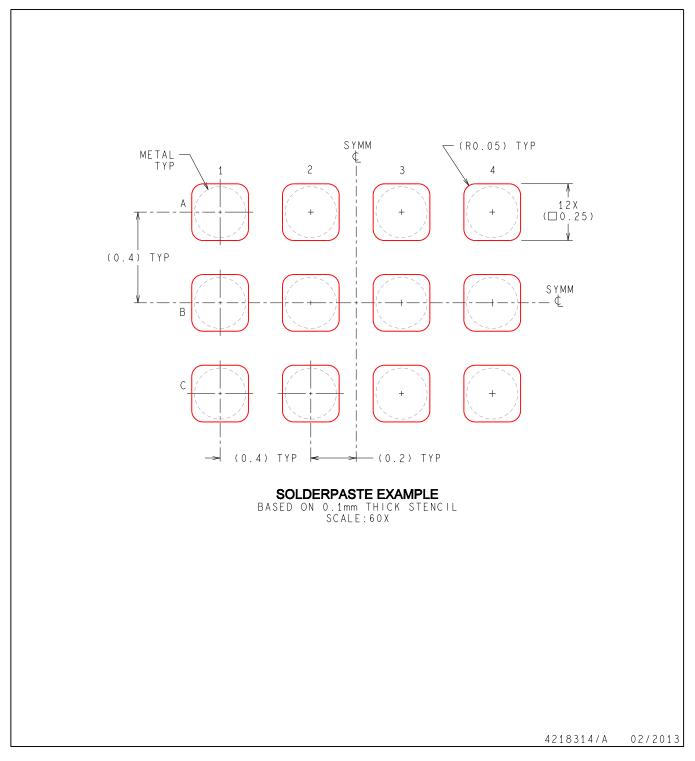

- DSBGA 12-Pin Package, 0.4-mm Pitch

# 2 Applications

- Fun Lights

- Indicator Lights

- Keypad RGB Backlighting and Phone Cosmetics

# 3 Description

Tools &

Software

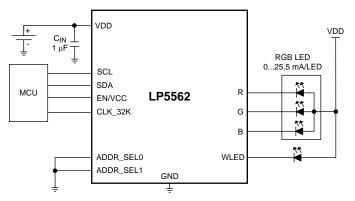

The LP5562 is a four-channel LED driver designed to produce variety of lighting effects. The device has a program memory for creating variety of lighting sequences. When the program memory has been loaded, the LP5562 can operate independently without processor control.

Support &

Community

....

The LP5562 is able to automatically enter power save mode, when LED outputs are not active and thus lowering current consumption.

Four independent LED channels have accurate programmable current sinks, from 0 mA to 25.5 mA with 100- $\mu$ A steps and flexible PWM control. Each channel can be configured into each of the three program execution engines. Program execution engines have program memory for creating desired lighting sequences with PWM control.

The LP5562 has four pin-selectable  $I^2C$  addresses. This allows connecting up to four parallel devices in one  $I^2C$  bus. The device requires only one small, lowcost ceramic capacitor.

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)     |

|-------------|------------|---------------------|

| LP5562      | DSBGA (12) | 1.648 mm × 1.248 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

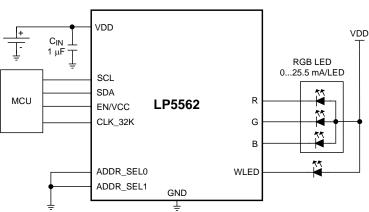

#### **Typical Application Diagram**

Features ..... 1

Applications ..... 1 Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Specifications...... 4 Absolute Maximum Ratings ...... 4

ESD Ratings..... 4

Recommended Operating Conditions ...... 4

Thermal Information ...... 4

6.7 Recommended External Clock Source Conditions... 6 6.10 Typical Characteristics: LED Output ...... 9 Detailed Description ..... 10

7.1 Overview ...... 10 7.2 Functional Block Diagram ..... 10

1

2

3 4

5

6

7

6.1

6.2

6.3

6.4

2

# Device Functional Modes...... 23 7.4 8

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (April 2013) to Revision A

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional |

|---|------------------------------------------------------------------------------------------------------------------|

|   | Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device      |

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                  |

# Table of Contents

|    | 7.5  | Programming                       | 25 |

|----|------|-----------------------------------|----|

|    | 7.6  | Register Maps                     | 30 |

| 8  | Арр  | lication and Implementation       | 40 |

|    | 8.1  | Application Information           | 40 |

|    | 8.2  | Typical Application               | 40 |

| 9  | Pow  | er Supply Recommendation          | 43 |

| 10 | Lay  | out                               | 43 |

|    | 10.1 | Layout Guidelines                 | 43 |

|    | 10.2 | Layout Example                    | 43 |

| 11 | Dev  | ice and Documentation Support     | 44 |

|    | 11.1 | Device Support                    | 44 |

|    | 11.2 | Documentation Support             | 44 |

|    | 11.3 | Community Resources               | 44 |

|    | 11.4 | Trademarks                        | 44 |

|    | 11.5 | Electrostatic Discharge Caution   | 44 |

|    | 11.6 | Glossary                          | 44 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 44 |

7.3 Feature Description..... 10

| Texas       |

|-------------|

| INSTRUMENTS |

www.ti.com

Page

#### LP5562 SNVS820A – APRIL 2013–REVISED SEPTEMBER 2015

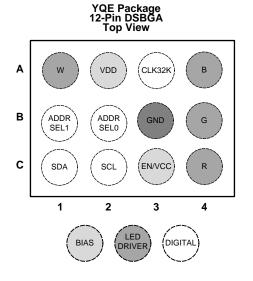

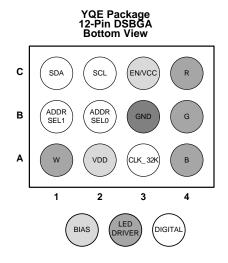

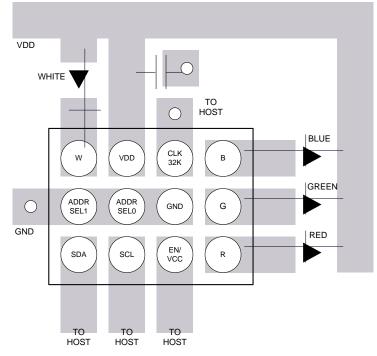

# 5 Pin Configuration and Functions

#### **Pin Functions**

| P           | IN        | I/O <sup>(1)</sup> | DESCRIPTION                                         |  |  |  |

|-------------|-----------|--------------------|-----------------------------------------------------|--|--|--|

| NUMBER NAME |           | 1/0 ( )            | DESCRIPTION                                         |  |  |  |

| A1          | W         | А                  | LED driver current sink terminal                    |  |  |  |

| A2          | VDD       | Р                  | Power supply                                        |  |  |  |

| A3          | CLK_32K   | I                  | External 32-kHz clock input                         |  |  |  |

| A4          | В         | А                  | LED driver current sink terminal                    |  |  |  |

| B1          | ADDR_SEL1 | I                  | I <sup>2</sup> C address selection pin              |  |  |  |

| B2          | ADDR_SEL0 | I                  | I <sup>2</sup> C address selection pin              |  |  |  |

| B3          | GND       | G                  | Ground                                              |  |  |  |

| B4          | G         | А                  | LED driver current sink terminal                    |  |  |  |

| C1          | SDA       | I/O                | I <sup>2</sup> C serial interface data input/output |  |  |  |

| C2          | SCL       | I                  | I <sup>2</sup> C serial interface clock             |  |  |  |

| C3          | EN/VCC    | Р                  | Enable/Logic power supply                           |  |  |  |

| C4          | R         | А                  | LED driver current sink terminal                    |  |  |  |

(1) A: Analog; G: Ground; P: Power pin; I: Input pin; I/O: Input/Output pin; O: Output pin.

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                        | MIN  | MAX                                | UNIT |

|--------------------------------------------------------|------|------------------------------------|------|

| V (V <sub>DD</sub> , V <sub>EN/VCC</sub> , R, G, B, W) | -0.3 | 6                                  | V    |

| Voltage on pins                                        | -0.3 | V <sub>DD</sub> + 0.3 with 6-V max | V    |

| Continuous power dissipation <sup>(2)</sup>            |      | Internally limited                 |      |

| Junction temperature, T <sub>J-MAX</sub>               |      | 125                                | °C   |

| Maximum lead temperature (soldering)                   |      | See <sup>(3)</sup>                 |      |

| Storage temperature, T <sub>stg</sub>                  | -65  | 150                                | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typical) and disengages at T<sub>J</sub> = 130°C (typical).

(3) For detailed soldering specifications and information, please refer to Texas Instruments Application Note AN-1112 : DSBGA Wafer Level Chip Scale Package (SNVA009).

#### 6.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                   | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left(2\right)}$ | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                    | MIN  | NOM MAX         | UNIT |

|----------------------------------------------------|------|-----------------|------|

| V <sub>DD</sub>                                    | 2.7  | 5.5             | V    |

| V <sub>EN/VCC</sub>                                | 1.65 | V <sub>DD</sub> | V    |

| Junction temperature, T <sub>J</sub>               | -40  | 125             | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(1)</sup> | -40  | 85              | °C   |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

#### 6.4 Thermal Information

|                                                         | LP5562      |      |

|---------------------------------------------------------|-------------|------|

| THERMAL METRIC <sup>(1)</sup>                           | YQE (DSBGA) | UNIT |

|                                                         | 12 PINS     |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 68          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

Unless otherwise specified: limits for typical values are for  $T_A = 25^{\circ}C$  and minimum and maximum limits apply over the operating ambient temperature range (-40°C <  $T_A$  < +85°C);  $V_{IN} = 3.6V$ ,  $V_{ENVCC} = 1.8 \text{ V}$ .<sup>(1)(2)(3)</sup>

|                  | PARAMETER                                 | TEST CONDITIONS                                                                  | MIN | TYP  | MAX | UNIT |

|------------------|-------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| CURRENT          | CONSUMPTION AND OSCILLAT                  | OR ELECTRICAL CHARACTERISTICS                                                    |     |      |     |      |

|                  |                                           | EN = 0 (pin), CHIP_EN = 0 (bit), external 32<br>kHz clock running or not running |     | 0.2  | 2   | μA   |

|                  | Standby supply current                    | EN = 1 (pin), CHIP_EN = 0 (bit),<br>external 32 kHz clock not running            |     | 2    |     | μA   |

| I <sub>VDD</sub> |                                           | EN = 1 (pin), CHIP_EN = 0 (bit)<br>External 32-kHz clock running                 |     | 2.4  |     | μA   |

|                  |                                           | LED drivers disabled                                                             |     | 0.25 |     | mA   |

|                  | Normal mode supply current                | LED drivers enabled                                                              |     | 1    |     | mA   |

|                  | Powersave mode supply                     | External 32-kHz clock running                                                    |     | 10   |     | μA   |

|                  | current                                   | Internal oscillator running                                                      |     | 0.25 |     | mA   |

| _                | Internal oscillator frequency             | T <sub>A</sub> = 25°C                                                            | -4% |      | 4%  |      |

| fosc             | accuracy                                  |                                                                                  | -7% |      | 7%  |      |

| LED DRIVE        | ER ELECTRICAL CHARACTERIS                 | TICS (R, G, B, W OUTPUTS)                                                        |     |      |     |      |

| ILEAKAGE         | R, G, B, W pin leakage current            | T <sub>A</sub> = 25°C                                                            |     | 0.1  | 1   | μA   |

| I <sub>MAX</sub> | Maximum source current                    | Outputs R, G, B, W                                                               |     | 25.5 |     | mA   |

| I <sub>OUT</sub> | Accuracy of output current <sup>(4)</sup> | Output current set to 17.5 mA, $V_{DD} = 3.6 \text{ V}$<br>T <sub>A</sub> = 25°C | -4% |      | 4%  |      |

| 001              |                                           | Output current set to 17.5 mA, V <sub>DD</sub> = 3.6 V                           | -5% |      | 5%  |      |

| IMATCH           | Matching <sup>(4)</sup>                   | Output current set to 17.5 mA, V <sub>DD</sub> = 3.6V                            |     | 1%   | 2%  |      |

|                  |                                           | PWM_HF = 1                                                                       |     | 558  |     |      |

| fled             | LED PWM switching frequency               | $PWM_HF = 0$                                                                     |     | 256  |     | Hz   |

| V <sub>SAT</sub> | Saturation voltage <sup>(5)</sup>         | Output current set to 17.5 mA $T_A = 25^{\circ}C$                                |     | 60   | 100 | mV   |

(1) The electrical characteristics tables list ensured specifications under the listed recommended conditions except as otherwise modified or specified by the electrical characteristics test conditions and/or notes. Typical specifications are estimations only and are not verified by production testing.

(2) All voltages are with respect to the potential at the GND pins.

(3) Minimum and maximum limits are ensured by design, test, or statistical analysis. Typical numbers are not verified by production, but do represent the most likely norm.

(4) Output current accuracy is the difference between the actual value of the output current and programmed value of this current. Matching is the maximum difference from the average. For the constant current outputs on the part, the following are determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of all outputs (AVG). Two matching numbers are calculated: (MAX – AVG)/AVG and (AVG – MIN)/AVG. The largest number of the two (worst case) is considered the matching figure. Note that some manufacturers have different definitions in use.

(5) Saturation voltage is defined as the voltage when the LED current has dropped 10% from the set value.

#### 6.6 Logic Interface Characteristics

Unless otherwise specified: limits for typical values are for  $T_A = 25^{\circ}C$  and minimum and maximum limits apply over the operating ambient temperature range (-40°C <  $T_A$  < +85°C);  $V_{EN} = 1.65$  V.

|                    | PARAMETER                   | TEST CONDITIONS                          | MIN                 | TYP | MAX                 | UNIT |

|--------------------|-----------------------------|------------------------------------------|---------------------|-----|---------------------|------|

| LOGIC INF          | PUT EN                      |                                          |                     |     |                     |      |

| V <sub>IL</sub>    | Input low level             |                                          |                     |     | 0.5                 | V    |

| V <sub>IH</sub>    | Input high level            |                                          | 1.2                 |     |                     | V    |

| l <sub>l</sub>     | Logic input current         |                                          | -1                  |     | 1                   | μA   |

| t <sub>DELAY</sub> | Input delay <sup>(1)</sup>  |                                          |                     | 2   |                     | μs   |

| LOGIC INF          | UT SCL, SDA, CLK_32K, ADDR_ | SEL0, ADDR_SEL1, V <sub>EN</sub> = 1.8 V |                     |     |                     |      |

| V <sub>IL</sub>    | Input low level             |                                          |                     |     | $0.2 \times V_{EN}$ | V    |

| V <sub>IH</sub>    | Input high level            |                                          | $0.8 \times V_{EN}$ |     |                     | V    |

| l <sub>l</sub>     | Input current               |                                          | -1                  |     | 1                   | μA   |

| fclk_32к           | Clock frequency             |                                          |                     | 32  |                     | kHz  |

| fscl               | Clock frequency             |                                          |                     |     | 400                 | kHz  |

| LOGIC OU           | TPUT SDA                    | · · · · · · · · · · · · · · · · · · ·    |                     |     |                     |      |

| V <sub>OL</sub>    | Output low level            | I <sub>OUT</sub> = 3 mA (pullup current) |                     | 0.3 | 0.5                 | V    |

| IL                 | Output leakage current      |                                          |                     |     | 1                   | μA   |

(1) The I<sup>2</sup>C host should allow at least 1ms before sending data to the LP5562 after the rising edge of the enable line.

#### 6.7 Recommended External Clock Source Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                     | PARAMETER       | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |  |  |  |

|---------------------|-----------------|-----------------|-----|------|-----|------|--|--|--|

| LOGIC INPUT CLK_32K |                 |                 |     |      |     |      |  |  |  |

| $f_{CLK\_32K}$      | Clock frequency |                 |     | 32.7 |     | kHz  |  |  |  |

| t <sub>CLKH</sub>   | High time       |                 | 6   |      |     | μs   |  |  |  |

| t <sub>CLKL</sub>   | Low time        |                 | 6   |      |     | μs   |  |  |  |

| t <sub>r</sub>      | Clock rise time | 10% to 90%      |     |      | 2   | μs   |  |  |  |

| t <sub>f</sub>      | Clock fall time | 90% to 10%      |     |      | 2   | μs   |  |  |  |

Specification is ensured by design and is not tested in production. V<sub>EN</sub> = 1.65 V to V<sub>DD</sub>.

The ideal external clock signal for the LP5562 is a 0 V to V<sub>EN</sub> 25% to 75% duty-cycle square wave. At frequencies above 32.7 kHz, program execution will be faster and at frequencies below 32.7 kHz program execution will be slower.

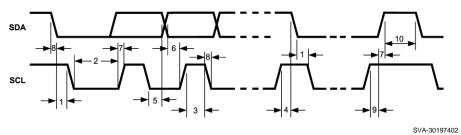

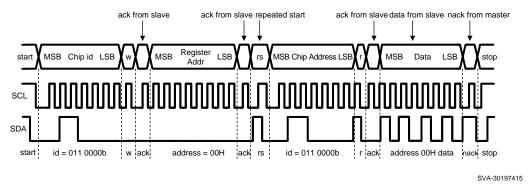

# 6.8 I<sup>2</sup>C Timing Requirements (SDA, SCL)

| See <sup>(1)</sup> |

|--------------------|

|--------------------|

|      |                                                    | MIN        | MAX | UNIT |

|------|----------------------------------------------------|------------|-----|------|

| fscl | Clock frequency                                    |            | 400 | kHz  |

| 1    | Hold time (repeated) START condition               | 0.6        |     | μs   |

| 2    | Clock low time                                     | 1.3        |     | μs   |

| 3    | Clock high time                                    | 600        |     | ns   |

| 4    | Setup time for a repeated START condition          | 600        |     | ns   |

| 5    | Data hold time                                     | 50         |     | ns   |

| 6    | Data setup time                                    | 100        |     | ns   |

| 7    | Rise time of SDA and SCL                           | 20 + 0.1Cb | 300 | ns   |

| 8    | Fall time of SDA and SCL                           | 15 + 0.1Cb | 300 | ns   |

| 9    | Set-up time for STOP condition                     | 600        |     | ns   |

| 10   | Bus-free time between a STOP and a START condition | 1.3        |     | μs   |

| Cb   | Capacitive load for each bus line                  | 10         | 200 | pF   |

(1) Specification is ensured by design and is not tested in production.  $V_{EN} = 1.65$  V to  $V_{DD}$ .

90% 90% tCLKL 90% 90% 10% ViL 10% tr - tr SVA-30197417

Figure 1. External Clock Timing

Figure 2. I<sup>2</sup>C Timing Parameters

3VA-30

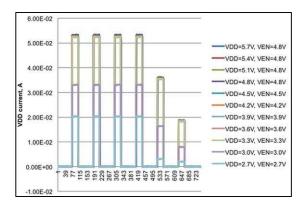

# 6.9 Typical Characteristics: Current Consumption

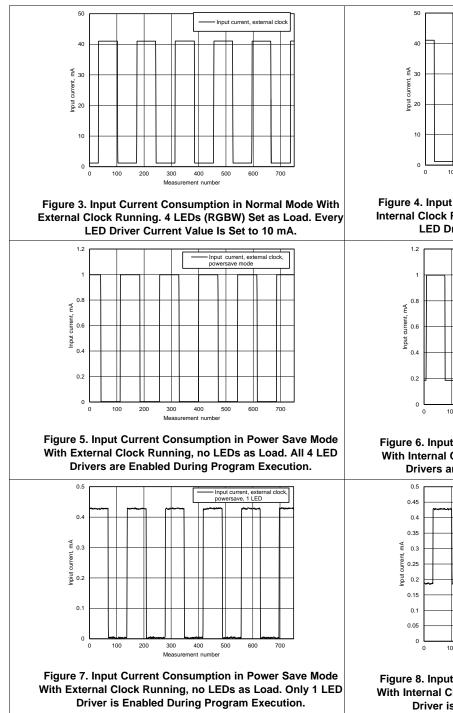

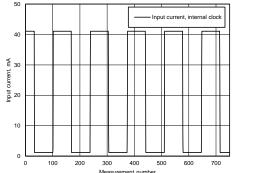

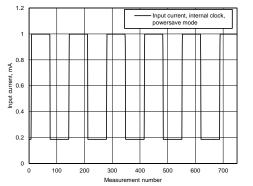

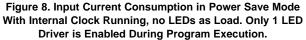

Unless otherwise specified:  $V_{DD} = 3.6 \text{ V}$ ,  $V_{EN} = 3.3 \text{ V}$ . Here are presented input current consumption measurements. Current consumption is measured during a LED blink program execution. Program code sets every LED output to full PWM value for 2 seconds and then PWM is set to 0 for 2 seconds. This is looped endlessly. 750 measurements are taken during one measurement cycle.

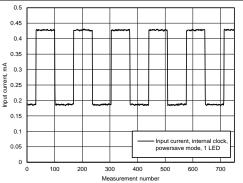

Figure 4. Input Current Consumption in Normal Mode With Internal Clock Running. 4 LEDs (RGBW) set as Load. Every LED Driver Current Value is Set to 10 mA.

Figure 6. Input Current Consumption in Power Save Mode With Internal Clock Running, no LEDs as Load. All 4 LED Drivers are Enabled During Program Execution.

8

# Typical Characteristics: Current Consumption (continued)

Unless otherwise specified:  $V_{DD} = 3.6 \text{ V}$ ,  $V_{EN} = 3.3 \text{ V}$ . Here are presented input current consumption measurements. Current consumption is measured during a LED blink program execution. Program code sets every LED output to full PWM value for 2 seconds and then PWM is set to 0 for 2 seconds. This is looped endlessly. 750 measurements are taken during one measurement cycle.

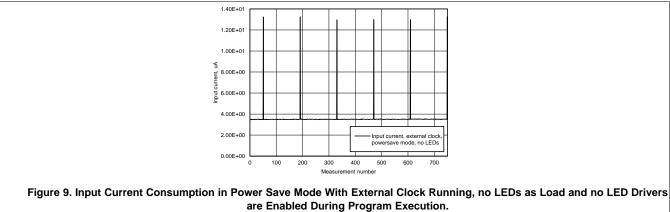

# 6.10 Typical Characteristics: LED Output

LED driver typical performance images.

#### 7 Detailed Description

#### 7.1 Overview

The LP5562 is a RGBW LED driver for indicator LED and keypad lighting. The device has an internal program memory for creating a variety of lighting sequences. When the program memory has been loaded, the LP5562 can operate independently without processor control.

The device has 4 LED drivers that are constant current sinks with 8-bit current and 8-bit PWM control. The current sinks can be controlled via the three execution engines or direct PWM control. The execution engines have five different functions used to build lighting sequences: Ramp, Set PWM, Go to Start, Branch, or End Trigger. These control methods and functions are explained in detail in *Feature Description* and *Device Functional Modes*.

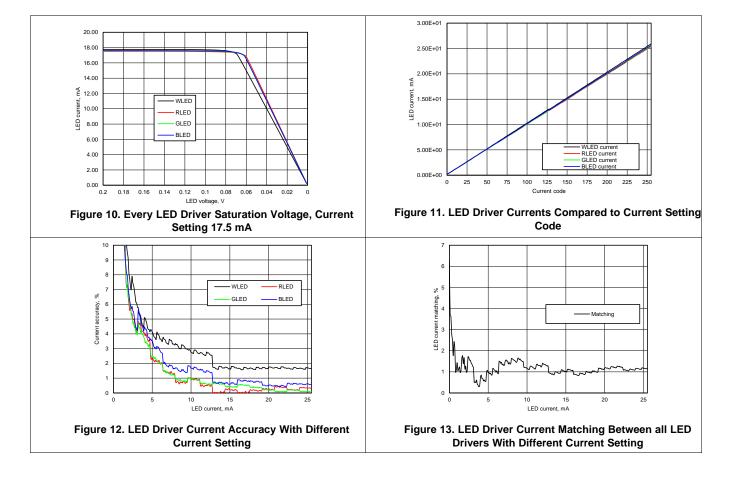

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 LED Drivers Operational Description

The LP5562 has 4 LED drivers that are constant current sinks with 8-bit current and 8-bit PWM control. Current is controlled from  $I^2C$  registers. PWM can be controlled with program execution engines or direct  $I^2C$  register writes.

#### 7.3.1.1 LED Driver Current Control

LED driver output current can be programmed with  $I^2C$  register from 0 mA up to 25.5 mA. Current setting resolution is 100  $\mu$ A (8-bit control).

| NAME    | BIT |                 | DESCR |     |            |

|---------|-----|-----------------|-------|-----|------------|

|         |     | CURRENT SETTING |       |     |            |

|         |     | bin             | hex   | dec | mA         |

|         |     | 0000 0000       | 00    | 0   | 0.0        |

|         |     | 0000 0001       | 01    | 1   | 0.1        |

|         |     | 0000 0010       | 02    | 2   | 0.2        |

|         |     | 0000 0011       | 03    | 3   | 0.3        |

|         |     | 0000 0100       | 04    | 4   | 0.4        |

|         |     | 0000 0101       | 05    | 5   | 0.5        |

| CURRENT | 7:0 | 0000 0110       | 06    | 6   | 0.6        |

|         |     |                 |       |     |            |

|         |     | 1010 1111       | AF    | 175 | 17.5 (def) |

|         |     |                 |       |     |            |

|         |     | 1111 1011       | FB    | 251 | 25.1       |

|         |     | 1111 1100       | FC    | 252 | 25.2       |

|         |     | 1111 1101       | FS    | 253 | 25.3       |

|         |     | 1111 1110       | FE    | 254 | 25.4       |

|         |     | 1111 1111       | FF    | 255 | 25.5       |

# Table 1. B\_CURRENT Register (05h), G\_CURRENT Register (06h), R\_CURRENT Register (06h), W CURRENT Register (07h)

#### 7.3.1.2 Controlling LED Driver Output PWM

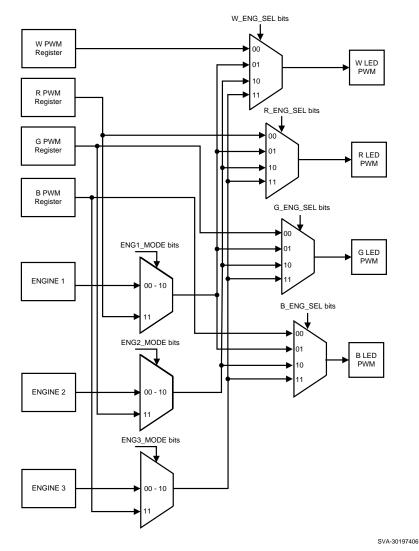

PWM can be controlled by either with program execution engines (1, 2 and 3) or via I<sup>2</sup>C registers (02h for B, 03h for G, 04h for R and 0Eh for W).

Control of LED driver output PWM selection is managed with 2 bits for each LED output from register 70h. The Table 3 describes the selection options. With these bits for example all LED outputs can be controlled from one program execution engine.

Figure 14. Controlling LED Outputs

The LED driver PWM control with 8-bit I<sup>2</sup>C register is defined in Table 2.

| NAME | BIT DESCRIPTION |                                                              |  |

|------|-----------------|--------------------------------------------------------------|--|

| PWM  | 7:0             | LED PWM value during I <sup>2</sup> C control operation mode |  |

|      |                 | 0000 0000 = 0% PWM                                           |  |

|      |                 | 1111 1111 = 100% PWM                                         |  |

If the LED driver outputs are controlled with engines, the engine adjusts the PWM according to the program code. However, when the engine *mode* bits are set to '11', the engine is set to *direct* mode. In *direct* mode the PWM controls of engines comes:

- Engine 1 PWM control comes from B PWM I<sup>2</sup>C register (02h)

- Engine 2 PWM control comes from G PWM I<sup>2</sup>C register (03h)

- Engine 3 PWM control comes from R PWM I<sup>2</sup>C register (04h)

When the engine *mode* bits are set to '11' along with the LED PWM Output selection bits, it is possible to control all LED outputs from one I<sup>2</sup>C register.

#### Table 3. LED PWM Output Selection Bits

| B_ENG_SEL bits[1:0]<br>G_ENG_SEL bits[3:2]<br>R_ENG_SEL bits[5:4]<br>W_ENG_SEL bits[7:6] | DESCRIPTION                                                                                  |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 00                                                                                       | Output is controlled via I <sup>2</sup> C registers                                          |

| 01                                                                                       | ENG1_MODE and ENG1_EXEC register control LED output PWM instead of I <sup>2</sup> C register |

| 10                                                                                       | ENG2_MODE and ENG2_EXEC register control LED output PWM instead of I <sup>2</sup> C register |

| 11                                                                                       | ENG3_MODE and ENG3_EXEC register control LED output PWM instead of I <sup>2</sup> C register |

#### 7.3.2 Direct I<sup>2</sup>C Register PWM Control Example

- Device Start-up

- Supply 3.6 V to VDD

- Supply 1.8 V to EN

- Wait 1 ms

- Write to address 00h 0100 0000b (chip\_en to '1')

- Wait 500 µs (start-up delay)

- Use internal clock

- Write to address 08h 0000 0001b (enable internal clock)

- Direct PWM control

- Write to address 70h 0000 0000b (Configure all LED outputs to be controlled from I<sup>2</sup>C registers)

- Write PWM values

- Write to address 02h 1000 0000b (B driver PWM 50% duty cycle)

- Write to address 03h 1100 0000b (G driver PWM 75% duty cycle)

- Write to address 04h 1111 1111b (R driver PWM 100% duty cycle)

LEDs are turned on after the PWM values are written. Changes to the PWM value registers are reflected immediately to the LED brightness. Default LED current (17.5 mA) is used for LED outputs, if no other values are written.

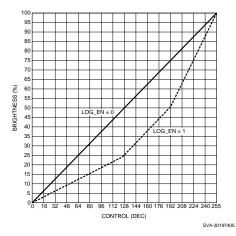

PWM frequency is either 256 Hz or 558 Hz. Frequency is set with PWM\_HF bit in register 08h. When PWM\_HF is 0, the frequency is 256 Hz. When the PWM\_HF bit is 1, the PWM frequency is 558 Hz. Brightness adjustment is either linear or logarithmic. This can be set with LOG\_EN bit in register 00h. When LOG\_EN = 0 linear adjustment scale is used and when LOG\_EN = 1 logarithmic scale is used. By using logarithmic scale the visual effect seems linear to the eye. Register control bits are presented in following tables:

| Table 4. ENABLE Register (00h) |  |

|--------------------------------|--|

|--------------------------------|--|

| NAME   | BIT | DESCRIPTION                           |

|--------|-----|---------------------------------------|

|        |     | Logarithmic PWM adjustment enable bit |

| LOG_EN |     | 0 = Linear adjustment                 |

|        |     | 1 = Logarithmic adjustment            |

#### Table 5. CONFIG Register (08h)

| NAME   | BIT | DESCRIPTION         |

|--------|-----|---------------------|

|        |     | PWM clock frequency |

| PWM_HF | 6   | 0 = 256 Hz          |

|        |     | 1 = 558 Hz          |

Figure 15. Logarithmic and Linear PWM Adjustment Curves

#### 7.3.3 Program Execution Engines

Use of program execution engines is the other LED output PWM control method available in the LP5562. The device has 3 program execution engines. These engines create PWM controlled lighting patterns to the mapped LED outputs according to program codes developed by the user. Program coding is done using programming commands (see *Program Execution Engine Programming Commands*.) Programs are loaded into SRAM memory and engine control bits are used to run these programs autonomously. LED outputs can be mapped into these 3 engines with register 70h bit settings (see Table 3). The engines have different operation modes, program execution states, and program counters. Each engine has its own section of the SRAM memory.

#### 7.3.3.1 Program Execution Engine States

Engine program execution is controlled from ENABLE register (00h). There are four different states for each engine, and these states are described in Table 6.

| NAME      | BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENG1_EXEC | 5:4 | Engine 1 program execution<br><b>Obb</b> = Hold: Wait until current command is finished then stop while<br>EXEC mode is hold. PC can be read or written only in this mode.<br><b>O1b</b> = Step: Execute instruction defined by current Engine 1 PC value,<br>increment PC, and change ENG1_EXEC to 00b (Hold).<br><b>10b</b> = Run: Start at program counter value defined by current Engine 1<br>PC value.<br><b>11b</b> = Execute instruction defined by current Engine 1 PC value and<br>change ENG1_EXEC to 00b (Hold).                                          |

| ENG2_EXEC | 3:2 | Engine 2 program execution<br><b>Obb</b> = Hold: Wait until current command is finished then stop while<br>EXEC mode is hold. PC can be read or written only in this mode.<br><b>O1b</b> = Step: Execute instruction defined by current Engine 2 PC value,<br>increment PC, and change ENG2_EXEC to 00b (Hold).<br><b>10b</b> = Run: Start at program counter value defined by current Engine 2<br>PC value.<br><b>11b</b> = Execute instruction defined by current Engine 2 PC value and<br>change ENG2_EXEC to 00b (Hold).                                          |

| ENG3_EXEC | 1:0 | <ul> <li>Engine 3 program execution</li> <li><b>00b</b> = Hold: Wait until current command is finished then stop while</li> <li>EXEC mode is hold. PC can be read or written only in this mode.</li> <li><b>01b</b> = Step: Execute instruction defined by current engine 3 PC value, increment PC, and change ENG3_EXEC to 00b (Hold).</li> <li><b>10b</b> = Run: Start at program counter value defined by current engine 3 PC value.</li> <li><b>11b</b> = Execute instruction defined by current engine 3 PC value and change ENG3_EXEC to 00b (Hold).</li> </ul> |

#### 7.3.3.2 Program Execution Engine Operation Modes

Operation modes are defined in register address 01h. Each engine (1, 2, 3) operation mode can be configured separately. *Mode* registers are synchronized to a 32-kHz clock. Delay between consecutive  $I^2C$  writes to OP\_MODE register (01h) need to be longer than 153 µs (typ).

| NAME      | BIT | DESCRIPTION                                                                                                                                                                                                                                                         |  |  |

|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ENG1_MODE | 5:4 | Engine 1 operation mode<br><b>00b</b> = Disabled, reset engine 1 PC<br><b>01b</b> = Load program to SRAM, reset engine 1 PC<br><b>10b</b> = Run program defined by ENG1_EXEC<br><b>11b</b> = Direct control from B PWM I <sup>2</sup> C register, reset engine 1 PC |  |  |

| ENG2_MODE | 3:2 | Engine 2 operation mode<br><b>00b</b> = Disabled, reset engine 2 PC<br><b>01b</b> = Load program to SRAM, reset engine 2 PC<br><b>10b</b> = Run program defined by ENG2_EXEC<br><b>11b</b> = Direct control from G PWM I <sup>2</sup> C register, reset engine 2 PC |  |  |

| ENG3_MODE | 1:0 | Engine 3 operation mode<br><b>00b</b> = Disabled, reset engine 3 PC<br><b>01b</b> = Load program to SRAM, reset engine 3 PC<br><b>10b</b> = Run program defined by ENG3_EXEC<br><b>11b</b> = Direct control from R PWM I <sup>2</sup> C register, reset engine 3 PC |  |  |

#### Table 7. Operation Mode Register (OP\_MODE (01h))

#### 7.3.3.2.1 Operation Modes

#### Disabled

Each channel can be configured to disabled mode. For the current engine mapped LED output brightness will be 0 during this mode. Disabled mode resets respective engine's PC.

#### Load program

- LP5562 can store 16 commands for each engine (1, 2, 3). Each command consists of 16 bits. Because one register has only 8 bits, one command requires two I<sup>2</sup>C register addresses. In order to reduce program load time the LP5562 supports address auto increment. Register address is incremented after each 8 data bits. The whole program memory can be written in one I<sup>2</sup>C write sequence. Program memory is defined in the LP5562 register table, from address 10h to address 2Fh for engine 1, from address 30h to address 4Fh for engine 2, and from address 50h to address 6Fh for engine 3. In order to access program memory at least one channel operation mode needs to be *load program*.

- SRAM memory writes are allowed only to the channel in *load program* mode. All engines are in hold while one or several engines are in *load program* mode, and PWM values are frozen for the engines which are not in *load program*mode. Program execution continues when all engines are out of *load program* mode. *Load program* mode resets respective engine's Program Counter (PC).

#### Run program

- Run program mode executes the commands defined in program memory for respective engine (1, 2, 3). Execution register bits in ENABLE register (00h) define how the program is executed. The program start position can be programmed to Program Counter register (see Table 8). By manually selecting the PC start value, user can write different lighting sequences to the SRAM memory, and select appropriate sequence with the PC register. If program counter runs to end (15), next command will be executed from program location 0. If internal clock is used in the *run program* mode, operation mode needs to be written disabled (00b) before disabling the chip (with CHIP\_EN bit or EN pin) to ensure that the sequence starts from the correct program counter (PC) value when restarting the sequence. PC registers are synchronized to 32 kHz clock. Delay between consecutive I<sup>2</sup>C writes to Program Counter (PC) registers (09h, 0Ah, 0Bh) need to be longer than 153µs (typ.).

- Execution registers are synchronized to 32kHz clock. Delay between consecutive I<sup>2</sup>C writes to ENABLE register (00h) need to be longer than 488µs (typ.).

- Note that entering LOAD program or Direct Control Mode from RUN PROGRAM mode is not allowed. Engine execution mode should be set to Hold, and Operation Mode to disabled, when changing operation mode from RUN mode.

#### Direct control

- In *Direct control* mode the engine PWM output is controlled by R, G and B PWM I<sup>2</sup>C registers.

- When engine 1 is in *Direct control* mode, the engine 1 PWM output is controlled by B PWM I<sup>2</sup>C register (02h).

- When engine 2 is in *Direct control* mode, the engine 2 PWM output is controlled by G PWM I<sup>2</sup>C register (03h).

- When engine 3 is in *Direct control* mode, the engine 3 PWM output is controlled by R PWM I<sup>2</sup>C register (04h).

#### 7.3.3.3 Program Execution Engine Program Counter (PC)

Program execution engine Program Counter tells the current program code command, which engine is executing. By setting the program counter value before starting the engine execution, user can set the starting point of the program execution.

#### Table 8. Engine1 PC Register (09h), Engine2 PC Register (0Ah), Engine3 PC Register (0Bh)

| NAME | BIT | DESCRIPTION                         |

|------|-----|-------------------------------------|

| PC   | 3:0 | Program counter value from 0 to 15d |

#### 7.3.3.4 Program Execution Engine Programming Commands

The LP5562 has three independent programmable engines (1, 2, 3). Trigger connections between engines are common for all engines. All engines have own program memory sections for storing LED lighting patterns. Brightness control and patterns are done with 8-bit PWM control (256 steps) to get accurate and smooth color control. Program execution is timed with a 32.7-kHz clock. This clock can be generated internally or an external 32-kHz clock can be connected to the CLK\_32K pin. Using an external clock enables synchronization of LED timing to this clock rather than an internal clock. Selection of the clock is made with address 08H bits INT\_CLK\_EN and CLK\_DET\_EN. See *External Clock* for details. Supported commands are listed in Table 9.

# Table 9. LED Controller Programming Commands<sup>(1)</sup>

|             |    |               |    |     |              |      | 5        | 5                     |                                                          |   |   |         |            |           |     |   |

|-------------|----|---------------|----|-----|--------------|------|----------|-----------------------|----------------------------------------------------------|---|---|---------|------------|-----------|-----|---|

| Command     | 15 | 14            | 13 | 12  | 12 11 10 9 8 |      |          |                       |                                                          | 6 | 5 | 4       | 3          | 2         | 1   | 0 |

| RampWait    | 0  | Pre-<br>scale |    |     | Step         | time |          |                       | Sign                                                     |   |   | Increme | nt (number | of steps) |     |   |

| Set PWM     | 0  | 1             |    |     |              | 0    |          |                       |                                                          |   |   | PWM     | Value      |           |     |   |

| Go to Start | 0  | 0             |    |     | (            | 0    |          |                       | 0                                                        | 0 | 0 | 0       | 0          | 0         | 0   | 0 |

| Branch      | 1  | 0             | 1  |     |              | Loop | count    |                       |                                                          | х |   | S       | tep / comm | nand numb | ber |   |

| End         | 1  | 1             | 0  | Int | Reset        |      |          |                       |                                                          |   | Х |         |            |           |     |   |

| Trigger     | 1  | 1             | 1  | x   | х            | x    | Wait for | trigger on<br>1, 2, 3 | er on engines X X X Send trigger to engines 1,2,<br>2, 3 |   |   |         | х          |           |     |   |

(1) X means do not care whether 1 or 0.

#### 7.3.3.4.1 Ramp/Wait

The ramp command generates a PWM ramp starting from current value. At each ramp step the output is incremented by one. Time for one step is defined with Prescale and Step time bits. Minimum time for one step is 0.49 ms and maximum time is  $63 \times 15.6$  ms = 1 second/step, so it is possible to program very fast and also very slow ramps. Increment value defines how many steps are taken in one command. Number of actual steps is Increment + 1. Maximum value is 127d, which corresponds to half of full-scale (128 steps). If during ramp command PWM reaches minimum/maximum (0/255) ramp command will be executed to the end and PWM will stay at minimum/maximum. This enables the ramp command to be used as combined ramp and wait command in a single instruction.

The ramp command can be used as wait instruction when increment is zero.

Setting register 00h bit LOG\_EN sets the scale as either linear to logarithmic. When LOG\_EN = 0, linear scale is used, and when LOG\_EN = 1, logarithmic scale is used. By using logarithmic scale the visual effect of the ramp command seems linear to the eye.

| Ramp/\ | Wait com      | mand |           |    |    |   |   |   |   |   |   |          |   |   |   |

|--------|---------------|------|-----------|----|----|---|---|---|---|---|---|----------|---|---|---|

| 15     | 14            | 13   | 12        | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

| 0      | Pre-<br>scale |      | Step time |    |    |   |   |   |   |   |   | Incremen | t |   |   |

Table 11. Ramp/Wait Command Bits

#### Table 10. Ramp/Wait Command

| NAME      | VALUE(d) | DESCRIPTION                                                                                    |

|-----------|----------|------------------------------------------------------------------------------------------------|

| Drocoolo  | 0        | Divides master clock (32.768 Hz) by 16 = 2048 Hz, 0.49 ms cycle time                           |

| Prescale  | 1        | Divides master clock (32.768 Hz) by 512 = 64 Hz, 15.6 ms cycle time                            |

| Step time | 1-63     | One ramp increment done in (step time) x (clock after prescale) Note: 0 means set PMW command. |

| Circa.    | 0        | Increase PWM output                                                                            |

| Sign      | 1        | Decrease PWM output                                                                            |

| Increment | 0-127    | The number of steps is Increment + 1. Note: 0 is a wait instruction.                           |

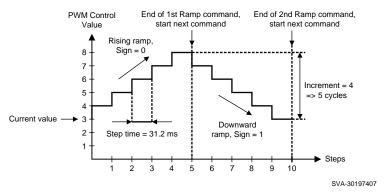

For example, if following parameters are used for ramp:

- Prescale = 1 ≥ cycle time = 15.6 ms

- Step time = 2 ≥ time = 15.6 ms × 2 = 31.2 ms

- Sign =  $0 \ge$  rising ramp Increment =  $4 \ge 5$  cycles

Ramp command will be: 0100 0010 0000 0100b = 4204h

If current PWM value is 3, and the first command is as described above, the next command is a ramp with otherwise same the parameters, but with Sign = 1 (Command = 4284h), the result will be like in the following figure:

#### 7.3.3.4.2 Set PWM

Set PWM output value from 0 to 255. Command takes sixteen 32-kHz clock cycles (= 488 µs). Setting register 00h bit LOG\_EN sets the scale from linear to logarithmic.

| Table 12. S | Set PWM | Command Bits |  |

|-------------|---------|--------------|--|

|-------------|---------|--------------|--|

| Set PW | M comm | and |    |    |    |   |   |   |   |   |     |       |   |   |   |

|--------|--------|-----|----|----|----|---|---|---|---|---|-----|-------|---|---|---|

| 15     | 14     | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3     | 2 | 1 | 0 |

| 0      | 1      | 0   | 0  | 0  | 0  | 0 | 0 |   |   |   | PWM | value |   |   |   |

#### 7.3.3.4.3 Go-to-Start

Go-to-start command resets the Program Counter register and continues executing program from the 00h location. Command takes sixteen 32-kHz clock cycles. Note that default value for all program memory registers is 0000h, which is Go-to-Start command.

| Table 13. Go-to-Start | Command Bits |

|-----------------------|--------------|

|-----------------------|--------------|

| Go-to-S | Start com | mand |    |    |    |   |   |   |   |   |   |   |   |   |   |

|---------|-----------|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 15      | 14        | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0       | 0         | 0    | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### 7.3.3.4.4 Branch

When branch command is executed, the 'step number' value is loaded to PC, and program execution continues from this location. Looping is done by the number defined in loop count parameter. Nested looping is supported (loop inside loop). The number of nested loops is not limited. Command takes sixteen 32-kHz clock cycles.

#### Table 14. Branch Command <sup>(1)</sup>

| Branch | comma | nd |    |            |    |   |   |   |   |   |   |   |        |       |   |

|--------|-------|----|----|------------|----|---|---|---|---|---|---|---|--------|-------|---|

| 15     | 14    | 13 | 12 | 11         | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2      | 1     | 0 |

| 1      | 0     | 1  |    | Loop count |    |   |   |   |   | Х | Х |   | Step n | umber |   |

(1) X means do not care whether 1 or 0

#### **Table 15. Branch Command Bits**

| NAME        | VALUE | DESCRIPTION                                            |

|-------------|-------|--------------------------------------------------------|

| loop count  | 0-63  | The number of loops to be done. 0 means infinite loop. |

| step number | 0-15  | The step number to be loaded to program counter.       |

#### 7.3.3.4.5 End

End program execution resets the program counter and sets the corresponding EXEC register to 00b (hold). Command takes sixteen 32 kHz clock cycles.

#### Table 16. End Command <sup>(1)</sup>

| End co | ommand |    |     |       |    |   |   |   |   |   |   |   |   |   |   |

|--------|--------|----|-----|-------|----|---|---|---|---|---|---|---|---|---|---|

| 15     | 14     | 13 | 12  | 11    | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1      | 1      | 0  | int | reset | Х  | Х | Х | Х | Х | Х | Х | Х | Х | Х | Х |

(1) X means do not care whether 1 or 0.

#### Table 17. End Command Bits

| NAME | VALUE | DESCRIPTION                                                                                                                                                                      |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 0     | No interrupt will be sent.                                                                                                                                                       |

| int  | 1     | Send interrupt by setting corresponding status register bit high to<br>notify that program has ended. Interrupt can only be cleared by<br>reading interrupt status register 0Ch. |

TEXAS INSTRUMENTS

www.ti.com

#### Table 17. End Command Bits (continued)

| NAME  | VALUE | DESCRIPTION                 |

|-------|-------|-----------------------------|

| rooot | 0     | Keep the current PWM value. |

| reset | 1     | Set PWM value to 0.         |

#### 7.3.3.4.6 Trigger

Wait or send triggers can be used to synchronize operation between different engines. The send-trigger command takes sixteen 32-kHz clock cycles; the wait-for-trigger command takes at least sixteen 32-kHz clock cycles. The receiving engine stores sent triggers. Received triggers are cleared by wait for trigger command if received triggers match to engines defined in the command. Engine waits until all defined triggers have been received.

#### Table 18. Trigger Command<sup>(1)</sup>

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8         | 7     | 6 | 5 | 4 | 3    | 2           | 1     | 0 |

|----|----|----|----|----|----|------|-----------|-------|---|---|---|------|-------------|-------|---|

| 1  | 1  | 1  | Х  | Х  | Х  | wait | trigger < | :2:0> | Х | Х | Х | senc | l trigger < | <2:0> | Х |

|    |    |    |    |    |    | ENG3 | ENG2      | ENG1  |   |   |   | ENG3 | ENG2        | ENG1  |   |

(1) X means do not care whether 1 or 0.

| Table | 19. | Triager    | Command Bits |

|-------|-----|------------|--------------|

| Tuble |     | i i i ggei |              |

| NAME                 | VALUE(d) | DESCRIPTION                                                                                                                                              |  |  |  |  |  |

|----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| wait<br>trigger<2:0> | 0-7      | Wait for trigger for the engine(s) defined. Several triggers can be defined in the same command. Bit 0 is engine 1, bit 1 is engine2, bit 2 is engine 3. |  |  |  |  |  |

| send<br>trigger<2:0> | 0-7      | Send trigger for the engine(s) defined. Several triggers can be defined in the same command. Bit 0 is engine 1, bit 1 is engine2, bit 2 is engine 3.     |  |  |  |  |  |

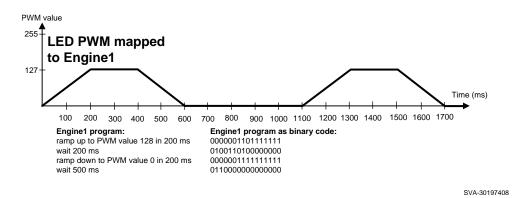

#### 7.3.3.5 Program Load and Execution Example

- Start up device and configure device to SRAM write mode

- Supply 3.6V to VDD

- Supply 1.8V to EN

- Wait 1 ms

- Generate 32 kHz clock to CLK\_32K pin

- Write to address 00h 0100 0000b (enable device)

- Wait 500 µs (startup delay)

- Write to address 01h 0001 0000b (configure engine 1 into 'Load program to SRAM' mode)

- Program load to SRAM

- Write to address 10h 0000 0011b (1st ramp command 8MSB)

- Write to address 11h 0111 1111b (1st ramp command 8 LSB)

- Write to address 12h 0100 1101b (1st wait command 8 MSB)

- Write to address 13h 0000 0000b (1st wait command 8 LSB)

- Write to address 14h 0000 0011b (2nd ramp command 8 MSB)

- Write to address 15h 1111 1111b (2nd ramp command 8 LSB)

- Write to address 16h 0110 0000b (2nd wait command 8 MSB)

- Write to address 17h 0000 0000b (2nd wait command 8 LSB)

- Enable Power Save and use external 32 kHz clock

- Write to address 08h 0010 0000b (enable powersave, use external clock)

- Run program

- Write to address 01h 0010 0000b (Configure LED controller operation mode to "Run program" in engine 1)

- Write to address 00h 0110 0000b (Configure program execution mode from "Hold" to "Run" in engine 1)

The LP5562 will generate a 1100 ms long LED pattern which will be repeated infinitely. The LED pattern is illustrated in the figure below.

#### 7.3.4 Power-Save Mode

Automatic power save mode is enabled when the PS\_EN bit in register address 08h is 1. Almost all analog blocks are powered down in power save, if an external clock is used. However, if an internal clock has been selected, only the LED drivers are disabled during power save since the digital part of the LED controller need to remain active. During program execution the LP5562 can enter power-save mode if there is no PWM activity in engine controlled outputs. To prevent short power-save sequences during program execution, the LP5562 has a command look-ahead filter. In each instruction cycle every engine commands are analyzed, and if there is sufficient time left with no PWM activity, the device will enter power save. In power save program execution continues uninterruptedly. When a command that requires PWM activity is executed, fast internal startup sequence will be started automatically. The following tables describe commands and conditions that can activate power save. All engines need to meet power-save conditions in order to enable power save.

| ENGINE OPERATION<br>MODE             | POWER SAVE CONDITION                                                                                            |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| 00b Disabled mode enables power save |                                                                                                                 |  |

| 01b                                  | Load program to SRAM mode prevents power save.                                                                  |  |

| 10b                                  | Run program mode enables power save if there is no PWM activity and command look-ahead filter condition is met. |  |

| 11b                                  | Direct control mode enables power save if there is no PWM activity.                                             |  |

#### Table 20. Engine Operation Mode and Power Save

| COMMAND        | POWER SAVE CONDITION                                                                                                                                          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait           | No PWM activity and current command wait time longer than 50 ms. If prescale = 1 then wait time needs to be longer than 80 ms.                                |

| Ramp           | Ramp command PWM value reaches minimum 0 and current command execution time left more than 50 ms. If prescale = 1 then time left needs to be more than 80 ms. |

| Trigger        | No PWM activity during wait for trigger command execution.                                                                                                    |

| End            | No PWM activity or Reset bit = 1.                                                                                                                             |

| Set PWM        | Enables power save if PWM set to 0 and next command generates at least 50 ms wait.                                                                            |

| Other commands | No effect to power save.                                                                                                                                      |

#### 7.3.5 External Clock

The presence of an external clock can be detected by the LP5562. Program execution is clocked with an internal 32-kHz clock or with an external clock. Clocking is controlled with register address 08h bits, INT\_CLK\_EN, and CLK\_DET\_EN as seen in Table 22.

An external clock can be used if clock is present at the CLK\_32K pin. The external clock frequency must be 32 kHz for the program execution PWM timing to be as specified. If higher or lower frequency is used, it will affect the program engine execution speed. If a clock frequency other than 32 kHz is used, the program execution timings must be scaled accordingly.

The LP5562 has automatic external clock detection. The external clock detector block only detects too low clock frequency (< 4 kHz), but it is recommended not to use external clock below 20 kHz. If external clock frequency is higher than specified, the external clock detector notifies that external clock is present. External clock status can be checked with read only bit EXT\_CLK\_USED in register address 0Ch, when the external clock detection is enabled (CLK\_DET\_EN bit = high). If EXT\_CLK\_USED = 1, then the external clock is detected and it is used for timing, if automatic clock selection is enabled.

If an external clock is stuck-at-zero or stuck-at-one, or the clock frequency is too low, the clock detector indicates that external clock is not present.

If an external clock is not used on the application, CLK\_32K pin should be connected to GND to prevent floating of this pin and extra current consumption.

| NAME                      | BIT | DESCRIPTION                                                                                                                                       |

|---------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_DET_EN,<br>INT_CLK_EN | 1:0 | LED Controller clock source<br>00b = External clock source (CLK_32K)<br>01b = Internal clock<br>10b = Automatic selection<br>11b = Internal clock |

#### Table 22. CONFIG Register (08h)

#### 7.3.6 Thermal Shutdown

If the LP5562 reaches thermal shutdown temperature (150°C typical) the device operation is disabled and the device state is in STARTUP mode, until no thermal shutdown event is present. Device will enter Normal mode when temperature drops below 130°C (typical) degrees.

Fault is cleared when thermal shutdown disappears.

#### 7.3.7 Logic Interface Operational Description

The LP5562 features a flexible logic interface for connecting to processor and peripheral devices. Communication is done with the l<sup>2</sup>C-compatible interface, and different logic input/output pins makes it possible to synchronize operation of several devices.

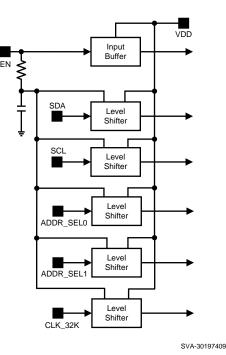

#### 7.3.8 I/O Levels

I<sup>2</sup>C interface, CLK\_32K. ADDR\_SEL0, and ADDR\_SEL1 pins input levels are defined by voltage in EN pin. Using the EN pin as a voltage reference for logic inputs simplifies PCB routing and eliminates the need for a dedicated VIO pin. The following block diagram describes EN pin connections.

Figure 18. Using EN Pin as Digital I/O Voltage Reference

#### 7.3.9 ADDR\_SEL0, ADDR\_SEL1 Pins

The ADDR\_SEL0 and ADDR\_SEL1 pins define the device I<sup>2</sup>C address. Pins are referenced to EN pin signal level. See I<sup>2</sup>C Addresses for I<sup>2</sup>C address definitions.

#### 7.3.10 CLK\_32 Pin

The CLK\_32K pin is used for connecting an external 32-kHz clock to LP5562. An external clock can be used to synchronize the sequence engines of several LP5562 devices. Using an external clock can also improve automatic power save mode efficiency, because an internal clock can be switched off automatically when device has entered power-save mode, and an external clock is present. Device can be used without the external clock. If external clock is not used on the application, the CLK\_32K pin should be connected to GND to prevent floating of this pin and extra current consumption.

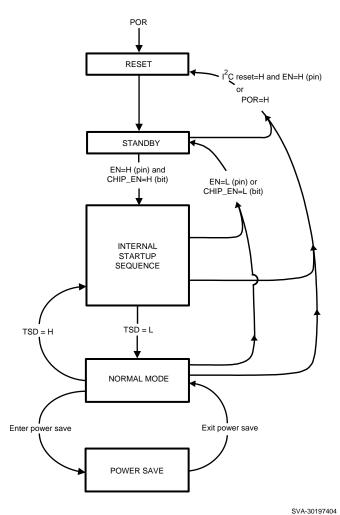

#### 7.4 Device Functional Modes

- **RESET:** In the *reset* mode all the internal registers are reset to the default values. Reset is done always if FFh is written to Reset Register (0Dh) or internal Power On Reset is activated. Power On Reset (POR) will activate when supply voltage is connected or when the supply voltage V<sub>DD</sub> falls below 1.5 V (typical). Once V<sub>DD</sub> rises above 1.9 V (typical), POR will inactivate and the chip will continue to the *standby* mode. CHIP\_EN control bit is low after POR by default.

- **STANDBY:** The *standby* mode is entered if the register bit CHIP\_EN or EN pin is *low* and Reset is not active. This is the low power consumption mode, when all circuit functions are disabled. Registers can be written in this mode if EN pin is high. Control bits are effective after start up.

- START-UP: When CHIP\_EN bit is written high and EN pin is high, the *internal startup sequence* powers up all the needed internal blocks (VREF, Bias, Oscillator etc.). Start-up delay after setting EN pin *high* is 1 ms (typical). Start-up delay after setting chip\_en bit to '1' is 500 μs (typical). If the device temperature rises too high, the Thermal Shutdown (TSD) disables the device operation and the device state is in *start-up* mode, until no thermal shutdown event is present.

- **NORMAL:** During *normal* mode the user controls the device using the Control Registers. If EN pin is set low, the CHIP\_EN bit is reset to 0.

TEXAS INSTRUMENTS

www.ti.com

#### **Device Functional Modes (continued)**

**POWER** In *power save* mode analog blocks are disabled to minimize power consumption. See *Power-Save* **SAVE:** *Mode* for further information.

Figure 19. Modes of Operation

#### 7.5 Programming

#### 7.5.1 SRAM Memory

In the LP5562 there is a SRAM memory reserved for storing the LED lighting programs. Each engine has its own section of the memory so that engine 1 has registers 10h to 2Fh, engine 2 has registers 30h to 4Fh, and engine 3 has registers 50h to 6Fh. For each engine 16 engine commands (16-bit) can be stored. Each 16-bit command takes up two I<sup>2</sup>C registers.

|         | _                |                      |                     |      |          |              |      |      |      |

|---------|------------------|----------------------|---------------------|------|----------|--------------|------|------|------|

| Address | Register         | Bit7                 | Bit6                | Bit5 | Bit4     | Bit3         | Bit2 | Bit1 | Bit0 |

| 10h     | Prog mem<br>ENG1 |                      | COMMAND1_ENG1[15:8] |      |          |              |      |      |      |

| 11h     | Prog mem<br>ENG1 |                      | COMMAND1_ENG1[7:0]  |      |          |              |      |      |      |

|         |                  |                      |                     |      |          |              |      |      |      |

| 2Eh     | Prog mem<br>ENG1 |                      |                     |      | COMMAND1 | 6_ENG1[15:8] |      |      |      |

| 2Fh     | Prog mem<br>ENG1 |                      |                     |      | COMMAND1 | 6_ENG1[7:0]  |      |      |      |

| 30h     | Prog mem<br>ENG2 |                      | COMMAND1_ENG2[15:8] |      |          |              |      |      |      |

| 31h     | Prog mem<br>ENG2 | COMMAND1_ENG2[7:0]   |                     |      |          |              |      |      |      |

|         |                  |                      |                     |      |          |              |      |      |      |

| 4Eh     | Prog mem<br>ENG2 | COMMAND16_ENG2[15:8] |                     |      |          |              |      |      |      |

| 4Fh     | Prog mem<br>ENG2 | COMMAND16_ENG2[7:0]  |                     |      |          |              |      |      |      |

| 50h     | Prog mem<br>ENG3 |                      | COMMAND1_ENG3[15:8] |      |          |              |      |      |      |

| 51h     | Prog mem<br>ENG3 | COMMAND1_ENG3[7:0]   |                     |      |          |              |      |      |      |

|         | · ·              |                      |                     |      |          |              |      |      |      |

| 6Eh     | Prog mem<br>ENG3 | COMMAND16_ENG3[15:8] |                     |      |          |              |      |      |      |

| 6Fh     | Prog mem<br>ENG3 |                      |                     |      | COMMAND1 | 6_ENG3[7:0]  |      |      |      |

When downloading a program to the SRAM engine modes need to be set to Load mode (see Table 6). While loading sequential I<sup>2</sup>C writing can be used (repeated start see Figure 24). However, please note that sequential read of the SRAM is not possible.

#### 7.5.2 I<sup>2</sup>C-Compatible Serial Bus Interface

#### 7.5.2.1 Interface Bus Overview

The I<sup>2</sup>C compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bidirectional communications between the IC's connected to the bus. The two interface lines are the Serial Data Line (SDA), and the Serial Clock Line (SCL). These lines should be connected to a positive supply, via a pullup resistor and remain HIGH even when the bus is idle.

Every device on the bus is assigned a unique address and acts as either a Master or a Slave depending on whether it generates or receives the serial clock (SCL).

LP5562

SNVS820A - APRIL 2013 - REVISED SEPTEMBER 2015

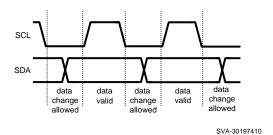

#### 7.5.2.2 Data Transactions

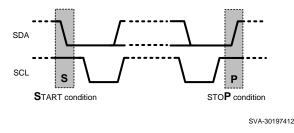

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Figure 20. Data Validity

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow. The following sections provide further details of this process.

SVA-30197411

Figure 21. Acknowledge Signal

The Master device on the bus always generates the Start and Stop Conditions (control codes). After a Start Condition is generated, the bus is considered busy and it retains this status until a certain time after a Stop Condition is generated. A high-to-low transition of the data line (SDA) while the clock (SCL) is high indicates a Start Condition. A low-to-high transition of the SDA line while the SCL is high indicates a Stop Condition.

Figure 22. Start and Stop Conditions

In addition to the first Start Condition, a repeated Start Condition can be generated in the middle of a transaction. This allows another device to be accessed, or a register read cycle.

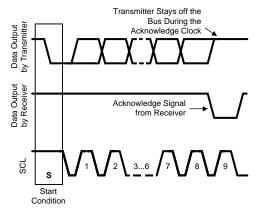

#### 7.5.2.3 Acknowledge Cycle

SNVS820A – APRIL 2013–REVISED SEPTEMBER 2015

LP5562

The Acknowledge Cycle consists of two signals: the acknowledge clock pulse the master sends with each byte transferred, and the acknowledge signal sent by the receiving device.

The master generates the acknowledge clock pulse on the ninth clock pulse of the byte transfer. The transmitter releases the SDA line (permits it to go high) to allow the receiver to send the acknowledge signal. The receiver must pull down the SDA line during the acknowledge clock pulse and ensure that SDA remains low during the high period of the clock pulse, thus signaling the correct reception of the last data byte and its readiness to receive the next byte.

#### 7.5.2.4 Acknowledge After Every Byte Rule

The master generates an acknowledge clock pulse after each byte transfer. The receiver sends an acknowledge signal after every byte received.

There is one exception to the "acknowledge after every byte" rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging ("negative acknowledge") the last byte clocked out of the slave. This "negative acknowledge" still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

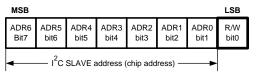

#### 7.5.2.5 Addressing Transfer Formats

Each device on the bus has a unique slave address. The LP5562 operates as a slave device with the 7-bit address. LP5562  $I^2C$  address is pin selectable from four different choices. If 8-bit address is used for programming, the 8th bit is 1 for read and 0 for write. Table 24 shows the 8-bit  $I^2C$  addresses.

| ADDR_SEL<br>[1:0] | I <sup>2</sup> C ADDRESS WRITE<br>(8 bits) | I <sup>2</sup> C ADDRESS READ<br>(8 bits) |

|-------------------|--------------------------------------------|-------------------------------------------|

| 00                | 0110 0000 = 60h                            | 0110 0001 = 61h                           |

| 01                | 0110 0010 = 62h                            | 0110 0011 = 63h                           |

| 10                | 0110 0100 = 64h                            | 0110 0101 = 65h                           |

| 11                | 0110 0110 = 66h                            | 0110 0111 = 67h                           |

#### Table 24. I<sup>2</sup>C Addresses

Before any data is transmitted, the master transmits the address of the slave being addressed.

The slave device should send an acknowledge signal on the SDA line, once it recognizes its address.

The slave address is the first seven bits after a Start Condition. The direction of the data transfer (R/W) depends on the bit sent after the slave address — the eighth bit.

When the slave address is sent, each device in the system compares this slave address with its own. If there is a match, the device considers itself addressed and sends an acknowledge signal. Depending upon the state of the R/W bit (1:read, 0:write), the device acts as a transmitter or a receiver.

SVA-30197413

#### Figure 23. I<sup>2</sup>C chip address

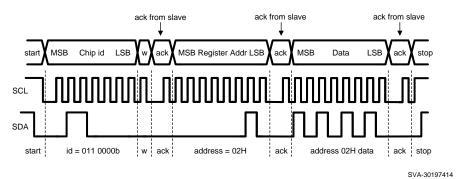

#### 7.5.2.6 Control Register Write Cycle

- Master device generates start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- · Master sends data byte to be written to the addressed register.

LP5562

SNVS820A - APRIL 2013-REVISED SEPTEMBER 2015

www.ti.com

- Slave sends acknowledge signal.

- If master will send further data bytes the control register address will be incremented by one after acknowledge signal.

- Write cycle ends when the master creates stop condition.

#### 7.5.2.7 Control Register Read Cycle

- Master device generates a start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master device generates repeated start condition.

- Master sends the slave address (7 bits) and the data direction bit (r/w = 1).

- Slave sends acknowledge signal if the slave address is correct.

- Slave sends data byte from addressed register.

- If the master device sends acknowledge signal, the control register address will be incremented by one. Slave device sends data byte from addressed register.

- Read cycle ends when the master does not generate acknowledge signal after data byte and generates stop condition.

|            | ADDRESS MODE                                               |

|------------|------------------------------------------------------------|

|            | <start condition=""></start>                               |

|            | <slave address=""><r w="0">[Ack]</r></slave>               |

|            | <register addr.="">[Ack]</register>                        |

| Data Read  | <repeated condition="" start=""></repeated>                |

| Dala Reau  | <slave address=""><r w="1">[Ack]</r></slave>               |

|            | [Register Data] <ack nack="" or=""></ack>                  |

|            | additional reads from subsequent register address possible |

|            | <stop condition=""></stop>                                 |

|            | <start condition=""></start>                               |

|            | <slave address=""><r w="0">[Ack]</r></slave>               |

| Data Write | <register addr.="">[Ack]</register>                        |

| Data White | <register data="">[Ack]</register>                         |

|            | additional writes to subsequent register address possible  |

|            | <stop condition=""></stop>                                 |

#### Table 25. I<sup>2</sup>C Data Read/Write Flow<sup>(1)</sup>

(1) <>Data from master [] Data from slave

#### 7.5.2.8 Register Read/Write Format

When a *read* function is to be accomplished, a *write* function must precede the *read* function, as show in the Read Cycle waveform.

Figure 25. Register Read Format

w = write (SDA = 0)

r = read (SDA = 1)

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = 7-bit chip address

# 7.6 Register Maps

| ADDR<br>(HEX) | REGISTER         | D7     | D6                                           | D5                               | D4    | D3               | D2       | D1         | D0          | DEFAULT   |  |  |

|---------------|------------------|--------|----------------------------------------------|----------------------------------|-------|------------------|----------|------------|-------------|-----------|--|--|

| 00            | ENABLE           | LOG_EN | CHIP_EN                                      | CHIP_EN ENG1_EXEC[1:0] ENG2_EXEC |       |                  |          | ENG3_E     | XEC[1:0]    | 0000 0000 |  |  |

| 01            | OP MODE          |        | ENG1_MODE[1:0] ENG2_MODE[1:0] ENG3_MODE[1:0] |                                  |       |                  |          |            |             | 0000 0000 |  |  |

| 02            | B PWM            |        | B_PWM[7:0]                                   |                                  |       |                  |          |            |             |           |  |  |

| 03            | G PWM            |        |                                              |                                  | G_    | PWM[7:0]         |          |            |             | 0000 0000 |  |  |

| 04            | R PWM            |        |                                              |                                  | R_    | PWM[7:0]         |          |            |             | 0000 0000 |  |  |

| 05            | B CURRENT        |        |                                              |                                  | B_CL  | JRRENT[7:0]      |          |            |             | 1010 1111 |  |  |