# LM5113 5A, 100V Half-Bridge Gate Driver for Enhancement Mode GaN FETs

Check for Samples: LM5113

### **FEATURES**

- Independent high-side and low-side TTL logic inputs

- 1.2A/5A peak source/sink current

- High-side floating bias voltage rail operates up to 100VDC

- Internal bootstrap supply voltage clamping

- Split outputs for adjustable turn-on/turn-off strength

- 0.6Ω /2.1Ω pull-down/pull-up resistance

- Fast propagation times (28ns typical)

- Excellent propagation delay matching (1.5ns typical)

- Supply rail under-voltage lockout

- Low power consumption

### TYPICAL APPLICATIONS

- Current Fed Push-Pull converters

- Half and Full-Bridge converters

- Synchronous Buck converters

- Two-switch Forward converters

- Forward with Active Clamp converters

#### DESCRIPTION

The LM5113 is designed to drive both the high-side and the low-side enhancement mode Gallium Nitride (GaN) FETs in a synchronous buck or a half bridge configuration. The floating high-side driver is capable of driving a high-side enhancement mode GaN FET operating up to 100V. The high-side bias voltage is generated using a bootstrap technique and is internally clamped at 5.2V, which prevents the gate voltage from exceeding the maximum gate-source voltage rating of enhancement mode GaN FETs. The inputs of the LM5113 are TTL logic compatible, and can withstand input voltages up to 14V regardless of the VDD voltage. The LM5113 has split gate outputs, providing flexibility to adjust the turn-on and turn-off strength independently.

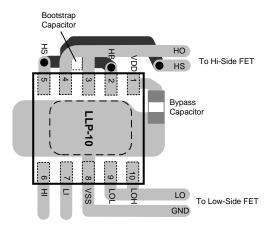

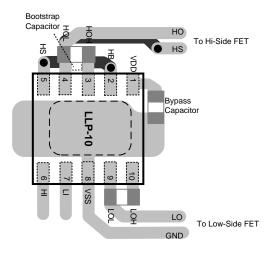

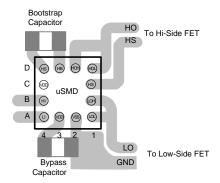

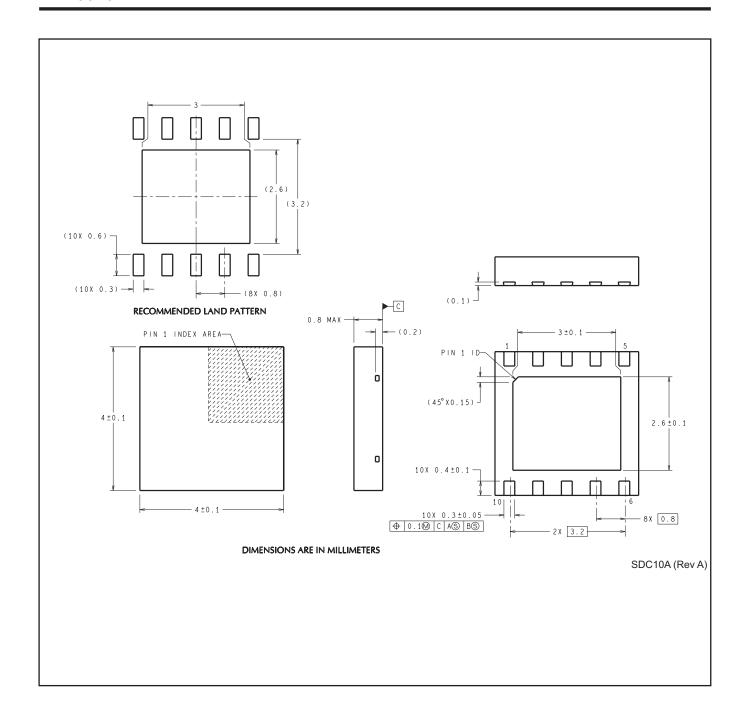

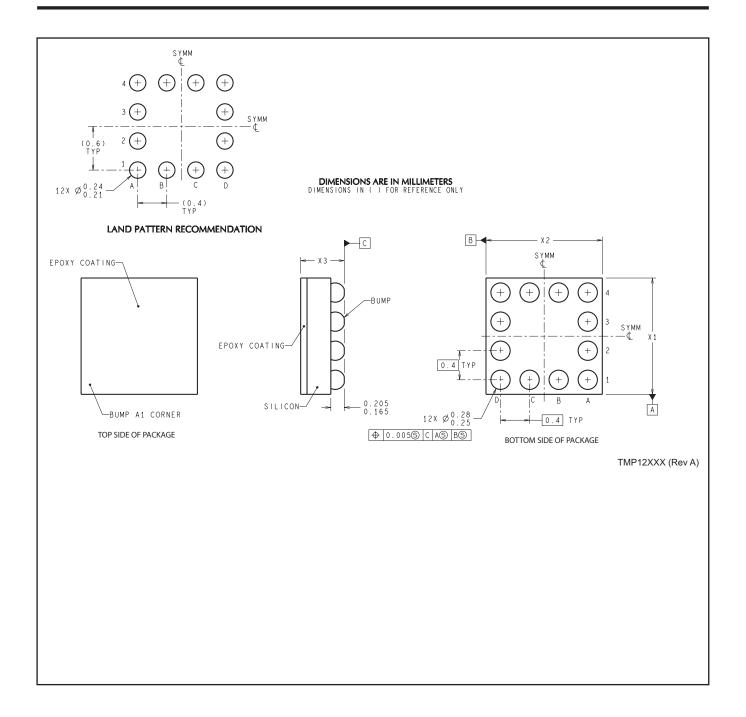

In addition, the strong sink capability of the LM5113 maintains the gate in the low state, preventing unintended turn-on during switching. The LM5113 can operate up to several MHz. The LM5113 is available in a standard LLP-10 pin package and a 12-bump micro SMD package. The LLP-10 pin package contains an exposed pad to aid power dissipation. The micro SMD package offers a compact footprint and minimized package inductance.

### **Packages**

- LLP-10 (4 mm x 4 mm)

- micro SMD (2 mm x 2 mm)

ATA.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

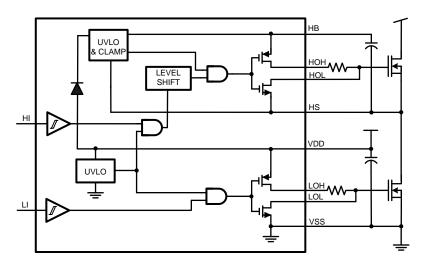

# **Typical Application**

Figure 1.

**Table 1. Truth Table**

| HI | LI | НОН  | HOL  | LOH  | LOL  |

|----|----|------|------|------|------|

| L  | L  | Open | L    | Open | L    |

| L  | Н  | Open | L    | Н    | Open |

| Н  | L  | Н    | Open | Open | L    |

| Н  | Н  | Н    | Open | Н    | Open |

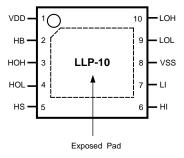

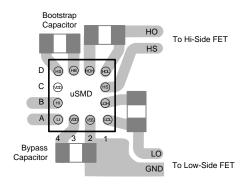

# **Connection Diagram**

Figure 2. micro SMD

**Table 2. Pin Descriptions**

| Pin Number            |        | Name | Description                                    | Applications Information                                                                                                                                                 |

|-----------------------|--------|------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| micro SMD             | LLP-10 |      |                                                |                                                                                                                                                                          |

| A3, C4 <sup>(1)</sup> | 1      | VDD  | 5V Positive gate drive supply                  | Locally decouple to VSS using low ESR/ESL capacitor located as close to the IC as possible.                                                                              |

| D3                    | 2      | НВ   | High-side gate driver bootstrap rail           | Connect the positive terminal of the bootstrap capacitor to HB and the negative terminal to HS. The bootstrap capacitor should be placed as close to the IC as possible. |

| D2                    | 3      | НОН  | High-side gate driver turn-on output           | Connect to the gate of high-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turn-on speed.                                     |

| D1                    | 4      | HOL  | High-side gate driver turn-off output          | Connect to the gate of high-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turn-off speed.                                    |

| C1, D4 <sup>(2)</sup> | 5      | HS   | High-side GaN FET source connection            | Connect to the bootstrap capacitor negative terminal and the source of the high-side GaN FET.                                                                            |

| B4                    | 6      | HI   | High-side driver control input                 | The LM5113 inputs have TTL type thresholds. Unused inputs should be tied to ground and not left open.                                                                    |

| A4                    | 7      | LI   | Low-side driver control input                  | The LM5113 inputs have TTL type thresholds. Unused inputs should be tied to ground and not left open.                                                                    |

| A2                    | 8      | VSS  | Ground return                                  | All signals are referenced to this ground.                                                                                                                               |

| A1                    | 9      | LOL  | Low-side gate driver sink-current output       | Connect to the gate of the low-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turn-off speed.                                 |

| B1                    | 10     | LOH  | Low-side gate driver source-<br>current output | Connect to the gate of high-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turn-on speed.                                     |

|                       | EP     |      | Exposed Pad                                    | It is recommended that the exposed pad on the bottom of the package be soldered to ground plane on the PC board to aid thermal dissipation.                              |

<sup>(1)</sup> A3 and C4, C1 and D4 are internally connected.

<sup>(2)</sup> A3 and C4, C1 and D4 are internally connected.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Copyright © 2011–2012, Texas Instruments Incorporated

# **Absolute Maximum Ratings (1)**

|                           | <del>_</del>                                   |

|---------------------------|------------------------------------------------|

| VDD to VSS                | -0.3V to 7V                                    |

| HB to HS                  | -0.3V to 7V                                    |

| LI or HI Input            | -0.3V to 15V                                   |

| LOH, LOL Output           | -0.3V to VDD +0.3V                             |

| HOH, HOL Output           | V <sub>HS</sub> -0.3V to V <sub>HB</sub> +0.3V |

| HS to VSS                 | -5V to +100V                                   |

| HB to VSS                 | 0 to 107V                                      |

| HB to VDD                 | 0 to 100V                                      |

| Junction Temperature      | +150°C                                         |

| Storage Temperature Range | −55°C to +150°C                                |

| ESD Rating HBM            | 2 kV                                           |

|                           | ,                                              |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

## **Recommended Operating Conditions**

| VDD                  | +4.5V to +5.5V                 |

|----------------------|--------------------------------|

| LI or HI Input       | 0V to +14V                     |

| HS                   | -5V to 100V                    |

| НВ                   | $V_{HS}$ +4V to $V_{HS}$ +5.5V |

| HS Slew Rate         | <50 V/ns                       |

| Junction Temperature | −40°C to +125°C                |

## **Electrical Characteristics**

Limits in standard type are for  $T_J$  = 25°C only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise specified,  $V_{DD} = V_{HB} = 5V$ ,  $V_{SS} = V_{HS} = 0V$ , No Load on LOL and HOL or HOH and HOL (1).

| Symbol            | Parameter                                                                              | Conditions                           | Min  | Тур  | Max      | Units |

|-------------------|----------------------------------------------------------------------------------------|--------------------------------------|------|------|----------|-------|

| SUPPLY (          | CURRENTS                                                                               |                                      |      |      | <u> </u> |       |

| I <sub>DD</sub>   | VDD Quiescent Current                                                                  | LI = HI = 0V                         |      | 0.07 | 0.1      | mA    |

| I <sub>DDO</sub>  | VDD Operating Current                                                                  | f = 500 kHz                          |      | 2.0  | 3.0      | mA    |

| I <sub>HB</sub>   | Total HB Quiescent Current                                                             | LI = HI = 0V                         |      | 0.08 | 0.1      | mA    |

| I <sub>HBO</sub>  | Total HB Operating Current                                                             | f = 500 kHz                          |      | 1.5  | 2.5      | mA    |

| I <sub>HBS</sub>  | HB to VSS Current, Quiescent                                                           | HS = HB = 100V                       |      | 0.1  | 8        | μA    |

| I <sub>HBSO</sub> | HB to VSS Current, Operating                                                           | f = 500 kHz                          |      | 0.4  | 1.0      | mA    |

| INPUT PI          | NS                                                                                     |                                      | II.  |      |          | 1     |

| V <sub>IR</sub>   | Input Voltage Threshold                                                                | Rising Edge                          | 1.89 | 2.06 | 2.18     | V     |

| V <sub>IF</sub>   | Input Voltage Threshold                                                                | Falling Edge                         | 1.48 | 1.66 | 1.76     | V     |

| V <sub>IHYS</sub> | Input Voltage Hysteresis                                                               |                                      |      | 400  |          | mV    |

| R <sub>I</sub>    | Input Pulldown Resistance                                                              |                                      | 100  | 200  | 300      | kΩ    |

| UNDER V           | OLTAGE PROTECTION                                                                      |                                      |      |      |          |       |

| $V_{DDR}$         | VDD Rising Threshold                                                                   |                                      | 3.2  | 3.8  | 4.5      | V     |

| V <sub>DDH</sub>  | VDD Threshold Hysteresis                                                               |                                      |      | 0.2  |          | V     |

| V <sub>HBR</sub>  | HB Rising Threshold                                                                    |                                      | 2.5  | 3.2  | 3.9      | V     |

| $V_{HBH}$         | HB Threshold Hysteresis                                                                |                                      |      | 0.2  |          | V     |

| BOOTSTE           | RAP DIODE                                                                              |                                      | II.  |      |          | 1     |

| $V_{DL}$          | Low-Current Forward Voltage                                                            | I <sub>VDD-HB</sub> = 100 μA         |      | 0.45 | 0.65     | V     |

| $V_{DH}$          | High-Current Forward Voltage                                                           | I <sub>VDD-HB</sub> = 100 mA         |      | 0.90 | 1.00     | V     |

| R <sub>D</sub>    | Dynamic Resistance                                                                     | $I_{VDD-HB} = 100 \text{ mA}$        |      | 1.85 | 3.60     | Ω     |

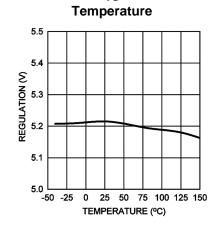

|                   | HB-HS Clamp                                                                            | Regulation Voltage                   | 4.7  | 5.2  | 5.45     | V     |

| LOW & H           | GH SIDE GATE DRIVER                                                                    | ,                                    | 1    |      |          |       |

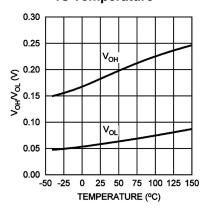

| V <sub>OL</sub>   | Low-Level Output Voltage                                                               | $I_{HOL} = I_{LOL} = 100 \text{ mA}$ |      | 0.06 | 0.10     | V     |

| $V_{OH}$          | High-Level Output Voltage<br>V <sub>OH</sub> = VDD – LOH or V <sub>OH</sub> = HB – HOH | $I_{HOH} = I_{LOH} = 100 \text{ mA}$ |      | 0.21 | 0.31     | V     |

| I <sub>OHL</sub>  | Peak Source Current                                                                    | HOH, LOH = 0V                        |      | 1.2  |          | Α     |

| I <sub>OLL</sub>  | Peak Sink Current                                                                      | HOL, LOL = 5V                        |      | 5    |          | Α     |

| I <sub>OHLK</sub> | High-Level Output Leakage Current                                                      | HOH, LOH = 0V                        |      |      | 1.5      | μA    |

| I <sub>OLLK</sub> | Low-Level Output Leakage Current                                                       | HOL, LOL = 5V                        |      |      | 1.5      | μΑ    |

| THERMAI           | RESISTANCE                                                                             | ·                                    | ,    |      | •        | •     |

| $\theta_{JA}$     | Junction to Ambient (2)                                                                | LLP-10                               |      | 40   |          | °C/W  |

|                   |                                                                                        | 12-bump micro SMD                    |      | 80   |          | °C/W  |

<sup>(1)</sup> Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Product Folder Links: LM5113

<sup>(2)</sup> Four layer board with Cu finished thickness 1.5/1/1/1.5 oz. Maximum die size used. 5x body length of Cu trace on PCB top. 50 x 50mm ground and power planes embedded in PCB. See Application Note AN-1187.

## **Switching Characteristics**

Limits in standard type are for  $T_J = 25^{\circ}C$  only; limits in boldface type apply over the junction temperature  $(T_J)$  range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only. Unless otherwise specified,  $V_{DD} = V_{HB} = 5V$ ,  $V_{SS} = V_{HS} = 0V$ , No Load on LOL and LOH or HOL and HOH  $^{(1)}$ .

| Symbol            | Parameter                                         | Conditions                                        | Min | Тур  | Max  | Units |

|-------------------|---------------------------------------------------|---------------------------------------------------|-----|------|------|-------|

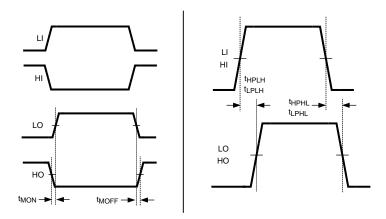

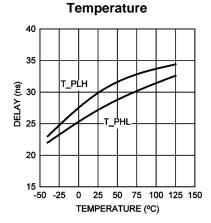

| t <sub>LPHL</sub> | LO Turn-Off Propagation Delay                     | LI Falling to LOL Falling                         |     | 26.5 | 45.0 | ns    |

| t <sub>LPLH</sub> | LO Turn-On Propagation Delay                      | LI Rising to LOH Rising                           |     | 28.0 | 45.0 | ns    |

| t <sub>HPHL</sub> | HO Turn-Off Propagation Delay                     | HI Falling to HOL Falling                         |     | 26.5 | 45.0 | ns    |

| t <sub>HPLH</sub> | HO Turn-On Propagation Delay                      | HI Rising to HOH Rising                           |     | 28.0 | 45.0 | ns    |

| t <sub>MON</sub>  | Delay Matching: LO on & HO off                    |                                                   |     | 1.5  | 8.0  | ns    |

| t <sub>MOFF</sub> | Delay Matching: LO off & HO on                    |                                                   |     | 1.5  | 8.0  | ns    |

| t <sub>HRC</sub>  | HO Rise Time (0.5V - 4.5V)                        | C <sub>L</sub> = 1000 pF                          |     | 7.0  |      | ns    |

| t <sub>LRC</sub>  | LO Rise Time (0.5V – 4.5V)                        | C <sub>L</sub> = 1000 pF                          |     | 7.0  |      | ns    |

| t <sub>HFC</sub>  | HO Fall Time (0.5V - 4.5V)                        | C <sub>L</sub> = 1000 pF                          |     | 1.5  |      | ns    |

| t <sub>LFC</sub>  | LO Fall Time (0.5V - 4.5V)                        | C <sub>L</sub> = 1000 pF                          |     | 1.5  |      | ns    |

| t <sub>PW</sub>   | Minimum Input Pulse Width that Changes the Output |                                                   |     | 10   |      | ns    |

| t <sub>BS</sub>   | Bootstrap Diode Reverse Recovery Time             | I <sub>F</sub> = 100mA,<br>I <sub>R</sub> = 100mA |     | 40   |      | ns    |

<sup>(1)</sup> Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

## **Timing Diagram**

Figure 3. Timing Diagram

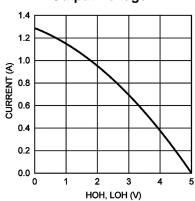

# **Typical Performance Characteristics**

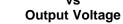

Figure 4. Peak Source Current vs

Output Voltage

Figure 5. Peak Sink Current

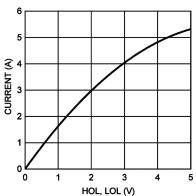

Figure 6. I<sub>DDO</sub> vs

Frequency

Copyright © 2011–2012, Texas Instruments Incorporated

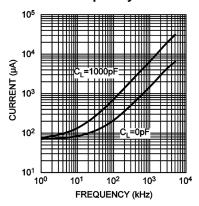

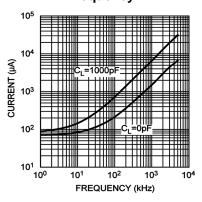

Figure 7. I<sub>HBO</sub> vs Frequency

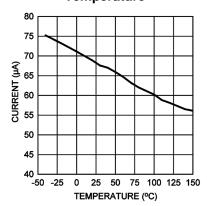

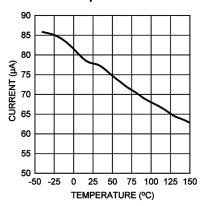

Figure 8.  $I_{DD}$  vs Temperature

Figure 9. I<sub>HB</sub> vs Temperature

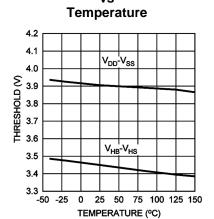

Figure 10. UVLO Rising Thresholds

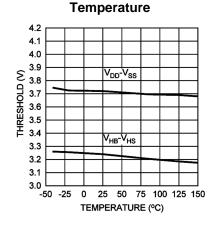

Figure 11. UVLO Falling Thresholds

vs

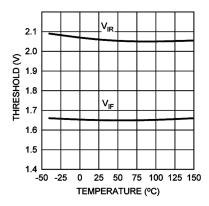

Figure 12. Input Thresholds vs

Temperature

Copyright © 2011–2012, Texas Instruments Incorporated

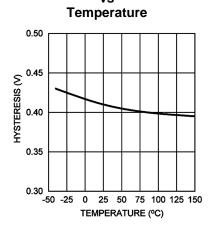

Figure 13. Input Threshold Hysteresis

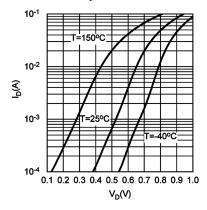

Figure 14. Bootstrap Diode Forward Voltage

Figure 15. Propagation Delay

Figure 16. LO&HO Gate Drive — High/Low Level Output Voltage vs Temperature

Figure 17. HB Regulation Voltage

Unless otherwise specified, VDD = VHB = 5V, VSS = VHS = 0V.

#### **Detailed Operating Description**

The LM5113 is designed to drive both the high-side and the low-side enhancement mode Gallium Nitride FETs in a synchronous buck or a half-bridge configuration. The outputs of the LM5113 are independently controlled with TTL input thresholds. The inputs of the LM5113 can withstand voltages up to 14V regardless of the VDD voltage, and can be directly connected to the outputs of PWM controllers.

The high side driver uses the floating bootstrap capacitor voltage to drive the high-side FET. As shown in Figure 1, the bootstrap capacitor is recharged through an internal bootstrap diode each cycle when the HS pin is pulled below the VDD voltage. For inductive load applications the HS node will fall to a negative potential, clamped by the low side FET.

Due to the intrinsic feature of enhancement mode GaN FETs the source-to-drain voltage, when the gate is pulled low, is usually higher than a diode forward voltage drop. This can lead to an excessive bootstrap voltage that can damage the high-side GaN FET. The LM5113 solves this problem with an internal clamping circuit that prevents the bootstrap voltage from exceeding 5.2V typical.

The output pull-down and pull-up resistance of LM5113 is optimized for enhancement mode GaN FETs to achieve high frequency, efficient operation. The  $0.6\Omega$  pull-down resistance provides a robust low impedance turn-off path necessary to eliminate undesired turn-on induced by high dv/dt or high di/dt. The  $2.1\Omega$  pull-up resistance helps reduce the ringing and over-shoot of the switch node voltage. The split outputs of the LM5113 offer flexibility to adjust the turn-on and turn-off speed by independently adding additional impedance in either the turn-on path and/or the turn-off path.

Copyright © 2011–2012, Texas Instruments Incorporated

The LM5113 has an Under-voltage Lockout (UVLO) on both the VDD and bootstrap supplies. When the VDD voltage is below the threshold voltage of 3.8V, both the HI and LI inputs are ignored, to prevent the GaN FETs from being partially turned on. Also if there is sufficient VDD voltage, the UVLO will actively pull the LOL and HOL low. When the HB to HS bootstrap voltage is below the UVLO threshold of 3.2V, only HOL is pulled low. Both UVLO threshold voltages have 200mV of hysteresis to avoid chattering.

## **Bypass Capacitor**

The VDD bypass capacitor provides the gate charge for the low-side and high-side transistors and to absorb the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated as follows:

$$C_{VDD} > \frac{Q_{gH} + Q_{gL} + Q_{rr}}{\Delta V}$$

$Q_{gH}$  and  $Q_{gL}$  are gate charge of the high-side and low-side transistors respectively.  $Q_{rr}$  is the reverse recovery charge of the bootstrap diode, which is typically around 4nC.  $\Delta V$  is the maximum allowable voltage drop across the bypass capacitor. A 0.1uF or larger value, good quality, ceramic capacitor is recommended. The bypass capacitor should be placed as close to the pins of the IC as possible to minimize the parasitic inductance.

## **Bootstrap Capacitor**

The bootstrap capacitor provides the gate charge for the high-side switch, dc bias power for HB under-voltage lockout circuit, and the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated as follows:

$$C_{BST} > \frac{Q_{gH} + I_{HB} \times t_{ON} + Q_{rr}}{\Delta V}$$

$I_{HB}$  is the quiescent current of the high-side driver.  $t_{on}$  is the maximum on-time period of the high-side transistor. A good quality, ceramic capacitor should be used for the bootstrap capacitor. It is recommended to place the bootstrap capacitor as close to the HB and HS pins as possible.

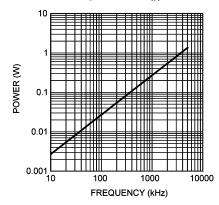

### **Power Dissipation**

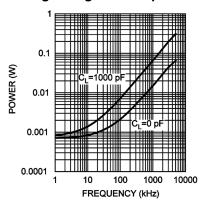

The power consumption of the driver is an important measure that determines the maximum achievable operating frequency of the driver. It should be kept below the maximum power dissipation limit of the package at the operating temperature. The total power dissipation of the LM5113 is the sum of the gate driver losses and the bootstrap diode power loss.

The gate driver losses are incurred by charge and discharge of the capacitive load. It can be approximated as

$$P = (C_{LoadH} + C_{LoadL}) \times V_{DD}^{2} \times f_{SW}$$

$C_{LoadH}$  and  $C_{LoadL}$  are the high-side and the low-side capacitive loads respectively. It can also be calculated with the total input gate charge of the high-side and the low-side transistors as

2 Submit Documentation Feedback

Copyright © 2011–2012, Texas Instruments Incorporated

(4)

$$P = (Q_{gH} + Q_{gL}) \times V_{DD} \times f_{sw}$$

There are some additional losses in the gate drivers due to the internal CMOS stages used to buffer the LO and HO outputs. The following plot shows the measured gate driver power dissipation versus frequency and load capacitance. At higher frequencies and load capacitance values, the power dissipation is dominated by the power losses driving the output loads and agrees well with the above equations. This plot can be used to approximate the power losses due to the gate drivers.

Figure 18. Neglecting Bootstrap Diode Losses

Gate Driver Power Dissipation (LO+HO) VDD=+5V,

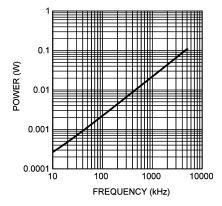

The bootstrap diode power loss is the sum of the forward bias power loss that occurs while charging the bootstrap capacitor and the reverse bias power loss that occurs during reverse recovery. Since each of these events happens once per cycle, the diode power loss is proportional to the operating frequency. Larger capacitive loads require more energy to recharge the bootstrap capacitor resulting in more losses. Higher input voltages  $(V_{IN})$  to the half bridge also result in higher reverse recovery losses.

The following two plots illustrate the forward bias power loss and the reverse bias power loss of the bootstrap diode respectively. The plots are generated based on calculations and lab measurements of the diode reverse time and current under several operating conditions. The plots can be used to predict the bootstrap diode power loss under different operating conditions.

Figure 19. Forward Bias Power Loss of Bootstrap Diode V<sub>IN</sub>=50V

The Load of High-Side Driver is a GaN FET with Total Gate Charge of 10nC

Figure 20. Reverse Recovery Power Loss of Bootstrap Diode V<sub>IN</sub>=50V

The Load of High-Side Driver is a GaN FET with Total Gate Charge of 10nC

The sum of the driver loss and the bootstrap diode loss is the total power loss of the IC. For a given ambient temperature, the maximum allowable power loss of the IC can be defined as

$$P = \frac{(T_J - T_A)}{\theta_{JA}} \tag{5}$$

### **Layout Considerations**

Small gate capacitance and miller capacitance enable enhancement mode GaN FETs to operate with fast switching speed. The induced high dv/dt and di/dt, coupled with a low gate threshold voltage and limited headroom of enhancement mode GaN FETs gate voltage, make the circuit layout crucial to the optimum performance. Following are some hints.

- The first priority in designing the layout of the driver is to confine the high peak currents that charge and discharge the GaN FETs gate into a minimal physical area. This will decrease the loop inductance and minimize noise issues on the gate terminal of the GaN FETs. The GaN FETs should be placed close to the driver.

- 2. The second high current path includes the bootstrap capacitor, the local ground referenced VDD bypass capacitor and low-side GaN FET. The bootstrap capacitor is recharged on a cycle-by-cycle basis through the bootstrap diode from the ground referenced VDD capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

- 3. The parasitic inductance in series with the source of the high-side FET and the low-side FET can impose excessive negative voltage transients on the driver. It is recommended to connect HS pin and VSS pin to the respective source of the high-side and low-side transistors with a short and low-inductance path.

- 4. The parasitic source inductance, along with the gate capacitor and the driver pull-down path, can form a LCR resonant tank, resulting in gate voltage oscillations. An optional resistor or ferrite bead can be used to damp the ringing.

- 5. Low ESR/ESL capacitors must be connected close to the IC, between VDD and VSS pins and between the HB and HS pins to support the high peak current being drawn from VDD during turn-on of the FETs. It is most desirable to place the VDD decoupling capacitor and the HB to HS bootstrap capacitor on the same side of the PC board as the driver. The inductance of vias can impose excessive ringing on the IC pins.

- 6. To prevent excessive ringing on the input power bus, good decoupling practices are required by placing low ESR ceramic capacitors adjacent to the GaN FETs.

The following figures show recommended layout patterns for LLP-10 package and micro SMD package respectively. Two cases are considered: (1) Without any gate resistors; (2) With an optional turn-on gate resistor. It should be noted that 0402 SMD package is assumed for the passive components in the drawings. For information on micro SMD package assembly, refer to Application Note AN-1112.

Submit Documentation Feedback

Copyright © 2011–2012, Texas Instruments Incorporated

Figure 21. Without Gate Resistors

Figure 22. With HOH and LOH Gate Resistors

Figure 23. Without Gate Resistors

Copyright © 2011–2012, Texas Instruments Incorporated

Figure 24. With HOH and LOH Gate Resistors

17-Nov-2012

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type |         |    | Package Qty | Eco Plan                   | Lead/Ball Finish |                    | Samples          |

|------------------|--------|--------------|---------|----|-------------|----------------------------|------------------|--------------------|------------------|

|                  | (1)    |              | Drawing |    |             | (2)                        |                  | (3)                | (Requires Login) |

| LM5113SD/NOPB    | ACTIVE | WSON         | DPR     | 10 | 1000        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |                  |

| LM5113SDE/NOPB   | ACTIVE | WSON         | DPR     | 10 | 250         | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |                  |

| LM5113SDX/NOPB   | ACTIVE | WSON         | DPR     | 10 | 4500        | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |                  |

| LM5113TME/NOPB   | ACTIVE | DSBGA        | YFX     | 12 | 250         | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM |                  |

| LM5113TMX/NOPB   | ACTIVE | DSBGA        | YFX     | 12 | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM |                  |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

17-Nov-2012

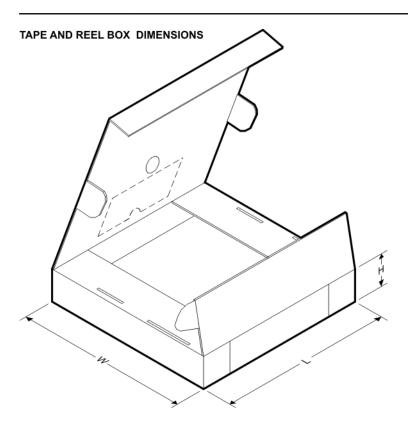

PACKAGE MATERIALS INFORMATION

www.ti.com 17-Nov-2012

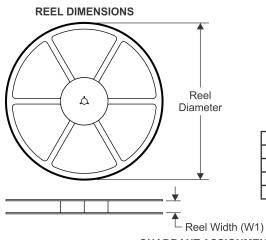

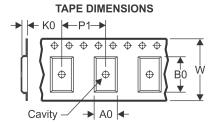

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

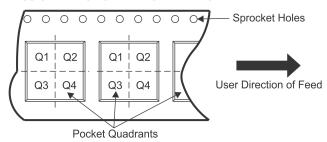

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5113SD/NOPB  | WSON            | DPR                | 10 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5113SDE/NOPB | WSON            | DPR                | 10 | 250  | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5113SDX/NOPB | WSON            | DPR                | 10 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5113TME/NOPB | DSBGA           | YFX                | 12 | 250  | 178.0                    | 8.4                      | 1.85       | 2.01       | 0.76       | 4.0        | 8.0       | Q1               |

| LM5113TMX/NOPB | DSBGA           | YFX                | 12 | 3000 | 178.0                    | 8.4                      | 1.85       | 2.01       | 0.76       | 4.0        | 8.0       | Q1               |

www.ti.com 17-Nov-2012

\*All dimensions are nominal

| 7 til diffictiolorio are florifital |              |                 |      |      |             |            |             |

|-------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LM5113SD/NOPB                       | WSON         | DPR             | 10   | 1000 | 203.0       | 190.0      | 41.0        |

| LM5113SDE/NOPB                      | WSON         | DPR             | 10   | 250  | 203.0       | 190.0      | 41.0        |

| LM5113SDX/NOPB                      | WSON         | DPR             | 10   | 4500 | 349.0       | 337.0      | 45.0        |

| LM5113TME/NOPB                      | DSBGA        | YFX             | 12   | 250  | 203.0       | 190.0      | 41.0        |

| LM5113TMX/NOPB                      | DSBGA        | YFX             | 12   | 3000 | 206.0       | 191.0      | 90.0        |

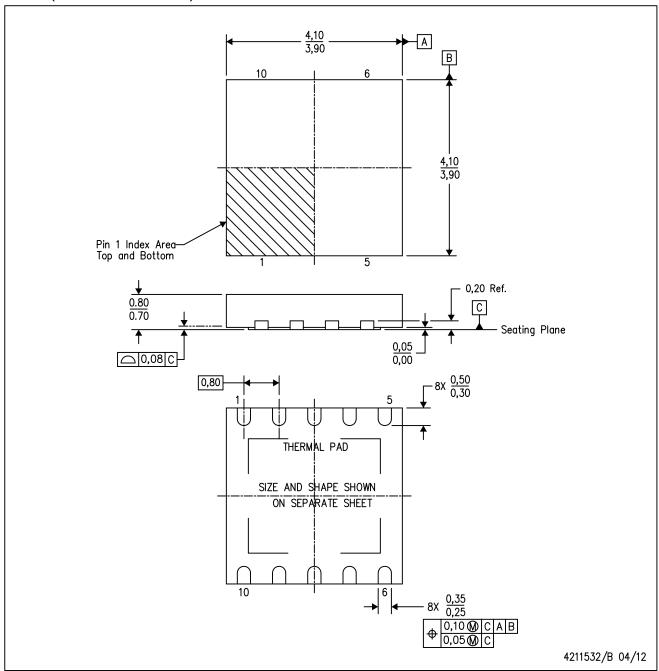

DPR (S-PWSON-N10)

PLASTIC SMALL OUTLINE NO-LEAD

NOTES: All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- SON (Small Outline No-Lead) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance.

See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>