Sample &

Buy

LM3704

SNVS088F-MAY 2004-REVISED APRIL 2016

# LM3704 Voltage Supervisor With Power-Fail Input, Low-Line Output and Manual Reset

Technical

Documents

## 1 Features

- Available Threshold Voltage of 3.08 V and 2.32 V

- No External Components Required

- Manual-Reset Input

- Available in Both Open-Drain and Push-Pull Configuration

- Reset Time-Out Delay of 200 ms

- Separate Power-Fail Comparator

- ±0.5% Reset Threshold Accuracy at Room Temperature

- ±2% Reset Threshold Accuracy Over Temperature

- 28-µA V<sub>CC</sub> Supply Current

## 2 Applications

- Embedded Controllers and Processors

- Intelligent Instruments

- Automotive Systems

- Critical µP Power Monitoring

## 3 Description

Tools &

Software

The LM3704 is a feature-rich, easy-to-use voltage supervisor. It is offered in both push-pull and opendrain configuration with a tight 2% accuracy over temperature.

Support &

Community

20

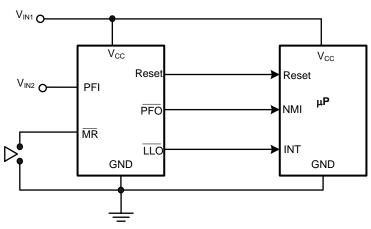

The LM3704 features include a manual reset, low-line output, and power-fail input detection. The power-fail input allows for a configurable second rail to be monitored helping detect upstream failures. The low-line output is used as a second interrupt line to indicate a fall in  $V_{CC}$  (1.02 × VRST).

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LM3704      | VSSOP (10) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

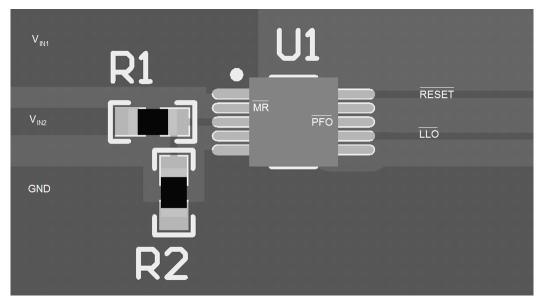

**Typical Application**

Copyright © 2016, Texas Instruments Incorporated

| Page |

|------|

|      |

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription1                          |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 4                      |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Typical Characteristics 8          |

| 7 | Deta | ailed Description 10               |

|   | 7.1  | Overview 10                        |

|   | 7.2  | Functional Block Diagram 10        |

|   | 7.3  | Feature Description 10             |

|   |      |                                    |

Changes from Revision E (November 2012) to Revision F

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section ......1

|    | 7.4  | Device Functional Modes 11         |

|----|------|------------------------------------|

| 8  | App  | lication and Implementation 12     |

|    | 8.1  | Application Information 12         |

|    | 8.2  | Typical Application 12             |

|    |      | System Examples 14                 |

| 9  | Pow  | er Supply Recommendations16        |

| 10 | Lay  | out                                |

|    | 10.1 | Layout Guidelines 16               |

|    | 10.2 | Layout Example 16                  |

| 11 | Dev  | ice and Documentation Support 17   |

|    | 11.1 | Device Support 17                  |

|    | 11.2 | Community Resources 17             |

|    | 11.3 | Trademarks 17                      |

|    | 11.4 | Electrostatic Discharge Caution 17 |

|    | 11.5 | Glossary 17                        |

| 12 |      | hanical, Packaging, and Orderable  |

|    | Info | rmation 17                         |

|    |      |                                    |

**4** Revision History

2

Submit Documentation Feedback

www.ti.com

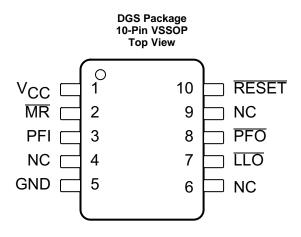

# 5 Pin Configuration and Functions

## **Pin Functions**

|     | PIN             | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |

|-----|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |

| 1   | V <sub>CC</sub> | I   | Power supply input.                                                                                                                                                                                                                                                                                                        |  |

| 2   | MR              | I   | Manual-reset input. When $\overline{MR}$ is less than $V_{MRT}$ (manual reset threshold) $\overline{RESET}/RESET$ is engaged.                                                                                                                                                                                              |  |

| 3   | PFI             | I   | ver-fail comparator input. When PFI is less than V <sub>PFT</sub> (power-fail reset threshold), the PFO goes low.<br>erwise, PFO remains high.                                                                                                                                                                             |  |

| 4   | NC              | —   | No connection.                                                                                                                                                                                                                                                                                                             |  |

| 5   | GND             | —   | Ground reference for all signals.                                                                                                                                                                                                                                                                                          |  |

| 6   | NC              | —   | No connection.                                                                                                                                                                                                                                                                                                             |  |

| 7   | LLO             | О   | Low-line logic output. Early power-fail warning output. Low when $V_{CC}$ falls below $V_{LLOT}$ (low-line output threshold). This output can be used to generate an NMI (non-maskable interrupt) to provide an early warning of imminent power failure.                                                                   |  |

| 8   | PFO             | 0   | Power-fail logic output. When PFI is below V <sub>PFT</sub> , PFO goes low; otherwise, PFO remains high.                                                                                                                                                                                                                   |  |

| 9   | NC              | _   | No connection. Test input used at factory only. Leave floating.                                                                                                                                                                                                                                                            |  |

| 10  | RESET           | О   | Reset logic output. Pulses low for $t_{RP}$ (reset time-out period) when triggered, and stays low whenever $V_{CC}$ is below the reset threshold or when MR is below $V_{MRT}$ . It remains low for $t_{RP}$ after either $V_{CC}$ rises above the reset threshold, or after $\overline{MR}$ input rises above $V_{MRT}$ . |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       | MIN  | MAX                   | UNIT |

|---------------------------------------|------|-----------------------|------|

| Supply voltage, V <sub>CC</sub>       | -0.3 | 6                     | V    |

| All other inputs                      | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Power dissipation                     | S    | See <sup>(2)</sup>    |      |

| Storage temperature, T <sub>stg</sub> | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance, θ<sub>J-A</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is calculated using:

$$P(MAX) = \frac{T_J(MAX) - T_A}{\theta_{J-A}}$$

Where the value of  $\theta_{J-A}$  for the 10-pin VSSOP package is 195°C/W in a typical printed-circuit board (PCB) mounting and the DSBGA package is 220°C/W.

## 6.2 ESD Ratings

|                                            |                                                                                |      | VALUE | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------------|------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              |      | N     |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±150 | v     |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                      | MIN | MAX | UNIT |

|----------------|----------------------|-----|-----|------|

| T <sub>A</sub> | Free-air temperature | -40 | 85  | °C   |

#### 6.4 Thermal Information

|                       |                                              | LM3704      |      |  |

|-----------------------|----------------------------------------------|-------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | UNIT |  |

|                       |                                              | 10 PINS     |      |  |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 163.7       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 58.3        | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 83.5        | °C/W |  |

| Ψյт                   | Junction-to-top characterization parameter   | 6           | °C/W |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 82.2        | °C/W |  |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _           | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

at  $T_J = 25^{\circ}C$  and  $V_{CC} = 2.2$  V to 5.5 V (unless otherwise noted)

|                                          | PARAMETER                      | TEST CONI                                                                                                                       | DITIONS                                         | MIN                   | TYP                     | MAX  | UNIT     |

|------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|-------------------------|------|----------|

| POWER                                    | R SUPPLY                       |                                                                                                                                 |                                                 |                       |                         |      |          |

| V <sub>CC</sub>                          | Operating voltage              | LM3704, $T_J = -40^{\circ}C$ to 8                                                                                               | 5°C                                             | 1                     |                         | 5.5  | V        |

|                                          |                                | All inputs = $V_{CC}$ ,                                                                                                         | $T_J = 25^{\circ}C$                             |                       | 28                      |      |          |

| I <sub>CC</sub>                          | V <sub>CC</sub> supply current | all outputs floating                                                                                                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$           |                       |                         | 50   | μA       |

| RESET                                    | THRESHOLD                      |                                                                                                                                 | 5                                               |                       |                         |      |          |

|                                          |                                |                                                                                                                                 | $T_J = 25^{\circ}C$                             | -0.5%                 | V <sub>RST</sub>        | 0.5% |          |

| V <sub>RST</sub>                         | Reset threshold                | V <sub>CC</sub> falling                                                                                                         | $T_{.1} = -40^{\circ}C \text{ to } 85^{\circ}C$ | -2%                   | 1.01                    | 2%   | -        |

| i loi                                    |                                | 00 0                                                                                                                            | $T_J = 0^{\circ}C$ to $70^{\circ}C$             | -1.5%                 |                         | 1.5% | -        |

| V <sub>RSTH</sub>                        | Reset threshold hysteresis     |                                                                                                                                 | 0                                               |                       | 0032 × V <sub>RST</sub> |      | mV       |

| Kom                                      |                                | Reset time-out period =                                                                                                         | T <sub>.1</sub> = 25°C                          |                       | 200                     |      |          |

| t <sub>RP</sub>                          | Reset time-out period          | C                                                                                                                               | $T_J = -40^{\circ}C \text{ to } 85^{\circ}C$    | 140                   |                         | 280  | ms       |

| t <sub>RD</sub>                          | V <sub>CC</sub> to reset delay | V <sub>CC</sub> falling at 1 mV/µs                                                                                              |                                                 |                       | 20                      | 200  | μs       |

| RESET                                    |                                |                                                                                                                                 |                                                 |                       | μο                      |      |          |

|                                          |                                | $V_{CC} > 1.0 \text{ V}, \text{ I}_{SINK} = 50 \mu$                                                                             | Α                                               |                       |                         |      |          |

|                                          |                                | $T_{\rm J} = -40^{\circ}$ C to 85°C                                                                                             | , ,,                                            |                       |                         | 0.3  |          |

|                                          |                                | V <sub>CC</sub> > 1.2 V, I <sub>SINK</sub> = 100                                                                                | μΑ,                                             |                       |                         | 0.3  |          |

|                                          |                                | $T_J = -40^{\circ}C$ to $85^{\circ}C$                                                                                           |                                                 |                       |                         | 0.0  | -        |

| V <sub>OL</sub>                          | RESET                          | $V_{CC} > 2.25 \text{ V}, \text{ I}_{SINK} = 900 \ \mu\text{A},$                                                                |                                                 |                       |                         | 0.3  | _        |

|                                          |                                | $T_{J} = -40^{\circ}C \text{ to } 85^{\circ}C$                                                                                  |                                                 |                       |                         |      |          |

|                                          |                                | $V_{CC} > 2.7 \text{ V}, \text{ I}_{SINK} = 1.2 \text{ mA},$<br>T <sub>J</sub> = -40°C to 85°C                                  |                                                 |                       |                         | 0.3  |          |

|                                          |                                | $V_{CC}$ > 4.5 V, I <sub>SINK</sub> = 3.2 mA,<br>T <sub>J</sub> = -40°C to 85°C                                                 |                                                 |                       |                         | 0.4  |          |

|                                          |                                | V <sub>CC</sub> > 2.25 V, I <sub>SOURCE</sub> = 300 μA,                                                                         |                                                 | 0.8 × V <sub>CC</sub> |                         |      |          |

|                                          |                                | $T_{\rm J} = -40^{\circ}$ C to 85°C                                                                                             |                                                 |                       |                         |      | V        |

| V <sub>OH</sub>                          | RESET                          | $V_{CC} > 2.7 \text{ V}, \text{ I}_{SOURCE} = 500 \mu\text{A},$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$ |                                                 | $0.8 \times V_{CC}$   |                         |      |          |

|                                          |                                | $V_{CC}$ > 4.5 V, I <sub>SOURCE</sub> = 800 µA,<br>T <sub>J</sub> = -40°C to 85°C                                               |                                                 | V <sub>CC</sub> – 1.5 |                         |      |          |

| PFI/MR                                   |                                |                                                                                                                                 |                                                 |                       |                         |      |          |

|                                          | •                              | T <sub>.1</sub> = 25°C                                                                                                          |                                                 |                       | 1.225                   |      |          |

| V <sub>PFT</sub>                         | PFI input threshold            | $T_{,1} = -40^{\circ}C \text{ to } 85^{\circ}C$                                                                                 |                                                 | 1.2                   |                         | 1.25 | V        |

|                                          |                                | , , , , , , , , , , , , , , , , , , ,                                                                                           | MR, low                                         |                       |                         | 0.8  |          |

| V <sub>MRT</sub>                         | MR Input threshold             | $T_J = -40^{\circ}C$ to $85^{\circ}C$                                                                                           | MR, high                                        | 2                     |                         |      | V        |

| V <sub>PFTH</sub> /<br>V <sub>MRTH</sub> | PFI/MR threshold hysteresis    | PFI/ $\overline{\text{MR}}$ falling, V <sub>CC</sub> = V <sub>R</sub> :                                                         |                                                 |                       | 0032 × V <sub>RST</sub> |      | mV       |

|                                          | Input current (PFI only)       | $T_J = -40^{\circ}C$ to $85^{\circ}C$                                                                                           |                                                 | -75                   |                         | 75   | nA       |

| I <sub>PFI</sub>                         | input current (i i i oniy)     | $T_{J} = 25^{\circ}C$                                                                                                           |                                                 | -75                   | 56                      | 15   |          |

| R <sub>MR</sub>                          | MR pullup resistance           | $T_{J} = 25 \text{ C}$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$                                          |                                                 | 35                    | 00                      | 75   | kΩ       |

| t                                        | MR to reset delay              | ·J = -0 0 10 05 0                                                                                                               |                                                 |                       | 12                      | 13   | μS       |

| t <sub>MD</sub>                          | MR to reset delay              | T <sub>.1</sub> = -40°C to 85°C                                                                                                 |                                                 | 25                    | 12                      |      | μS<br>μS |

| t <sub>MR</sub><br>PFO, L                |                                | ·J = -+0 0 10 05 0                                                                                                              |                                                 | 20                    |                         |      | μΟ       |

| 177 <b>0</b> , L                         | 10                             | V > 2.25 V I = 000                                                                                                              | )                                               |                       |                         |      |          |

|                                          |                                | $V_{CC} > 2.25 \text{ V}, I_{SINK} = 900$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$                       |                                                 |                       |                         | 0.3  |          |

| V <sub>OL</sub>                          | PFO, LLO output low voltage    | $V_{CC} > 2.7 \text{ V}, I_{SINK} = 1.2 \text{ mA}, T_{J} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$                 |                                                 |                       |                         | 0.3  | V        |

|                                          |                                | $V_{CC} > 4.5 \text{ V}, \text{ I}_{SINK} = 3.2 \text{ r}$<br>T <sub>J</sub> = -40°C to 85°C                                    | nA,                                             |                       |                         | 0.4  |          |

# **Electrical Characteristics (continued)**

|                    | PARAMETER                         | TEST COND                                                                              | DITIONS                               | MIN                     | TYP                     | MAX                     | UNIT |

|--------------------|-----------------------------------|----------------------------------------------------------------------------------------|---------------------------------------|-------------------------|-------------------------|-------------------------|------|

| V <sub>OH</sub>    | PFO, LLO output high<br>voltage   | $V_{CC}$ > 2.25 V, $I_{SOURCE}$ = 300 µA,<br>$T_{J}$ = -40°C to 85°C                   |                                       | 0.8 V <sub>CC</sub>     |                         |                         |      |

|                    |                                   | $V_{CC}$ > 2.7 V, $I_{SOURCE}$ = 500 µA,<br>T <sub>J</sub> = -40°C to 85°C             |                                       | 0.8 V <sub>CC</sub>     |                         |                         | V    |

|                    |                                   | $V_{CC} > 4.5 \text{ V}, \text{ I}_{SOURCE} = 800 \mu\text{A},$<br>T_J = -40°C to 85°C |                                       | V <sub>CC</sub> - 1.5   |                         |                         |      |

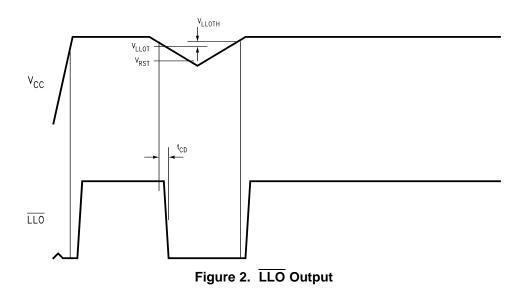

| LLO OU             | ITPUT                             |                                                                                        |                                       |                         |                         |                         |      |

| V                  |                                   |                                                                                        | $T_J = 25^{\circ}C$                   |                         | 1.02 × V <sub>RST</sub> |                         | v    |

| V <sub>LLOT</sub>  | LLO output threshold              | $V_{LLO} - V_{RST}, V_{CC}$ falling                                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 1.01 × V <sub>RST</sub> |                         | 1.03 × V <sub>RST</sub> | V    |

| V <sub>LLOTH</sub> | Low-line comparator<br>hysteresis |                                                                                        |                                       |                         | $0.0032 \times V_{RST}$ |                         | mV   |

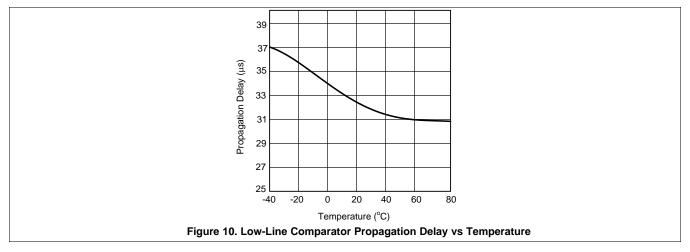

| t <sub>CD</sub>    | Low-line comparator delay         | V <sub>CC</sub> falling at 1 mV/µs                                                     |                                       |                         | 20                      |                         | μs   |

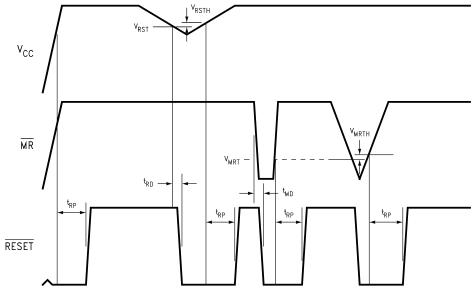

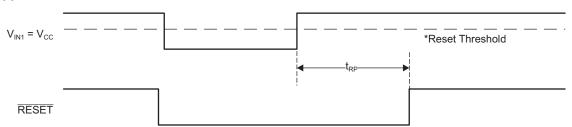

Figure 1. LM3704 Reset Time With MR

6

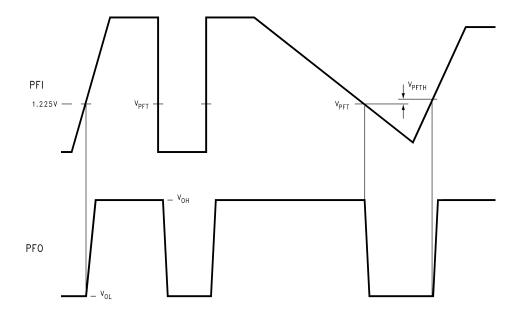

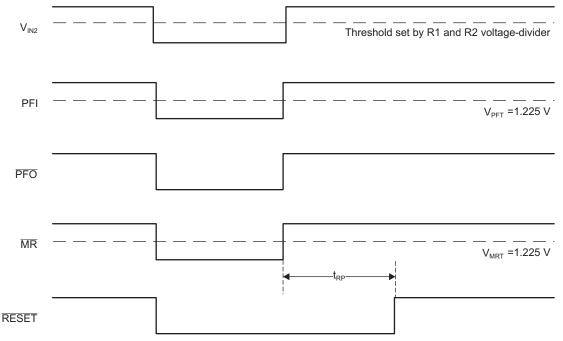

Figure 3. PFI Comparator Timing Diagram

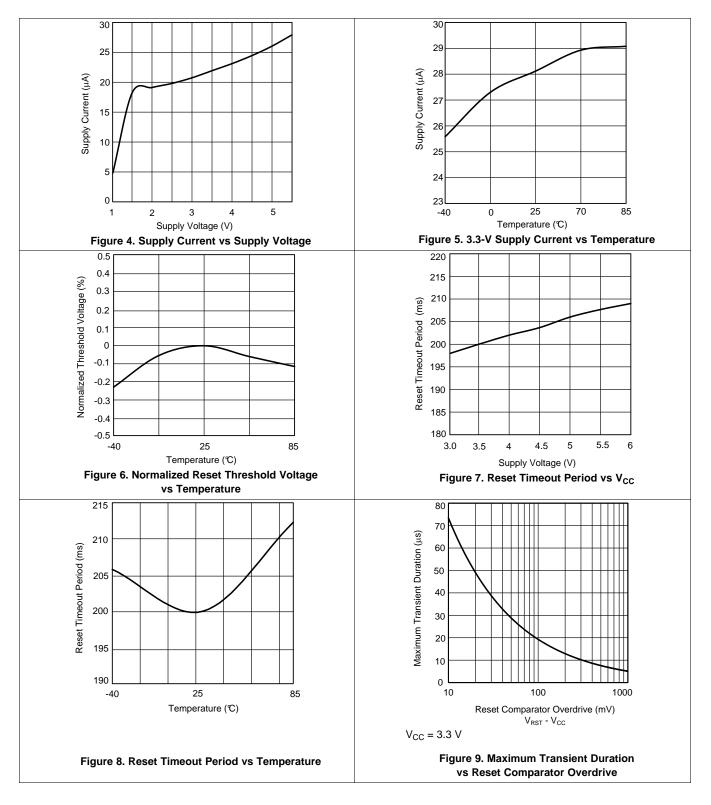

## 6.6 Typical Characteristics

# **Typical Characteristics (continued)**

9

# 7 Detailed Description

## 7.1 Overview

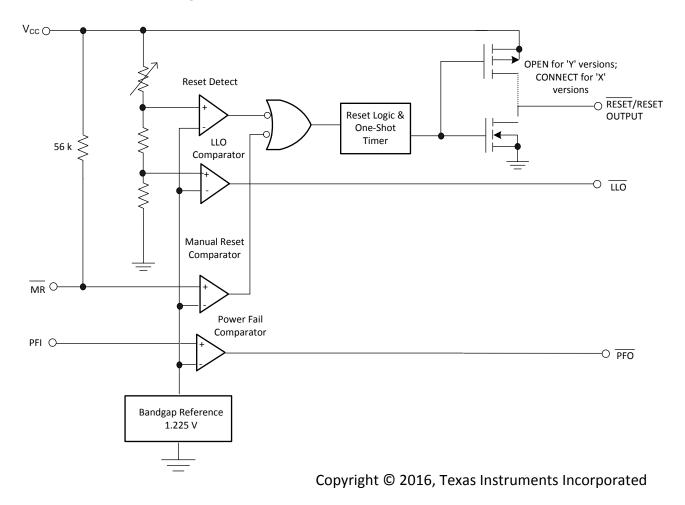

The LM3704 microprocessor supervisory circuit monitors power supplies and battery-controlled functions in systems and does not require external components. There is a standard reset threshold voltage of 3.08 V while other custom reset threshold voltages are available to provide maximum monitoring flexibility. The RESET pin pulses low for the reset time-out period when triggered and stays low whenever  $V_{CC}$  is below the reset threshold or when MR is below  $V_{MRT}$ . Once the  $V_{CC}$  rises above the reset threshold, or after MR input rises above  $V_{MRT}$ , the RESET pin remains low for the reset timeout period before coming up.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Reset Output

The reset input of a  $\mu$ P initializes the device into a known state. The LM3704 microprocessor supervisory circuit asserts a forced reset output to prevent code execution errors during power-up, power-down, and brownout conditions.

RESET is ensured valid for  $V_{CC} > 1$  V. Once  $V_{CC}$  exceeds the reset threshold, an internal timer maintains the output for the reset time-out period. After this interval, reset goes high. The LM3704 offers an active-low RESET.

Any time  $V_{CC}$  drops below the reset threshold (such as during a brownout), the reset activates. When  $V_{CC}$  again rises above the reset threshold, the internal timer starts. Reset holds until  $V_{CC}$  exceeds the reset threshold for longer than the reset time-out period. After this time, reset releases.

#### **Feature Description (continued)**

The Manual Reset input (MR) initiates a forced reset also. See *Manual Reset Input (MR)*.

#### 7.3.2 Reset Threshold

The LM3704 is available with a reset voltage of 3.08 V. Other reset thresholds in the 2.20-V to 5-V range, in steps of 10 mV, are available; contact Texas Instruments for details.

## 7.3.3 Manual Reset Input (MR)

Many  $\mu$ P-based products require a manual reset capability, allowing the operator to initiate a reset. The  $\overline{MR}$  input is fully debounced and provides an internal 56-k $\Omega$  pullup. When the  $\overline{MR}$  input is pulled below V<sub>MRT</sub> (1.225 V) for more than 25  $\mu$ s, reset is asserted after a typical delay of 12  $\mu$ s. Reset remains active as long as MR is held low, and releases after the reset time-out period expires after MR rises above V<sub>MRT</sub>. Use MR with digital logic to assert or to daisy chain supervisory circuits. It may be used as another low-line comparator by adding a buffer.

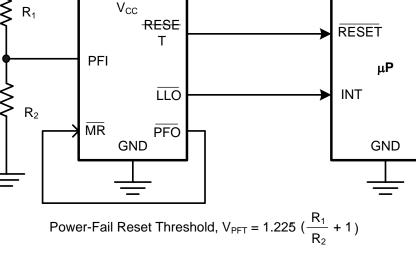

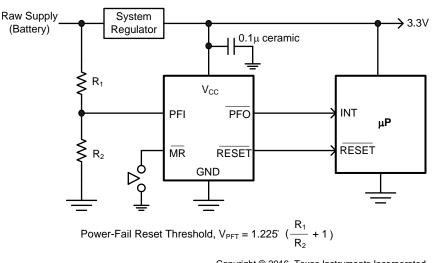

## 7.3.4 Power-Fail Comparator (PFI/PFO)

The PFI is compared to a 1.225-V internal reference,  $V_{PFT}$ . If PFI is less than  $V_{PFT}$ , the Power-Fail Output ( $\overline{PFO}$ ) drops low. The power-fail comparator signals a falling power supply, and is driven typically by an external voltage divider that senses either the unregulated supply or another system supply voltage. The voltage divider generally is chosen so the voltage at PFI drops below  $V_{PFT}$  several milliseconds before the main supply voltage drops below the reset threshold, providing advanced warning of a brownout.

The voltage threshold is set by  $R_1$  and  $R_2$  and is calculated with Equation 1.

$$V_{PFT} = \left(\frac{R1 + R2}{R2}\right) \times 1.225V$$

(1)

#### NOTE

This comparator is completely separate from the rest of the circuitry, and may be employed for other functions as needed.

## 7.3.5 Low-Line Output (LLO)

The low-line output comparator is typically used to provide a non-maskable interrupt to a  $\mu$ P when V<sub>CC</sub> begins falling. LLO monitors V<sub>CC</sub> and goes low when V<sub>CC</sub> falls below V<sub>LLOT</sub> (typically 1.02 × V<sub>RST</sub>) with hysteresis of 0.0032 × V<sub>RST</sub>.

## 7.4 Device Functional Modes

#### 7.4.1 **RESET** Output Low

Anytime V<sub>CC</sub> drops below the reset threshold, the  $\overline{\text{RESET}}$  output drops low and remains low until V<sub>CC</sub> rises above the threshold and the reset time-out period has expired. The manual reset input ( $\overline{\text{MR}}$ ) also causes the reset to be active. If  $\overline{\text{MR}}$  input is pulled below V<sub>MRT</sub> for more than 25 µs, the  $\overline{\text{RESET}}$  output drops low and remains low until  $\overline{\text{MR}}$  rises above the manual reset threshold (V<sub>MRT</sub>) and the reset time-out period has expired.

## 7.4.2 **RESET** Output High

The  $\overline{\text{RESET}}$  output remains high as long as V<sub>CC</sub> is above the reset threshold and  $\overline{\text{MR}}$  is above the manual reset threshold (V<sub>MRT</sub>).

8

Application and Implementation

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The LM3704 is a microprocessor supervisory circuit that provides the maximum flexibility for monitoring power supplies and battery-controlled functions. The reset threshold is typically 3.08 V but can be customized for voltages between 2.2 V and 5 V in 10-mV increments by contacting Texas Instruments. The power-fail input, which is a 1.225-V threshold detector for power-fail warning, can be adjusted using a resistor divider as shown in Figure 11. This section shows various application circuits to provide different monitoring solutions.

VIN1

## 8.2 Typical Application

$V_{IN2}$

Copyright © 2016, Texas Instruments Incorporated

#### Figure 11. Monitoring Two Critical Supplies

#### 8.2.1 Design Requirements

The component count is minimal; employing two resistors as part of a voltage-divider circuit is all that is needed for the typical application of monitoring two critical supplies shown in Figure 11.

#### 8.2.2 Detailed Design Procedure

The voltage-divider circuit that connects to the power-fail reset pin is chosen such that the reset threshold at the device is 1.225 V as shown in Figure 11.

Product Folder Links: LM3704

www.ti.com

## **Typical Application (continued)**

## 8.2.3 Application Curves

Standard reset threshold is 3.08 V. Custom reset voltages are available between 2.2 V and 5 V in 10-mV increments by contacting Texas Instruments.

See Electrical Characteristics for high and low levels of this specific application.

LM3704 SNVS088F – MAY 2004 – REVISED APRIL 2016

www.ti.com

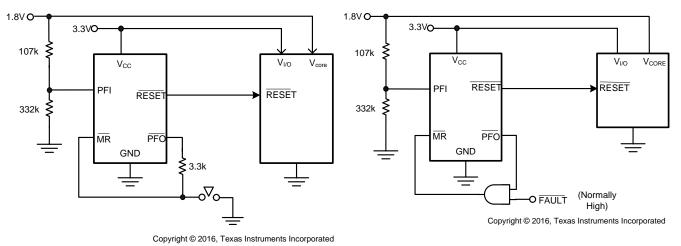

## 8.3 System Examples

The LM3704 voltage supervisor has various features such as power-fail input detection, low-line output, and manual reset while requiring few to no additional components making it versatile and easy-to-use. See Figure 14 through Figure 18 for a variety of circuit applications.

Copyright © 2016, Texas Instruments Incorporated

Figure 15. Monitoring Dual Supplies

Plus External Fault Input

$\overline{\text{MR}}$  input with its 1.225-V nominal threshold, may monitor an additional supply voltage. An internal 56-k $\Omega$  pullup resistor is included on this input.

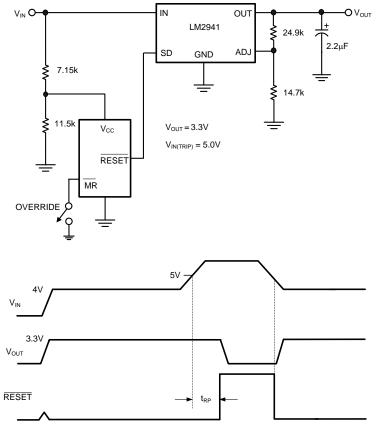

Figure 16. Microprocessor Supervisor With Early Warning Detector

## System Examples (continued)

Copyright © 2016, Texas Instruments Incorporated

Figure 17. Regulator/Switch With Long-Term Overvoltage Lockout Prevents Overdissipation in Linear Regulator

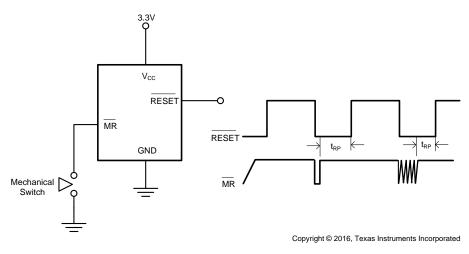

Figure 18. Switch Debouncer

## 9 Power Supply Recommendations

The input power supply to the V<sub>CC</sub> pin of the LM3704 must be kept at a voltage lower than the recommended voltage of 5.5 V. All other input pins must be kept at a voltage lower than V<sub>CC</sub> + 0.3 V. Do not exceed absolute maximum ratings found in *Absolute Maximum Ratings* in any circumstance.

## 10 Layout

## 10.1 Layout Guidelines

Keep traces short between IC and external components.

## **10.2 Layout Example**

Figure 19. Layout Example for Application Circuit

## **11** Device and Documentation Support

## **11.1 Device Support**

## 11.1.1 Device Nomenclature

| PART NUMBER | OUTPUT<br>(X = TOTEM-POLE)<br>(Y = OPEN-DRAIN) | RESET TIMEOUT PERIOD |  |  |  |

|-------------|------------------------------------------------|----------------------|--|--|--|

| LM3704      | Χ, Υ                                           | 200 ms               |  |  |  |

## Table 1. Table of Functions

## **11.2 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.3 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

## 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated