DLPS030C - DECEMBER 2013-REVISED NOVEMBER 2015

**DLPC2607**

# **DLPC2607 DLP PICO Processor 2607 ASIC**

#### **Features**

- Supports Reliable Operation of the 0.2-nHD, 0.24-VGA, and 0.3-WVGA DMDs

- Multi-Mode, 24-Bit Input Pixel Interfaces:

- Supports Parallel or BT656 Bus Protocol

- Supports Input Sizes from QVGA Through **WVGA**

- Supports 1- to 60-Hz Frame Rates

- Supports Pixel Clock up to 33.5 MHz

- Supports Landscape and Portrait Orientations

- Support 8-, 16-, 18-, and 24-Bit Bus Options

- Supports 3 Input Color Bit-Depth Options:

- RGB888, YCrCb888

- RGB666, YCrCb666

- RGB565, 4:2:2 YCrCb

- Pixel Data Processing:

- Image Resizing (Scaling)

- Frame Rate Conversion

- Color Coordinate Adjustment

- Automatic Gain Control

- Programmable Degamma

- Spatial-Temporal Multiplexing (Dithering)

- Video Processing Support:

- Color Space Conversion

- 4:2:2 to 4:4:4 Chroma Interpolation

- Field Scaled De-Interlacing

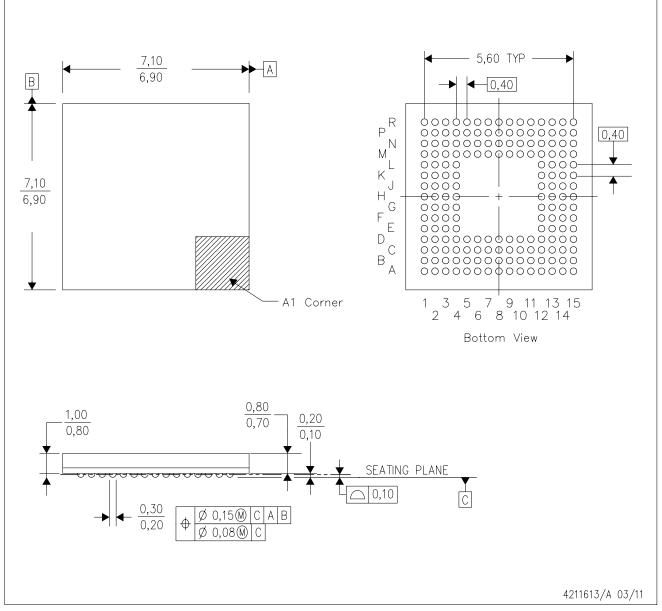

- Packaged in a 176-Pin, 0.4-mm Pitch, VFBGA

- **External Memory Support:**

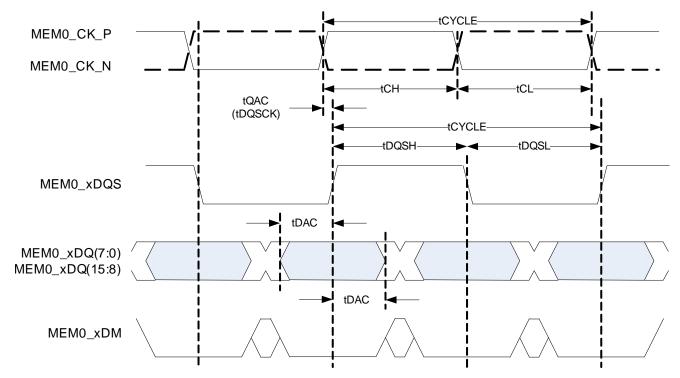

- 166-MHz Mobile DDR SDRAM

- 33.3-MHz Serial Flash

- WVGA, VGA, and nHD DMD Display Support

- DMD Bit-Plane Generation and Formatting

- Programmable Bit-Plane Display Sequencer (Controls the LED Enables and DMD Loading)

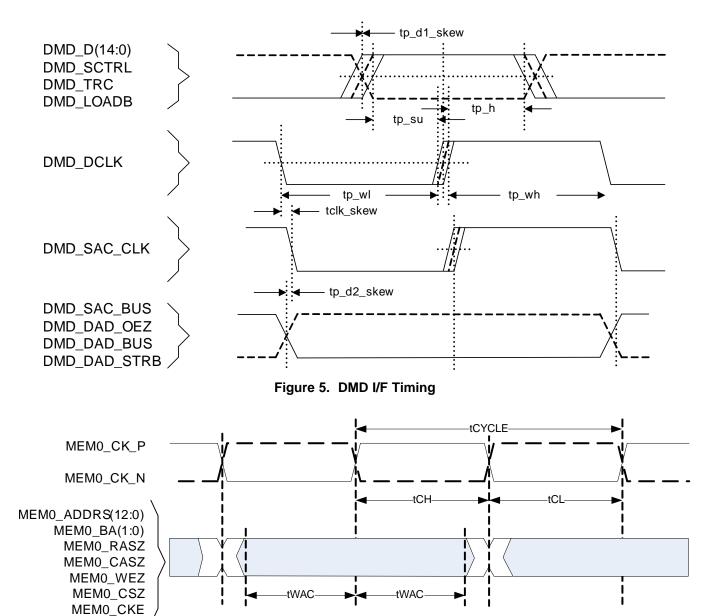

- 76.2-MHz Double Data Rate (DDR) DMD I/F

- Pulse-Width Modulation (PWM) for Mirrors:

- Auto DMD Parking at Power-Down

- 24-Bit Bit-Depth on DMD

- System Control:

- I<sup>2</sup>C Control of Device Configuration

- Programmable Splash Screens

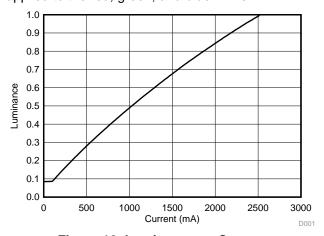

- Programmable LED Current Control

- DMD Power and Mirror Driver Control

- DMD Horizontal and Vertical Display Image

#### Flip

- Display Image Rotation

- Flash-Based Configuration Batch Files

- I/F Sleep Still Image Power Savings Mode

- **Test Support:**

- **Built-In Test Pattern Generation**

- JTAG With Boundary Scan Test Support

# 2 Applications

- **Embedded Mobile Projection**

- Smartphone

- Tablet

- Camera

- Laptop

- Mobile Accessories

- Wearable (Near-Eye) Displays

- **Battery-Operated Projectors**

# 3 Description

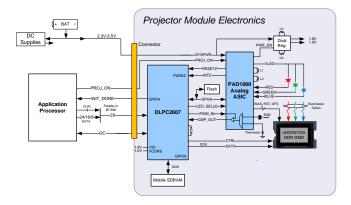

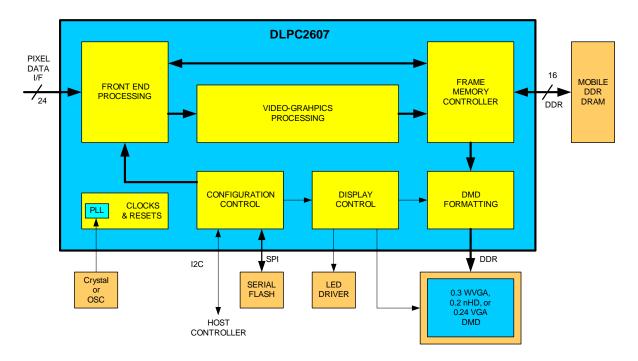

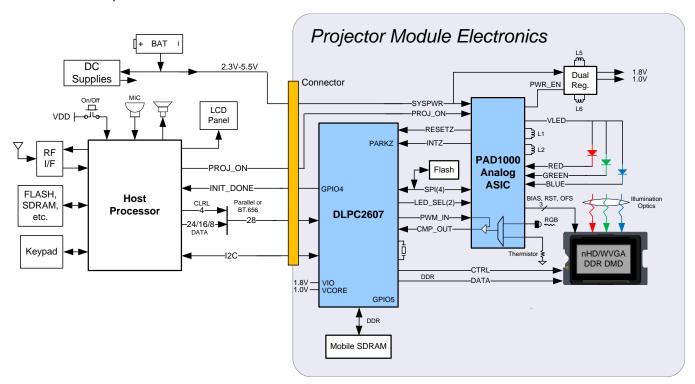

The DLPC2607 is a low power DLP™ digital controller for battery powered display applications. The controller supports reliable operation of 0.3-WVGA. 0.24-VGA and 0.2-nHD DMDs. DLPC2607 controller provides a convenient, multifunctional interface between system electronics and the DMD, enabling small form factor and low power displays.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |

|-------------|-------------|-------------------|--|

| DLPC2607    | VFBGA (176) | 7.00 mm × 7.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Table of Contents**

| 1 | Features 1                                              |    | 7.2 Functional Block Diagram                     | 19                |

|---|---------------------------------------------------------|----|--------------------------------------------------|-------------------|

| 2 | Applications 1                                          |    | 7.3 Feature Description                          | 19                |

| 3 | Description 1                                           |    | 7.4 Programming                                  | 21                |

| 4 | Revision History2                                       |    | 7.5 Device Functional Modes                      | 22                |

| 5 | Pin Configuration and Functions                         | 8  | Application and Implementation                   | 23                |

| 6 | Specifications8                                         |    | 8.1 Application Information                      | 23                |

| U | 6.1 Absolute Maximum Ratings                            |    | 8.2 Typical Application                          | 23                |

|   | 6.2 ESD Ratings                                         | 9  | Power Supply Recommendations                     | 27                |

|   | 6.3 Recommended Operating Conditions                    |    | 9.1 System Power Considerations                  | 27                |

|   | 6.4 Thermal Information                                 |    | 9.2 System Power-Up and Power-Down Sequence      | e <mark>27</mark> |

|   | 6.5 Typical Current and Power Dissipation               |    | 9.3 System Power I/O State Considerations        | 29                |

|   | 6.6 I/O Characteristics                                 |    | 9.4 Power-Up Initialization Sequence             | 29                |

|   | 6.7 Internal Pullup and Pulldown Characteristics 10     |    | 9.5 Power-Good (PARK) Support                    | 30                |

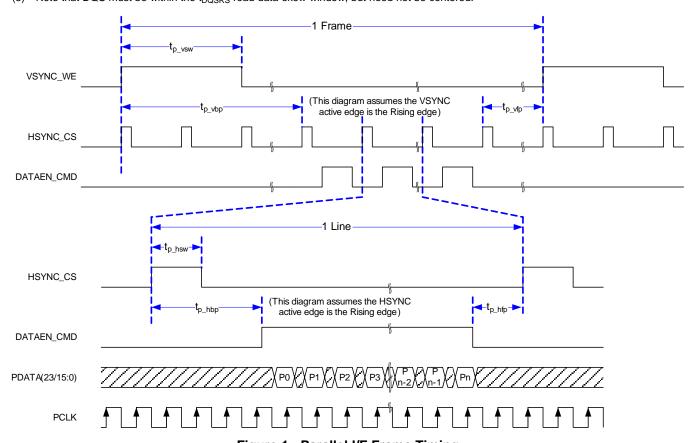

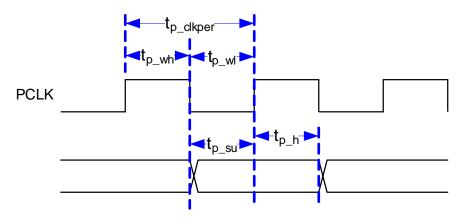

|   | 6.8 Parallel I/F Frame Timing Requirements              | 10 | Layout                                           | 31                |

|   | 6.9 Parallel I/F General Timing Requirements            |    | 10.1 Layout Guidelines                           | 31                |

|   | 6.10 Parallel I/F Max Supported Horizontal Line Rate 12 |    | 10.2 Layout Example                              | 37                |

|   | 6.11 BT.565 I/F General Timing Requirements             | 11 | Device and Documentation Support                 | 38                |

|   | 6.12 100- to 120-Hz Operational Limitations             |    | 11.1 Device Support                              | 38                |

|   | 6.13 Flash Interface Timing Requirements                |    | 11.2 Community Resources                         | 39                |

|   | 6.14 DMD Interface Timing Requirements                  |    | 11.3 Trademarks                                  | 39                |

|   | 6.15 mDDR Memory Interface Timing Requirements 15       |    | 11.4 Electrostatic Discharge Caution             | 39                |

| 7 | Detailed Description                                    |    | 11.5 Glossary                                    | 39                |

| • | 7.1 Overview                                            | 12 | Mechanical, Packaging, and Orderable Information | 39                |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision B (January 2014) to Revision C

Page

## Changes from Revision A (December 2013) to Revision B

**Page**

# Changes from Original (December 2013) to Revision A

Page

| • | Corrected columns for I <sub>OH</sub> and I <sub>OL</sub> in I/O Characteristics                  | 10 |

|---|---------------------------------------------------------------------------------------------------|----|

| • | Updated B38 I/O Type value for V <sub>OH</sub> (min) in <i>I/O Characteristics</i>                | 10 |

| • | Added additional table notes to I/O Characteristics                                               | 10 |

| • | Added table note to Internal Pullup and Pulldown Characteristics                                  | 10 |

| • | Corrected device reference to DLPC2607 in the notes for mDDR Memory Interface Timing Requirements | 15 |

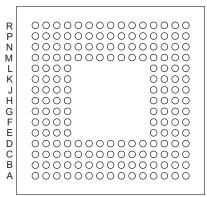

# 5 Pin Configuration and Functions

#### ZVB Package 176-Pin NFBGA Bottom View

#### 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

# Pin Functions (1)

| DIN                                                                          |                  | I/O             |      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------|------------------|-----------------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN                                                                          |                  |                 |      | CLOCK<br>SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| NAME NO. POWER TYPE DEVICE INITIALIZATION AND REFERENCE CLOCK <sup>(1)</sup> |                  |                 |      | STOTEM          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DEVICE INITIALIZA                                                            | ATION AND        | REFERENCE C     | LOCK |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RESETZ J14 VC                                                                |                  | VCC18           | l1   | Async           | DLPC2607 power-on reset. Self-configuration starts when a low-to-high transition is detected on this pin. All ASIC power and clocks must be stable before this reset is de-asserted (hysteresis buffer). Note that the following seven signals tri-state while RESET is asserted: DMD_PWR_EN, LEDDVR_ON, LED_SEL_0,LED_SEL_1, SPICLK, SPIDOUT, SPICSZ0 External pullups or pulldowns should be added as needed to these signals to avoid floating inputs where these signals are driven. |  |

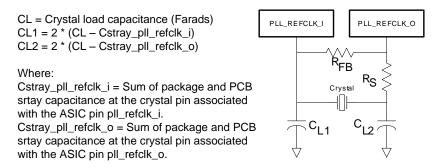

| PLL_REFCLK_I                                                                 | K15              | VCC18 (filter)  | 14   | N/A             | Reference clock crystal input. If an external oscillator is used in place of a crystal, then use this pin as the oscillator Input.                                                                                                                                                                                                                                                                                                                                                       |  |

| PLL_REFCLK_O                                                                 | J15              | VCC 16 (III.er) | O14  | N/A             | Reference clock crystal return. If an external oscillator is used in place of a crystal, then leave this pin unconnected (floating).                                                                                                                                                                                                                                                                                                                                                     |  |

| FLASH INTERFAC                                                               | E <sup>(2)</sup> |                 |      | •               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

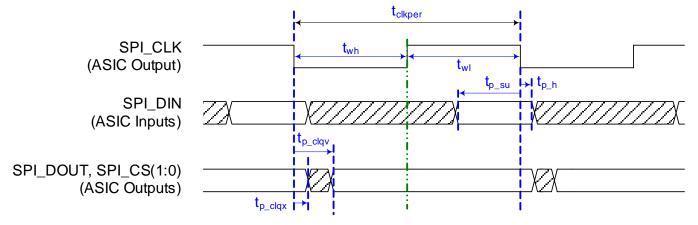

| SPICLK                                                                       | A4               |                 | O24  | N/A             | Clock for the external SPI device or devices                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| SPIDIN                                                                       | B4               |                 | 12   | SPICLK          | Serial data input from the external SPI device or devices                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| SPICSZ0                                                                      | A5               | VCC FLSH        | O24  | SPICLK          | Chip select 0 output for the external SPI flash device. Active low                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SPICSZ1                                                                      | C6               | 100_12011       | O24  | SPICLK          | Chip select 1 output for the external SPI PAD1000 device. Active low                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| SPIDOUT                                                                      | C5               |                 | O24  | SPICLK          | Serial data output to the external SPI device or devices. This pin sends address and control information as well as data when programming                                                                                                                                                                                                                                                                                                                                                |  |

| MAIN VIDEO DATA                                                              | AND CON          | TROL            |      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

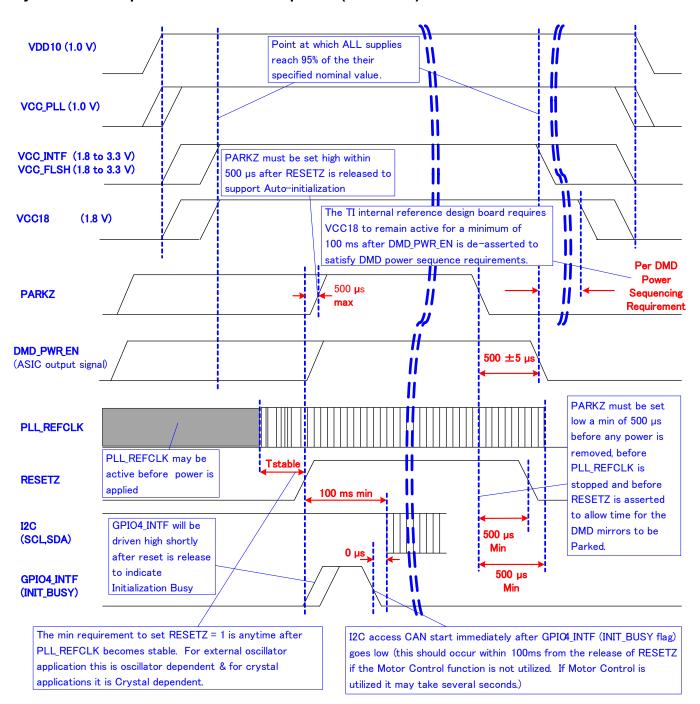

| PARK                                                                         | B8               | VCC_ INTF       | 13   | Async           | DMD park control (active low) is set high to enable typical operation. It should be set high prior to releasing RESET, or within 500 µs after releasing RESET. It should be set low a minimum of 500 µs before any power is to be removed from the DLPC2607 (hysteresis buffer).                                                                                                                                                                                                         |  |

| LED_ENABLE                                                                   | A11              | VCC_INTF        | 13   | Async           | LED enable (active high input). A logic low on this signal forces LEDDRV_ON low and LED_SEL(1:0) = b00. These signals are enabled 100 ms after LED_ENABLE transitions from low to high (hysteresis buffer).                                                                                                                                                                                                                                                                              |  |

| DBIC_CSZ                                                                     | B10              | VCC_ INTF       | 13   | SCL             | Unused/reserved: Should be pulled-up to VCC_INTF.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SCL                                                                          | A10              | VCC_ INTF       | B38  | N/A             | I <sup>2</sup> C clock (hysteresis buffer) bidirectional, open-drain signal. An external pullup is required. No I <sup>2</sup> C activity is permitted for a minimum of 100 ms after PARK and RESET are set high.                                                                                                                                                                                                                                                                        |  |

| SDA                                                                          | C10              | VCC_INTF        | B38  | SCL             | I <sup>2</sup> C data (hysteresis buffer) bidirectional, open-drain signal. An external pullup is required.                                                                                                                                                                                                                                                                                                                                                                              |  |

<sup>(1)</sup> Each device connected to the serial peripheral interface (SPI) bus must be operated off VCC\_FLSH

<sup>(2)</sup> Each device connected to the SPI bus must be operated off VCC\_FLSH

| PIN               |         | I/O       |      | CLOCK  | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |                       |  |

|-------------------|---------|-----------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| NAME              | NO.     | POWER     | TYPE | SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |                       |  |

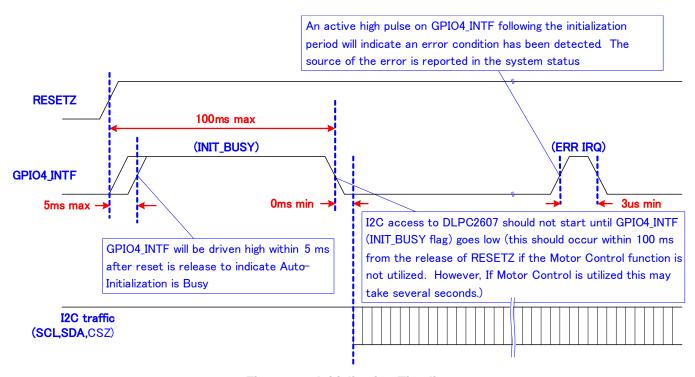

| GPIO4_INTF        | C9      | VCC_ INTF | B34  | Async  | General purpose I/O 4 (hysteresis buffer). Primary usage is to indicate when auto initialization is complete (also referred to as INIT-DONE, which is when GPIO4 transitions high then low following release of RESET) and to flag a detected erro condition in the form of a logic high, pulsed Interrupt flag subsequent to INIT-DONE. |                       |  |

| GPIO5_INTF        | В9      | VCC_ INTF | B34  | Async  | General purpose I/O 5 (hysteresis buffer). For applications that use focus motor control with a sensor, this pin is an input that is connected to the motor position sensor. For applications that use non-focus motor control with a sensor, configuration with an output at logic 0 and left unconnected.                              |                       |  |

| MAIN VIDEO DATA   | AND CON | ITROL     |      |        | PARALLEL RGB MODE                                                                                                                                                                                                                                                                                                                        | BT.656 I/F MODE       |  |

| PCLK (Hysteresis) | D13     | VCC_ INTF | 13   | N/A    | Pixel clock (3)                                                                                                                                                                                                                                                                                                                          | Pixel clock (3)       |  |

| PDM_CVS_TE        | H15     | VCC_INTF  | B34  | ASYNC  | Parallel data mask (4)                                                                                                                                                                                                                                                                                                                   | Unused (5)            |  |

| VSYNC_WE          | H14     | VCC_ INTF | 13   | ASYNC  | Vsync <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                     | Unused <sup>(5)</sup> |  |

| HSYNC_CS          | H13     | VCC_ INTF | 13   | PCLK   | Hsync <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                     | Unused (5)            |  |

| DATEN_CMD         | G15     | VCC_INTF  | 13   | PCLK   | Data valid <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                | Unused (5)            |  |

| PDATA[0]          | G14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data0 (7)             |  |

| PDATA[1]          | G13     | VCC_ INTF | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data1 (7)             |  |

| PDATA[2]          | F15     | VCC_INTF  | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Data2 (7)             |  |

| PDATA[3]          | F14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data3 <sup>(7)</sup>  |  |

| PDATA[4]          | F13     | VCC_INTF  | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Data4 (7)             |  |

| PDATA[5]          | E15     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data5 (7)             |  |

| PDATA[6]          | E14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data6 (7)             |  |

| PDATA[7]          | E13     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Data7 (7)             |  |

| PDATA[8]          | D15     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[9]          | D14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[10]         | C15     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[11]         | C14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[12]         | C13     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[13]         | B15     | VCC_ INTF | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[14]         | B14     | VCC_ INTF | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[15]         | A15     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[16]         | A14     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[17]         | B13     | VCC_ INTF | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused (5)            |  |

| PDATA[18]         | A13     | VCC_INTF  | 13   | PCLK   | Data <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                      | Unused (5)            |  |

| PDATA[19]         | C12     | VCC_ INTF | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused (5)            |  |

| PDATA[20]         | B12     | VCC_ INTF | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused (5)            |  |

| PDATA[21]         | A12     | VCC_ INTF | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused (5)            |  |

| PDATA[22]         | C11     | VCC_ INTF | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused <sup>(5)</sup> |  |

| PDATA[23]         | B11     | VCC_INTF  | 13   | PCLK   | Data (7)                                                                                                                                                                                                                                                                                                                                 | Unused (5)            |  |

- Pixel clock capture edge is software programmable.

Data mask is optional for parallel bus operation. If unused, it should be pulled to ground through a resistor.

Unused inputs should be pulled-down to ground through an external resistor.

VSYNC, HSYNC, and data valid polarity is software programmable.

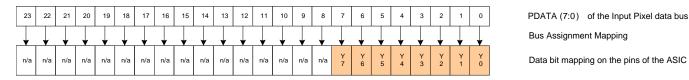

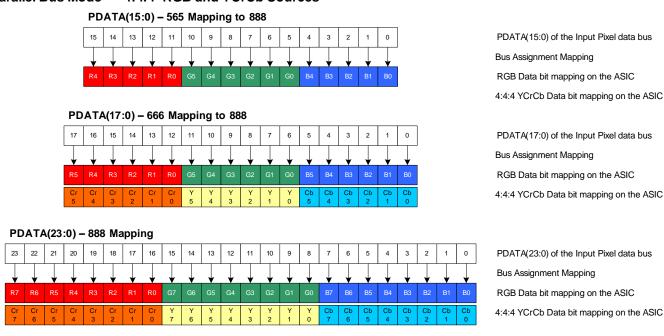

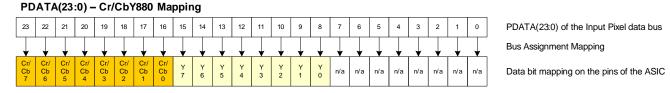

PDATA(23:0) bus mapping is pixel format and source mode dependent.

| PIN              |         | 1/0          | )    | CLOCK   | CK                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |

|------------------|---------|--------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| NAME             | NO.     | POWER        | TYPE | SYSTEM  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        | N                                     |  |

| LED DRIVER INTER | RFACE   |              |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |  |

| GPIO1_RPWM       | N8      |              | O14  | Async   | General-purpose I/O 1 (output only). If the PAD1000 is not used, then this output must be used as the red LED PWM signal used to control the LED current. (8) If the PAD1000 is used, then this output can be used as a general purpose output controlled by the WPC processor.                                                                                                                                                                    |                                       |  |

| GPIO2_GPWM       | P9      |              | O14  | Async   | General-purpose I/O 2 (output only). If the PAD must be used as the green LED PWM signal us the PAD1000 is used, then this output can be us controlled by the WPC processor.                                                                                                                                                                                                                                                                       | ed to control the LED current. (8) If |  |

| GPIO3_BPWM       | R8      |              | O14  | Async   | General-purpose I/O 3 (output only). If the PAD must be used as the blue LED PWM signal used the PAD1000 is used, then this output can be us controlled by the WPC processor.                                                                                                                                                                                                                                                                      | to control the LED current. (8) If    |  |

| LED_SEL_0        | R6      |              | O14  | Async   | LED enable SELECT. Controlled by programma (hysteresis buffer).                                                                                                                                                                                                                                                                                                                                                                                    | ble DMD sequence timing               |  |

|                  |         |              |      |         | LED_SEL(1:0)                                                                                                                                                                                                                                                                                                                                                                                                                                       | Selected LED                          |  |

|                  |         | VCC18        |      |         | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                 | None                                  |  |

|                  |         |              |      |         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Red                                   |  |

| LED_SEL_1        | N6      |              | 014  | Async   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Green                                 |  |

|                  |         |              |      |         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Blue                                  |  |

|                  |         |              |      |         | These outputs should be input directly to the PA not used, then a decode circuit is required to de                                                                                                                                                                                                                                                                                                                                                 |                                       |  |

| LEDDRV_ON        | P7      |              | O14  | Async   | LED driver enable. Active-high output control to external LED driver logic (master enable). It is driven high 100 ms after LED_ENABLE is driven high and driven low immediately when either LED ENABLE or PARK is driven low.                                                                                                                                                                                                                      |                                       |  |

| DMD_PWR_EN       | K14     |              | O14  | Async   | DMD power regulator enable (active high). This is an active-high output that should be used to control DMD V <sub>OFFSET</sub> , V <sub>BIAS</sub> , and V <sub>RESET</sub> voltages. DMD_PWR_EN is driven high when the PARK input signal is set high. However, DMD_PWR_EN is held high for 500 µs after the PARK input signal is set low before it is driven low. TI recommends a weak external pulldown resistor to keep this signal at a known |                                       |  |

| WHITE POINT COR  | RECTION | LIGHT SENSOR | l VF |         | state during power-up reset.                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |  |

| CMP_OUT          | A6      |              | I1   | Async   | Successive approximation ADC comparator output (DLPC2607 input). Assumes a successive approximation ADC is implemented with either a light sensor or thermocouple or both feeding one input of an external comparator and the other side of the comparator driven from the CMP_PWM pin of the ASIC. If this function is not used, pull it down to ground (hysteresis buffer).                                                                      |                                       |  |

| CMP_PWM          | В7      | VCC_ 18      | O14  | Async   | Successive approximation comparator pulse-wic<br>PWM signal to drive the successive approximati<br>to-voltage light sensor applications. If this function<br>unconnected.                                                                                                                                                                                                                                                                          | on ADC Comparator used in light-      |  |

| GPIO0_CMPPWR     | P5      |              | B14  | Async   | Power control signal for the WPC light sensor and other analog support circuits using the DLPC2607 ADC. Alternately, it provides general purpose I/O to the WPC microprocessor internal to the DLPC2607 device. If not used, leave it unconnected (hysteresis buffer).                                                                                                                                                                             |                                       |  |

| HWTEST_EN        | A9      | VCC _INTF    | 13   | N/A     | Manufacturing test enable signal. It should be connected directly to ground on the PCB for typical operation. Includes weak internal pulldown.                                                                                                                                                                                                                                                                                                     |                                       |  |

| JTAGTDI          | P6      |              |      | JTAGTCK | ITAC serial data in Includes weak internal nullun (When ITACRST7 is held low                                                                                                                                                                                                                                                                                                                                                                       |                                       |  |

| JTAGTCK          | N5      |              | I1   | N/A     | JTAG, serial data clock. Includes weak internal pullup.                                                                                                                                                                                                                                                                                                                                                                                            |                                       |  |

| JTAGTMS          | N7      | VCC _18      |      | JTAGTCK | JTAG, test mode select. Includes weak internal pullup.                                                                                                                                                                                                                                                                                                                                                                                             |                                       |  |

| JTAGTDO          | R7      |              | O14  | JTAGTCK | JTAG, serial data out                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |  |

| JTAGRSTZ         | P8      |              | I1   | ASYNC   | JTAG, RESET (active low). Includes weak interr to ground, through an external ≤15-kΩ resistor,                                                                                                                                                                                                                                                                                                                                                     |                                       |  |

<sup>(8)</sup> The PAD1000 is not available for initial DLPC2607 design applications. When the PAD1000 is not used, all LED PWM signals are forced high when LEDDRV\_ON = 0, software LED control is disabled, or the sequence stops.

| Pin Functions (7) (continued) |      |       |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |  |  |

|-------------------------------|------|-------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| PIN                           |      | I/O   |      | CLOCK  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                      |  |  |

| NAME                          | NO.  | POWER | TYPE | SYSTEM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |  |  |

| TSTPT_0                       | B B6 | VCC18 | B18  | Async  | Test pin 0 – Sampled as an input test mode selection control upon release of RESET, and then driven as an output. Includes weak internal pulldown. (9) Normal use: Reserved for test output (ICP/ WPC debug port TXD). Should be left open or unconnected for typical use.  Alternative use: If focus motor control is used, use this pin as the motor driver chip enable. An external pullup should not be applied to this pin to avoid putting the DLPC2607 device in a test mode.                      |                                                                                                      |  |  |

| TSTPT_1                       | A8   | VCC18 | B18  | Async  | Test pin 1 – Sampled as an input test mode sele RESET, and then driven as an output. Includes Normal use: Reserved for test output. Should be typical use.  Alternative use: If focus motor control is used, u bit1 (LSB). An external pullup should not be app DLPC2607 device in a test mode.                                                                                                                                                                                                           | weak internal pulldown. (9) e left open or unconnected for se this pin as the motor driver data      |  |  |

| TSTPT_2                       | C7   | VCC18 | B18  | Async  | Test pin 2 – Sampled as an input test mode selection control upon release of RESET, and then driven as an output. Includes weak internal pulldown. (9) Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: If focus motor control is used, use this pin as the motor driver data bit2. An external pullup should not be applied to this pin to avoid putting the DLPC2607 device in a test mode.                                                  |                                                                                                      |  |  |

| TSTPT_3                       | B5   | VCC18 | B18  | Async  | Test Pin 3 – Sampled as an input test mode selection control upon release of RESET, and then driven as an output. Includes weak internal pulldown. (9) Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: If focus motor control is used, use this pin as the motor driver motor driver data bit3. An external pullup should not be applied to this pin to avoid putting the DLPC2607 device in a test mode.                                     |                                                                                                      |  |  |

| TSTPT_4                       | A7   | VCC18 | B18  | Async  | Test pin 4 – Sampled as an input test mode selection control upon release of RESET, and then driven as an output. Includes weak internal pulldown. (9)  Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: If focus motor control is used, use this pin as the motor driver of bit4 (MSB). An external pullup should not be applied to this pin to avoid putting DLPC2607 device in a test mode.                                                 |                                                                                                      |  |  |

|                               |      |       |      |        | Without External Pullup (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | With External Pullup (10)                                                                            |  |  |

|                               |      |       |      |        | Enables auto-initialization from flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Disables auto-initialization and facilitates flash programming via I <sup>2</sup> C of a blank flash |  |  |

| TSTPT_5                       | C8   | VCC18 | B18  | Async  | Test pin 5 – Sampled as an input test mode selection control upon release of RESET and then driven as an output. Includes weak internal pulldown. (9) Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: Not yet defined. An external pullup should not be applied to this pin to avoid putting the DLPC2607 device in a test mode.                                                                                                              |                                                                                                      |  |  |

| TSTPT_6                       | N9   | VCC18 | B18  | Async  | Test pin 6 and PLL REFCLK frequency selection – Sampled as an input test more selection control upon release of RESET and then driven as an output. Includes weak internal pulldown. (9)  Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: Not yet defined.  This pin is sampled upon de-assertion of RESTZ to determine REFCLK frequer selection. DLPC2607 I <sup>2</sup> C address is set corresponding to the sampled input val as follows: |                                                                                                      |  |  |

|                               |      |       |      |        | Without External Pullup (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | With External Pullup (10)                                                                            |  |  |

|                               |      |       |      |        | PLL assumes REFCLK = 16.67 MHz  With External Pullup (10)  PLL assumes REFCLK = 8.33  MHz                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |  |  |

Product Folder Links: DLPC2607

(10) External pullup resistor must be 15 k $\Omega$  or less.

<sup>(9)</sup> If operation does not call for an external pullup and there is no external logic that might overcome the weak internal pulldown resistor, then this I/O can be left open or unconnected for typical operation. If operation does not call for an external pullup, but there is external logic that might overcome the weak internal pulldown resistor, then TI recommends an external pulldown resistor to ensure a logic low.

| PIN           |                                                                       | I/O   | CLOCK |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |  |

|---------------|-----------------------------------------------------------------------|-------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| NAME          | NO.                                                                   | POWER | TYPE  | SYSTEM | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |  |

| TSTPT_7       | R9                                                                    | VCC18 | B18   | Async  | Test pin 7 and I <sup>2</sup> C address selection – Sampled as an input test mode selection control upon release of RESET, and then driven as an output. Includes weak internal pulldown.  Normal use: Reserved for test output. Should be left open or unconnected for typical use.  Alternative use: Not yet defined.  This pin is sampled upon deassertion of RESET to determine I <sup>2</sup> C address selection. DLPC2607 I <sup>2</sup> C address is set corresponding to the sampled input valuas follows: |                                                                     |  |

|               |                                                                       |       |       |        | Without External Pullup (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | With External Pullup (10)                                           |  |

|               |                                                                       |       |       |        | I <sup>2</sup> C slave Write Address = x36<br>I <sup>2</sup> C slave Read Address = x37                                                                                                                                                                                                                                                                                                                                                                                                                             | $I^2C$ slave Write Address = x3A<br>$I^2C$ slave Read Address = x3B |  |

| POWER AND GRO | OUND <sup>(11)</sup>                                                  |       |       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |  |

| VDD10         | D5, D9,<br>F4, F12,<br>J4, J12,<br>M6, M8,<br>M11                     |       |       |        | 1-V core logic power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |  |

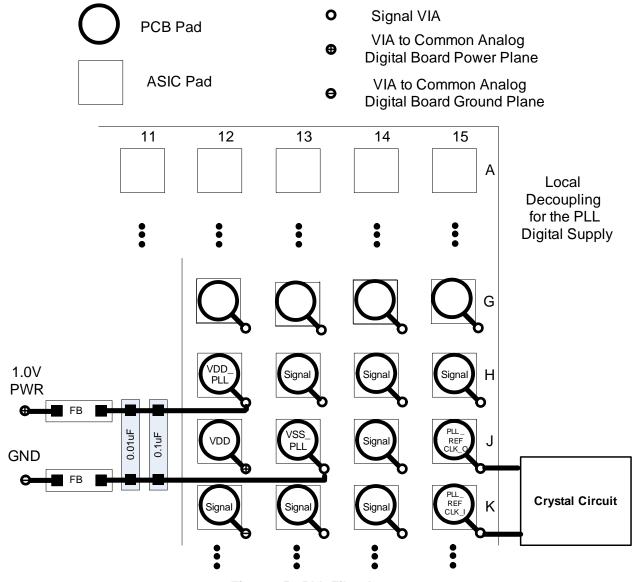

| VDD_PLL       | H12                                                                   |       |       |        | 1-V power supply for the internal PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |  |

| VCC18         | C4, D8,<br>E4, G3,<br>K3, K12,<br>L4, M5,<br>M9, M12,<br>N4, N12      |       |       |        | 1.8-V power supply for all I/O other than the ho buses                                                                                                                                                                                                                                                                                                                                                                                                                                                              | st, video interface, and SPI flash                                  |  |

| VCC_FLSH      | D6                                                                    |       |       |        | 1.8-V, 2.5-V, or 3.3-V power supply for SPI flas                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | h bus I/O                                                           |  |

| VCC_INTF      | D11, E12                                                              |       |       |        | 1.8-V, 2.5-V, or 3.3-V power supply for all I/Os (includes I <sup>2</sup> C, PDATA, video syncs, PARK, and                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |  |

| GND           | D4, D7,<br>D10,<br>D12, G4,<br>G12, H4,<br>K4, L12,<br>M4, M7,<br>M10 |       |       |        | Common ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |  |

| RTN_PLL       | J13                                                                   |       |       |        | Analog ground return for the PLL (This must be connected to the common ground GND through a ferrite.)                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |  |

| Reserved      | C2, C3,<br>N2, N3                                                     |       |       |        | No connects. Other signals can be routed througoing around them) to ease routing if desired                                                                                                                                                                                                                                                                                                                                                                                                                         | igh the ball on these pins (versus                                  |  |

<sup>(11) 134</sup> total signal I/O pins, 38 total power or ground pins, and 4 total reserved pins

# **Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1)

|                        |                                                   | MIN  | MAX  | UNIT |

|------------------------|---------------------------------------------------|------|------|------|

|                        | $V_{DD10}$                                        | -0.5 | 1.32 |      |

|                        | VDD_PLL                                           | -0.5 | 1.32 |      |

| Voltage <sup>(2)</sup> | V <sub>CC18</sub>                                 | -0.5 | 2.75 | V    |

| Voltage                | VCC_FLSH                                          | -0.5 | 3.6  | V    |

|                        | V <sub>CC_INTF</sub>                              | -0.5 | 3.6  |      |

|                        | V <sub>I</sub> 1.8 V, 2.5 V, 3.3 V <sup>(3)</sup> | -0.5 | 3.6  |      |

| $T_{J}$                | Operating junction temperature                    | -30  | 105  | °C   |

| T <sub>A</sub>         | Operating ambient temperature (4) (5)             | -30  | 85   | °C   |

| T <sub>stg</sub>       | Storage temperature                               | -40  | 125  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to GND and are at the device not at the power supply.

Applies to external input and bidirectional buffers.

Thus, maximum operating ambient temperature varies by application. (a)  $T_{A\_min} = T_{J\_min} - (P_{D\_min} \times R_{\theta JA}) = -30^{\circ}C - (0.0 \text{ W} \times 64.96^{\circ}C/W) = -30^{\circ}C$  (b)  $T_{A\_min} = T_{J\_min} - (P_{D\_min} \times R_{\theta JA}) = 105^{\circ}C - (0.3 \text{ W} \times 64.96^{\circ}C/W) = 85^{\circ}C$

# 6.2 ESD Ratings

|                  |                         |                                                                                          | VALUE | UNIT |

|------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| \/               | Electrostatic           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 | \/   |

| V <sub>(ES</sub> | <sup>D)</sup> discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                                |                  | MIN   | NOM | MAX                        | UNIT |

|-------------------|----------------------------------------------------------------|------------------|-------|-----|----------------------------|------|

| VDD10             | 1-V supply voltage, core logic                                 |                  | 0.95  | 1   | 1.05                       | V    |

| VDD_PLL           | Analog voltage for PLL                                         |                  | 0.95  | 1   | 1.05                       | V    |

| VCC18             | 1.8-V supply voltage (for all non-flash and host in            | terface signals) | 1.71  | 1.8 | 1.89                       | V    |

|                   |                                                                | 1.8-V LVCMOS     | 1.71  | 1.8 | 1.89                       | V    |

| VCC_FLSH          | C_FLSH Configuration and control I/O supply voltage (variable) | 2.5-V LVCMOS     | 2.375 | 2.5 | 2.625                      | V    |

|                   |                                                                | 3.3-V LVCMOS     | 3.135 | 3.3 | 3.465                      | V    |

|                   |                                                                | 1.8-V LVCMOS     | 1.71  | 1.8 | 1.89                       | V    |

| VCC_INTF          | Pixel interface supply voltage (variable)                      | 2.5-V LVCMOS     | 2.375 | 2.5 | 2.625                      | V    |

|                   |                                                                | 3.3-V LVCMOS     | 3.135 | 3.3 | 3.465                      | V    |

| V <sub>I</sub>    | Input voltage                                                  |                  | -0.3  |     | VCCIO <sup>(1)</sup> + 0.3 | V    |

| Vo                | Output voltage                                                 |                  | 0     |     | VCCIO <sup>(1)</sup>       | V    |

| t <sub>RAMP</sub> | Power supply ramp time                                         | ·-               | 10    |     |                            | μs   |

(1) VCCIO represents the actual supply voltage applied to the corresponding I/O.

TI strongly recommends I/O simulations (using IBIS models) for operation near the extremes of the supported ambient operating temperature range to ensure that the PCB design provides acceptable signal integrity.

The operating ambient temperature range assumes zero forced air flow, a JEDEC JESD51 junction-to-ambient thermal resistance value at zero forced air flow (R<sub>0JA</sub> at 0 m/s), a JEDEC JESD51 standard test card and environment, along with minimum and maximum estimated power dissipation across process, voltage, and temperature. Thermal conditions vary by application, which impacts R<sub>A IA</sub>.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.4 Thermal Information

over operating free-air temperature range (unless otherwise noted)

|                 | THERMAL METRIC <sup>(1)</sup>                               | DLPC2607<br>ZVB (NFBGA) | UNIT |

|-----------------|-------------------------------------------------------------|-------------------------|------|

|                 |                                                             | 176 PINS                |      |

| $R_{\theta JC}$ | Junction-to-case thermal resistance                         | 19.52                   | °C/W |

| $R_{\theta JA}$ | Junction-to-air thermal resistance (with no forced airflow) | 64.96                   | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

# 6.5 Typical Current and Power Dissipation

over operating free-air temperature range (unless otherwise noted)

|                         | TVDICAL                         | WVGA APP             | LICATIONS          | nHD APPL             | nHD APPLICATIONS   |  |  |

|-------------------------|---------------------------------|----------------------|--------------------|----------------------|--------------------|--|--|

| SUPPLY                  | TYPICAL<br>VOLTAGE (V)          | TYPICAL CURRENT (mA) | TYPICAL POWER (mW) | TYPICAL CURRENT (mA) | TYPICAL POWER (mW) |  |  |

| I/F Sleep Mode D        | Disabled <sup>(1) (2) (3)</sup> |                      |                    |                      |                    |  |  |

| VCC_INTF                | 1.8                             | 0                    | 0.1                | 0                    | 0.1                |  |  |

| VCC_FLSH <sup>(4)</sup> | 2.5                             | 0                    | 0                  | 0                    | 0                  |  |  |

| VCC18                   | 1.8                             | 28.2                 | 50.8               | 22.7                 | 40.9               |  |  |

| VDD_PLL                 | 1                               | 2.8                  | 2.8                | 2.8                  | 2.8                |  |  |

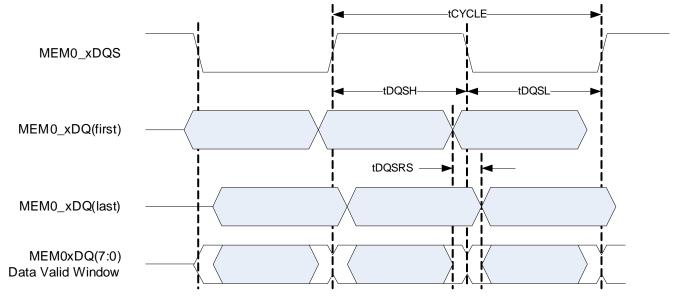

| VDD10                   | 1                               | 39                   | 39.0               | 37.7                 | 37.7               |  |  |